Design Guide: TIDA-010958

# Radiation-Hardened Dual-Phase Versal® FPGA Power Reference Design

## **Description**

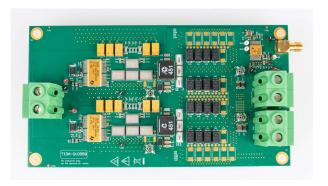

The TIDA-010958 is a radiation-hardened synchronous buck power reference design intended for the AMD® Versal® AI Core XQRVC1902 core rail. The design is optimized for a 12V input operation to generate a 0.8V output voltage and maximum 80A output current. This compact power design delivers high current while following the tight tolerance requirements of the FPGA. This power design, combined with the Versal® AI Core XQRVC1902. provides satellites with the accuracy, reliability, and efficiency needed to carry out different missions. TIDA-010958 has radiation-hardened devices and the passive components are compliant with MIL standard MIL-STD-55681 (or equivalent) where available. Otherwise, an equivalent value and component size was substituted.

#### Resources

TIDA-010958 Design Folder

TPS7H6023-SP Product Folder

TPS7H5004-SP Product Folder

Ask our TI  $E2E^{\mathsf{TM}}$  support experts

#### **Features**

- Radiation performance 100krad / 75MeV

- Nominal 12V DC input for space-based applications

- Load current up to 80A

- Switching frequency 278kHz

- · Packaged GaN assembly

- Board dimensions: 126.7mm × 61.2mm

- Designed to power core rail voltage of the AMD® Versal® AI Core XQRVC1902

## **Applications**

- Communications payload

- Radar imaging payload

- · Optical imaging payload

- Satellite electric power system (EPS)

System Description Www.ti.com

## 1 System Description

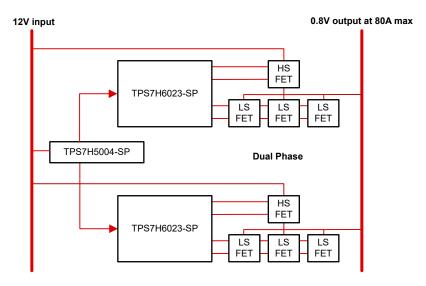

The TIDA-010958 reference design uses the TPS7H5004-SP, pulse-width modulation (PWM) controller, and TPS7H6023-SP gate driver, to create a synchronous buck converter. The design converts a 12V rail to a 0.8V rail intended for high-current FPGA designs and specifically to meet the regulation requirements of the AMD Versal™ AI Core XQRVC1902 core rail. A single TPS7H5004-SP provides a PWM output to two different TPS7H6023-SP devices which switch the FETs of the synchronous buck converter to provide voltage and current at the output. Each of the power stages delivers 40A for up to 80A total. Each gate driver drives one high-side FET and three low-side FETs. This reference design uses space-grade GaN FETs and a GaN gate driver.

## 2 System Overview

#### 2.1 Block Diagram

Figure 2-1. TIDA-010958 Block Diagram

#### 2.2 Design Considerations

**Table 2-1. Voltage and Current Requirements**

| PARAMETER            | SPECIFICATIONS |

|----------------------|----------------|

| Input Voltage        | 12V            |

| Output Voltage       | 0.8V           |

| Maximum Load Current | 80A            |

| Switching Frequency  | 278kHz         |

#### 2.2.1 Switching Frequency

There are different tradeoffs between efficiency and bandwidth in regard to the switching frequency. Higher switching frequencies have larger bandwidths, but a lower efficiency than lower switching frequencies. Based on the requirements, the maximum switching frequency for the device is 381kHz. To make sure the maximum switching frequency of the device was not approached, the switching frequency of the device was set to 278kHz. The switching frequency is set with equations from the *TPS7H5004-SP Radiation-Hardness-Assured 1.3A, 2.5A, Half Bridge GaN FET Gate Drivers* data sheet. The switching frequency is 278kHz for each phase.

#### 2.2.2 Design Size

Another key consideration in this design was creating a small design size while having a good efficiency. Generally, more compact designs have less space for cooling, causing heat dissipation problems, leading to reduced performance abilities. Additionally, placing components closely together can cause signal interference

www.ti.com System Overview

and a need for higher routing accuracy. This design prioritized having a small and compact design size while maintaining a reasonable efficiency.

#### 2.2.3 Gate Resistors

The gate resistors for the three low-side FETs in each phase were set to 0. This is intended to let the device switch as fast as possible and not allow efficiency to be affected by extra resistance in the current path.

#### 2.2.4 Output Ripple

To optimize the output ripple of the device to fit with the tight restrictions of the Versal FPGA core rail requirements, tantalum capacitors with a low ESR of 5mOhms each were chosen. The design consists of 8 tantalum capacitors per phase, making a total of 16 output tantalum capacitors.

#### 2.2.5 FET Placement

The recommended placement of the high side FET is directly centered between all the low side FETs. In this design there are three low-side FETs, so the high side FET is placed directly above the middle low side FET. The intention behind specific FET placement is to have balanced return paths with a single high side GaN FET to reduce potential switch node ringing.

#### 2.3 Highlighted Products

The following sections describe key features of the PWM controller and gate driver ICs used in this reference design.

#### 2.3.1 TPS7H5004-SP

The TPS7H500x-SP family of high speed radiation hardness-assured PWM controllers. The controllers provide a number of features that are beneficial for the design of DC-DC converter topologies intended for space applications. The controllers have a 0.613V +0.7%/–1% accurate internal reference and configurable switching frequency up to 2MHz. Each device offers programmable slope compensation and soft-start.

The TPS7H500x-SP series can be driven using an external clock through the SYNC pin or by using the internal oscillator at a frequency programmed by the user. The controller family offers the user various options for switching outputs, synchronous rectification capability, dead time (fixed or configurable), leading edge blank time (fixed or configurable), and duty cycle limit. Each device in the TPS7H500x-SP series is available in both a 22-pin CFP ceramic package and a 24-pin TSSOP plastic package.

#### 2.3.2 TPS7H6023-SP

The TPS7H60x3-SP series of radiation-hardness assured (RHA) gallium nitride (GaN) field effect transistor (FET) gate drivers is designed for high frequency, high efficiency applications. The series consists of the TPS7H6003-SP (200V rating), TPS7H6013-SP (60V rating), and the TPS7H6023-SP (22V rating). The drivers feature adjustable dead time capability, small 30ns propagation delay, and 5.5ns high-side and low-side matching. These parts also include internal high-side and low-side LDOs which makes sure of a drive voltage of 5V regardless of supply voltage. The TPS7H60x3-SP drivers all have split gate outputs, providing flexibility to adjust the turn-on and turn-off strength of the outputs independently.

The TPS7H60x3-SP drivers feature two control input modes: independent input mode (IIM) and PWM mode. In IIM each of the outputs is controlled by a dedicated input. In PWM mode, two complementary output signals are generated from a single input and the user can adjust the dead time for each edge.

The gate drivers also offer user configurable input interlock in independent input mode as anti-shoot through protection. Input interlock disallows turn-on of both outputs when both inputs are on simultaneously. The user has the option to enable or disable this protection in independent input mode, which allows the driver to be used in a number of different converter configurations. The drivers can also be utilized for both half-bridge and dual-low side converter applications.

The device is also offered in a plastic package as the TPS7H60x5-SEP and TPS7H60x5-SP.

## 3 Hardware, Testing Requirements, and Test Results

#### 3.1 Hardware Requirements

- TIDA-010958 Reference Design Board

- DC Power Supply (12V and 10A)

- Electronic Load (80A)

- Multimeter

- Oscilloscope

## 3.2 Test Setup

Connect the power supply to the input terminal blocks and place the GND and 12V connections in the correct slots. Input current for this board is up to approximately 10A, therefore verify that the power supply is rated to handle 10A at 12V. Connect the electronic load to the output terminal blocks by placing the GND cables in the terminal labeled *GND* and the output cables in the terminal labeled *0V8*. Increase the load to 80A.

#### 3.3 Test Results

#### 3.3.1 Efficiency Graphs

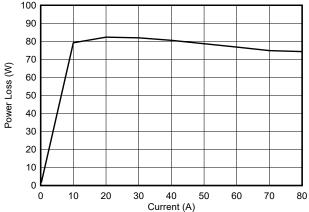

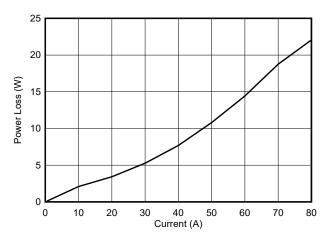

Figure 3-1 and Figure 3-2 show the TIDA-010958 efficiency and power loss graphs, respectively.

Figure 3-1. TIDA-010958 Efficiency, 12V Input, 0.8V Output

Figure 3-2. TIDA-010958 Power Loss, 12V Input, 0.8V Output

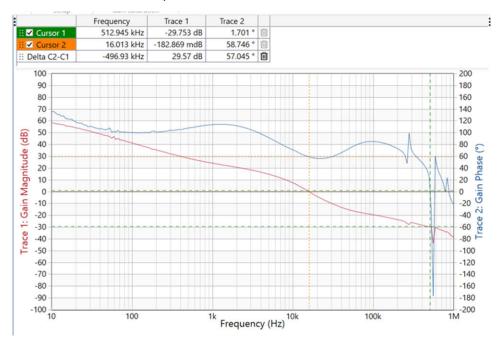

#### 3.3.2 Bode Plot

Figure 3-3 shows the TIDA-010958 bode plot.

Figure 3-3. 12V Input, 0.8V Output; Bandwidth = 10Hz, Phase Margin = 58.7 Degrees

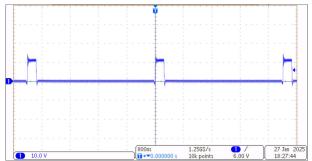

## 3.3.3 Switching

Figure 3-5 shows the switching behavior for TIDA-010958 measured with a test connector.

Figure 3-4. Switch Node Zoomed Out

Figure 3-5. 278kHz Switching Frequency

#### 3.3.4 Output Ripple

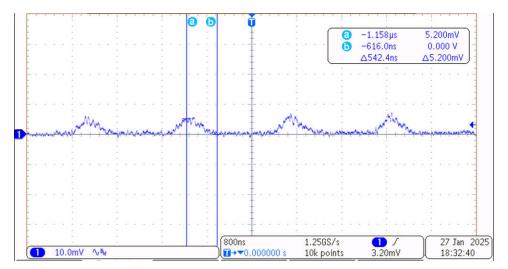

Figure 3-6 illustrates the TIDA-010958 output voltage ripple waveform. The output ripple is measured using a test connector.

Figure 3-6. Output Voltage Ripple (AC Coupled) Measured 5.2mV Peak to Peak

## 3.3.5 Gate Signals

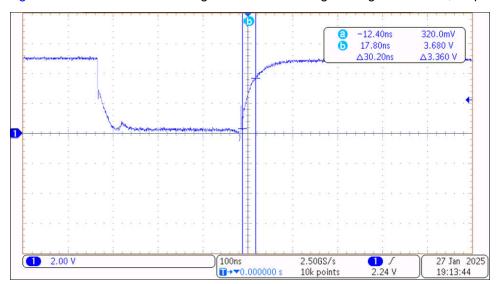

Figure 3-7 and Figure 3-8 illustrate the low-side gate rise time and high-side gate rise time, respectively.

Figure 3-7. Low-Side Gate Rise Time

Figure 3-8. High-Side Gate Rise Time

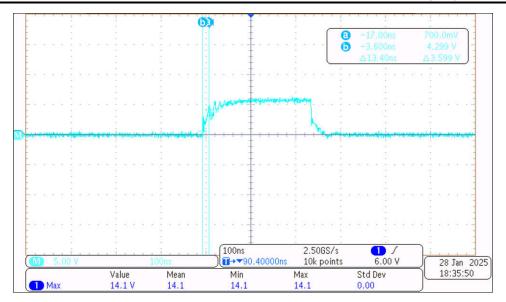

## 3.3.6 Start-Up Sequence

Figure 3-9 shows start-up behavior of TIDA-010958.

Figure 3-9. 12V Input, 0V Output, No Load

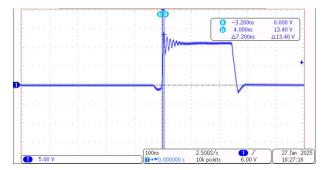

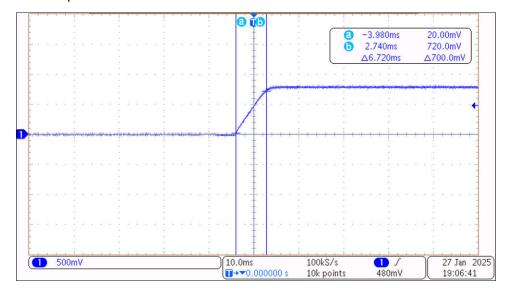

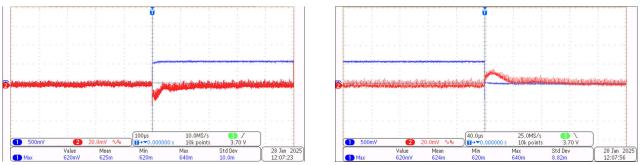

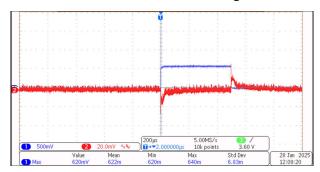

#### 3.3.7 Load Transient

Figure 3-12 shows the behavior of the TIDA-0109458 during a load transient at 0.8V, 10A to 30A, and 30A to 10A load steps.

Figure 3-10. 10A to 30A Load Step

Figure 3-11. 30A to 10A Load Step

Figure 3-12. 12V input; CH1: Output voltage, AC coupled 20mV/div; CH2: Output Current

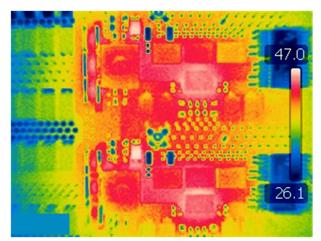

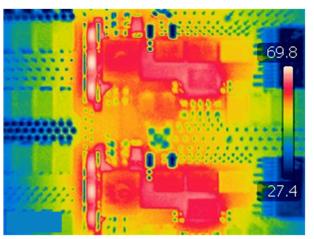

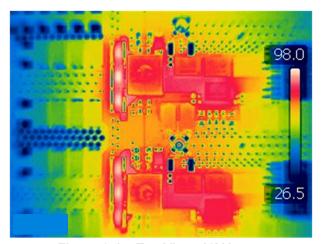

#### 3.3.8 Thermal Images

Figure 3-13, Figure 3-14, and Figure 3-15 show the thermal performance of the top side of the TIDA-010958 board at different load currents after one minute at each current.

Figure 3-13. Top View, 12V Input, 0.8V Output at 30A

Figure 3-14. Top View, 12V Input, 0.8V Output at 60A

Figure 3-15. Top View, 12V Input, 0.8V Output at 80A

## **4 Design and Documentation Support**

## 4.1 Design Files

#### 4.1.1 Schematics

To download the schematics, see the design files at TIDA-010958.

#### 4.1.2 BOM

To download the bill of materials (BOM), see the design files at TIDA-010958.

#### 4.2 Tools

#### **Tools**

POWERSTAGE-DESIGNER Power Stage Designer™ software tool of most commonly used switch-mode power supplies.

## 4.3 Documentation Support

- 1. Texas Instruments, TPS7H500x-SP Radiation-Hardness-Assured 2MHz Current Mode PWM Controllers Data Sheet

- 2. Texas Instruments, TPS7H60x3-SP Radiation-Hardness-Assured 1.3A, 2.5A, Half Bridge GaN FET Gate Drivers Data Sheet

## 4.4 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 4.5 Trademarks

TI E2E<sup>™</sup> and Power Stage Designer<sup>™</sup> are trademarks of Texas Instruments.

AMD® is a registered trademark of Advanced Micro Devices, Inc.

Versal® is a registered trademark of Xilinx, Inc.

All trademarks are the property of their respective owners.

#### 5 About the Author

**BHAVIKA KAGATHI** is a systems engineer at Texas Instruments, where she is responsible for developing system designs for space. Bhavika has been with TI since 2023. Bhavika earned her Bachelor of Science and Masters of Engineering in Bioengineering from the University of Illinois Urbana-Champaign.

www.ti.com Revision History

## **6 Revision History**

| Changes from Revision * (February 2025) to Revision A (March 2025) |                                                                                                | Page |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|

| •                                                                  | Updated the numbering format for tables, figures, and cross-references throughout the document | 1    |

| •                                                                  | Changed Figure 3-14 and Figure 3-15 by switching the images                                    | 9    |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated