# Design Guide: TIDA-010089 **Two-Quadrant, 15V, 8A, Programmable Linear DC Power Supply Reference Design**

# Description

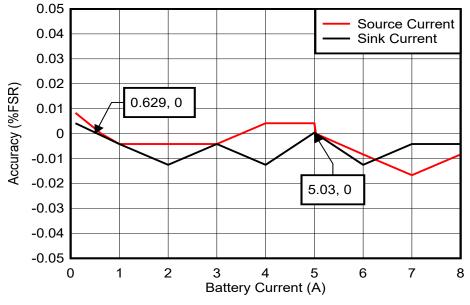

This reference design demonstrates a low-noise, efficient, bidirectional power supply that achieves less than  $\pm 0.02\%$  full-scale (FS) current and voltage control accuracy. The design utilizes an analog feedback loop for precise current control, and implements a voltage tracking circuit to minimize the power dissipation in linear stage for the source mode. This implementation enables 120W output power, and can sink up to 25W with external cooling.

## Resources

| TIDA-010089                       | Design Folder  |

|-----------------------------------|----------------|

| LM393BIDR, TMP708AIDBVR, TPSI305  | Product Folder |

| TVS1801, LMR38010, CSD17575Q3     | Product Folder |

| TLV709, LM2665, REF5025           | Product Folder |

| DAC70502DRXR, OPA192IDBVT, INA818 | Product Folder |

| LM358BIDGKR, TMUX4053, LM5146     | Product Folder |

#### Features

- Low-noise linear output stage, 3mVpp output noise in 20MHz bandwidth

- Precise current and voltage control with accuracy better than ±0.02% full scale

- · Maximum power during source operation: 120W

- Maximum power sink operation: 25W

- Tracking DC/DC to minimize power dissipation in source mode

## Applications

- Battery cell formation and test equipment

- Programmable DC power supply

Ask our TI E2E<sup>™</sup> support experts

# **1** System Description

The battery tester equipment includes a wide variety of equipment used to test single cells, battery modules, and high-voltage battery packs. The test equipment contains precision power supplies and data acquisition systems, and is used for charging and discharging of batteries, and measures various parameters of the cells.

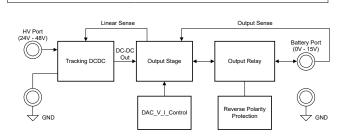

Figure 1-1 shows a simplified lithium-ion (Li-ion) battery manufacturing process. The Final stage, *End-of-Line Conditioning*, includes cell formation and testing. Formation is a critical step when manufacturing Li-ion cells. During formation, the cells go through a process of initial charge and discharge, which results in the formation of the solid electrolyte interface (SEI) layer. The quality of the SEI layer impacts the capacity and reliability of the battery cell. To control the formation process, precise programmable power supplies are used for charging and discharging of cells. These power supplies are called battery formation systems or battery testers. The accuracy required in battery testers for voltage and current is typically between  $\pm 0.02\%$  and  $\pm 0.05\%$  of full-scale.

Figure 1-1. Simplified Li-Ion Battery Manufacturing Process

### 1.1 Key System Specifications

| PARAMETER                          | SPECIFICATION                     |

|------------------------------------|-----------------------------------|

| Input Voltage                      | 24V to 48V                        |

| Output Voltage                     | 0V to 15V                         |

| Maximum Output Current             | ±8A                               |

| Тороlоду                           | DC/DC + LDO with voltage tracking |

| Power (Source)                     | 120W                              |

| Power (Sink)                       | 8W (without fan), 25W(with fan)   |

| Current and Voltage Set Resolution | 14b                               |

| Current Regulation Error           | < ±3mA (0.02% FS)                 |

| Voltage Regulation Error           | < ±3mV (0.02% FS)                 |

# 2 System Overview

### 2.1 Block Diagram

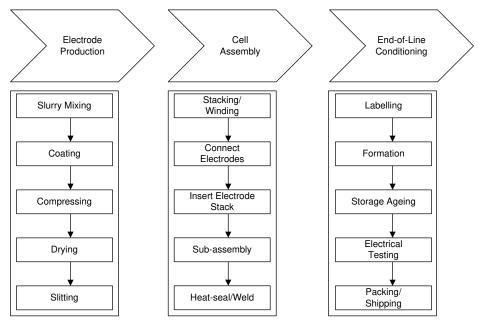

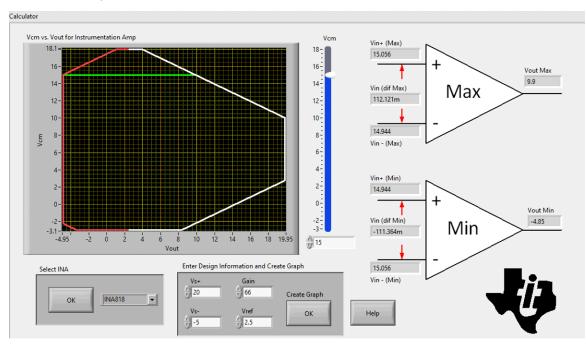

Figure 2-1 shows a block diagram of the reference design. LM5146 is a buck converter used in voltage tracking configuration to minimize the headroom of the discrete two-quadrant linear power stage. Precise current sense is implemented using INA818, and LM358 is used to measure the output voltage. The current and voltage sense signal are fed into the analog feedback loop which controls gate voltage of the power metal-oxide semiconductor field-effect transistor (MOSFET). A DAC70502 14-bit , 2-channel digital-to-analog converter (DAC), is used to set the output current and voltage. The DAC is programmed using a USB2ANY adapter.

Figure 2-1. Linear Battery Tester

### 2.2 Design Considerations

This reference design features low-noise, two-quadrant linear power supply with flexibility of output voltage adjustment. To improve efficiency, a tracking pre-regulator is implemented using the LM5146 buck converter for voltage tracking configuration to minimize the headroom of the discrete two-quadrant linear power stage.

Precise current sense is implemented using INA818, and LM358 is used to measure the output voltage. The current and voltage sense signals are fed into the analog feedback loop which controls the gate voltage of the power MOSFET. A DAC70502 14-bit , 2-channel DAC, is used to set the output current and voltage. The DAC is programmed using a USB2ANY adapter.

### 2.3 Highlighted Products

This reference design features the following devices:

- DAC70502: Dual-channel, 1-LSB INL, 14-bit, serial peripheral interface (SPI) voltage-output digital-to-analog converter (DAC)

- INA818: Low-power (350µA), precision instrumentation amplifier with ±60V over-voltage protection (gain pins 1, 8)

- OPA192: High-voltage, rail-to-rail input/output, 5µV, 0.2µV/°C, precision operational amplifier

- LM5146: 100V synchronous buck DC/DC controller with wide duty-cycle range

#### 2.3.1 DAC70502: Dual-Channel, 1-LSB INL, 14-Bit, SPI Voltage-Output Digital-to-Analog Converter (DAC)

The DAC70502 device offers linearity of < 1LSB. The high accuracy combined with a tiny package make the DAC70502 an excellent choice for applications such as gain and offset calibration, current or voltage set point generation, and power-supply control. These devices include a 2.5V, 5ppm/°C internal reference, giving full-scale output voltage ranges of 1.25V, 2.5V, or 5V.

The digital interface of the DAC70502 can be configured to a SPI or I2C mode using the SPI2C pin. In SPI mode, the DAC0502 uses a versatile 3-wire serial interface that operates at clock rates up to 50MHz. In I2C mode, the DAC70502 operates in standard (100kbps), fast (400kbps), and fast+ (1.0Mbps) modes.

Important features include:

- 16-bit performance: 1-LSB INL and DNL (maximum)

- Pin-selectable serial interface

- 3-wire, SPI compatible up to 50MHz

- 2-wire, I2C compatible

- Low power: 1mA per channel at 5.5V

#### 2.3.2 INA818: 35µV Offset, 8nV/\/Hz Noise, Low-Power, Precision Instrumentation Amplifier

The INA818 is a high-precision instrumentation amplifier that offers low power consumption and operates over a very wide single-supply or dual-supply range. A single external resistor sets any gain from 1 to 10000. This device measures and amplifies a differential voltage that represents output current which acts as feedback to regulate current. With a built-in super-beta input transistor, this device provides low-input offset voltage, offset voltage drift, input bias current, input voltage, and current noise.

Important features include:

- Gain drift: 5ppm/°C (G = 1), 35ppm/°C (G > 1) (maximum)

- Bandwidth: 2MHz (G = 1), 270kHz (G = 100)

- Inputs protected up to ±60V

- Common-mode rejection: 110dB, G = 10 (minimum)

#### 2.3.3 OPA192: High-Voltage, Rail-to-Rail Input/Output, 5µV, 0.2µV/°C, Precision Operational Amplifier

OPA192IDBVT offers outstanding DC precision and AC performance, including rail-to-rail input/output, low offset ( $\pm 5\mu$ V, typ), low offset drift ( $\pm 0.2\mu$ V/°C, typ), and 10MHz bandwidth. Such amplifier offers high-precision constant current (CC) loop control voltage to calibrate the target signal. Unique features such as differential input-voltage range to the supply rail, high-output current ( $\pm 6mA$ ) high capacitive load drive of up to 1nF, and high slew rate (20V/µs) make the OPA192 a robust, high-performance operational amplifier for high-voltage industrial applications.

Important features include:

- Wide supply: ±2.25V to ±18V, 4.5V to 36V

- Low offset voltage drift: ±0.2µV/°C

- Wide bandwidth: 10MHz gain-bandwidth (GBW)

- · Low quiescent current: 1mA per amplifier

#### 2.3.4 LM5146: 100V Synchronous Buck DC/DC Controller With Wide Duty Cycle Range

The LM5146 100V synchronous buck controller regulates from a high input voltage source or from an input rail subject to high-voltage transients, minimizing the need for external surge suppression components. The LM5146 continues to operate during input voltage dips as low as 5.5V, at nearly 100% duty cycle, if needed, making the device an excellent choice for high-performance industrial controls, robotics, data communication, and RF applications. Feedback pins provide a reference voltage for tracking the linear stage feedback.

Important features includes:

- Wide input voltage range of 5.5V to 100V

- 0.8V reference with ±1% feedback accuracy

- Adjustable output voltage from 0.8V to 60V

# **3 System Design Theory**

# 3.1 Constant Current Control Design

The constant current control design requires a high-precision current sensor, and the selection of the right operational amplifier (op amp) for measuring battery charge or battery discharge current through a shunt resistor is pivotal for accurate and reliable current measurement. The Y14770R00300F9R shunt resistor, with a resistance of  $3m\Omega$  made up of a power metal strip, is an excellent choice for current sensing. With a 1% tolerance and a maximum temperature coefficient of ±40ppm/°C, this shunt resistor provides accurate and stable performance.

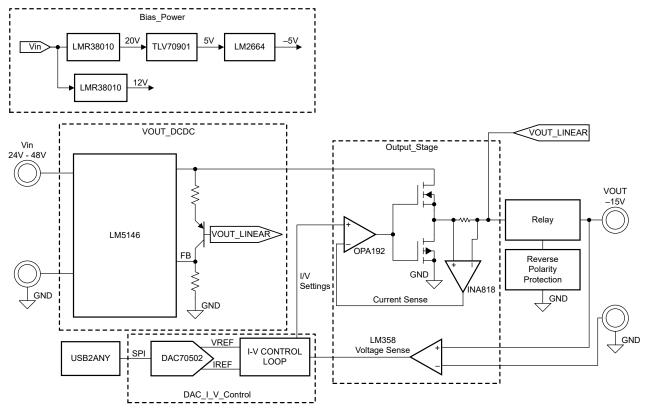

For amplifying the current signal across the shunt, the INA818, a high-precision instrumentation amplifier, is used. The choice of an instrumentation amplifier with the right common-mode voltage is crucial, because the amplifier directly impacts the input and output voltage limitations. The instrumentation amplifier provides compatibility with the common-mode voltage of the application and is essential for achieving accurate and reliable current measurements in CC control.

Using TI's analog engineer's calculator to determine the input common-mode and limitations of the INA818, Figure 3-1 shows the calculation results. The maximum common-mode voltage is consistent with the maximum voltage on the battery side, which is 15V in this case. The INA818 is powered by 20V and –5V, and the reference voltage generated from the DAC is 2.5V. When the gain is set to 66, the calculation shows the input range from –111.4mV to 112.1mV, fitting within the current signal range ( $\pm 8A \times 3m\Omega = 24mV$ ).

The CC control loop also needs a high-precision op amp. The precision drift op amp, OPA192, with maximum input offset drift of  $\pm 0.1 \mu$ V/°C, is used for this function.

Figure 3-1. Vcm vs Vout Calculator for INA818

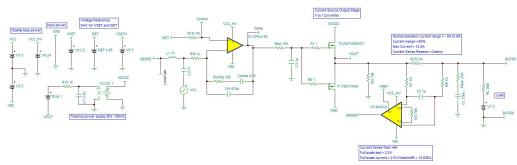

Figure 3-2 illustrates the CC control loop schematic. The output voltage, linked to a voltage-controlled voltage source, functions as the tracking input for the DC-DC converter, supplying  $V_{DCDC}$  to the MOSFET drain. An intentional 1V rise is incorporated into the configuration to maintain  $V_{DS}$  at 1V, regardless of load conditions. The reference voltage,  $I_{SET}$ , is generated from a digital-to-analog converter (DAC) to control the output current or voltage depending on the operation mode. Another input,  $I_{SENSE}$  is the current feedback signal acquired through the differential voltage across the current sense resistor. These signals undergo differentiation in the error amplifier, OPA192, to facilitate current loop control. For small signal simulation, a 1TF capacitor and 1TH inductor are connected to the  $I_{SENSE}$ . This purpose is to break the feedback loop as the capacitor is open at DC while the inductor is a short. At high frequencies, the inductor is open and the capacitor is shorted.

Figure 3-2. Schematic for Constant Current Loop Simulation

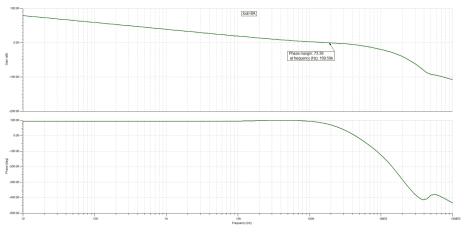

Figure 3-3 shows the small signal of the CC simulation. The phase margin for constant current output of 8A is 73.39°, with the crossover frequency of 189.59kHz. This simulation affirms the stability of the control circuit and bandwidth sufficiency.

Figure 3-3. Stability Simulation for Current Loop Analysis

The voltage to adjust output current can be set from 0V to 5V. Use Equation 1 to calculate the input reference voltage for the desired current settings. In this reference design, to generate 8A output current,  $I_{SET}$ , the DAC output voltage, is set to 4.08V.

$I_{SET} = I_{desired} \times INA818 \text{ gain} \times R_{SENSE} + V_{REF}$

6

(1)

(2)

7

# 3.2 Constant Current and Voltage Simulation

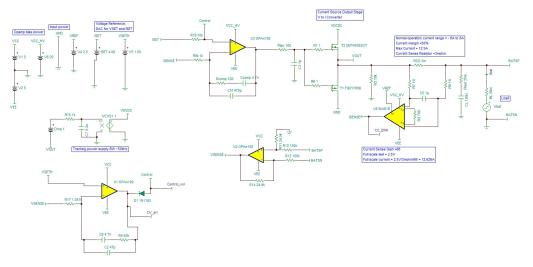

Figure 3-4 shows the simulation of the battery charging circuit with the CC and CV loops. The CC and CV control loops are interconnected through D1 and R19. The battery charging environment is simulated with an output capacitance of 10mF.

Figure 3-4. Power Supply With Constant Current and Voltage Loops

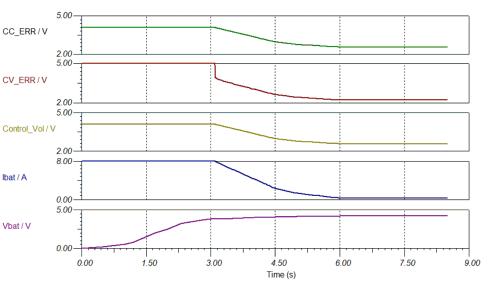

Figure 3-5 shows the transient schematic capturing the transition from CC to CV control during the battery charging process. Initially when the battery is depleted, the CC control loop is activated and the battery is charged at a constant current of 8A. The charge current is determined by the DAC ISET. As the battery capacity increases, the output voltage of the CV error amplifier decreases, leading to a gradual transition into CV control. During this phase, the charging current gradually decreases while the charge voltage is maintained at a constant level. Ultimately, when the battery reaches full charge, the charging current approaches zero, and the voltage is stabilized at 4.2V, as set by the DAC VSET reference voltage.

$$V_{REF} = LM358B \text{ gain} \times V_{OUT}$$

Figure 3-5. CC to CV Transition

# 4 Hardware, Software, Testing Requirements, and Test Results

### 4.1 Hardware Requirements

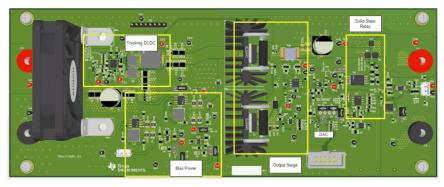

Figure 4-1 shows the hardware snapshot for this reference design. Jumper J9, J10, J12, and J13 configure the power rail connections to circuitry on the board. The J5 jumper provides reference voltage programmed by the DAC to the control system for configuring operation mode. J7 can disable the solid-state relay to interrupt output states. J8 controls functionality of the output switch relay based on the sensing signal from the feedback, safeguarding the circuit from reverse polarity.

Figure 4-1. TIDA010089 Hardware

The MOSFETs in the output stage are responsible for either sourcing or sinking current from the battery side, the excess heat must be carried away from both MOSFETS to provide normal operation. The heat sink and fan is applied in this design to dissipate any excess amount of heat. Particularly, the P-channel metal-oxide-semiconductor (PMOS) handles sinking the current and has higher thermal resistance. The selection of the heat sink and fan is contingent upon the specific power dissipation requirements and case temperature criteria. In this design, the target power dissipation is 8W without the fan, and the chosen heat sink is capable of dissipating 20W with an airflow of 30ft<sup>3</sup>/min. This makes sure that the thermal management of the system meets the design specifications for reliable operation.

### 4.2 Software Requirements

In this reference design, the reference signal for current and voltage loops uses the DAC70502, 14-bit DAC, which is programmed using the USB2ANY interface adapter.

Use the following steps for the initial setup of a new USB2ANY device:

- 1. Open the USB2ANY Explorer

- 2. Click and hold the button inside the small hole of the USB2ANY before plugging the device into the computer

- 3. The software prompts for an update after the device is plugged in

- 4. Confirm the software update

- 5. Release the button

USB2ANY sets up the device properly.

Use the following steps to configure the DAC:

- 1. Open the USB2Any Explorer

- 2. Click the Select Interfaces button. The Select Interfaces window opens

- 3. Select SPI

- 4. Close the Select Interfaces window

- 5. In the *USB2Any Explorer* window, select *SPI* above activity logging. If the *SPI* tab is not shown, click around the space above activity logging because the tabs can be hidden.

- 6. Write data code into the terminal to generate the desired output parameter

Figure 4-2 shows the GUI parameters for the setup.

| USB2ANY Explorer v2.7.0.5                                                                                                                                                                                                                                                                                  | (API v2.7.0.0)                                                                                        |                                                                                                                                                                                                                                                                                               |                                                 |                                     | _     | ×            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------|-------|--------------|

|                                                                                                                                                                                                                                                                                                            |                                                                                                       |                                                                                                                                                                                                                                                                                               |                                                 |                                     |       |              |

| Type: USB2ANY Rev:                                                                                                                                                                                                                                                                                         | Serial #:                                                                                             |                                                                                                                                                                                                                                                                                               | Firmware Vers                                   |                                     | Clo   | se Device    |

| Inactive Low                                                                                                                                                                                                                                                                                               | ock Phase<br>● Trailing Edge<br>⊂ Leading Edge                                                        | CS Polarity<br>C Active High<br>Active Low                                                                                                                                                                                                                                                    | Bit Direction<br>C LSB First<br>MSB First       | Length<br>7 Bits<br>© 8 Bits        | Selec | t Interfaces |

| Bit Rate Si                                                                                                                                                                                                                                                                                                | ave Device                                                                                            | CS Type<br>Per Packet                                                                                                                                                                                                                                                                         |                                                 |                                     |       |              |

| MOSI Message / Data                                                                                                                                                                                                                                                                                        |                                                                                                       |                                                                                                                                                                                                                                                                                               |                                                 |                                     | 3.    | 3V OFF       |

| Write data:                                                                                                                                                                                                                                                                                                |                                                                                                       |                                                                                                                                                                                                                                                                                               | 1:3                                             |                                     |       |              |

| 09 4C 7C                                                                                                                                                                                                                                                                                                   |                                                                                                       |                                                                                                                                                                                                                                                                                               | [                                               | Write/Read<br>3 bytes<br>• Auto-set | 5.    | OV OFF       |

| Read data:                                                                                                                                                                                                                                                                                                 |                                                                                                       |                                                                                                                                                                                                                                                                                               |                                                 |                                     |       |              |

| 00 00 00                                                                                                                                                                                                                                                                                                   |                                                                                                       |                                                                                                                                                                                                                                                                                               | -                                               | Load<br>Save<br>Clear Data          |       |              |

|                                                                                                                                                                                                                                                                                                            |                                                                                                       |                                                                                                                                                                                                                                                                                               |                                                 |                                     | Log   | Comment      |

| Activity Log:<br>Timestamp Mod R/W                                                                                                                                                                                                                                                                         | / Addr Len Data/Me                                                                                    | essage                                                                                                                                                                                                                                                                                        |                                                 |                                     |       |              |

| 2023-12-04 11 INFO   2023-12-04 11 SPI   2023-12-04 11 SPI | Enabled<br>Clock p<br>Clock p<br>Latch p<br>SPI bit 1<br>SPI bit 1<br>Charact<br>Target 1<br>SPI with | re Version: 2.7.0.0<br>EVM Detect interrupt<br>olarity set to Inactive L<br>nase set to Falling Edg<br>olarity set to Active Hig<br>rate set to 100.000 kH<br>rate set to 100.000 kH<br>re length set to 8 bits<br>Power: 3.3v is OFF, 5.<br>je/read count set to 3<br>rate set to 100.000 kH | Low<br>Je<br>gh<br>Iz.<br>Jv is OFF, Adj is OFF |                                     |       |              |

Figure 4-2. USB2ANY Configuration

#### 4.3 Test Setup

#### 4.3.1 Constant Current Test Setup

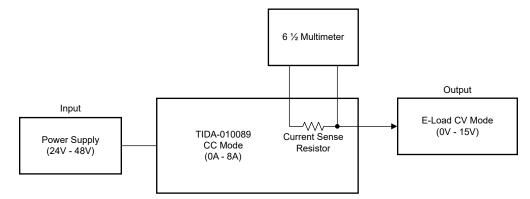

Figure 4-3 shows the hardware setup to test the constant current charging performance.

Figure 4-3. Constant Current Charging

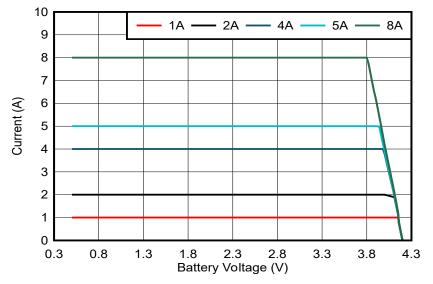

Given the capability of the design to source up to 120W of power, the input power supply needs to provide sufficient power to support the charge mode. The output electronic load (e-load) simulates the battery charging process. Set the e-load to CV mode and make sure the voltage value is lower than the output voltage set by DAC. At start-up,  $V_{SET}$  is at 2.5V which makes the output voltage 10V at open load. Without modifying the  $V_{SET}$ , set the e-load to less than 10V.

Connect a multimeter across the current shunt resistor on the board by placing the positive probe on TP9 and the negative probe on TP10 to measure the voltage across the sense resistor. This voltage can be utilized to

calculate the output current. Using a 6.5-digits multimeter is recommended for precise measurements in the microvolt range. Due to offset in the sense resistor and the gain resistor for INA818, the calculated current across the shunt can exhibit a slight variation of 1mA to 2mA.

After completing the hardware setup, turn on the input power supply only, and observe the e-load voltage reading. At this point the e-load is acting as a multimeter measuring the open load voltage. The reading can drop to zero volts from some voltage, due to the current loop being active initially, driven by offsets in the cascading op amps and feedback resistors. At this point, the Constant Current (CC) loop has a lower voltage level and takes control of the system. Increase the I<sub>REF</sub> by applying any code of I<sub>SET</sub> which is greater than mid-voltage can pull the voltage control signal across D3, enabling the Constant Voltage (CV) loop to take control of the system.

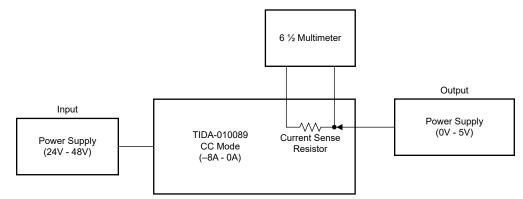

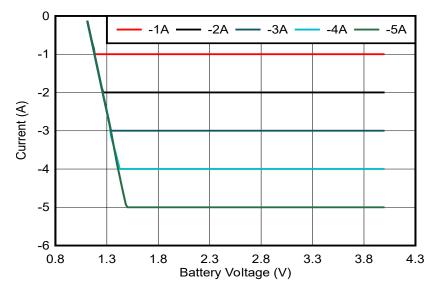

Figure 4-4 shows the hardware setup used to test the CC discharging performance.

Figure 4-4. Constant Current Discharging

Similar to the CC loop setup at positive current, the only difference lies in replacing the output e-load with a power supply. When the fan is off, configure the power supply within the 8W limit. When the fan is active, the output supply can be set within the 20W limit to align with the maximum heat dissipation of the design. Make sure that at full negative current range, the voltage of the power supply does not exceed 2.5V to prevent power dissipation of more than 20W.

### 4.3.2 Constant Voltage Test Setup

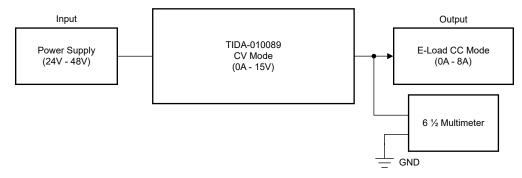

Figure 4-5 shows the test setup for CV control loop.

Figure 4-5. Constant Voltage Test Setup

Make sure the setting current of the e-load is configured to a value less than the control current set by the DAC to maintain a stable voltage loop.

Connect the positive probe of the 6.5-digits multimeter to the output of the board for an accurate reading of the voltage in mV.

# 4.4 Test Results

## 4.4.1 Current Control Accuracy

The current loop can be affected by the variation of the output voltage level. To assess any impact on the control loop, perform a load regulation test. Table 4-1 shows the CC load regulation for charging and Table 4-2 shows the CC load regulation for discharging.

| FULL SCALE<br>RATING (FSR) (A) | 8       |          |          |                   |          |          |

|--------------------------------|---------|----------|----------|-------------------|----------|----------|

| I <sub>SET</sub> (A)           | 0.1     | 1        | 2        | 4                 | 6        | 8        |

| CV E-LOAD                      |         |          | ISENS    | <sub>ie</sub> (A) |          |          |

| 1                              | 0.09987 | 1.00033  | 2.00033  | 3.99933           | 6.00033  | 7.99933  |

| 2                              | 0.09933 | 1.00033  | 2.00033  | 3.99933           | 6.00033  | 7.99933  |

| 4                              | 0.09933 | 1.00033  | 2.00000  | 4.00033           | 6.00067  | 8.00133  |

| 8                              | 0.09967 | 1.00067  | 2.00067  | 4.00067           | 6.00167  | 8.00500  |

| 10                             | 0.09967 | 1.00003  | 2.00033  | 4.00067           | 6.00167  | 8.00567  |

| 14                             | 0.09967 | 1.00067  | 2.00067  | 4.00033           | 6.00133  | 8.00667  |

| ERROR (%FSR)                   | 0.00833 | -0.00833 | -0.00833 | -0.00833          | -0.02083 | -0.08333 |

Table 4-1. Constant Current Load Regulation for Charging

| Table 4-2 | Constant | Current | l oad F | Regulation  | for | Discharging |

|-----------|----------|---------|---------|-------------|-----|-------------|

|           | Constant | ouncill |         | (cguiation) | 101 | Discharging |

| FSR (A)                      | -8                     |               |          |          |          |          |  |  |

|------------------------------|------------------------|---------------|----------|----------|----------|----------|--|--|

| I <sub>SET</sub> (A)         | 0.1                    | 0.1 1 2 3 4 5 |          |          |          |          |  |  |

| CV POWER<br>SUPPLY (BATTERY) | I <sub>SENSE</sub> (A) |               |          |          |          |          |  |  |

| 1                            | -0.10133               | -1.00133      | -2.00167 | -3.00167 | -4.00167 | NA       |  |  |

| 2                            | -0.10167               | -1.00167      | -2.00167 | -3.00167 | -4.00167 | -5.00167 |  |  |

| 3                            | -0.10167               | -1.00167      | -2.00167 | -3.00167 | -4.00167 | -5.00167 |  |  |

| 4                            | -0.10167               | -1.00167      | -2.00167 | -3.00167 | -4.00167 | -5.00167 |  |  |

| 4.2                          | -0.10167               | -1.00167      | -2.00167 | -3.00167 | -4.00167 | -5.00167 |  |  |

| ERROR (%FSR)                 | 0.02083                | 0.02083       | 0.02083  | 0.02083  | 0.02083  | 0.02083  |  |  |

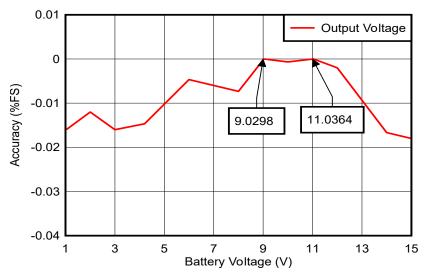

#### 4.4.2 Voltage Control Accuracy

Figure 4-7. Voltage Loop Linearity Test

Different current drawn from the load can also affect the CV control accuracy, a CV load regulation test is required. Table 4-3 shows the variation of constant current settings with respect to load voltage regulation. The data has minimal difference with the change in current.

| FS (V)                       | 15               |          |         |         |          |         |  |

|------------------------------|------------------|----------|---------|---------|----------|---------|--|

| V <sub>SET</sub> (V)         | 1                | 2        | 3       | 4.2     | 8        | 15      |  |

| CC MODE I <sub>SET</sub> (A) | LOAD VOLTAGE (V) |          |         |         |          |         |  |

| 0.1                          | 0.997423         | 1.99792  | 2.99827 | 4.19865 | 7.99858  | 14.9975 |  |

| 1                            | 0.99751          | 1.998    | 2.99835 | 4.1987  | 7.9987   | 14.9977 |  |

| 2                            | 0.99769          | 1.99819  | 2.99853 | 4.19888 | 7.99891  | 14.9978 |  |

| 4                            | 0.99801          | 1.99853  | 2.99886 | 4.19923 | 7.99929  | 14.9981 |  |

| 6                            | 0.998378         | 1.99887  | 2.99922 | 4.19957 | 7.9997   | 14.9984 |  |

| 7                            | 0.99855          | 1.99904  | 2.99941 | 4.19965 | 7.99978  | 14.9985 |  |

| ERROR (%FS)                  | 0.011533         | 0.013867 | 0.01153 | 0.009   | 0.009467 | 0.01667 |  |

#### Table 4-3. Voltage Regulation Under Different Currents

## 4.4.3 CC, CV Transformation

The complete battery formation profile includes both CC and CV control. The CC and CV transformation ought to be smooth to perform this task. Figure 4-8 and Figure 4-9 show the transition from CC mode to CV mode under different current settings, in both charge and discharge mode.

Figure 4-8. CC CV Charge Transformation Under Different Current Setting

Figure 4-9. CC CV Discharge Transformation Under Different Current Setting

#### 4.4.4 Constant Current Transient Response

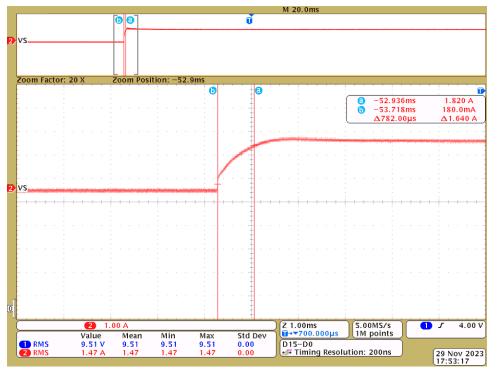

Figure 4-10 shows the current transition from 180mA to 1.82A, with the rise time being less than 1ms. The test was done by using an e-load to draw current for the circuit in CV condition. The result demonstrates smooth current transition, fast settling time, and stable current loop response.

Figure 4-10. Transient Response at Current Transition

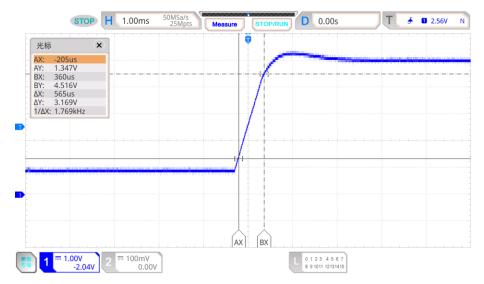

#### 4.4.5 Constant Voltage Transient Response

Figure 4-11. Transient Response at Voltage Transition

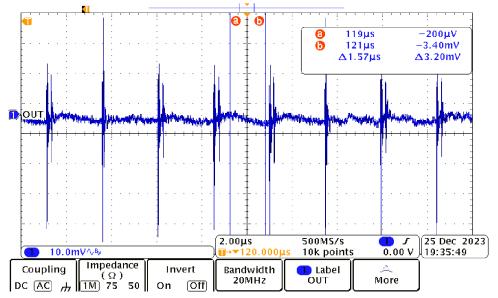

### 4.4.6 Voltage Ripple at Short Circuit

The voltage ripple is observed under short-circuit conditions. The test is performed under AC coupling with 10 × probe connected to the output capacitor of the linear stage subsystem. The ripple is approximately 3mV peak to peak.

Figure 4-12. Voltage Ripple Under Short-Circuit Conditions

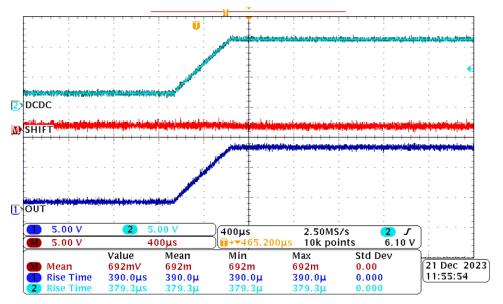

#### 4.4.7 Tracking DC-DC output

The voltage tracking circuit provides constant headroom in the linear power stage. Figure 4-13 shows when the DC-DC power supply tracking the linear stage output, providing constant headroom.

Figure 4-13. Tracking DC-DC Signal (SHIFT)

# **5** Design and Documentation Support

# 5.1 Design Files

#### 5.1.1 Schematics

To download the schematics, see the design files at TIDA-010089.

### 5.1.2 BOM

To download the bill of materials (BOM), see the design files at TIDA-010089.

### 5.2 Tools and Software

USB2ANY USB2ANY interface adapter

### **5.3 Documentation Support**

- 1. Texas Instruments, DACx0502, Dual, 16-Bit, 14-Bit, and 12-Bit, 1-LSB INL, Voltage-Output DACs With Precision Internal Reference Data Sheet

- 2. Texas Instruments, *LM5146 100V Synchronous Buck DC/DC Controller With Wide Duty Cycle Range Data Sheet*

- 3. Texas Instruments, INA818 35µV Offset, 8nV/\Hz Noise, Low-Power, Precision Instrumentation Amplifier Data Sheet

### **5.4 Support Resources**

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 5.5 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments. All trademarks are the property of their respective owners.

### 6 About the Author

**SHAURY ANAND** is a systems engineer at Texas Instruments, where he is responsible for developing reference designs for Test and Measurement applications. Shaury earned his bachelor's degree (B.Tech) in electrical engineering from the Indian Institute of Technology, Roorkee.

**ETHAN YU** is a systems engineer at Texas Instruments, where he is responsible for developing reference designs for Test and Measurement applications. Ethan earned his bachelor of science degree in electrical engineering from Texas A&M University.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated