TI Designs: TIDA-01081

# LED Lighting Control Reference Design for Machine Vision

# Description

This LED lighting control reference design demonstrates a unique approach to drive and control a string of multiple high-power light-emitting diodes (LEDs). This reference design is targeted for industrial machine vision systems and is also suitable for other industrial or automotive lighting applications. The design allows users to program LED current and timing to enable the safe overdriving of LEDs for increased brightness. The design can operate autonomously but can also be triggered or generate a trigger through an isolated interface. Internal circuit blocks support a wide input voltage range, a programmable input current, and input power control as well as protect against reverse polarity, overvoltage, and overtemperature.

#### Resources

#### **Design Folder**

#### TIDA-01081

#### **Product Folders**

| TPS92515HV   | TPS92561    | TPS26602    | LM5165     |

|--------------|-------------|-------------|------------|

| DAC082S085   | REF3025     | INA169      | DAC7311    |

| MSP430F5172  | ISOW7842    | LP5907      | TPS22810   |

| TPS7A4101    | UCC27511    | TLV3201     | TMP116     |

| SN74LVC1G175 | SN74LVC1G02 | CSD18543Q3A | CSD15380F3 |

| SN74LVC1G17  | SN74LVC1G14 | TPD1E10B06  |            |

ASK Our E2E™ Experts

#### **Features**

- LED String Voltage up to 24 V

- Programmability of Multiple Parameters:

- LED Current: 200 mA to 2.4 A

- LED Mode: Continuous or Pulsed 200 ns to 4.9

- LED Pulse Repetition: 0.2 Hz to 10 kHz

- Trigger Delay Time: 10 µs for Trigger Input

- Multi-Pulse Time, and Current Bracketing to Support AEB and HDR Imaging

- Cascaded Dual Power Stages:

- Pre-Boost: Wide 8 V to 36 V, 15-W System Input With Adaptive Inductor Current Limit

- Buck: Fast Inductor Current Ramping

- Isolated Trigger and UART Interface:

- Isolated 5-V, 50-mA Output

- Sinking NPN- and TTL Trigger IN and OUT

- eFuse: Reverse Protection, Adaptive Overcurrent Limit, and Input Power Limit

- Comprehensive System Supervision and Protection:

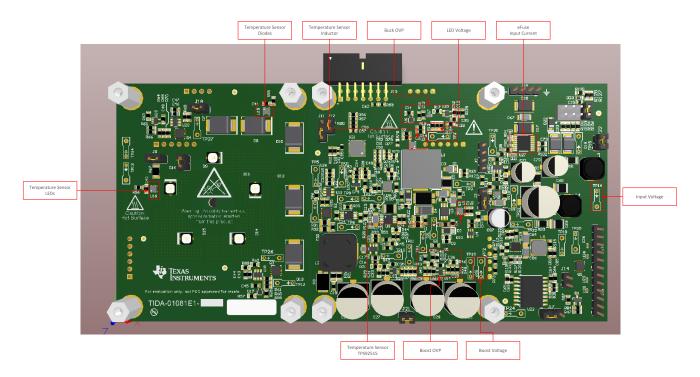

- **Onboard Temperature Sensors** and Voltage Supervision

- Ultra-Fast Output Overvoltage Protection

- EEPROM for up to 256 Bits of User Data

## **Applications**

- Machine Vision and Logistics:

- Lighting and Illumination

- **Solutions**

- Cameras

- · Code Readers

- · Barcode Scanners

- **Industrial Lighting**

- **Automotive Lighting**

System Description www.ti.com

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

# **CAUTION:**

Do not leave this reference design powered when unattended.

# **HOT SURFACE:**

Contact may cause burns. Do not touch. Take the proper precautions when operating.

## **LED Safety Guidelines**

## **CAUTION**

Retinal blue light or thermal hazard = 400-nm to 780-nm wavelength.

The high-power LEDs used and controlled in this reference design are in excess of the LED Exempt Risk Group. The viewer-related risk is dependent upon how the user installs and uses this reference design.

LEDs contained on this board are Risk Group 2, and reduce to Risk Group 1 at a distance > 0.5 m. To minimize risk of eye injury, never stare at operating LEDs as may be harmful to the eyes.

www.ti.com System Description

# **WARNING**

To minimize risk of eye injury, do not remove LED cover plate.

Intense light sources have a high secondary blinding effect. A temporary reduction in visual acuity and afterimages can occur, leading to irritation, annoyance, visual impairment, and even accidents—depending on the situation.

Always consider the use of light filtering and darkening protective eye wear and be fully aware of surrounding laboratory type setups when viewing intense light sources to minimize or eliminate such risks to avoid accidents related to temporary blindness.

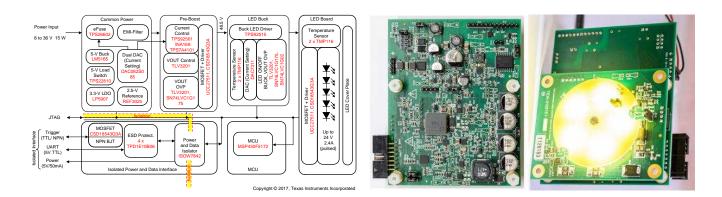

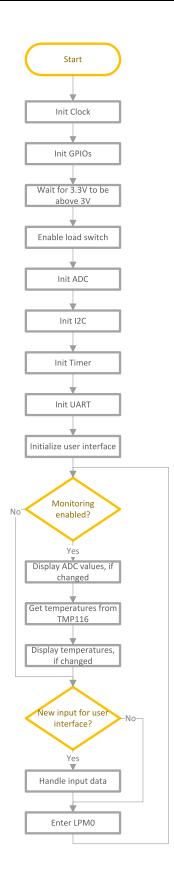

This reference design is designed with the requirements of machine vision applications for factory automation and logistics in mind. Machine vision has proven itself as a key technology, addressing the needs of automated manufacturing, including inspection, identification, quality control and logistics. The illumination solution and lighting control of machine vision systems play a major role to meet the challenging requirements of modern imaging solutions regarding increased production speed and effectiveness. The illumination and lighting control applications can be found as separate end equipment, but can be also found as integrated parts of cameras, code readers, or barcode scanners.

These applications have common requirements such as:

- Using high-power LEDs as a source of light

- Programmable LED current as a direct measure of light brightness, including a safe overdriving of the LEDs during pulsed operation with short LED ON-times

- Precise timing control, including autonomous and synchronized (externally triggered) operation with short trigger delay time

- Continuous ON as well as pulsed operation of the LEDs

- Support of LED ON-times down to the µs range to avoid or reduce motion blurs (this includes ultra-fast ramping up or down of the LED current)

- Pulse repetition frequencies up to 1 kHz or above to support the frame rate requirements of high-speed imaging

- Wide supply input voltage range, supporting standard 24-V power sources as found in industrial applications, but also other standard voltages like 12 V or 15 V

This reference design for LED lighting control reflects the market trend of using high-power LEDs as the light source. The design demonstrates how to drive those LEDs with a programmable constant current up to 2.4 A provided by a dedicated buck LED driver. A strobe repetition frequency (frame rate) of up to 10 kHz and a configurable pulse width down to 200 ns match the requirements of light sources needed for high-speed imaging. A digital-to-analog converter (DAC) is used to set the output current of the *LED buck*. The output voltage of the LED buck and the temperature of the buck LED driver as well as the buck inductor are supervised to protect against overvoltage and overtemperature. Each of the used temperature sensors offer 64 bits of user programmable EEPROM, which allows the user to save and read data for board identification, configuration, parameter sets, or other purposes.

A *pre-boost* converter enables operation over an 8-V to 36-V input voltage range. This wide input voltage range ensures that this reference design can use 12-V, 15-V, or 24-V power supplies as input power source. The pre-boost provides a regulated 48.5-V output, serving as the input for the downstream LED buck. The output of the pre-boost is supervised by a dedicated overvoltage protection (OVP) circuitry.

System Description www.ti.com

The pre-boost is equipped with an adaptive average input current limit and an energy storing bank of output capacitors. Those two features together avoid overloading of the input power source of the reference design while enabling a much higher instantaneous power level to drive the LEDs. The adaptive average input current limit of the pre-boost results in an 8-W to 10-W input power limit while the LEDs are driven with a peak pulse power of up to 40 W in the exemplary case of this reference design.

The *common power* block of the design uses an eFuse as a second level of a smart input current and input power limit. The input current limit of the reference design can be a selectable fixed value or to be adaptive to the output voltage of the input power source. The adaptive option limits the reference design's input power to a range of 12 W to 15 W, which avoids the need for oversized power supplies. The common power block contains further a 5-V buck and load switch, a 3.3-V LDO, and a 2.5-V reference, providing the needed point-of-load rails as well as their sequencing. The dual DAC of the common power block controls the adaptive current limit of the eFuse and of the pre-boost.

The reference design uses an exemplary string of five white high-power LEDs on a separate *LED board* for the purpose of demonstrating the feature set of the design. The need for ultra-fast ON- and OFF-switching of the LEDs is addressed by separate MOSFETs and their driver circuits on the LED board.

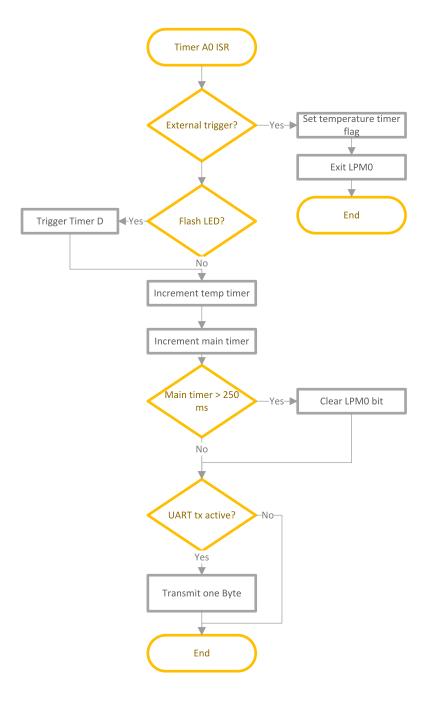

The *MCU* block of the reference design controls the ON- and OFF-timing of the LEDs and the value of the LED current. This flexible control allows the user to set up this reference design to generate single pulses as well as multiple pulses (burst) with an identical pulse width or with a progressively rising pulse width. The reference design can also demonstrate how a sequence of pulses with changing intensity can be generated. The latter two features are a pre-requisite to enable automatic exposure bracketing (AEB) and high dynamic range (HDR) imaging.

The MCU block interfaces furthermore with the eFuse and pre-boost, controls the sequencing of the 5-V rails, and monitors important system voltages and currents as well as the temperature data and content of the total 256 bits of general purpose EEPROM provided by the four temperature sensors.

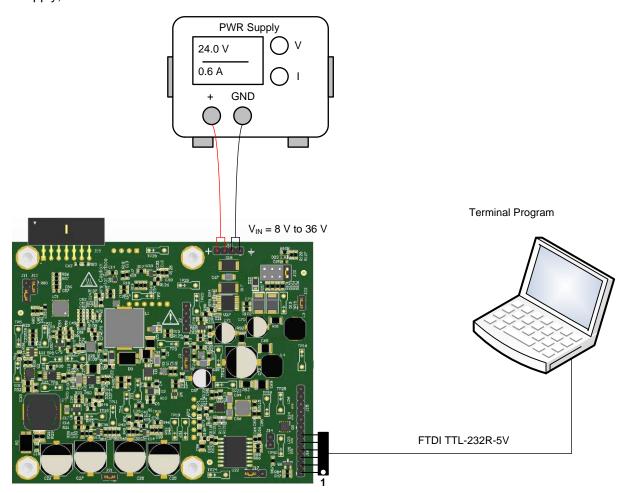

The reference design features an *isolated power and data interface* to enable trouble-free communication with a notebook or PC and triggering from external sources. The isolated UART interface supports configuration, monitoring and control of the design through a simple terminal software. The isolated interface provides furthermore an isolated 5-V rail, which can be loaded with up to 50 mA.

Besides its use in machine vision and logistics applications, the different blocks of this reference designs can also be adapted and modified for usage in industrial and automotive lighting applications.

www.ti.com System Description

# 1.1 Key System Specifications

**Table 1. Key System Specifications**

| PARAMETER                                | SPECIFICATIONS                                                                                                                             | DETAILS              |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| POWER INPUT                              |                                                                                                                                            |                      |  |  |

| Input voltage                            | 8 V to 36 V                                                                                                                                | _                    |  |  |

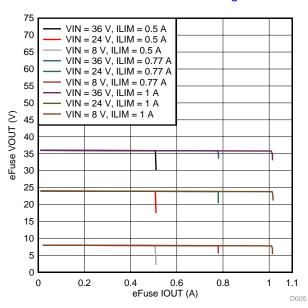

| eFuse current limit                      | Selectable:<br>500 mA , 770 mA, 1 A<br>Adaptive to provided input voltage to limit input power to 15<br>W for input voltage of 8 V to 36 V | Section 2.4.1.5      |  |  |

| LED OUTPUT                               |                                                                                                                                            |                      |  |  |

| LED string voltage                       | Up to 24 V                                                                                                                                 |                      |  |  |

| Average LED current (brightness control) | 200 mA to 2.4 A<br>Programmable in steps of 50 mA                                                                                          | Section 2.4.1.1      |  |  |

| Pulse width                              | 200 ns to 4.9 s; programmable                                                                                                              |                      |  |  |

| Pulse rise- and fall-time                | < 40 to 100 ns; depends on LED current                                                                                                     | Section 3.1.2.1      |  |  |

| Maximum duty cycle                       | 1% to 100%; programmable; depends on LED current                                                                                           | Section 3.1.2.1      |  |  |

| Pulse repetition frequency (frame rate)  | 0.2 Hz to 10 kHz; programmable                                                                                                             |                      |  |  |

| ISOLATED TRIGGER INTERFACE               |                                                                                                                                            |                      |  |  |

| Isolated power output                    | 5 V / 50 mA                                                                                                                                |                      |  |  |

| Isolated trigger input                   | Trigger delay time: 10 μs<br>Inverting TTL-IN<br>Non-inverting NPN-Sourcing-IN (pullup resistor)                                           |                      |  |  |

| Isolated trigger output                  | Delay time: –6.5 µs Non-inverting TTL-OUT Inverting NPN-Sinking-OUT (open drain output)                                                    | Section 2.4.1.6      |  |  |

| Isolated UART                            | TTL-IN (RXD)<br>TTL-OUT (TXD)                                                                                                              |                      |  |  |

| MODES OF OPERATION                       |                                                                                                                                            |                      |  |  |

| Continuous                               |                                                                                                                                            |                      |  |  |

| Pulsed                                   |                                                                                                                                            |                      |  |  |

| Externally triggered                     |                                                                                                                                            | For combinations and |  |  |

| Standalone (internally triggered)        |                                                                                                                                            | limitations, see     |  |  |

| Switched                                 | Section 3                                                                                                                                  |                      |  |  |

| Multi-pulsed                             |                                                                                                                                            |                      |  |  |

| Automatic exposure bracketing (AEB)      |                                                                                                                                            |                      |  |  |

# 2 System Overview

# 2.1 Block Diagram

Figure 1. TIDA-01081 Block Diagram

# 2.2 Highlighted Products

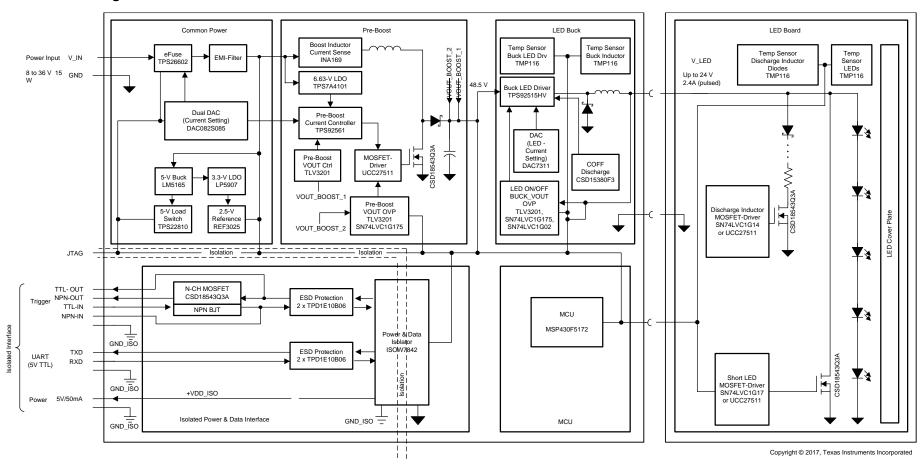

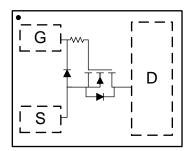

#### 2.2.1 TPS92515HV

The TPS92515HV is a compact, monolithic switching regulator integrating a low resistance N-Channel MOSFET. The device is intended for high-brightness LED lighting applications where efficiency, high bandwidth, PWM, analog dimming, and small size are important. The regulator operates using a constant off-time, peak current control. After an off-time based on the output voltage, an on-time begins. The on-time ends once the inductor peak current threshold is reached. The TPS92515HV can be configured to maintain a constant peak-to-peak ripple during the ON and OFF periods of a shunt FET dimming cycle. This constant peak-to-peak ripple is ideal for maintaining a linear response across the entire shunt FET dimming range. Steady-state accuracy is aided by the inclusion of a low-offset, high-side comparator. LED current can be modulated using either analog or PWM dimming, or both simultaneously. Other features include undervoltage lockout (UVLO), wide input voltage operation, inherent LED open operation, and a wide operating temperature range with thermal shutdown. The TPS92515HV offers a high input voltage range of up to 65 V. The device is available in a thermally enhanced 10-pin HVSSOP package.

Figure 2. Functional Block Diagram of TPS92515HV

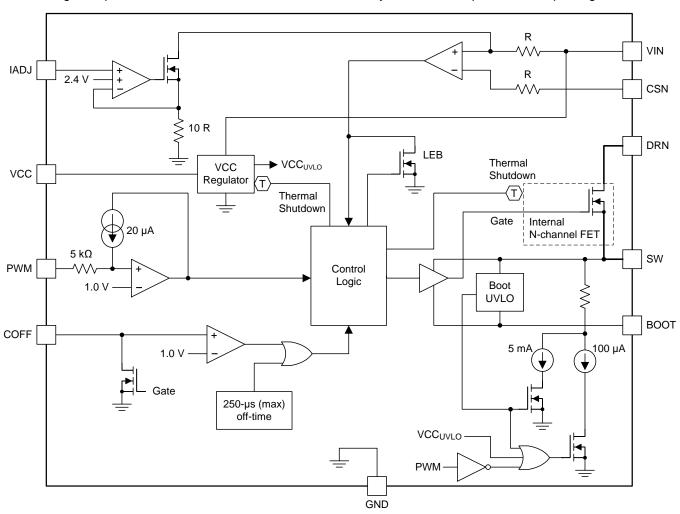

## 2.2.2 TPS92561

The TPS92561 device is a boost controller for LED lighting applications using high-voltage, low-current LEDs. A boost converter approach to lighting applications allows the creation of the smallest volume converter possible and enables high efficiencies beyond 90%. The device incorporates a current sense comparator with a fixed offset enabling a simple hysteretic control scheme free of the loop compensation issues typically associated with a boost converter. The integrated OVP and VCC regulator further simplify the design procedure and reduce external component count.

Figure 3. Functional Block Diagram of TPS92561

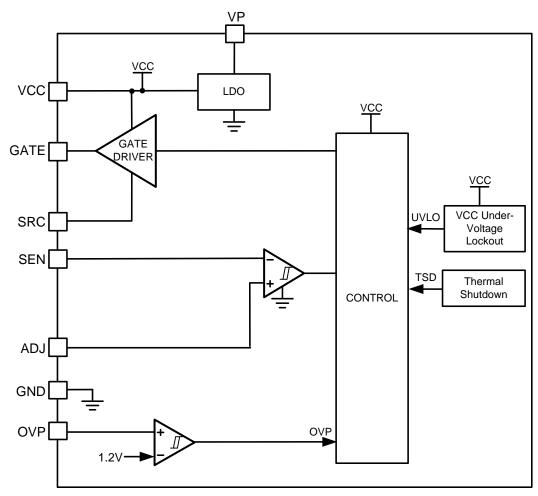

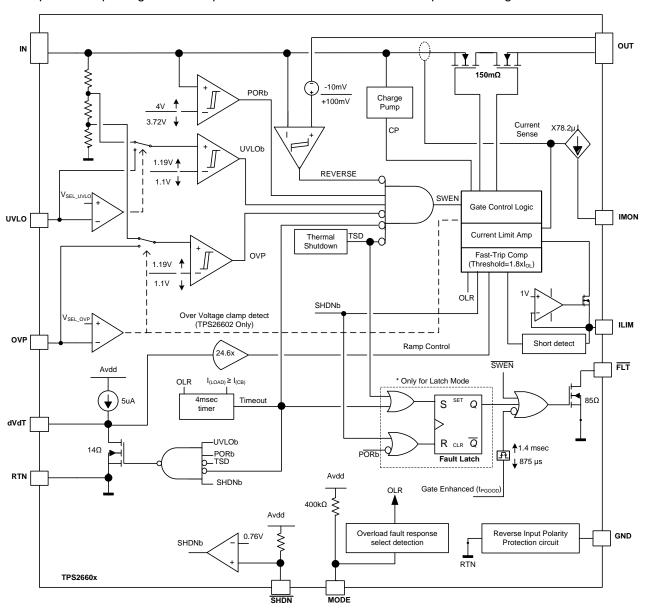

## 2.2.3 TPS26602

The TPS26602 device is a compact and feature rich high-voltage eFuse with a full suite of protection features. The wide supply input range of 4.2 V to 55 V allows the device to control many popular DC bus voltages. The device can withstand and protect the loads from positive and negative supply voltages up to ±60 V. Integrated back-to-back FETs provide a reverse current blocking feature, making the device suitable for systems with output voltage holdup requirements during power fail and brownout conditions. Load, source, and device protections are provided with many adjustable features including overcurrent, output slew rate, and overvoltage and undervoltage thresholds. The internal robust protection control blocks along with the high-voltage rating of the TPS26602 help simplify the system designs for surge protection. A shutdown pin provides external control for enabling and disabling the internal FETs as well as placing the device in a low-current shutdown mode. To monitor system status and downstream load control, the device provides fault and precise current monitor output. The MODE pin allows flexibility to configure the device between the three current-limiting fault responses (circuit breaker, latch off, and auto-retry modes). The devices are available in a 5-mm × 4.4-mm 16-pin HTSSOP as well as 5-mm × 4-mm 24-pin VQFN package and are specified over a -40°C to +125°C temperature range.

Figure 4. Functional Block Diagram of TPS2660x

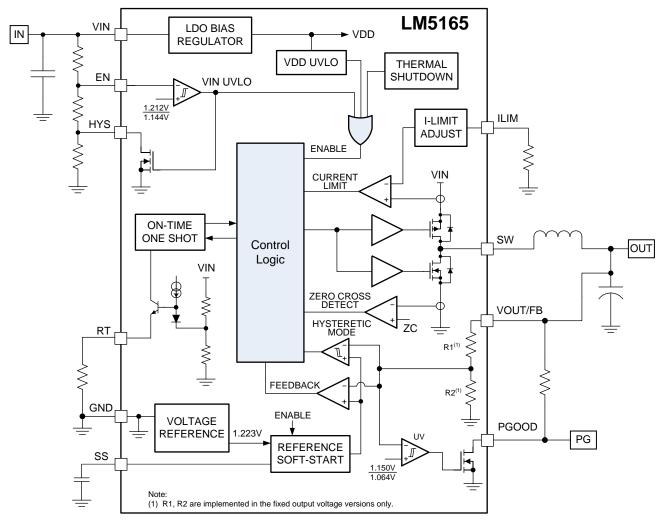

#### 2.2.4 LM5165

The LM5165 device is a compact, easy-to-use, 3-V to 65-V, ultra-low  $I_{\rm Q}$  synchronous buck converter with high efficiency over wide input voltage and load current ranges. With integrated high-side and low-side power MOSFETs, up to 150 mA of output current can be delivered at fixed output voltages of 3.3 V or 5 V or at an adjustable output. The converter is designed to simplify implementation while providing options to optimize the performance for the target application. Pulse frequency modulation (PFM) mode is selected for optimal light-load efficiency or constant on-time (COT) control for nearly constant operating frequency. Both control schemes do not require loop compensation while providing excellent line and load transient response and short PWM on-time for large step-down conversion ratios. The high-side P-channel MOSFET can operate at a 100% duty cycle for lowest dropout voltage and does not require a bootstrap capacitor for the gate drive. Also, the current limit setpoint is adjustable to optimize the inductor selection for a particular output current requirement. Selectable and adjustable start-up timing options include minimum delay (no soft start), internally fixed (900  $\mu$ s), and externally programmable soft start using a capacitor. An open-drain PGOOD indicator can be used for sequencing, fault reporting, and output voltage monitoring. The LM5165 buck converter is available in a 10-pin, 3-mm × 3-mm, thermally-enhanced VSON-10 package with a 0.5-mm pin pitch.

Figure 5. Functional Block Diagram of LM5165

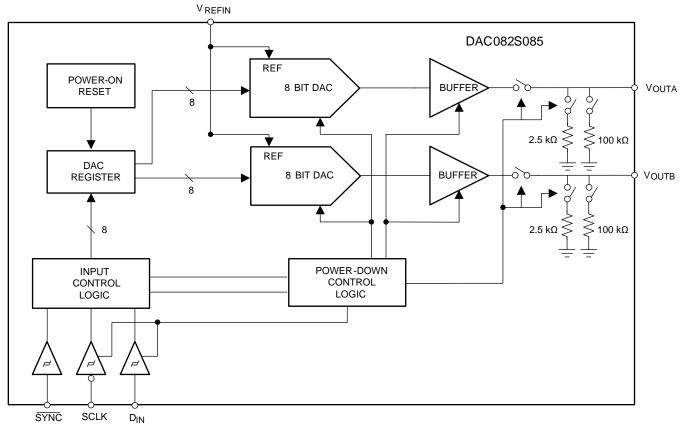

## 2.2.5 DAC082S085

The DAC082S085 device is a full-featured, general-purpose, dual, 8-bit, voltage-output DAC that can operate from a single 2.7-V to 5.5-V supply and consume 0.6 mW at 3 V and 1.6 mW at 5 V. The DAC082S085 is packaged in 10-pin SON and VSSOP packages. The 10-pin WSON package makes the DAC082S085 the smallest dual DAC in its class. The on-chip output amplifier allows rail-to-rail output swing, and the three-wire serial interface operates at clock rates up to 40 MHz over the entire supply voltage range. Competitive devices are limited to 25-MHz clock rates at supply voltages in the 2.7-V to 3.6-V range. The serial interface is compatible with standard SPI<sup>™</sup>, QSPI<sup>™</sup>, MICROWIRE, and DSP interfaces.

Copyright © 2016, Texas Instruments Incorporated

Figure 6. Functional Block Diagram of DAC082S085

## 2.2.6 REF3025

The REF3025 is a precision, low-power, low dropout voltage reference available in a tiny SOT-23-3 package. The REF3025 offers excellent temperature drift and initial accuracy while operating at a quiescent current of 42  $\mu$ A (typical). The low power consumption and the relatively high precision make the REF3025 very attractive for loop-powered industrial applications such as pressure and temperature transmitter applications. The REF3025 is easy to use in intrinsically safe and explosion-proof applications because it does not require a load capacitor to be stable. The REF3025 is specified over the extended industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. The REF3025 operates with supplies within 1 mV of output voltage under zero-load conditions. The low dropout along with small size and low power consumption make The REF3025 ideal for portable and battery-powered applications.

Copyright © 2016, Texas Instruments Incorporated

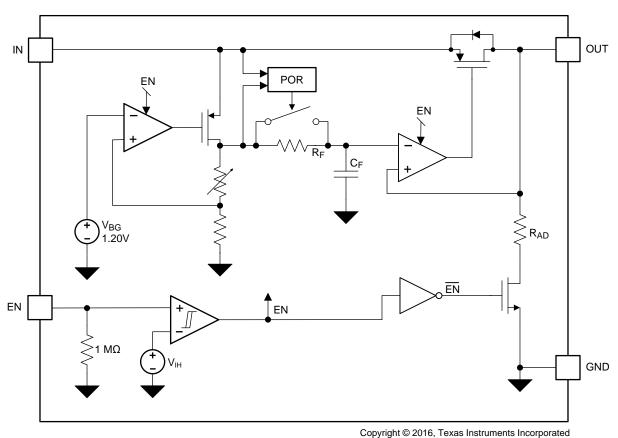

Figure 7. Functional Block Diagram of REF3025

## 2.2.7 INA169

The INA169 is a high-side, unipolar, current shunt monitor. Its wide input common-mode voltage range, high speed, low quiescent current, and tiny SOT-23 packaging enable use in a variety of applications. Input common-mode and power supply voltages are independent and can range from 2.7 V to 60 V for the INA169. The quiescent current of the device is only 60  $\mu$ A, which permits connecting the power supply to either side of the current measurement shunt with minimal error. The device converts a differential input voltage to a current output. This current is converted back to a voltage with an external load resistor that sets any gain from 1 to over 100. Although designed for current shunt measurement, the circuit invites creative applications in measurement and level shifting. The INA169 is available in a 5-pin SOT-23 package. The INA169 is specified from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Copyright © 2017, Texas Instruments Incorporated

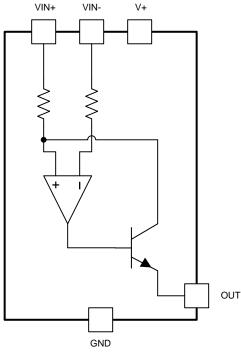

Figure 8. Functional Block Diagram of INA169

## 2.2.8 DAC7311

The DAC7311 (12-bit) device is a low-power, single-channel, voltage output DAC. The low power consumption of this device in normal operation (0.55 mW at 5 V, reducing to 2.5  $\mu$ W in power-down mode) makes it ideally suited for portable, battery-operated applications. This DAC is monotonic by design, provides excellent linearity, and minimizes undesired code-to-code transient voltages while offering an easy upgrade path within a pin-compatible family. This device uses a versatile, three-wire serial interface that operates at clock rates of up to 50 MHz and is compatible with standard SPI, QSPI, Microwire, and digital signal processor (DSP) interfaces. The DAC7311 uses an external power supply as a reference voltage to set the output range. The device incorporates a power-on reset (POR) circuit that ensures the DAC output powers up at 0 V and remains there until a valid write to the device occurs. The DAC7311 contains a power-down feature, accessed over the serial interface, that reduces current consumption of the device to 0.1  $\mu$ A at 2.0 V in power-down mode. This device is pin-compatible with the DAC8311 and DAC8411, offering an easy upgrade path from 8-, 10-, and 12-bit resolution to 14- and 16-bit. The DAC7311 is available in a small, 6-pin, SC70 (SOT) package. This package offers a flexible, pin- and function-compatible, drop-in solution within the family over an extended temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

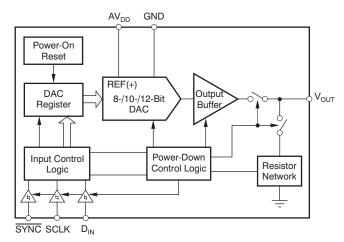

Figure 9. Functional Block Diagram of DAC7311

## 2.2.9 MSP430F5172

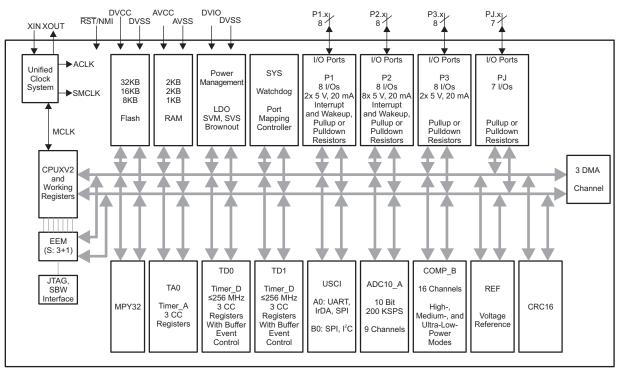

The TI MSP family of ultra-low-power microcontrollers (MCUs) consists of several devices featuring different sets of peripherals targeted for various applications. Combined with five low-power modes, the architecture is optimized to achieve extended battery life in portable measurement applications. The device features a powerful 16-bit RISC CPU, 16-bit registers, and constant generators that contribute to maximum code efficiency. The digitally controlled oscillator (DCO) allows the devices to wake up from low-power modes to active mode in less than 5 µs. The MSP430F5172 MCUs include two 16-bit high-resolution timers, two USCIs (USCI\_A0 and USCI\_B0), a 32-bit hardware multiplier, a high-performance 10-bit analog-to-digital converter (ADC), an on-chip comparator, a 3-channel DMA, 5-V tolerant I/Os, and up to 29 I/O pins. Typical applications for this device includes analog and digital sensor systems, LED lighting, digital power supplies, motor controls, remote controls, thermostats, digital timers, and handheld meters.

Copyright © 2017, Texas Instruments Incorporated

Figure 10. Functional Block Diagram of MSP430F5172

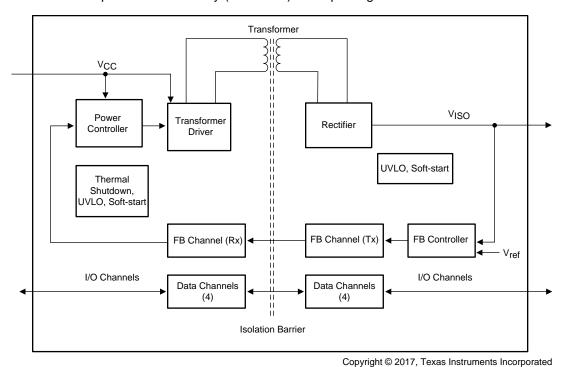

#### 2.2.10 ISOW7842

The ISOW7842 is a high-performance, quad-channel reinforced digital isolator with an integrated high-efficiency power converter. The integrated DC/DC converter provides up to 650 mW of isolated power at high efficiency and can be configured for various input and output voltage configurations. Therefore, this device eliminates the need for a separate isolated power supply in space-constrained isolated designs. The ISOW7842 device provides high electromagnetic immunity (EMI) and low emissions while isolating CMOS or LVCMOS digital I/Os. The signal-isolation channel has a logic input and output buffer separated by a silicon dioxide (SiO<sub>2</sub>) insulation barrier, whereas, power isolation uses on-chip transformers separated by thin film polymer as insulating material. Various configurations of forward and reverse channels are available. If the input signal is lost, the default output is high for the ISOW7842 and low for the devices with the F suffix. This device helps prevent noise currents on a data bus or other circuits from entering the local ground and interfering with or damaging sensitive circuitry. Through innovative chip design and layout techniques, electromagnetic compatibility of the ISOW7842 device has been significantly enhanced to ease system-level ESD, EFT, surge, and emissions compliance. The high-efficiency of the power converter allows operation at a higher ambient temperature. The ISOW7842 device is available in a 16-pin SOIC wide-body (SOIC-WB) DWE package.

Figure 11. Functional Block Diagram of ISOW784x

## 2.2.11 LP5907

The LP5907 is a low-noise LDO that can supply up to a 250-mA output current. Designed to meet the requirements of RF and analog circuits, the LP5907 device provides low noise, high PSRR, low quiescent current, and low line or load transient response figures. Using new innovative design techniques, the LP5907 offers class-leading noise performance without a noise bypass capacitor and the ability for remote output capacitor placement. The device is designed to work with a 1-µF input and a 1-µF output ceramic capacitor (no separate noise bypass capacitor is required). This device is available with fixed output voltages from 1.2 V to 4.5 V in 25-mV steps. Contact Texas Instruments Sales for specific voltage option needs.

Figure 12. Functional Block Diagram of LP5907

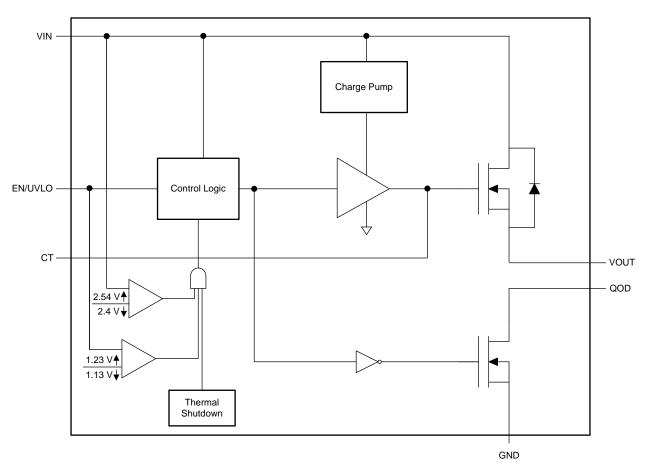

#### 2.2.12 TPS22810

The TPS22810 is a single-channel load switch with a configurable rise time and with an integrated quick output discharge (QOD). In addition, the device features thermal shutdown to protect the device against high junction temperature. Because of this, the safe operating area of the device is inherently ensured. The device contains an N-channel MOSFET that can operate over an input voltage range of 2.7 V to 18 V. A SOT23-5 (DBV) package can support a maximum current of 2 A. A WSON (DRV) package can support a maximum current of 3 A. The switch is controlled by an on and off input, which is capable of interfacing directly with low-voltage control signals. The configurable rise time of the device greatly reduces inrush current caused by large bulk load capacitances, thereby reducing or eliminating power supply droop. UVLO is used to turn off the device if the V<sub>IN</sub> voltage drops below a threshold value, ensuring that the downstream circuitry is not damaged by being supplied by a voltage lower than intended. The configurable QOD pin controls the fall time of the device to allow design flexibility for power down. The TPS22810 is available in a leaded, SOT-23 package (DBV), which allows to visually inspect solder joints as well as a WSON package (DRV). The device is characterized for operation over the free-air temperature range of -40°C to +105°C.

Copyright © 2016, Texas Instruments Incorporated

Figure 13. Functional Block Diagram of TPS22810

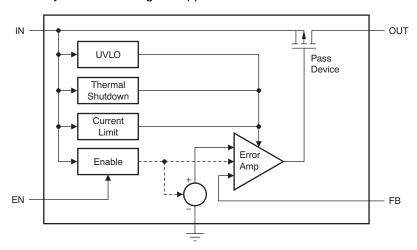

## 2.2.13 TPS7A4101

The TPS7A4101 device is a very high-voltage-tolerant linear regulator that offers the benefits of a thermally-enhanced package (MSOP-8) and is able to withstand continuous DC or transient input voltages of up to 50 V. The TPS7A4101 is stable with any output capacitance greater than 4.7  $\mu$ F and any input capacitance greater than 1  $\mu$ F (over temperature and tolerance). Thus, implementations of this device require minimal board space because of its miniaturized packaging (MSOP-8) and a potentially small output capacitor. In addition, the TPS7A4101 offers an enable pin (EN) compatible with standard CMOS logic to enable a low-current shutdown mode. The TPS7A4101 has an internal thermal shutdown and current limiting to protect the system during fault conditions. The MSOP-8 packages has an operating temperature range of  $T_J = -40^{\circ}$ C to +125°C. In addition, the TPS7A4101 is ideal for generating a low-voltage supply from intermediate voltage rails in telecom and industrial applications; not only can the device supply a well-regulated voltage rail, but it can also withstand and maintain regulation during very high and fast voltage transients. These features translate to a simpler and more cost-effective electrical surge-protection circuitry for a wide range of applications.

Figure 14. Functional Block Diagram of TPS7A4101

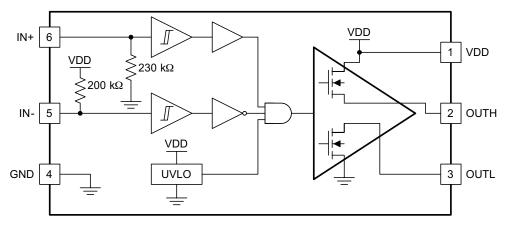

#### 2.2.14 UCC27511

The UCC27511 device is a single-channel, high-speed, low-side gate driver that can effectively drive MOSFET and IGBT power switches. Using a design that inherently minimizes shoot-through current, the UCC27511 is capable of sourcing and sinking high peak-current pulses into capacitive loads offering railto-rail drive capability and extremely small propagation delay, typically 13 ns. The UCC27511 features a dual-input design, which offers flexibility of implementing both inverting (IN- pin) and non-inverting (IN+ pin) configuration with the same device. Either the IN+ or IN- pin can be used to control the state of the driver output. The unused input pin can be used for enable and disable functions. For safety purposes, internal pullup and pulldown resistors on the input pins ensure that outputs are held low when input pins are in floating condition. Hence the unused input pin is not left floating and must be properly biased to ensure that driver output is in enabled for normal operation. The input pin threshold of the UCC27511 device is based on TTL and CMOS-compatible low-voltage logic, which is fixed and independent of the VDD supply voltage. Wide hysteresis between the high and low thresholds offers excellent noise immunity. The UCC27511 provides a 4-A source, 8-A sink (asymmetrical drive) peak-drive current capability. Strong sink capability in asymmetrical drive boosts immunity against parasitic, Miller turnon effect. The UCC27511 device also features a unique split output configuration where the gate drive current is sourced through OUTH pin and sunk through OUTL pin. This unique pin arrangement allows the user to apply independent turnon and turnoff resistors to the OUTH and OUTL pins, respectively, and easily control the switching slew rates. The UCC27511 device is designed to operate over a wide VDD range of 4.5 V to 18 V and a wide temperature range of -40°C to +140°C. The internal UVLO circuitry on the VDD pin holds output low outside the VDD operating range.

Figure 15. Functional Block Diagram of UCC27511

#### 2.2.15 TLV3201

The TLV3201 is a single-channel comparator that offers the ultimate combination of high speed (40 ns) and low-power consumption (40  $\mu$ A), all in an extremely small package with features such as rail-to-rail inputs, low offset voltage (1 mV), and large output drive current. The device is also very easy to implement in a wide variety of applications where response time is critical. The TLV3201 comparator is available with push-pull outputs. The TLV3201 is available in 5-pin SOT-23 and 5-pin SC70 packages. This devices is specified to operate across the expanded industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

Copyright © 2016, Texas Instruments Incorporated

Figure 16. Functional Block Diagram of TLV3201

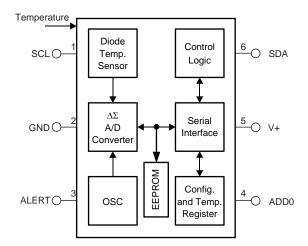

## 2.2.16 TMP116

The TMP116 (TMP116, TMP116N) is a family of low-power, high-precision temperature sensors with integrated EEPROM memory. The TMP116 provides a 16-bit temperature result with a resolution of  $0.0078^{\circ}$ C and an accuracy of up to  $\pm 0.2^{\circ}$ C with no calibration. The TMP116 is  $I^{2}$ C- and SMBus-interface compatible, has programmable alert functionality, and can support up to four devices on a single bus. In addition to providing power savings, the TMP116 consumes minimal current that minimizes self-heating and improves measurement accuracy. The TMP116 operates from 1.9 V to 5.5 V and typically consumes  $3.5~\mu$ A. Across the device operating temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C, the TMP116 exceeds the accuracy of a class A RTD, while consuming less than one fifth of the typical excitation current for a PT100 RTD. The TMP116 is easier to use than RTDs, eliminating the need for calibration, external circuitry, matched traces, and Kelvin connections. The TMP116 units are 100% tested on a production setup that is NIST traceable and verified with equipment that is calibrated to ISO and IEC 17025 accredited standards.

Figure 17. Functional Block Diagram of TMP116

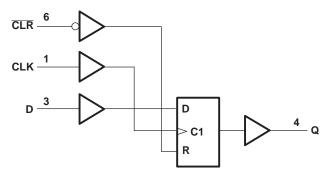

## 2.2.17 SN74LVC1G175

This single D-type flip-flop is designed for 1.65-V to 5.5-V VCC operation. The SN74LVC1G175 device has an asynchronous clear (CLR) input. When CLR is high, data from the input pin (D) is transferred to the output pin (Q) on the rising edge of the clock (CLK). When CLR is low, Q is forced into the low state, regardless of the clock edge or data on D. NanoFree™ package technology is a major breakthrough in device packaging concepts, using the die as the package.

This device is fully specified for partial-power-down applications using  $I_{OFF}$ . The  $I_{OFF}$  circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

Figure 18. Functional Block Diagram of SN74LVC1G175

Table 2. Function Table of SN74LVC1G175

| INPUTS |        |   | OUTPUT |

|--------|--------|---|--------|

| CLR    | CLK    | D | Q      |

| Н      | 1      | L | L      |

| Н      | 1      | Н | Н      |

| Н      | H or L | Х | $Q_0$  |

| L      | X      | X | L      |

#### 2.2.18 SN74LVC1G02

This single, two-input, positive-NOR gate is designed for a 1.65-V to 5.5-V VCC operation. The SN74LVC1G02 performs the Boolean function  $Y = \overline{A} + \overline{B}$  or  $Y = \overline{A} \times \overline{B}$  in positive logic. The CMOS device has high output drive while maintaining low static power dissipation over a broad VCC operating range. The SN74LVC1G02 device is available in a variety of packages, including the ultra-small DPW package with a body size of  $0.8 \times 0.8$  mm.

Figure 19. Functional Block Diagram of SN74LVC1G02

Table 3. Function Table of SN74LVC1G02

| INPUTS |   | OUTPUT |  |

|--------|---|--------|--|

| Α      | В | Y      |  |

| Н      | Х | L      |  |

| X      | Н | L      |  |

| L      | L | Н      |  |

## 2.2.19 SN74LVC1G17

This single Schmitt trigger buffer is designed for a 1.65-V to 5.5-V VCC operation. The SN74LVC1G17 device contains one buffer and performs the Boolean function Y = A. The CMOS device has high output drive while maintaining low static power dissipation over a broad VCC operating range. The SN74LVC1G17 is available in a variety of packages, including the ultra-small DPW package with a body size of 0.8 mm  $\times$  0.8 mm.

Figure 20. Functional Block Diagram of SN74LVC1G17

Table 4. Function Table of SN74LVC1G17

| INPUT<br>A | OUTPUT<br>Y |

|------------|-------------|

| Н          | Н           |

| L          | L           |

## 2.2.20 SN74LVC1G14

This single Schmitt-trigger inverter is designed for 1.65-V to 5.5-V VCC operation. The SN74LVC1G14 device contains one inverter and performs the Boolean function  $Y = \overline{A}$ . The device functions as an independent inverter, but because of Schmitt action, it may have different input threshold levels for positive-going (VT+) and negative-going (VT-) signals. NanoFree package technology is a major breakthrough in device packaging concepts, using the die as the package.

This device is fully specified for partial-power-down applications using  $I_{OFF}$ . The  $I_{OFF}$  circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

Figure 21. Functional Block Diagram of SN74LVC1G14 for Different Packages

## 2.2.21 CSD18543Q3A

This 60-V, 8.1-m $\Omega$ , SON 3.3-mm × 3.3-mm NexFET<sup>TM</sup> power MOSFET is designed to minimize losses in power conversion applications.

Figure 22. Top View of CSD18543Q3A

Table 5. Product Summary of CSD18543Q3A

| T <sub>A</sub> = 25°C |                               | TYPICAL VAL             | TYPICAL VALUE |                                         |

|-----------------------|-------------------------------|-------------------------|---------------|-----------------------------------------|

| V <sub>DS</sub>       | Drain-to-source voltage       | 60                      | 60            |                                         |

| Q <sub>g</sub>        | Gate charge total (10 V)      | 11.1                    | 11.1          |                                         |

| Q <sub>gd</sub>       | Gate charge gate-to-drain     | 1.7                     | 1.7           |                                         |

| В                     | Drain-to-source on resistance | V <sub>GS</sub> = 4.5 V | 12.0          | mΩ                                      |

| R <sub>DS(on)</sub>   |                               | V <sub>GS</sub> = 10 V  | 8.1           | 111111111111111111111111111111111111111 |

| V <sub>GS(th)</sub>   | Threshold voltage             | 2.0                     | 2.0           |                                         |

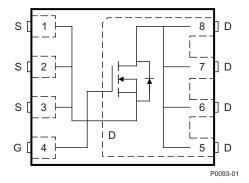

# 2.2.22 CSD15380F3

This 20-V, 990-mΩ, N-channel FemtoFET<sup>TM</sup> MOSFET is designed and optimized to minimize the footprint in many handheld and mobile applications. Ultra-low capacitance improves switching speeds. When used in data line applications, the low capacitance minimizes noise coupling. This technology is capable of replacing standard small-signal MOSFETs while providing a substantial reduction in footprint size.

Figure 23. Top View of CSD15380F3

Table 6. Product Summary of CSD15380F3

| T <sub>A</sub> = 25°C |                               | TYPICAL V               | TYPICAL VALUE |    |

|-----------------------|-------------------------------|-------------------------|---------------|----|

| $V_{DS}$              | Drain-to-source voltage       | 20                      | 20            |    |

| Q <sub>g</sub>        | Gate charge total (4.5 V)     | 0.216                   | 0.216         |    |

| $Q_{gd}$              | Gate charge gate-to-drain     | 0.027                   | 0.027         |    |

|                       |                               | V <sub>GS</sub> = 2.5 V | 2220          | mΩ |

| R <sub>DS(on)</sub>   | Drain-to-source on-resistance | V <sub>GS</sub> = 4.5 V | 1170          | mΩ |

|                       |                               | V <sub>GS</sub> = 8 V   | 990           | mΩ |

| V <sub>GS(th)</sub>   | Threshold voltage             | 1.1                     | 1.1           |    |

## 2.2.23 TPD1E10B06

The TPD1E10B06 device is a single-channel electrostatic discharge (ESD) transient voltage suppression (TVS) diode in a small 0402 package. This TVS protection product offers ±30-kV contact ESD, ±30-kV IEC air-gap protection, and has an ESD clamp circuit with a back-to-back TVS diode for bipolar or bidirectional signal support. The 12-pF line capacitance of this ESD protection diode is suitable for a wide range of applications supporting data rates up to 400 Mbps. The 0402 package is an industry standard and is convenient for component placement in space-saving applications.

Typical applications of this ESD protection product are circuit protection for audio lines (microphone, earphone, and speakerphone), SD interfacing, keypad or other buttons, VBUS pin and ID pin of USB ports, and general-purpose I/O ports. This ESD clamp is good for the protection of the end equipment like ebooks, tablets, remote controllers, wearables, set-top boxes, and electronic point of sale equipment.

Figure 24. Functional Block Diagram of TPD1E10B06

# 2.3 Design Considerations

Driving high-power LEDs with pulses of high current in a fast and accurate manner is known to be a design challenge. Designers are commonly confronted with limitations based on the basic laws of physics, component ratings, and environmental conditions.

This reference design provides an example on how to address some of these challenges in the hardware and software design. For more details, consult outside literature.

# 2.4 System Design Theory

#### 2.4.1 Hardware

## 2.4.1.1 LED Buck

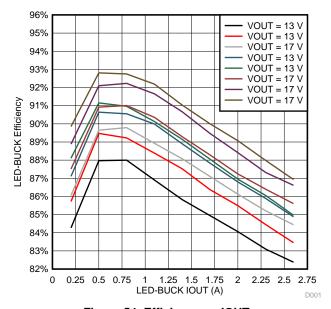

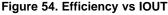

The LED buck is the core hardware block that directly influences the electrical characteristics of driving the LEDs. A switching regulator is selected to drive the string of five LEDs with a constant current of up to 2.4 A. Using this switching regulator has the clear advantage of less power dissipation compared to any linear regulator approach. This holds especially true when considering the huge variation in the LED string voltage over forward current, temperature, and binned forward voltage groups.

However, using a switching regulator introduces other burdens for the design, for example noise, ripple, complexity, and ability to fulfill the demanding dynamic requirements.

The buck topology is selected because it is the only topology out of the standard non-isolated topologies (buck, boost, inverting buck-boost, SEPIC) that ensures a continuous current flow through the load (LEDs) on its output, even without the need for an energy storing output capacitor. The buck topology eases furthermore the accurate control of its load (LEDs) current because this load current equals the inductor current of the buck.

Table 7 lists the challenges for the practical design of the specific LED buck.

**MEASURES TO ADDRESS DESIRED** ADDITIONAL OR ALTERNATIVE **FEATURES FEATURE MEASURES** L COUT FS VIN ILED: support short ON-times  $\downarrow$ 1 Start converter into shorted output, actively ILED: short rise, fall, or trigger delay times **↑** discharge inductor for switching LEDs off ILED: low ripple 1 1 1  $\downarrow$ Efficiency: high  $\downarrow$  $\downarrow$ Minimum ON-time limit of buck converter, **↑** 1  $\downarrow$ do not violate

Table 7. Challenges of LED Buck Design and Measures to Address Them

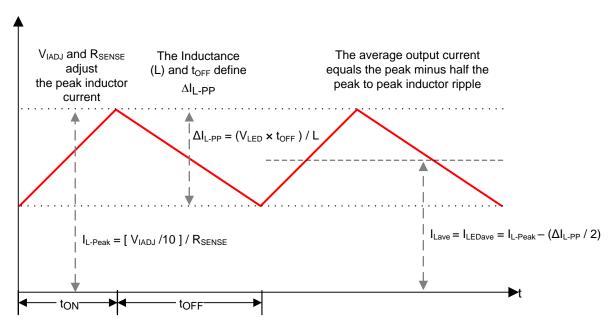

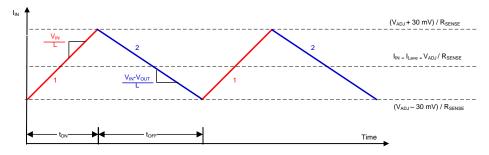

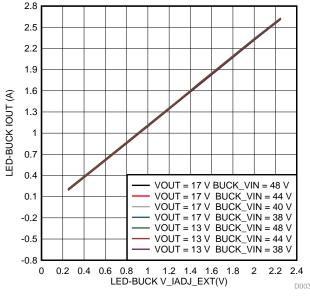

A dedicated buck LED driver, TPS92515HV  $^{\text{\tiny II}}$ , is chosen due to its integrated switching FET and its used constant off-time, peak-current control as shown in Figure 25. The principle of this special mode is based on two states dictating the high-side FET control. The switch turns on and stays on until the programmed peak current I<sub>L-Peak</sub> is reached. The peak current is controlled by monitoring the voltage across the sense resistor, R<sub>SENSE</sub>. When the voltage drop is higher than the programmed threshold (V<sub>IADJ</sub>/10), the peak current is reached, and the switch is turned OFF, which initiates the OFF-time period t<sub>OFF</sub>. The OFF-time is derived from the output voltage V<sub>IED</sub> to create a quasi-constant inductor ripple  $\Delta I_{I-PP}$ .

Equation 1 gives the ideal values for the average inductor current,  $I_{Lave}$ , and for the average LED current  $I_{LEDave}$ . Equation 1 is valid for positive integer numbers of switching periods only. Non-integer numbers of switching periods lead to a deviation from the ideal values. The resulting error is negligible for large numbers of switching periods (when the switching frequency of the buck LED driver >>  $1/LED_{on_time}$ ) and for  $I_{Lave} >> \Delta I_{L-PP}$ .

$$I_{Lave} = I_{LEDave} = \frac{\frac{V_{IADJ}}{10}}{R_{SENSE}} - \left(\frac{\Delta I_{L-PP}}{2}\right)$$

(1)

Figure 25. Principle of Hysteretic Operation: Constant Off-Time, Peak-Current Control

Furthermore, the TPS92515HV offers the advantage of a dedicated PWM dimming input to switch the buck instantaneously ON and OFF without the delay or soft-start phases found in other DC/DC converters and LED drivers.

The TPS92515HV provides additionally a specific IADJ input for setting the  $I_{L-Peak}$  threshold by an analog voltage  $V_{IADJ}$  applied to that input pin. This feature enables the control of the average inductor current  $I_{Lave}$  and therefore also the control of the average LED current  $I_{L-Peak}$ .

Although the hysteretic operation of the TPS92515HV allows a high control bandwidth, this reference design cannot fulfill the fast rise and fall time requirements for the LED current given in Table 1 based on the hysteretic operation alone. The buck inductor and its physical property of slowing down any change in current flow through the inductor is the reason for it. This challenge can be addressed in theory by reducing the inductor value or increasing the voltage  $V_L$  applied across the inductor. The former measure can be in conflict with the minimum on-time limits of the TPS92515HV as well as with the desired low ripple of the LED current.

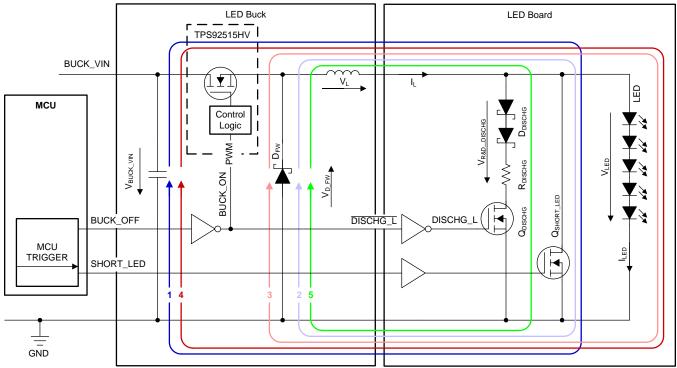

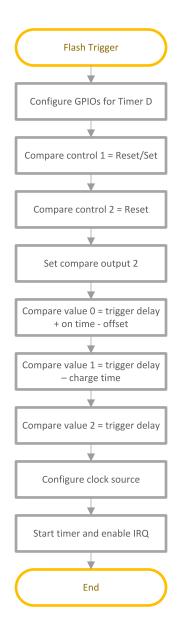

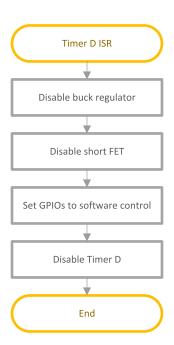

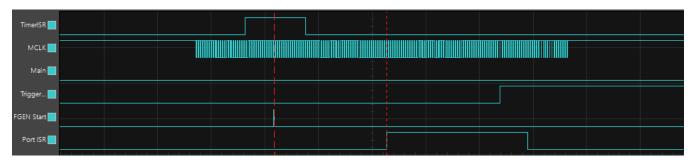

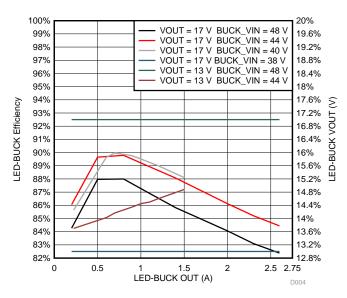

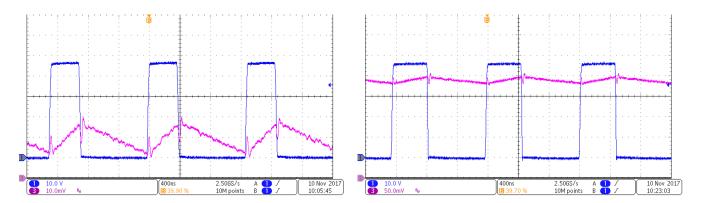

This reference design uses an innovative approach to optimize  $V_L$  and to achieve finally the required short timing requirements. Figure 26 shows the basic approach for the circuit as well as the path where the inductor current flows during the different states of operation.

Copyright © 2017, Texas Instruments Incorporated

Figure 26. Basic Schematic of LED Buck and LED Board

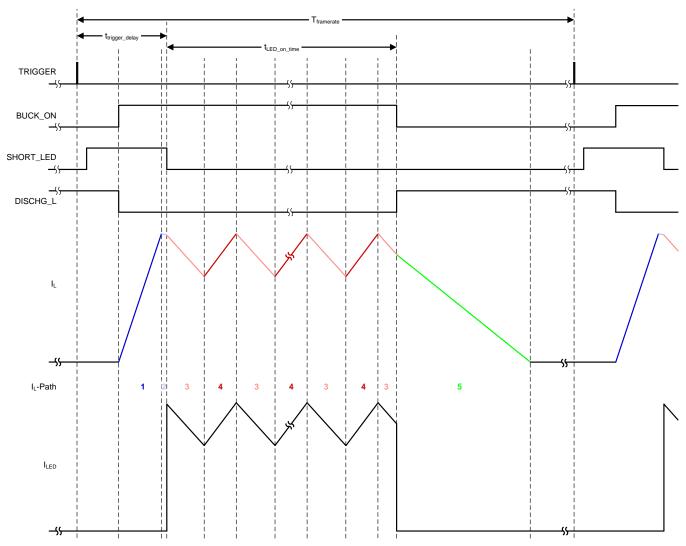

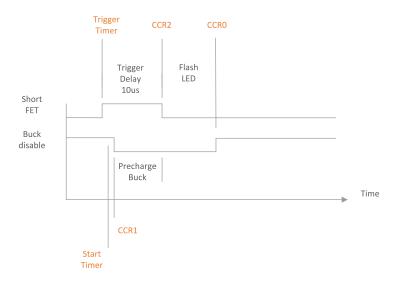

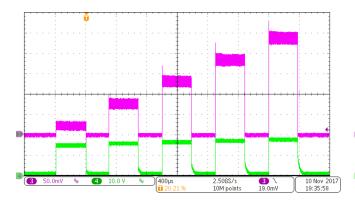

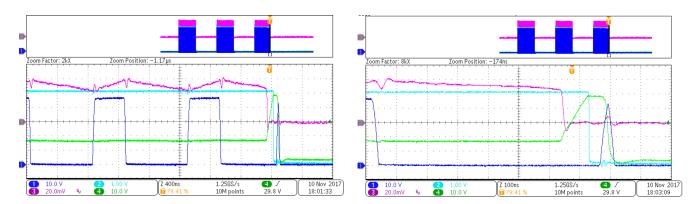

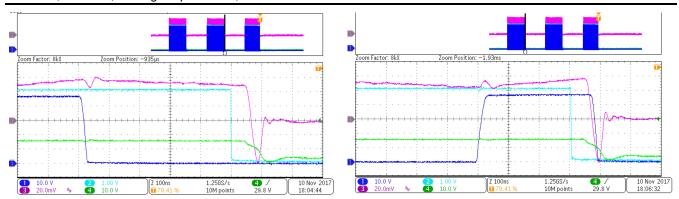

The basic circuit diagram is furthermore supplemented by the respective timing diagram provided in Figure 27. This timing diagram shows the most important details of the signals that control the timing of the LED buck as well as of the switches (MOSFETs) on the LED board. Figure 27 also illustrates the ideal waveforms for the inductor current of the LED buck and for the LED current I<sub>LED</sub>.

Figure 27. Timing Diagram of LED Buck and LED Board

Table 8 provides further specifics of the control and timing. This table not only describes each of the different states shown in the timing diagram, but also provides the ideal value for the voltage  $V_L$  applied across the inductor during each of the states. The larger the value of  $V_L$ , the faster the current through the inductor can change.

Table 8. Detailed Description of LED Buck and LED Board Control and Timing

| STATE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>L</sub>                                                                                                               |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Trigger | Interrupt, caused externally by isolated trigger input or internally by timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                              |

| 1       | Start of the buck LED driver (TPS92515HV) and precharge of its inductor to the $I_{L\text{-Peak}}$ corresponding to the configured "I LED" (see Table 9). Start of this state is initiated by MCU (BUCK_ON is going high and DISCHG_L is going low and is based on the desired $t_{trigger\_delay}$ (10 $\mu s$ ), the estimated precharge time (duration of state 1), and the time margin factored in (state 2). Output of buck is shorted by $Q_{SHORT\_LED}$ to maximize $V_L$ and to minimize the time needed for state 1. End of state 1 is controlled by buck LED driver (TPS92515HV) when $I_{L\text{-Peak}}$ threshold is hit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>BUCK_VIN</sub> (2)                                                                                                    |

| 2       | Time margin with freewheeling of I <sub>L</sub> (using Schottky diode D <sub>FW</sub> ) to factor in tolerances in precharging (state 1). State 2 starts automatically as soon as the buck LED driver stops state 1. Output of buck is still shorted by $Q_{\text{SHORT\_LED}}$ to minimize $V_L$ and to minimize the drop in I <sub>L</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $-V_{D_FW}$ (3)                                                                                                              |

| 3 and 4 | $t_{\text{LED\_on\_time}}$ is when the output of the buck is not longer shortened by $Q_{\text{SHORT\_LED}}$ and $l_{\text{L}}$ flows through the LEDs (as $l_{\text{LED}}$ ). Waveform and switching frequency of $l_{\text{LED}}$ are completely controlled by buck LED driver (TPS92515HV). Start of first falling slope of $l_{\text{LED}}$ is initiated by MCU control (SHORT_LED signal going low). First falling slope of $l_{\text{LED}}$ starts almost at the configured $l_{\text{L-Peak}}$ level due to the short time margin (state 2) and the minimized drop of $l_{\text{L}}$ during state 2. The MCU controls the end of $t_{\text{LED\_on\_time}}$ determined by the configured "On Time" parameter (see Table 9). As a result, the current flow through the LEDs can stop anytime during state 3 or state 4, leading to non-integer number of switching periods and causing a deviation of the resulting $l_{\text{LEDave}}$ from the ideal value calculated by Equation 1.                                                                                                                                    | Down-Slope (State 3): $-\left(V_{LED}+V_{D\_FW}\right) \tag{4}$ $Up\text{-Slope (State 4):}$ $V_{BUCK\_VIN}-V_{LED} \tag{5}$ |

| 5       | Inductor discharge state: to start any LED pulse (flash) from a know state of the circuit and to ensure that minimum ON-time limit of the buck LED driver (TPS92515HV) is not violated. The MCU stops operation of buck LED driver by driving the BUCK_ON signal to go low and the DISCHG_L signal to go high. The latter one switches $Q_{\mbox{\scriptsize DISCHG}}$ on and steers $I_{\mbox{\scriptsize L}}$ away from the LEDs towards the path through $D_{\mbox{\scriptsize DISCHG}}$ and $R_{\mbox{\scriptsize DISCHG}}$ . To be fast and effective the following condition needs to be fulfilled. $V_{\mbox{\scriptsize LED}} >> V_{\mbox{\scriptsize R\&D\_DISCHG}} >> 0 \ V \label{eq:VLED}$ This approach significantly increases the voltage across the inductor $V_{\mbox{\scriptsize L}}$ and decreases the time needed to completely discharge the inductor when compared to the standard freewheeling with the LEDs simply shortened as in state 2. A fast inductor discharge reduces the average power dissipation in the freewheeling diode and inductor compared to a pure shunt-FET dimming implementation. | -(V <sub>R&amp;D_DISCHG</sub> + V <sub>D_FW</sub> ) (7)                                                                      |

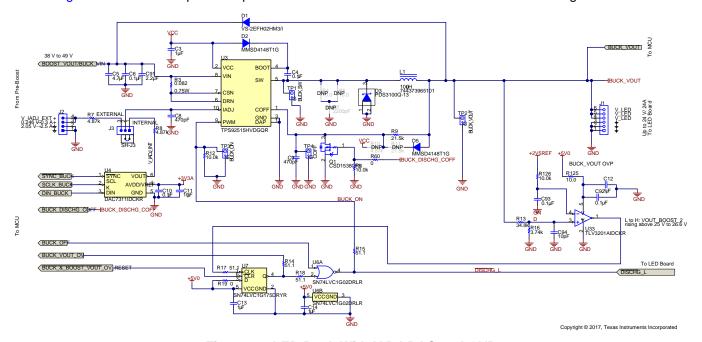

# 2.4.1.1.1 Specific Implementation of LED Buck

A maximized voltage  $V_L$  across the inductor is needed to obtain a fast change of the inductor current  $I_L$ . According to Table 8, a maximized input voltage for state 1 is required to meet the trigger delay time specification of 10  $\mu$ s, especially for the maximum LED current  $I_{LEDave}$  of 2.4 A. The high-voltage version of TPS92515HV is therefore selected, offering a maximum  $V_{IN}$  of 65 V compared to its standard (non-HV) version with only a 42-V input voltage capability.

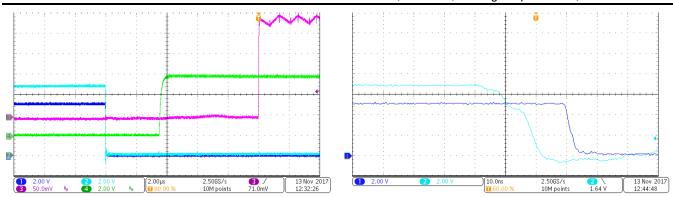

Figure 28 shows the specific implementation of the TPS92515HV in this reference design.

Figure 28. LED Buck With IADJ-DAC and OVP

The input voltage of the LED buck (BUCK\_VIN) is provided by the pre-boost (BOOST\_VOUT). The LED buck can operate over a nominal input voltage range (BUCK\_VIN) from 38 V to 49 V. C5, C6, and C91 serve as bypass capacitors and need to be placed as close as possible to their respective pins of U3. The peak inductor current of L1 can be configured either by an external analog voltage (V\_IADJ\_EXT) applied to header J2 or by an internal voltage (V\_IADJ\_INT) provided by the DAC U4. DAC U4 is controlled from the MCU. The jumper setting on header J3 selects whether the internal or external voltage is used. R7 and C8 or R8 and C8 form a low-pass filter and lead to a RC time constant of roughly 2.5 µs.

31

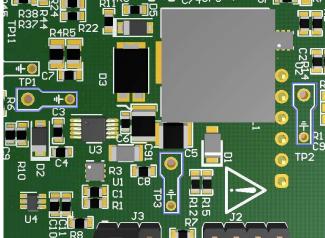

The switch node of the LED buck can be probed on test point TP1 by using a modified oscilloscope probe. The reference design contains numerous of such test points for all the different circuit blocks to simplify the evaluation of the board. Figure 30 shows three of the four test points assigned to the LED buck. To modify the probe, remove the probe tip cover. In addition, the ground lead and alligator clip must be replaced by a ground spring as shown in Figure 29. The small ground spring reduces significantly the noise, which can couple otherwise into the long ground lead of a standard probe configuration.

Figure 29. Probe With Long Ground Lead and Alligator Clip vs Probe With Ground Spring

Figure 30. Dedicated Test Points (Blue) to Simplify Board Evaluation

R4, R5, and C7 are placeholders for a snubber network on the switch node of the LED buck. The type and value of snubber components must be adapted to the circuit of a specific design in case a snubber is needed. Testing the reference design (see Section 3.2.3) shows a very clean switching waveform on TP1, which makes a snubber unnecessary.

The buck inductor L1 is selected carefully. This inductor influences the accuracy of the output current of the buck and therefore also the current through the LEDs as outlined in *TPS92515x 2-A*, *Buck LED Driver with Integrated N-channel FET, High-Side Current Sense, and Shunt FET PWM Dimming Capability*. The selected inductor is rated for 2.6 A, which is sufficient for the peak inductor current of 2.5 A in this reference design. Beside this, the saturation characteristic plays an important role. The inductance of inductors falls usually more or less rapidly in close proximity to the given rated current; however, the selected power inductor from Würth Elektronik shines with a inductance drop of only 20% at 5.2 A given as the saturation current.

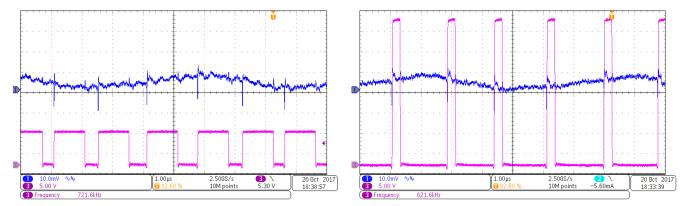

R9 and C9 are other components influencing the ripple current of the inductor and LED (states 3 shown in Figure 27). The peak-to-peak ripple current based on those components and on the 100 µH chosen for L1 is roughly 200 mA, resulting in an switching frequency in the range of 600 kHz to 900 kHz. The switching frequency of the LED buck increases when the voltage of the LED string and the input voltage applied to the LED buck increase; however, the switching frequency decreases when the LED current increases.

The LED buck of this reference design uses a very specific approach for protecting the buck circuit as well as the voltage sensitive components on the LED board (MOSFETs Q3 and Q4) against overvoltage. Overvoltage events can be caused by a sudden interruption of the current flow of the buck inductor. Reasons for such interruptions are, for example, the disconnection of the LED board from the rest of the circuit or LED open failures.

To address such cases, diode D1 is implemented to clamp any voltage on the output of the LED buck to the safe level of the input voltage (BUCK\_VIN). In addition, an overvoltage detection circuit based on the comparator U33, the D-Flip-Flop U7, and the NOR-gate U6 is implemented. A detected overvoltage event causes a low-to-high transition on the comparator's output, leading to a positive edge on the clock input of the D-Flip-Flop. As a result, the High signal from the input pin of the D-Flip-Flop (D) is transferred to its output pin (Q), which drives the output of the NOR-gate U6 low. The NOR-gate's output provides the BUCK\_ON signal for the PWM input of the buck LED driver U3. The BUCK\_ON signal is low due to the overvoltage event and switches the buck LED driver U3 off. This state is latched by the D-Flip-Flop.

The overvoltage event is also detected by the MCU through the BUCK\_VOUT\_OV signal, which is generated by the D-Flip-Flop. The terminal software shows "Buck OVP fault" when an overvoltage event for the buck is detected. To return to a normal system state, the user needs to acknowledge the "Buck OVP fault" by "Reset OV" in the terminal software window. The "Reset OV" forces the MCU to reset the D-Flip-Flop by applying the BUCK\_&\_BOOST\_VOUT\_OV\_RESET signal to the CLR input of the D-Flip-Flop.

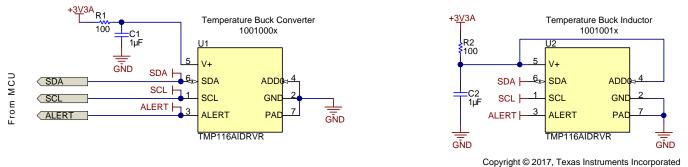

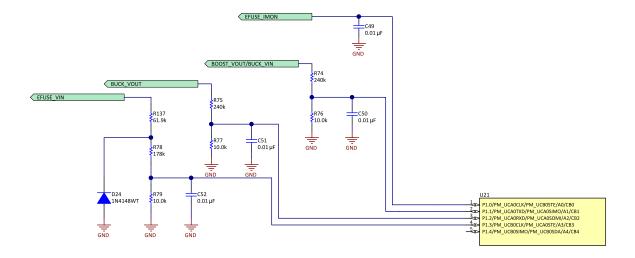

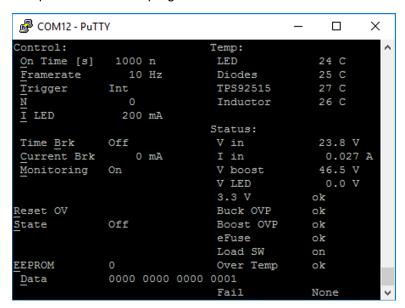

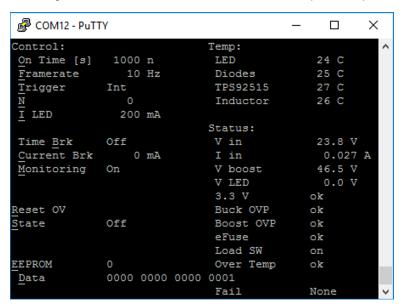

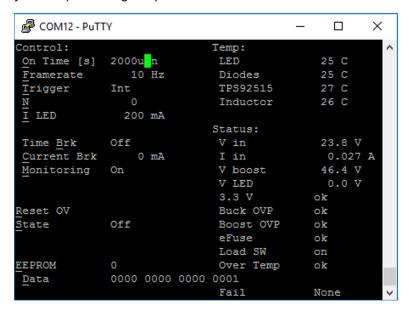

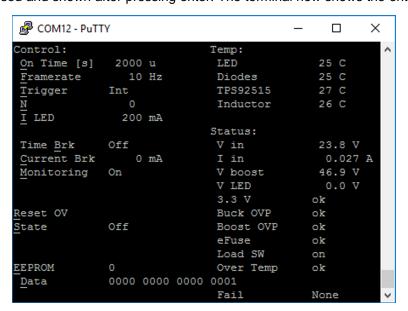

This reference design demonstrates a dedicated solution for overtemperature protection. The temperature of the buck converter (U3) and of the buck inductor (L1) are supervised by two separate temperature sensors, U1 and U2. The temperature sensors communicate through the I<sup>2</sup>C bus with the MCU to enable configuration, readout of the sensed temperature data and alerting of overtemperature (see Section 2.4.2.3). The measured temperatures are shown in the terminal software in the status output zone under "Temp:", "TPS92515", and "Inductor".

The buck inductor is not connected to ground. The thermal pad of the temperature sensor is therefore electrically not connected to the inductor, nor is it from a thermal perspective optimal coupled to it. The latter one holds true for the thermal connection of the temperature sensor sensing the temperature of the TPS92515HV as well. This can lead to severe differences between the actual temperature of the components and the temperatures sensed and shown by the temperature sensors.

Therefore, the user must verify the temperature of those components under operating conditions by own temperature measurements. Do not leave the reference design powered when unattended.

Each of the two TMP116 temperature sensors offer 64 bits of user programmable EEPROM as a unique and helpful feature. This feature enables the user to save and read data for board identification, configuration, parameter sets, or other purposes. Using this EEPROM is supported by the terminal software's parameters "EEPROM" and "Data" as listed in Table 9.

Figure 31. Temperature Sensors of LED Buck

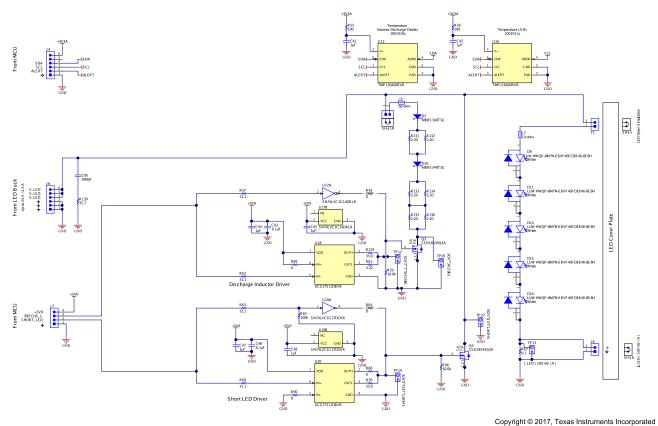

#### 2.4.1.2 LED Board

This reference design has a dedicated board (LED board) assigned to the five high-power LEDs: D9, D11, D14, D15, and D16. For demonstration purposes, this reference design uses OSLON™ Black Flat LEDs™. These LEDs are specified in their data sheet for forward currents up to 1.5 A and provide even graphs for currents down to 300 mA (down to 50 mA with increased tolerances). The data sheet gives even data for the permissible pulse handling capability up to peak pulses of 2.5 A.

Figure 32. Schematic of LED Board

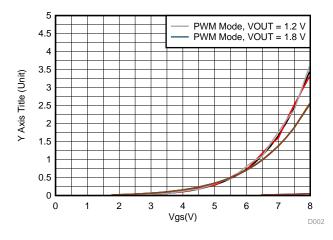

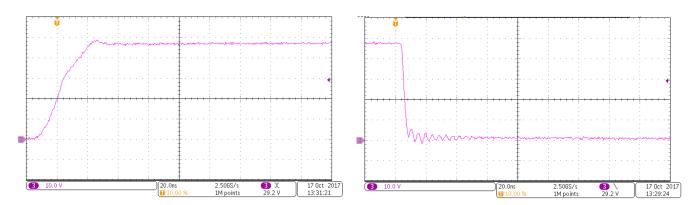

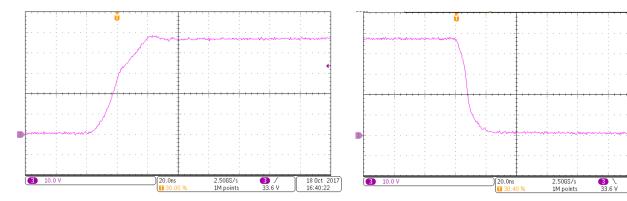

The target of this reference design is to demonstrate that the LED string can be turned on and off very fast with rise and fall times in the 40- to 100-ns range. To achieve this target specification, the two MOSFETs Q4 and Q3 are located in close proximity to the LEDs to steer the current flow.

Q4 acts as  $Q_{SHORT\_LED}$ -FET (see Figure 26 and Figure 27). This FET shorts the LEDs and therefore the output of the LED buck during the precharge of L1 (state 1) and the first freewheeling of L1 (state 2). When this FET is switched off, the inductor current IL is steered immediately through the five LEDs, switching them on instantaneously.

Q3 acts as Q<sub>DISCHG</sub>-FET, which is activated to switch the LEDs off. Q3 provides an parallel path (D7, D10, R131 to R136, and L6, Q3) to the LED string. The voltage drop across this parallel path (at the same current as the LED current) is much lower than the forward voltage of the LED string. This is why the LED current is instantaneously steered away from the LEDs towards this parallel path. This parallel path accelerates the discharging of the buck inductor L1 to shorten the time and as a result reduce the losses during which the inductor's freewheeling current flows through the DC resistance of the inductor L1 as well as through the freewheeling diode D3 of the LED buck. The reduced losses reduces the heating of those components (especially at high LED currents). L1 and D3 needs to be placed in close proximity to U3 from an EMI point of view. Those three components together form a thermal hotspot if accelerated discharging L1 is not implemented.

The losses and heating of the LED board are increased. In a real system, it is likely that the LED board is designed with a dedicated thermal board design in mind so that the additional losses can be managed better on the LED board.

The time needed to switch the LEDs on and off depends on the switching speed of the FETs Q3 and Q4. Dedicated MOSFET drivers (U18 and U20) provide the needed gate drive current for a fast switching of the FETs. Separate outputs (OUTH and OUTL) on those drivers allow a separate fine tuning for the speed with which the MOSFETs are switched on and off. The separate IN+ and IN- pins of this driver (UCC27511 ) enables its configuration as an inverting or non-inverting MOSFET driver. This kind of flexibility is used in this reference design as well.

Figure 32 shows a simplified approach for how to drive the MOSFETs alternative but is not tested in this reference design. The shown single-gate Schmitt triggers (U17 inverting, U19 non-inverting) have a reasonable output drive capability and might be sufficient for driving MOSFET. To evaluate, populate R58 and R64 and remove R129, R61, R68 and R70.

The ferrite beads L6 and L7 and the snubber R130/C95 are used to improve EMI; however, these parts slow down the speed of switching the LEDs on and off. This speed is critical when using the design for ultra-short LED pulses of less than 1  $\mu$ s.

The LED board uses the two TMP116 temperature sensors similarly to the LED buck (see Section 2.4.2.3) to sense the temperature of the LEDs (U16) as well as of the components of the discharge path (U15). U16 is placed close to the LED D16 while U15 is placed near R131, R132, and D10. The sensed temperatures are shown in the terminal software in the status output zone under "Temp:", "LED", and "Diodes". The "Diodes" value represents the sensed temperature of the respective resistors R131 and R132 and diode D10. The two temperature sensors do not only sense the temperatures but provide also an alert in case of overtemperature conditions ( $\geq 70^{\circ}$ C).

The LEDs and the components of the discharge path are electrically floating and are not connected to ground. The thermal pad of the temperature sensors is therefore electrically not connected to the LED or the components of the discharge path, nor is it from a thermal perspective optimal coupled to them. This can lead to severe differences between the actual temperature of the components and the temperatures sensed and shown by the temperature sensors.

Therefore, the user must verify the temperature of those components under operating conditions by own temperature measurements. Do not leave the reference design powered when unattended.

Each of the two TMP116 sensors offer 64 bits of user programmable EEPROM as already outlined for the temperature sensors of the LED buck.

#### 2.4.1.3 Pre-Boost

The pre-boost has the following manifold purposes in this reference design:

- Boost the 8-V to 36-V input voltage (V\_IN on J19) of the reference design to the 48.5-V level needed by the downstream LED buck

- Separate the large discontinuous input ripple current of the LED buck from the input of this reference design by converting it into the more continuous input current ripple of the pre-boost.

- Provide an average input current limit, which adapts to the reference designs input voltage (V\_IN on J19). The adaptable input current limits of the pre-boost leads to a quasi-constant input power limit of 8 W to 10 W, which is independent of the V\_IN applied on J19.

- Implement the average input current limit of the pre-boost in a quasi-lossless manner. The pre-boost operates always with this average input current limit as long as the pre-boost is active. This is in contrast to the reference design's higher input current limit provided by the eFuse U27. The eFuse limits the current by controlling the ON-resistance of the internal pass FET. There is therefore an increase of losses and power dissipation in the eFuse as soon as the eFuse enters the current limit region.

- Energy storage in the pre-boost output capacitors enables the LED buck to generate LED pulses with higher peak power (up to 40 W and more) than the 8-W to 10-W input power limit of the pre-boost.

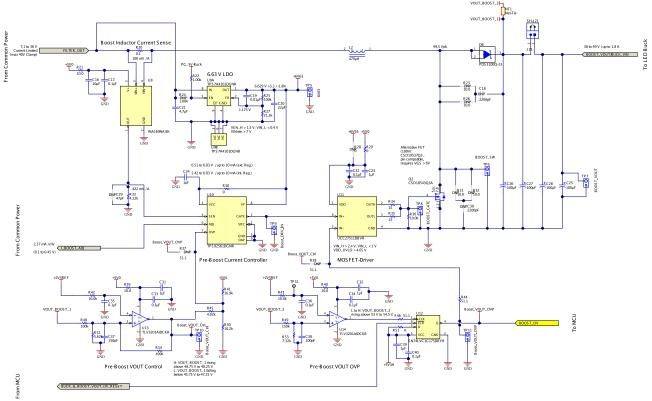

## 2.4.1.3.1 Specific Implementation of Pre-Boost

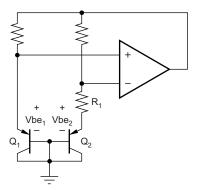

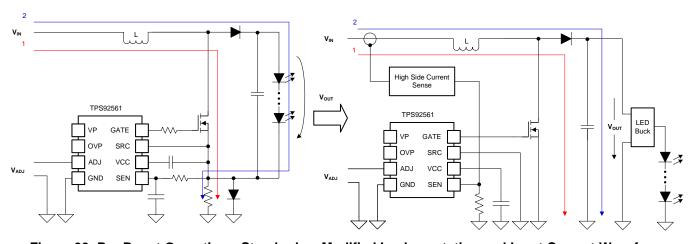

The core of the pre-boost implementation is the pre-boost current controller, U10. The TPS92561  $^{\text{\tiny IR}}$  is selected as a control device for this purpose due to its pure and simple hysteretic operation as shown in Figure 33. Two thresholds are formed as a result from a voltage applied on the ADJ-pin of U10 and from an internally superimposed  $\pm 30$  mV to this ADJ voltage. These thresholds determine the control of the ON- and OFF-times,  $t_{\text{ON}}$  and  $t_{\text{OFF}}$ . The comparator-based operation principle takes complete care of the inductor and input-current control of the pre-boost without any control loop involved. The hysteretic approach also avoids the delays, bandwidth limitations, and loop stability issues commonly found in standard loop-controlled boost topologies.

This reference design uses a modified implementation of the TPS92561 device. The left schematic shown in Figure 33 represents the standard usage of the TPS92561 while the right schematic illustrates the specific implementation of the device to enable its operation in this reference design. The main difference is the current sensing scheme and the ground connection of the load.

The standard implementation does not allow a direct ground connection of the load (string of LEDs). Instead, the LEDs must be connected to ground through a low-side current sense resistor to enable the inductor and input current to be sensed even during the OFF-time of the boost's MOSFET (state 2,  $t_{OFF}$ ). The sensing of the inductor current during  $t_{ON}$  and  $t_{OFF}$  is a prerequisite for equating the input current  $I_{IN}$  with the inductor current  $I_{IN}$ .

The specific case of this more complex reference design requires a common ground usable for the complete system, ranging from the system's power input (J19) over the eFuse, pre-boost, MCU, and LED buck to the output LED string. To achieve this common ground connectivity, the low-side current sensing of the standard configuration is replaced by a high-side current sensing of the inductor current. The input current waveform is almost identical for both use cases. The modified implementation requires just that the  $R_{\text{SENSE}}$  term in the equations given in Figure 33 are corrected by the resulting gain of the high-side current sensing.

Figure 33. Pre-Boost Operation—Standard vs Modified Implementation and Input Current Waveform

A dedicated high-side current shunt monitor (INA169) is used in the real schematic of the pre-boost to implement the high-side current sensing of the boost inductor's current (see Figure 34).

Copyright © 2017, Texas Instruments Incorporated

Figure 34. Schematic of Pre-Boost

R20 serves as current sense resistor, providing a voltage ( $V_{R20}$ ) of 100 mV/A. The INA169 (U8) offers a differential input for sensing this voltage and converts the sensed voltage  $V_{R20}$  into a current  $I_{OUT\_U8}$  (see Equation 8) flowing through R33 to ground (GND). gm is the transconductance of U8 and has a value of 1000  $\mu$ A/V.

$$I_{OUT\_U8} = g_m \times V_{R20} = 1000 \frac{\mu A}{V} \times 100 \frac{mV}{A} \times I_{L2} = 100 \times 10^{-6} \times I_{L2} \tag{8}$$

R33 is converting  $I_{\text{OUT\_U8}}$  into a ground referred voltage  $V_{\text{R33}}$  (as shown in Equation 9), which is perfectly suited to be used as sense voltage  $V_{\text{SEN\_U10}}$  for the boost controller U10.

$$V_{SEN\_U10} = V_{R33} = I_{OUT\_U8} \times R33 = 100 \times 10^{-6} \times I_{L2} \times 4.22 \text{ k}\Omega = 422 \frac{\text{mV}}{\text{A}} \times I_{L2}$$

(9)

U10 compares internally the sense voltage ( $V_{\text{SEN\_U10}}$ ) applied to its SEN pin with the voltage  $V_{\text{ADJ\_U10}}$  applied to its ADJ pin.  $V_{\text{ADJ\_U10}}$  serves for setting the average boost inductor current limit  $I_{\text{L2\_limave}}$ , which equals the average input current limit of the pre-boost  $I_{\text{IN\_Pre-Boost\_limave}}$ .  $V_{\text{ADJ\_U10}}$  to get a specific desired current limit can be calculated according to Equation 10.

$$V_{ADJ\_U10} = V_{SEN\_U10} = 422 \frac{mV}{A} \times I_{L2\_limave} = 422 \frac{mV}{A} \times I_{IN\_Pre\text{-Boost\_limave}}$$

$$\tag{10}$$

The current limit for an specific V<sub>ADJ\_U10</sub> applied to the ADJ pin of U10 can be calculated by Equation 11.

$$I_{L2\_limave} = I_{IN\_Pre\text{-Boost\_limave}} = \frac{V_{ADJ\_U10}}{422 \frac{mV}{A}} = 2.37 \frac{A}{V} \times V_{ADJ\_U10}$$

$$\tag{11}$$

In this reference design, the  $V_{ADJ\_U10}$  is provided by the channel B of the dual DAC U28, which is part of the common power block. The provided  $V_{ADJ\_U10}$  is adapted (see also Section 2.4.2.9) to the input voltage applied to J19 of this reference design to achieve the desired constant input power limit of 8 to 10 W for the pre-boost.

U10 is powered by a separate LDO U9, generating a 6.63-V rail instead of using the internal 8.35-V LDO of U10. The output (VCC) of this internal 8.35-V LDO is shorted to its power input pin VP. This LDO (TPS7A4101 ) has a maximum input voltage of 50 V (recommended) and an absolute maximum rating of 55 V. This high input voltage capability gives an additional margin compared to a 42-V or 45-V maximum input voltage capability of the TPS92561—especially when system input voltage transients like surges are considered. The external LDO U9 ensures a stable operation even for very low input voltages of the preboost down to 7.1 V. Such input conditions can be expected at the lowest system input voltage (8 V) and largest voltage drop across the eFuse and the EMI filter at maximum load.

Due to its low dropout voltage (< 290 mV) and the ability to adjust the output voltage to 6.63 V, a much more stable output voltage can be expected over the full input voltage range (down to 7.1 V) when using this external TPS7A41 compared to the internal 8.35-V LDO of U10. The separate LDO also offers an ENABLE pin, which supports a sequenced start-up of the different voltage rails of the system. For this reference design, the 6.63-V LDO (and with it the pre-boost) is enabled by the power-good signal of the 5-V buck (PG\_5V-Buck).

An additional delay is introduced by the MOSFET driver U11. The output of U11 is held low by the internal UVLO of U11, which supervises the supply voltage on the VDD pin of the MOSFET driver. U11 is powered by the +5V0 rail, which is not powered up when the system starts. This +5V0 rail is controlled by the MCU and comes up later during the system start-up.

This sequenced approach ensures that the eFuse can smoothly charge all the capacitors of the eFuse, the EMI filter, and the pre-boost without being disturbed by the larger start-up and operation current of the pre-boost.

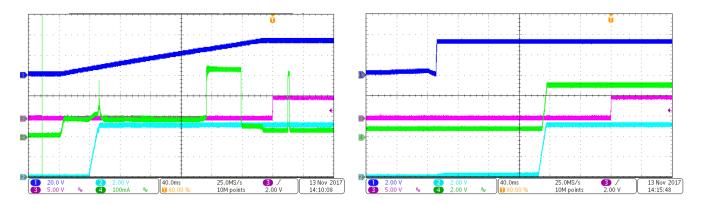

The TPS92561 is designed to control current, but the device does not have an internal loop to regulate output voltage. The output voltage is usually determined and clamped by the forward voltage of the LED string when the TPS92561 is used in its standard configuration of driving LEDs directly (shown in the left schematic of Figure 33). The device in this standard configuration has an OVP with a ±7% threshold tolerance, which steps in when the LEDs are disconnected or when the LEDs fail to open.