# TI Designs 12-Bit, 20-MSPS Data Acquisition Reference Design for Digitizers

# Texas Instruments

# Description

This reference design utilizes the ADS4122 ADC along with OPA656 and THS4541 amplifiers to develop a 12bit, 20-MSPS digitizer for the BeagleBone Cape form factor. This expansion board interfaces with the BeagleBone Black development platform, which is a low-cost, open source, community-supported environment based on the ARM® Cortex®-A8 processor. This design shows a cost-effective and low-power data acquisition system (DAQ) that provides an alternative to FPGA-based systems and features a single-ended, high-impedance input that can be used in a wide number of applications including portable instrumentation and digitizers.

# Resources

TI E2E<sup>™</sup> Community

| TIDA-00942     | Design Folder  |

|----------------|----------------|

| ADS4122        | Product Folder |

| OPA656         | Product Folder |

| THS4541        | Product Folder |

| Sitara™ AM335x | Product Folder |

# Features

- Single-Ended-to-Differential Digitizer Reference Design Using OPA656 and THS4541

- DC-Coupled Signal Path (0 MHz to 9 MHz)

- Low-Power Operation (330 mW)

- 2-V<sub>P-P</sub> Input Voltage Range

- Option to Choose Between 50- $\Omega$  or 1-M $\Omega$  Input Impedance

- Available, Onboard 20-MHz Crystal Oscillator Option for External Clocking

- Low System Cost; BeagleBone Black (BBB) Sitara<sup>™</sup> Processor Reduces System Cost Over FPGA-Based Solutions.

# Applications

- Portable Instrumentation

- Low-Power Data Acquisition

- Industrial Sensor Data Analyzers

- Oscilloscopes

ASK Our E2E Experts

**A**

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

All trademarks are the property of their respective owners.

# 1 System Overview

# 1.1 System Description

This design demonstrates a low-power, 20-MSPS digitizer signal-chain based on the ADS4122 ADC and BeagleBone Black (BBB) development platform. This design includes an OPA656 high-input impedance buffer, THS4541 single-ended-to- differential converter, antialiasing filtering, and digital interfacing.

# 1.2 Key System Specifications

| PARAMETER                  | SPECIFICATIONS                      |

|----------------------------|-------------------------------------|

| Input signal voltage range | 2-V <sub>P-P</sub>                  |

| Resolution                 | 12-bit                              |

| Sample rate                | 20 MSPS                             |

| Input signal bandwidth     | 9 MHz                               |

| Power consumption          | 330 mW                              |

| Output data rate           | 20 MSPS                             |

| Supply voltage             | 5 V (USB bus or externally powered) |

Table 1. Key System Specifications

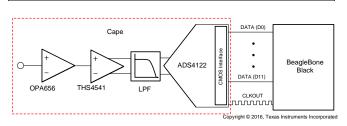

# 1.3 Block Diagram

2

Figure 1 shows the block diagram for the reference design which is composed of a high-input impedance junction gate field-effect transistor (JFET) input buffer (OPA656), single-ended-to-differential converter (THS4541), second-order 9-MHz low-pass antialiasing filter, and 12-bit 20-MSPS ADS4122 analog-to-digital converter (ADC). The parallel CMOS output of the ADC is connected to the BeagleBone Black through the cape interface connectors. Section 2 describes these components in more detail.

Figure 1. TIDA-00942 Block Diagram

# 1.4 Highlighted Products

# 1.4.1 ADS4122

ADS4122 is member of the ADS41xx family of ADCs. These devices provide high dynamic performance while consuming extremely low power at a 1.8-V supply. ADS4122 ADCs have fine gain options that can be used to improve spurious-free dynamic range (SFDR) performance at lower full-scale input ranges, especially at high input frequencies. The ADS4122 includes a DC offset correction loop that can be used to cancel the ADC offset. At lower sampling rates, the ADC automatically operates at a scaled-down power mode without any loss in performance, which makes it suitable for low-power applications.

# 1.4.2 OPA656

The OPA656 is a wideband, unity-gain stable, voltage-feedback operational amplifier with a JFET-input stage to offer an ultra-high dynamic-range amplifier for ADC buffering and transimpedance applications. The device provides extremely low DC error and provides high precision in optical applications. The high unity-gain stable bandwidth and JFET input allows exceptional performance in high-speed, low-noise applications.

# 1.4.3 THS4541

THS4541 is low-power, voltage-feedback, fully differential amplifier (FDA) with an input common-mode range below the negative rail and rail-to-rail output. The amplifier has been designed for low-power data acquisition systems where high density is critical in a high-performance ADC. The THS4541 features the negative-rail input required when interfacing a DC-coupled, ground-centered source signal. This negative-rail input, with rail-to-rail output, allows for easy interface between single-ended, ground-referenced, bipolar signals.

# 2 System Design Theory

This reference design demonstrates the implementation of a low-cost, low-power, data capture solution, which can be used in industrial sensor measurement systems. This fully self-contained BeagleBone Black cape houses an optimized analog front-end (AFE) signal chain and ADC.

# 2.1 Design Theory

The AFE for this cape design combines a high-impedance input buffer, single-ended-to-differential converter, and a 9-MHz second-order low-pass Bessel filter.

Two main parameters must be considered for the AFE design:

- Allowed maximum analog input voltage for the ADC is 2-V<sub>P-P</sub>

- Targeted bandwidth for First Nyquist operation is 10 MHz

Based on these requirements, the acceptable input signal can be  $2-V_{P,P}$ . In this design, the OPA656 device is set up to accept ±1 V and design it with a gain of 1.8 V/V. This setting provides  $3.6-V_{P,P}$  to the fully-differential amplifier stage, which will be brought down to  $1.8-V_{P,P}$ , max input for the ADC. The  $2-V_{P,P}$  (0-dBFS) input voltage is brought down to  $1.8-V_{P,P}$  (-1-dBFS) to prevent saturation of the ADC.

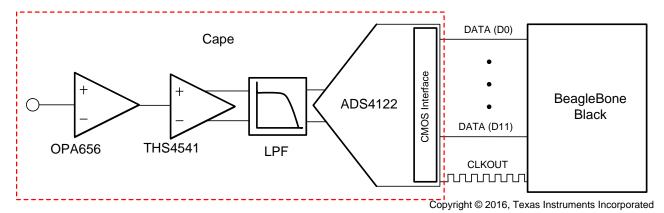

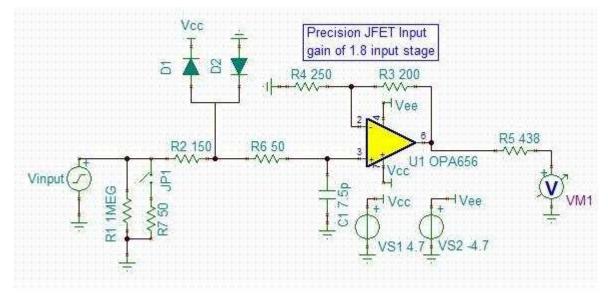

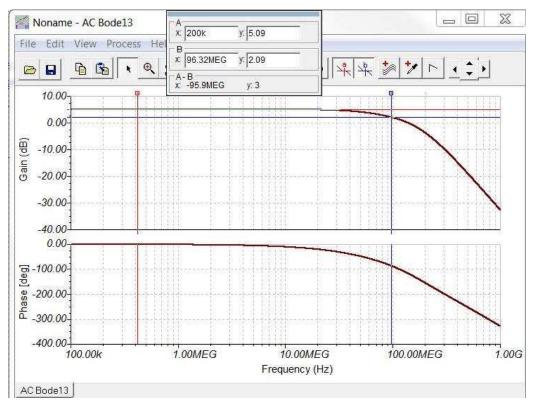

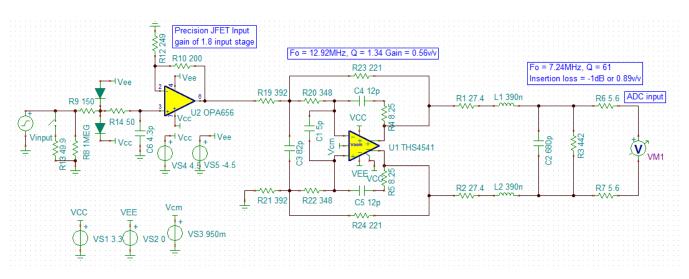

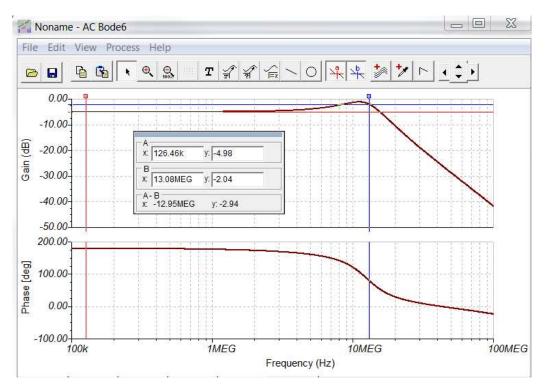

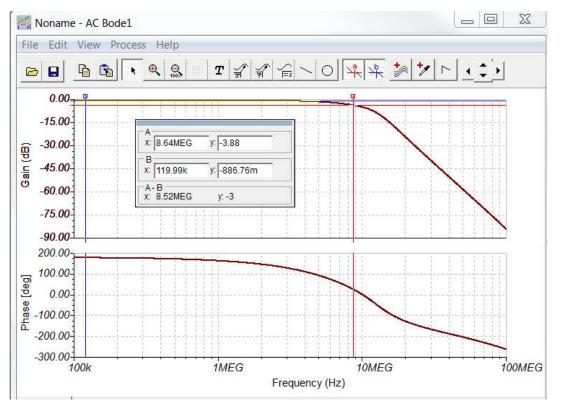

Figure 2 shows the circuit diagram from the OPA656 input buffer, which is operated in a non-inverting configuration with a gain of +1.8 V/V. The input impedance is jumper-selectable between 1 M $\Omega$  or 50  $\Omega$  and has an overdrive protection clamp based on the BAV99 diode pair, which can clamp transients up to ±50 V. The 150  $\Omega$  between the input and diode pair limits the current into the diodes and is followed by an additional 50  $\Omega$ , which ensures that most clamped transient current flows through the external diodes and not the OPA656 electrostatic discharge (ESD) cells. The combined response of the input circuit as shown in Figure 3 serves to limit the bandwidth to 100 MHz, which limits high-frequency noise.

Figure 2. Circuit for Input Buffer Stage (OPA656)

12-Bit, 20-MSPS Data Acquisition Reference Design for Digitizers

Figure 3. Frequency Response of Input Buffer Stage (OPA656)

As Figure 4 shows, the output of the OPA656 device is converted from single-ended to differential by the THS4541 fully differential amplifier (FDA). This amplifier also acts as a second-order, multi-feedback (MFB) based low-pass filter with a cutoff frequency of 13 MHz. To achieve the required  $1.8 - V_{P-P}$  signal level at the ADC input, the combined response of the FDA and following, passive low-pass filter must have a –6 dB gain. A –5 dB is implemented in the FDA with the remaining 1 dB coming from the passive filter. Figure 5 shows the combined frequency response of the FDA and MFB low-pass filter. For more information on how to design the active filter stage, refer to the *Design Methodology for MFB filters in ADC Interface Applications* report [1].

A second-order low-pass RLC filter is implemented right before the input of the ADC and after the singleended-to-differential stage amplifier. The low-pass filter has been designed to have a cutoff frequency of 7.24 MHz and insertion loss of –1dB. For detailed information on how to design the passive filter see the *RLC Filter Design for ADC Interface Applications* report [2].

# System Design Theory

Figure 4. Input Circuit With OPA656, THS4541, and Low-pass Filter

Figure 5. Frequency Response of FDA (THS4541) and MFB Low-pass Filter

12-Bit, 20-MSPS Data Acquisition Reference Design for Digitizers

Figure 6 shows the overall frequency response of the input buffer stage, FDA with MFB low-pass filter, and RLC low-pass filter.

Figure 6. Frequency Response of Input Circuit

# 3 Getting Started Hardware and Software

# 3.1 Hardware

Figure 7 shows the cape board plugs on top of the BBB. By default, all the jumpers on the cape board have been set up to make the cape board function without any register configuration from the BBB. By default, the cape board utilizes the onboard 20-MHz oscillator to clock the ADC. An option also exists to provide an external clock through connector J3. If an external clock is desired, the jumper JP8 must be moved from pin 1-2 to pin 2-3, and jumper JP9 must be installed.

By default, the cape board has been designed to provide a 1-M $\Omega$  termination with an optional 50- $\Omega$  input resistance for a 50- $\Omega$  source. The input resistance can be selected by installing (50  $\Omega$ ) and uninstalling (1 M $\Omega$ ) jumper JP5 on the board.

The cape draws its power from the BBB, which can either be powered by the USB 5 V or the DC input jack. By default, the cape has been set up to draw power from the VDD\_5V pin (jumper JP4 at pin 1-2). If powering the BBB through USB, then the cape board must be configured to draw power from SYS\_5V pin (JP4 at pin 2-3).

The ADS4122 device on the cape board can be configured through either onboard jumpers or through the serial peripheral interface (SPI). By default, the ADC is setup to be configured through jumpers. To control ADS4122 using ADS4122 software graphical user interface (GUI), install the jumper JP3 (SPI-ACTIVE) and remove the jumper JP2 (SPI-SRC). An option also exists to configure the ADC using SPI signals from the BBB. To control the ADC using a BBB, the designer must install both the jumper JP3 (SPI-ACTIVE) and JP2 (SPI-SRC).

# Cape Board

# BeagleBone Black

Figure 7. Stacked view of cape and BeagleBone Black

# 3.2 Software

# 3.2.1 ADS4122 GUI

The ADS4122 GUI is used to configure the ADC. Refer to the ADS4122 tool folder at http://www.ti.com/tool/ads4122evm for a detailed description on how to use the GUI.

# 3.2.2 HSDC Pro GUI

HSDC Pro software is used to analyze the digital data captured by the BBB. Refer to the HSDC Pro tool folder at http://www.ti.com/tool/dataconverterpro-sw for a detailed description on how to use the GUI.

# 3.2.3 BeagleBone Black Data Capture Application

A BeagleBone Black is used to capture data from the ADC. The main processor of the device is the Sitara AM335x, which has a separate co-processor called the Programmable Real-Time Unit Subsystem and Industrial Communication Subsystem (PRU-ICSS) that directly connects to the ADC output. The programmable PRU-ICSS captures 12-bit samples every clock cycle from the ADC and buffers the data into internal memory. The Cortex-A8 on the AM335x then moves the data into its own allocated memory and finally creates a text file of the data samples in its file system. Then access the data file through USB or serial port and run post processing. For further information, contact the Sitara applications team on the Sitara processor E2E forum.

# 4 Testing and Results

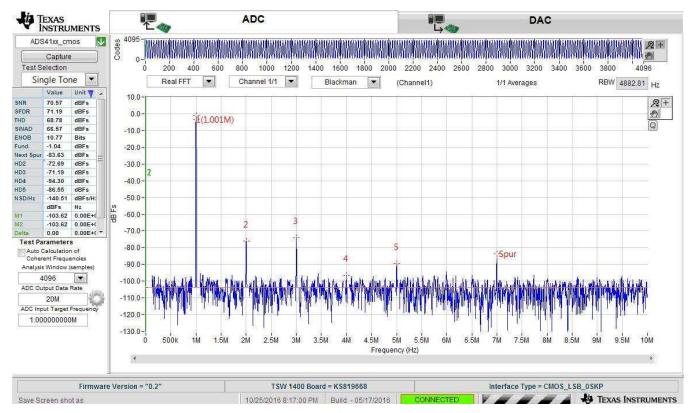

In this section a variety of measurements have been performed to demonstrate the performance of the cape board and describe the process. The cape board is plugged **into** the BeagleBone Black, which captures the data generated by the ADC. The data is analyzed using the HSDC Pro software. Performance measurements have been made on filtered input signals connected to the BNC connector (J1) on the cape.

Figure 8 shows the frequency domain performance of the cape board. A fast Fourier transform (FFT) was performed on a 1-MHz, –1-dBFS input signal. The resulting SNR is 70.5 dB and the SFDR is 71 dB.

Figure 8. FFT 1-MHz –1-dBFS Input Signal

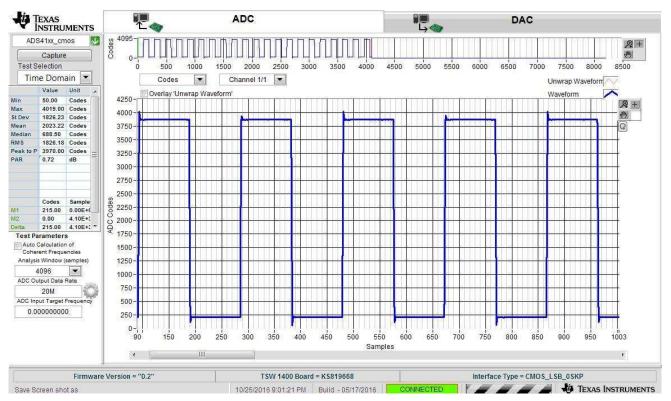

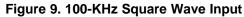

Figure 9 and Figure 10 show the results when a 100-KHz and 1-MHz, ±1-V square wave has been applied at the input of cape board.

Design Files

# 5 Design Files

# 5.1 Schematics

To download the schematics, see the design files at TIDA-00942.

# 5.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00942.

# 5.3 PCB Layout Recommendations

# 5.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-00942.

# 5.4 Gerber Files

To download the Gerber files, see the design files at TIDA-00942.

# 5.5 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-00942.

# 6 Software Files

To download the software files, see the design files at TIDA-00942.

# 7 References

- 1. Texas Instruments, *Design Methodology for MFB Filters in ADC Interface Applications*, Application Report (SBOA114)

- 2. Texas Instruments, RLC Filter Design for ADC Interface Applications, Application Report (SBAA108)

# 8 About the Author

**NEERAJ GILL** is a part of the applications team in the high speed catalog converters group at the Texas Instruments. Neeraj received his BSEE from University of New Hampshire in 2011 and then his Masters in Electrical Engineering also from University of New Hampshire in 2013.

**DAVID GUIDRY** is a part of the applications team in the high speed catalog converters group at the Texas Instruments. He received his BSEE from Texas A&M University, College Station in 2001. Since graduation he has worked for Texas Instruments with roles in SOC characterization, production test development, test strategy, instrumentation design, analog IC design, systems and applications.

12 12-Bit, 20-MSPS Data Acquisition Reference Design for Digitizers

# **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ('TI') reference designs are solely intended to assist designers ("Designer(s)") who are developing systems that incorporate TI products. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.

TI's provision of reference designs and any other technical, applications or design advice, quality characterization, reliability data or other information or services does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such reference designs or other items.

TI reserves the right to make corrections, enhancements, improvements and other changes to its reference designs and other items.

Designer understands and agrees that Designer remains responsible for using its independent analysis, evaluation and judgment in designing Designer's systems and products, and has full and exclusive responsibility to assure the safety of its products and compliance of its products (and of all TI products used in or for such Designer's products) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to its applications, it has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any systems that include TI products, Designer will thoroughly test such systems and the functionality of such TI products as used in such systems. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equivalent classifications outside the U.S.

Designers are authorized to use, copy and modify any individual TI reference design only in connection with the development of end products that include the TI product(s) identified in that reference design. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of the reference design or other items described above may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS AND OTHER ITEMS DESCRIBED ABOVE ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNERS AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS AS DESCRIBED IN A TI REFERENCE DESIGN OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

TI's standard terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products. Additional terms may apply to the use or sale of other types of TI products and services.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's noncompliance with the terms and provisions of this Notice.

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated