# TI Designs

# Reference Design to Measure AC Voltage and Current in Protection Relay With Delta-Sigma Chip Diagnostics

# **Description**

This high-accuracy analog front-end (AFE) reference design measures analog input performance and includes chip diagnostics to help identify power system failures using AC voltage and current measurement AFE using a 4-channel, 24-bit simultaneously sampling differential input delta-sigma ADC for measurement over a wide dynamic range. The ADC is configured to measure 0- to 5-V unipolar. The inputs are scaled to ADC measurement range using a fixed-gain amplifier with 2.5-V DC output level shift. The AFE can be used to measure output of a current transformer, potential divider with analog isolation, and Rogowski coil-based active integrator. The AFE uses a 10-bit, lowresolution successive approximation register (SAR) ADC in parallel with ADS131A04 delta-sigma ADC for diagnostics.

#### Resources

| TIDA-00810   | Design Folder  |

|--------------|----------------|

| ADS131A04    | Product Folder |

| CDCLVC1102PW | Product Folder |

| OPA4180ID    | Product Folder |

| LMV331       | Product Folder |

| AMC1200      | Product Folder |

| SN6501       | Product Folder |

| TPS71733DCKR | Product Folder |

| TLV70450DBVR | Product Folder |

| LM4040       | Product Folder |

| ADC104S021   | Product Folder |

| MSP432P401R  | Product Folder |

|              |                |

Ask Our E2E Experts

#### **Features**

- Data Acquisition

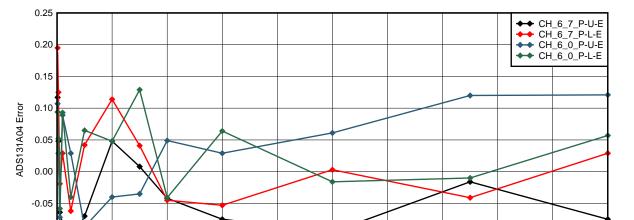

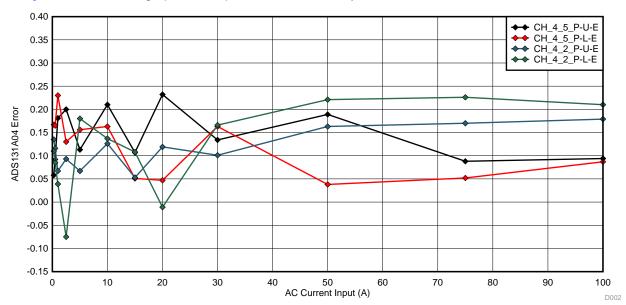

- Four-Channel, Simultaneous-Sampling, 24-Bit Delta-Sigma ADS131A04 ADC-Based AFE Measures Wide Inputs Within ±0.5% Accuracy

- Two ADCs Synchronized For Expanding Input Channels (Eight)

- Analog Inputs

- Current Measurement With Onboard Burden (Low-Value Resistor and Current Transformer)

- Interfaces to Output of TIDA-00777 Rogowski Sensor With Active Hardware Integrator

- Voltage Measurement Using Potential Divider (Alternative to Potential Transformer [PT] or Instrument Transformer) and Isolation Amplifier (AMC1200, Basic Isolation)

- Diagnostics

- Alternate Measurement Path Using 10-Bit SAR ADC for Delta-Sigma ADC Chip Diagnostics

- Provision for 0- to 5-V AVDD Power Supply and 3.3-V DVDD Power Supply for Host Interface

- Interfaces With ARM® Cortex®-M4F-Based Low-Power MCU MSP432P401R

#### **Applications**

- Merging Unit, Bay Control Unit

- Protection Relay

- Molded Case Circuit Breaker

- Power Quality Analyzer

System Overview www.ti.com

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

## 1 System Overview

## 1.1 System Description

Protection relays are installed along the power systems to protect primary equipment like transformers, breakers, and customer loads (motors and busbar). Protection relays are used in generation, transmission, distribution, and at consumer locations. The features and complexities vary depending on the installation. Protection relays detect defective lines, apparatus, and other abnormal or dangerous power system conditions. Protection relays also initiate appropriate control over circuit action. Relays detect and locate faults by measuring electrical quantities in the power system which are different during normal and intolerable conditions. The most important role of protection relays is to first protect individuals and then protect equipment.

Protection relays also minimize the damage and expense caused by insulation breakdowns, which (above overloads) are called faults. These faults can occur as a result of deteriorated insulation or unforeseen events such as lightning strikes or power trips caused by contact with trees and foliage. Protection relays are not required to operate during normal operation, but must immediately activate to handle intolerable system conditions. This immediate availability criterion is necessary to avoid serious outages and damage to portions of or the entire power network. In theory, a relay system should be able to respond to an infinite number of abnormalities that may occur within the network.

Protection relays are intelligent electronic devices (IEDs) that receive measured signals from the secondary side of current transformers (CTs) and voltage transformers (VTs). The relays detect whether or not the protected unit is in a stressed condition (based on the type and configuration of the unit). The protective relays send a trip signal to the circuit breakers to disconnect the faulty components from the power system if necessary.

www.ti.com System Overview

# 1.1.1 Introduction to Protection Relays and Subsystems for Grid Applications

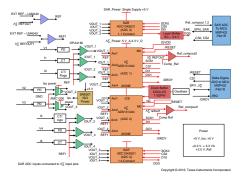

Figure 1 shows a generic block diagram for a multifunction protection relay.

Copyright © 2016, Texas Instruments Incorporated

Figure 1. Generic Block Diagram of Protection Relay

System Overview www.ti.com

Protective relays are categorized based on the equipment type protected such as generators, transmission lines, transformers, and loads.

The protection relays or IEDs used in grid applications have the following generic subsystems. The subsystems are based on the functionality.

- CPU or DSP module This module handles all protection functions and logic. Additionally, this module also handles the HMI and communication functions.

- Power supply

- Nominal auxiliary voltage: 24-V DC, 48- to 60-V DC, 110- to 125-V DC, 220-V DC, 230-V AC, 50 or 60 Hz, ±20%, and 40-W maximum admissible consumption

- Stored energy for up to 50-ms power supply interruption

- AC measurement inputs

- Nominal frequency (FNOM): 50 or 60 Hz

- Operating range: 45 to 66 Hz

- Accuracy: 0.2% FS at FNOM

- · CT measurements inputs

- Nominal current: 1 or 5 A (IN)

- Nominal consumption per phase: < 0.15 A at IN</li>

- Load rating: 20 A in continuous; 30 A for 3 s; 100 A for 1 s

- VT measurements inputs

- Nominal voltage: 57.7 to 500 V

- Nominal consumption per phase: < 0.1 VA at 130 V</li>

- Maximum measurable voltage: 577 V<sub>RMS</sub>

- DC analog input range (independently configurable):

- ±1.25, ±2.5, ±5, and ±10 V

- ±1, ±5, ±10, and ±20 mA

- 0 to 1, 0 to 5, 0 to 10, 0 to 20, and 4 to 20 mA

- DC analog output range (independently configurable): ±5, ±10, ±20 mA, and 4 to 20 mA

- Digital inputs

- Nominal voltage: 24-V DC, 48- to 60-V DC, 110- to 125-V DC or AC, 220-V DC or AC, ±20% or multi-voltage (24- to 250-V DC or AC)

- Groups of 4, 8, 12, 16, or 32

- Digital output relays Continuous current: 5 A

- Control output relays Continuous current: 5 A

- Time synchronization

- IRIG-B GPS clock (through the IRIG-B input)

- Ethernet SNTP server

- Time telegram message issued by remote SCADA (DNP3.0, IEC 60870-5-101 or IEC 60870-5-104)

- Communication capabilities Ethernet communication

- 10BASE-TX or 100BASE-TX, auto-crossing, or 100BASE-FX

- Protocols include UCA2 or IEC 61850, IEC 60870-5-104 (multi-client), or DNP3.0 IP

- Embedded Ethernet switch module with up to six ports (permitting a compact connection of various devices or I/O extensions) – Serial communication

- Up to two SCADA or four IED links per device

- SCADA protocol can be switched between DNP3.0, IEC 60870-5-101, and MODBUS.

- IED protocol can be switched between DNP3.0, IEC 60870-5-103, MODBUS, and IEC 60870-5-101.

This TI reference design focuses on the accurate measurement of voltage and current inputs using a high-resolution delta-sigma ADC.

www.ti.com System Overview

# 1.1.2 Voltage, Current, and Power Measurement AFE

The AFE for measurement of AC voltage and current inputs consists of the following:

- · Voltage input circuit with potential divider, signal conditioning, and interface to ADC

- · Current input circuit consisting of burden resistors, signal conditioning, and interface to ADC

- Signal condition circuit provides fixed or variable gain to the AC inputs and also provides a common mode DC level shift based on application to interface to the ADC.

- ADC for sampling the analog inputs includes multichannel inputs and a high-resolution ADC capable of sampling at ≥ 80 samples per cycle.

- Interface to the MCU to process the sampled values includes an MCU and interconnection to the AFE.

- Power supply subsystem includes generation of required positive and negative power supplies.

#### Additional features of the AFE include:

- Measurement of a wide range of input currents and voltages

- Accurate measurement of AC parameters over the entire input range

- Isolated measurement of voltages using isolation amplifiers

- Measurement of increased number of channels

- Option to diagnose the ADC performance

## 1.1.3 Accurate Measurement of AC Voltage, Current, and Power

Most of the multifunction protection relays from different manufacturers provide power-measurement features. Protection relays are specified to measure wide input voltage and currents within a specified range of accuracy. To achieve wide dynamic input measurement within specified accuracy, an ADC with PGA or a high-resolution ADC are used. This reference design uses a 24-bit delta sigma ADC.

## 1.1.4 Increasing Analog Input Channels

Depending on the protection relay configuration and application, the number of current and voltage channels varies from 4 to 16 channels. The 4 to 16 channels are realized by using multiple ADCs. If each ADC has separate interfaces, the complexity increases. Also, it may be necessary to synchronize multiple ADCs to ensure accuracy. The simplest way to interface multiple ADCs is by daisy-chaining and using a common clock. In this reference design, two ADCs are used. Each ADC has four channels. The ADCs are chained as a single interface and both the ADCs share a common clock.

# 1.1.5 Measurement of Voltages and Currents

Protection relay is used in HV, MV, or LV applications. Depending on the application the voltage levels are high, and during fault conditions the protection relay becomes damaged due to the high voltage levels. The solution to this issue is isolating the voltage and current inputs. The voltages are isolated to provide user safety. The inputs can be isolated using analog isolation amplifiers or digitally using modulators. In this reference design isolation amplifiers are used and the output of the isolation amplifiers is interfaced to the delta-sigma ADC.

# 1.1.5.1 Current Transformer or Rogowski Coil Inputs

Primary current is reduced to measurable secondary current by an external CT and applied to the protection relay. The protection relay has an internal CT to transform the secondary current to a measurable input current level. The advantage of using a CT is that it provides isolation, and no additional isolation is required on the protection relay when an internal CT is used.

System Overview www.ti.com

# 1.1.5.2 Voltage Inputs

High-voltage inputs are connected to a PT and the secondary is connected to the input of the protection relay. Internally the protection relays have a PT that can transform the input AC voltage into a measurable value. PTs are large and have inherent nonlinearity. This issue is overcome by using a resistor divider; however, resistor dividers do not provide isolation like a PT. When using resistor dividers, isolation amplifiers provide the required isolation. Isolation amplifiers with basic or reinforced isolation can be used based on the application. The solution of using the resistor divider and isolation amplifier can be considered as an alternative to the conventional PT.

## 1.1.6 Alternative Methods for Interfacing Analog Inputs to ADC

ADS131A04 is a differential input. In applications where differential measurement is preferred, the following solutions can be considered:

- THS4551 a low-noise, precision, 150-MHz, fully differential amplifier

- THS4531 an ultra-low-power, RRO, fully differential amplifier

For cost-sensitive applications, sensor output can be directly interfaced to the differential input of the ADC. The performance must be evaluated with specific sensors for accuracy.

## 1.1.7 Diagnostics

With the demand to improve safety in the workplace and reliability of power systems, as well as reduce operating costs, industries including grid infrastructure have implemented functional safety complying with the functional safety requirements of standard IEC 61508. To conform with functional safety requirements, system manufacturers must perform safety analysis not just at the system level, but also down to the device level.

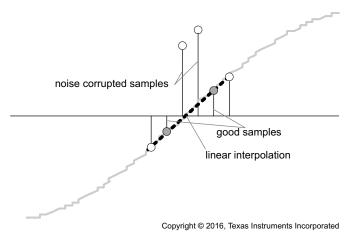

The high-resolution ADCs used for measurement can be diagnosed without stopping the conversion by using an additional lower-resolution ADC. The results of the lower resolution can be used to validate the higher-resolution ADC measurement in the application requiring functional safety.

www.ti.com System Overview

# 1.2 Key System Specifications

**Table 1. Key System Specifications**

| SERIAL NUMBER | PARAMETERS                                                     | DESCRIPTION                                                     | COMMENTS                                                                                              |

|---------------|----------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 1             | ADC for measurement of analog inputs  Type Resolution Channels | Delta-sigma, 24-bit, 4 channel                                  | Measurement accuracy ±0.5%                                                                            |

| 2             | Number of analog inputs                                        | Eight, two ADCs chained                                         | Both ADCs are synchronized using a common clock.                                                      |

| 3             | Non-isolated voltage input range                               | 5 V to 300 V with resistor divider and fixed-gain amplifier     | Measurement accuracy ±0.5%                                                                            |

| 4             | Isolated voltage input range                                   | 10- to 270-V AC<br>AMC1200 isolation (basic)<br>amplifier based | Measurement accuracy ±0.5%                                                                            |

| 5             | Current input measurement range                                | 0.25-A to 100-A AC with fixed-gain amplifier                    | Measurement accuracy ±0.5%                                                                            |

| 6             | ADC clock                                                      | 16.384-MHz oscillator with two buffered output clocks           | _                                                                                                     |

| 7             | Reference                                                      | Internal: • 2.442 VDC • 4 VDC  External (optional): • 2.5 VDC   | ADC on power up defaults to external reference.                                                       |

| 8             | Power supply for AFE                                           | Positive     Digital: +3.3 V     Analog: +5 V                   | Analog input voltage: VAVDD to VAVSS +5 V is used for unipolar input.                                 |

| 9             | Isolated power                                                 | Positive • Analog: +5 V                                         | _                                                                                                     |

| 10            | Interface to MCU for delta-<br>sigma and SAR                   | SPITM                                                           | See Section 3 for connection details.                                                                 |

| 11            | Diagnostics ADC                                                | 10-bit SAR, with 0-V to 5-V input range                         | _                                                                                                     |

| 12            | Diagnostics of reference output                                | Comparator with fixed threshold                                 | _                                                                                                     |

| 13            | SAR ADC to MCU interface                                       | 5-V to 3.3-V level shifter                                      | SAR ADC SPI clock output level of 5 V must be level shifted to 3.3 V to interface to the MSP432P401R. |

| NOTE: | All the voltage and current values are in $V_{\text{RMS}}$ . |

|-------|--------------------------------------------------------------|

| NOTE: | All the voltage and current values are in $V_{\text{RMS}}$ . |

System Overview www.ti.com

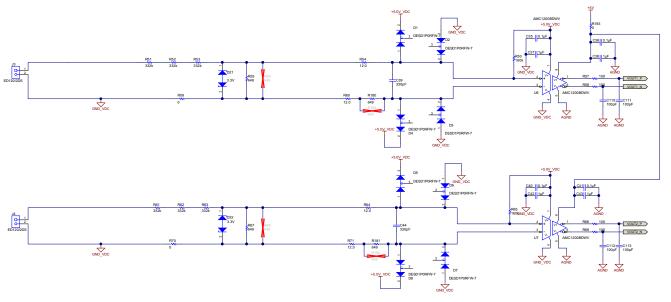

# 1.3 Block Diagram

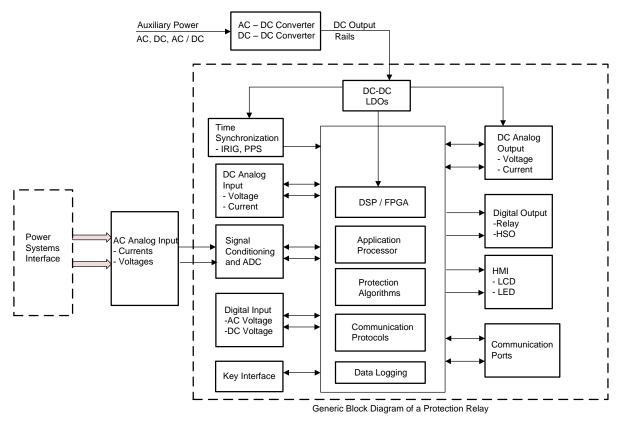

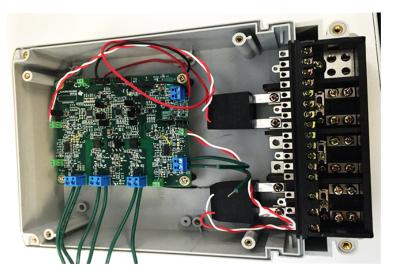

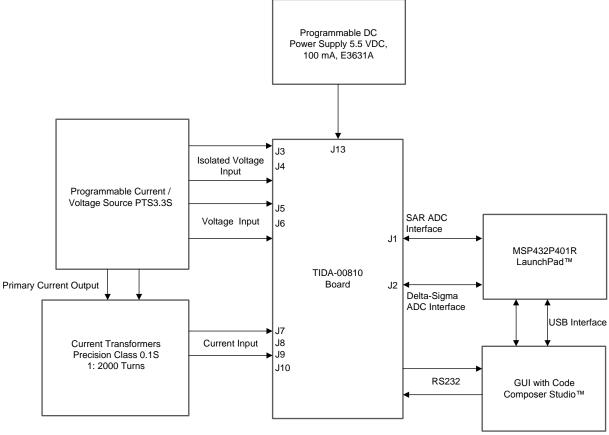

The high-performance AC analog input data acquisition (see Figure 2) has two 24-bit delta-sigma ADCs chained to measure up to eight analog inputs. Potential dividers are provided to directly connect the AC voltage up to 300 V. The option to measure isolated voltage has been provided using isolation amplifiers. The current and isolated voltage inputs have a fixed-gain front-end amplifier for adjusting the current measurement range, and the output of the amplifier is connected to the ADCs. The voltage and current inputs are measured as pseudo-differential inputs and the voltage inputs from the isolation amplifier are measured as differential input.

The required positive power supply for the ADCs operation is generated from one DC input, and provision to configure the power supply based on the input configuration has been provided. Isolated power required to operate isolation amplifiers is also generated onboard. Additionally the reference design has provision to diagnose reference, delta-sigma ADC using comparators, and low-resolution SAR ADCs.

Copyright © 2016, Texas Instruments Incorporated

Figure 2. Block Diagram of AFE With Delta-Sigma Chip Diagnostics

www.ti.com System Overview

## 1.3.1 Delta-Sigma ADC for Measurement

ADS131A04, a 24-bit, 4-channel, simultaneous-sampling differential ADC is used to measure the analog input accurately over a wide range. Two ADCs are chained to measure up to eight channels. For synchronizing the chained ADCs a common clock oscillator of 16.384 MHz frequency and clock buffer CDCLVC1102PW is used. The ADC analog power input is configurable from 0 to 5 V or ±2.5 V based on the application and the input configuration. The isolated voltage output is connected differentially to the ADC. The current and non-isolated voltage gain amplifier outputs are connected in a pseudo-differential input configuration to the ADCs.

#### 1.3.1.1 ADC Interface to MCU—MSP432P401R

Provision to interface ADS131A04 to the MSP432P401R LaunchPad<sup>™</sup> has been provided onboard. The SPI signals, ADC reset, and the ADC data ready signals are interfaced to the MSP432P401R LaunchPad. The ADC IOVDD is configured as asynchronous interrupt mode for communicating with the MCU.

#### 1.3.2 Signal Conditioning

## 1.3.2.1 Current and Non-Isolated Voltage Inputs (With Potential Divider)

The current inputs are connected to external CT of accuracy class 0.1 and the secondary output is connected to the AFE. The transformer has a turns ration of 2000. The secondary of the current transformer is differentially connected to the signal conditioning circuit. The gain is provided using an accurate opamp OP4180. The output of the gain amplifier is a single-ended output connected to the delta-sigma ADC.

An AC voltage input up to 300 V can be directly connected to the AFE. The AFE has an onboard potential divider which divides the 300-V AC input to less than 1.5 V. An amplifier is used to provide a fixed gain and the output of the amplifier is connected to the ADC.

## 1.3.2.2 Isolated Voltage Input Using Isolation Amplifier AMC1200

In applications that require basic isolation for voltage inputs AMC1200 is used. The voltage input is applied across a potential divider and the potential divider output is connected to the AMC1200. The AMC1200 has an input range of ±250 mV. The output has a common-mode shift of 2.55 V with 5-V supply and ×8 gain. The output of AMC1200 is differentially connected to the ADC.

#### 1.3.2.3 Reference

The reference is configured depending on the input. When operating in 0- to 5-V input mode the reference is 2.5 V. The ADC internal reference is 2.442 V or 4 V. The ADC provides a reference output, which can be used for the AFE signal conditioning. The ADC reference is by default configured for external reference. The device must be configured to internal reference for the reference output to be active. Alternatively, an external 2.5-V reference can be used to maximize dynamic range.

#### 1.3.2.4 Analog Inputs Protection

The current inputs are protected against opening by using two parallel resistors and TVS. The voltage inputs are protected for overvoltage and multiple resistors are used as potential divider for improved reliability.

The potential divide input to the isolation amplifier is also protected for overvoltage. Additionally, the isolation amplifiers are protected for overvoltage.

System Overview www.ti.com

# 1.3.3 Power Supply

#### 1.3.3.1 Non-Isolated Power

ADS131A04 has flexible analog power supply input options for operation.

Unipolar supply: 3.3 to 5.5 VDigital supply: 1.65 to 3.6 V

The required power supplies are generated from a single 5.5-V input. The positive voltages generated are 5 V and 3.3 V. These voltages provide flexibility to operate the ADC in any required input configuration.

#### 1.3.3.2 Isolated Power

The isolation amplifier is operated with 5 V on the analog input side. The isolated power supply required is generated from 5 V on the digital side. The required isolated power is generated using the SN6501 transformer driver and LDO. The transformer for the isolated power has been chosen with dielectric voltage of  $> 5 \text{ kV}_{\text{RMS}}$ .

# 1.3.4 Delta-Sigma ADC Diagnostics

For applications requiring functional safety, a low-resolution SAR ADC (ADC104S021CIMM) has been provided. By using the data from the SAR ADC, a delta-sigma ADC can be diagnosed. The references are diagnosed by using external comparators (LMV331) connected as GPIO inputs to the MCU. The ADC operates on 5 V and MCU operates on 3.3 V. The input levels from the MCU are compatible with the expected levels of the ADC. The ADC output is not compatible with the MCU input. A 5-V to 3.3-V level shifter (SN74LV1T34) is used to make the data output signal level from the SAR ADC compatible with MCU input levels.

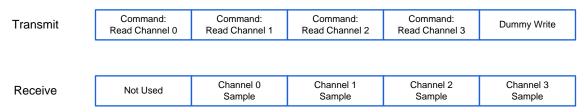

# 2 System Design Theory

# 2.1 Delta-Sigma ADC for Analog Input Measurement

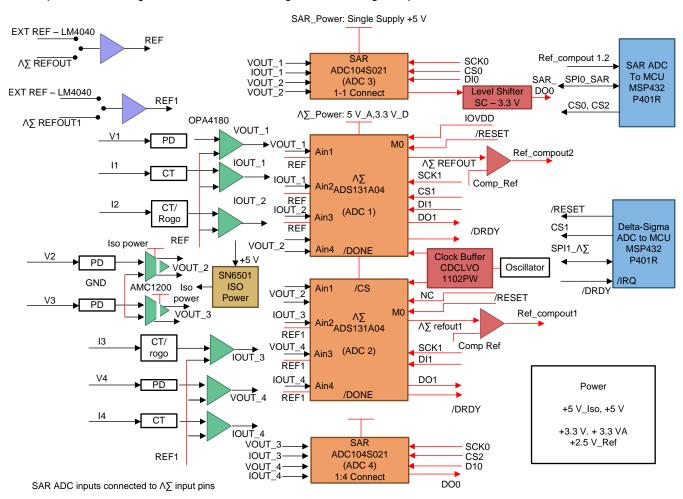

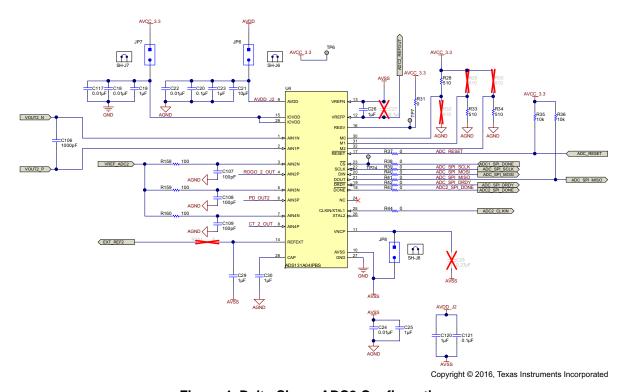

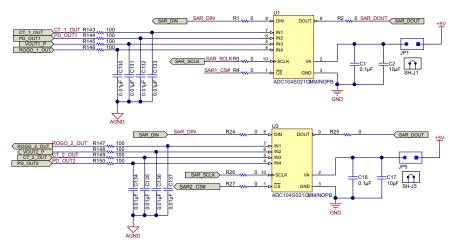

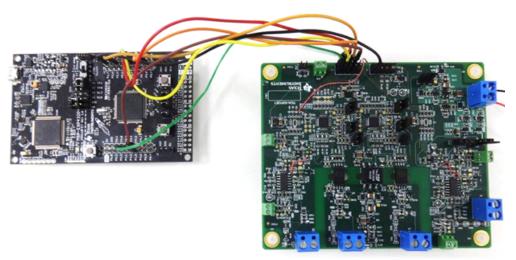

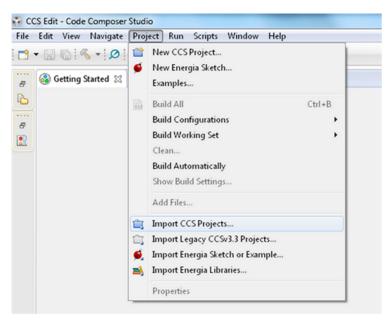

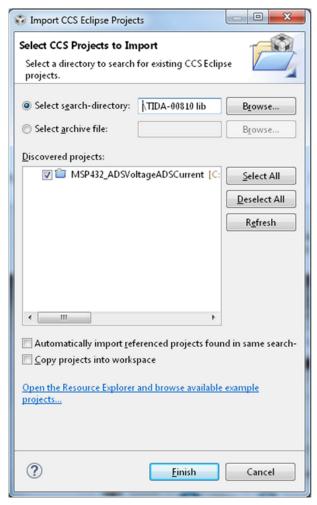

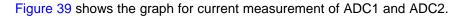

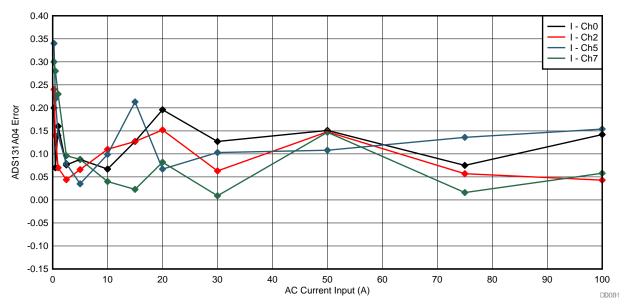

Figure 3 and Figure 4 show two ADS131A04 devices in chain configuration interfaced to the MCU.

Figure 3. Delta-Sigma ADC1 Configuration

Figure 4. Delta-Sigma ADC2 Configuration

Two ADS131A04 ADCs are chained in this reference design. The following inputs have been connected:

- Current input

- · Non-isolated voltage inputs

- Isolated amplifier output (isolated voltage)

The current inputs and the non-isolated voltage inputs are applied in a pseudo-differential configuration. The isolated voltage inputs are applied as differential inputs to the ADC. The ADC has an internal reference. The ADC is configured to use the internal reference, and an external clock input is applied for operation.

Jumpers are provided for the following:

- AVDD JP2 and JP6

- AVCC JP7 and JP3

- Charge pump disable JP4 and JP8

In the current design configuration the charge pump is disabled by mounting the jumpers. The power supply jumpers must also be mounted for proper operation.

For the unipolar mode of operation, an input of 0 to 5 V can be applied, and for bipolar mode input of ±2.5 V can be applied. The M0, M1, and M2 pins are used to configure the ADC. The ADC is configured in asynchronous interrupt mode in this design. Two devices have been chained to achieve eight inputs.

## 2.1.1 Delta-Sigma ADC—ADS131A04

The ADS131A04 are 4-channel, simultaneously sampling, 24-bit, delta sigma ADCs. Wide dynamic range, scalable data rates, and internal fault monitors make the ADS131A04 ideally suited for energy monitoring, protection, and control applications. Flexible power-supply options are available to maximize the effective number of bits (ENOB) for high dynamic range applications. Asynchronous and synchronous master and slave interface options are available, providing ADC configuration flexibility when chaining multiple devices in a single system.

## Features:

- Four simultaneously sampling differential inputs

- Data rates up to 128 kSPS

- Noise performance

- Single-channel accuracy better than 0.1% at 10000:1 dynamic range

- ENOB: 19.1 bits at 8 kSPS

- THD: –100 dB at 50 Hz and 60 Hz

- Integrated negative charge pump

- Flexible analog power-supply operation:

- Negative charge pump: 3.0 to 3.45 V

- Unipolar supply: 3.3 to 5.5 V

- Bipolar supply: ±2.5 V

- Digital supply: 1.65 to 3.6 V

- Low-drift internal voltage reference: 4 ppm/°C

- · ADC self checks

- Cyclic redundancy check (CRC) and hamming code error correction on communications

- Multiple SPI data modes:

- Asynchronous interrupt

- Synchronous master and slave

- Package: 32-pin TQFP

- Operating temperature range: –40°C to 125°C

Find more information at the device's product page: http://www.ti.com/product/ADS131A04

NOTE: The ADS131A02 2-Channel AFE can be considered in single-phase applications.

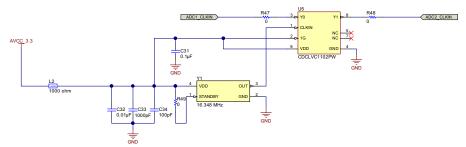

#### 2.1.2 Clock Buffer CDCLVC1102PW

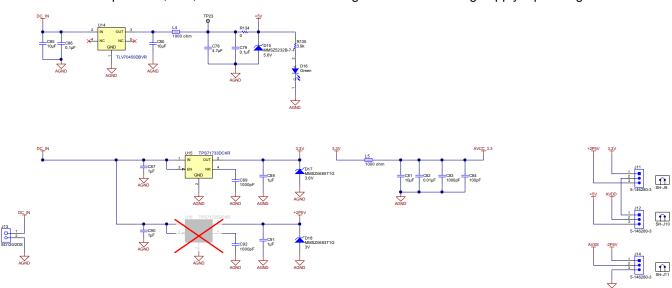

Two ADCs are used in this reference design. To synchronize the sampling of the two ADCs, the same clock is applied to both ADCs. A 16.348-MHz oscillator is used to generate the clock. The clock output is buffered using a clock buffer (see Figure 5).

Copyright © 2016, Texas Instruments Incorporated

Figure 5. Clock Buffer for Delta-Sigma ADCs

The CDCLVC11xx is a modular, high-performance, low-skew, general-purpose clock buffer family from TI. Seven different fan-out variations, 1:2 to 1:12, are available. All of the devices are pin compatible to each other for easy handling. All family members share the same high-performing characteristics such as low-additive jitter, low skew, and wide operating temperature range.

#### Features:

- High-performance LVCMOS clock buffer family

- Very low pin-to-pin skew < 50 ps</li>

- Very low additive jitter < 100 fs</li>

- Supply voltage: 3.3 V or 2.5 V

- f<sub>max</sub> = 250 MHz for 3.3 V

- $f_{max} = 180 \text{ MHz for } 2.5 \text{ V}$

- Operating temperature range: –40°C to 85°C

Table 2 lists the features of the CDCLVC1102PWR.

Table 2. CDCLVC1102PWR Features

| PARAMETER                 | DETAILS                          |

|---------------------------|----------------------------------|

| Part number               | CDCLVC1102PWR                    |

| Description               | IC CLK BUFFER 1:2 250-MHZ 8TSSOP |

| Туре                      | Fan-out buffer (distribution)    |

| Number of circuits        | 1                                |

| Ratio—input:output        | 1:02                             |

| Differential—input:output | No / no                          |

| Input                     | LVCMOS                           |

| Output                    | LVCMOS                           |

| Voltage supply            | 2.3 to 3.6 V                     |

| Mounting type             | Surface mount                    |

| Supplier device package   | 8-TSSOP                          |

Find more information at the device's product page: http://www.ti.com/product/CDCLVC1102

# 2.1.3 Delta-Sigma ADC Interface to MCU—MSP432P401R

Delta-sigma ADCs are interfaced to the MCU MSP432F401R through the SPI (see Figure 6). The required interface signals from the ADC are terminated to connector J2. Resetting the ADC is critical. Follow the instructions in Section 9.4.5 (RESET) of the data sheet (SBAS590) to reset the ADC during initialization.

Copyright © 2016, Texas Instruments Incorporated

Figure 6. Delta-Sigma ADC to MCU Interface Connector

The MSP432P401x device family is Tl's latest addition to its portfolio of efficient ultra-low-power mixed-signal MCUs. The MSP432P401x family features the ARM Cortex-M4 processor in a wide configuration of device options including a rich set of analog, timing, and communication peripherals, thereby catering to a large number of application scenarios where both efficient data processing and enhanced low-power operation are paramount.

#### Features:

- Core

- ARM 32-bit Cortex-M4F CPU with floating-point unit and memory protection unit

- Frequency up to 48 MHz

- Performance benchmark

- 1.196 DMIPS/MHz (Dhrystone 2.1)

- 3.41 CoreMark/MHz

- Energy benchmark:

- 167.4 ULPBench score

#### Memories

- Up to 256KB of flash main memory (simultaneous read and execute during program or erase)

- 16KB of flash information memory

- Up to 64KB of SRAM (including 8KB of backup memory)

- 32KB of ROM with MSPWare driver libraries

- Operating characteristics

- Wide supply voltage range: 1.62 to 3.7 V

- Temperature range (Ambient): –40°C to 85°C

- Serial communication

- Up to four eUSCI\_A modules

- UART with automatic baud-rate detection

- · IrDA encode and decode

- SPI (up to 16 Mbps)

- Up to four eUSCI\_B modules

- I<sup>2</sup>C (with multiple-slave addressing)

- SPI (up to 16 Mbps)

- Flexible I/O features

- Ultra-low-leakage I/Os (±20-nA maximum)

- Up to four high-drive I/Os (20-mA capability)

- All I/Os with capacitive touch capability

- Up to 48 I/Os with interrupt and wake-up capability

- Up to 24 I/Os with port mapping capability

- Eight I/Os with glitch filtering capability

- Advanced low-power analog features

- 14-bit, 1-MSPS SAR ADC

- Internal voltage reference with 10-ppm/°C typical stability

- Two analog comparators

Find more information at the device's product page: http://www.ti.com/product/MSP432P401R

## 2.1.3.1 MSP432P401R LaunchPad

The MSP432P401R LaunchPad lets users develop high-performance applications that benefit from low-power operation. The LaunchPad features the MSP432P401R, which includes the following:

- 48-MHz ARM Cortex-M4F

- 95-µA/MHz active power

- 850-nA RTC operation

- 14-bit 1-MSPS differential SAR ADC

- AES256 accelerator

This LaunchPad includes an onboard emulator with EnergyTrace<sup>™</sup>+ Technology, which means users can program and debug their projects without the need for additional tools, while also measuring total system energy consumption. All pins of the MSP-EXP432P401R device are fanned out for easy access.

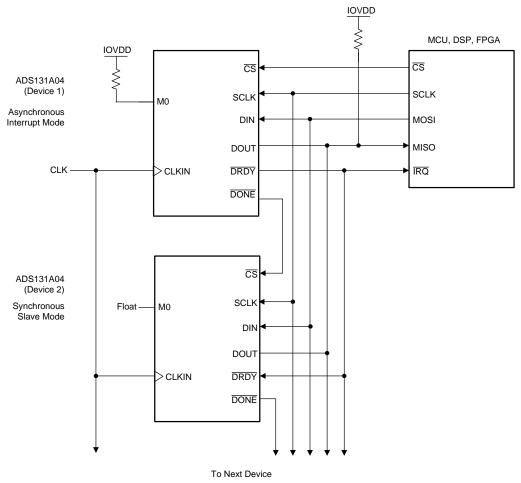

# 2.1.4 Chaining of Multiple Delta-Sigma ADCs

In this reference design two ADS131A04 devices are chained to increase the number of analog channels. The ADS131A04 lets the designer add channels by adding an additional device to the bus. The first device in the chain can be configured using any of the interface modes. All subsequent devices must be configured in synchronous slave mode. In all cases, however, the chain of ADS131A04 devices appears as a single device with extra channels, with the exception that each device sends individual status and data integrity words. In this manner, no additional pins on the host are required for an additional device on the chain. The only special provision that must be made in the interface is to extend the frame to the appropriate length.

# 2.1.4.1 First Device Configured in Asynchronous Interrupt Mode

Figure 7 shows a multiple-device configuration where the first device is configured in asynchronous interrupt mode as noted by the state of the M0 pin. The second ADS131A04 device and any additional devices are configured in synchronous slave mode.

Copyright © 2016, Texas Instruments Incorporated

Figure 7. Multiple Device Configuration Using Asynchronous Interrupt Mode

See Section 10.1.3 of the data sheet *Chaining for Multiple Device Configuration* (SBAS590) for more information on chaining multiple devices.

# 2.2 Signal Conditioning With OPA4180 Amplifier

The OPA4180 operational amplifiers use zero-drift techniques to simultaneously provide low-offset voltage (75  $\mu$ V), and near zero-drift over time and temperature. These miniature, high-precision, low-quiescent current amplifiers offer high-input impedance and rail-to-rail output swing within 18 mV of the rails. The input common-mode range includes the negative rail. Either single or dual supplies can be used in the range of 4.0 V to 36 V (±2 to ±18 V). The quad is offered in SOIC-14 and TSSOP-14 packages. All versions are specified for operation from –40°C to 105°C.

#### Features:

Low offset voltage: 75 μV (maximum)

Zero-drift: 0.1 μV/°C

Low noise: 10 nV/√Hz

Very low 1 / f noise

Excellent DC precision:

PSRR: 126 dBCMRR: 114 dB

Open-loop gain (AOL): 120 dB

Quiescent current: 525 μA (maximum)

Wide supply range: ±2 to ±18 V

Rail-to-rail output: input includes negative rail

Low bias current: 250 pA (typical)

RFI filtered inputs

Find more information at the device's product page: http://www.ti.com/product/OPA4180

## 2.2.1 Current Inputs

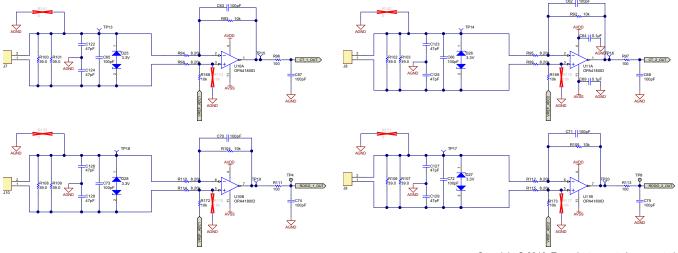

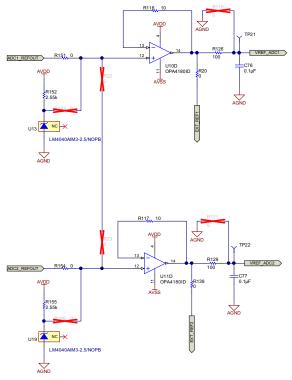

Figure 8 shows the current input scaling amplifiers for four input currents.

Copyright © 2016, Texas Instruments Incorporated

**Figure 8. Current Input Signal Conditioning**

This reference design provides provision to measure up to four current inputs. Two current channels are provided for each ADC. An external CT is used to step down the primary current. The CT ratio used in this TI Design is 1:2000. The secondary current is connected as input to a fixed-gain amplifier. The amplifier is configured in differential mode and depending on the application and the input voltage range the gain can be configured. The output of the amplifier is connected to the delta-sigma ADC for measurement.

The burden required for converting the current input to voltage is provided onboard.

Table 3 provides the calculation and the values for the current input scaling amplifiers.

Table 3. Calculation of Current Input Range

| CURRENT MEASUREMENT | VALUE     | UNIT     |

|---------------------|-----------|----------|

| Burden              | 19.5000   | Ω        |

| Gain                | 1.2195    | _        |

| RF                  | 10.0000   | Ω        |

| RI                  | 8.2000    | Ω        |

| Op amp rail         | 2300.0000 | mV       |

| Op amp input        | 1886.0000 | mV (PK)  |

| Op amp input        | 1333.8048 | mV (RMS) |

| CT sec current      | 68.4002   | mA       |

| CT ratio            | 2000.0000 | _        |

| Primary current     | 136.8005  | A        |

The output of TIDA-00777 can be connected to the current inputs designated Rogo\_1\_out and Rogo2\_Out. TIDA-00777 output is compatible to ADS131A04 output when configured for 2.442 V reference. To connect the Rogowski inputs make the following changes:

- Remove R111, R113, C74, and C75.

- Connect current inputs to TP4 and TP6.

**NOTE:** Ensure the ground of the two boards are connected together.

# 2.2.2 Non-Isolated Voltage Measurement (With Potential Divider)

Figure 9 shows voltage input scaling amplifiers for two non-isolated voltage inputs.

Copyright © 2016, Texas Instruments Incorporated

Figure 9. Voltage Input Signal Conditioning

This reference design provides the option to measure two non-isolated voltage inputs. One input is provided on each ADC. The AC input can be directly applied across the potential divider provided onboard. The output of the potential divider is connected to a fixed-gain amplifier. The amplifier is configured in differential mode and depending on the application and the input voltage range, the gain can be configured.

The output of the gain amplifier is connected to the ADC input.

Table 4 lists the input range calculation for voltage scaling of non isolated voltage input amplifiers.

| Table 4. | Input | Range for | Non-Isolated | <b>Voltage Input</b> |

|----------|-------|-----------|--------------|----------------------|

|          |       |           |              |                      |

| VOLTAGE MEASUREMENT_PD | VALUE     | UNIT     |

|------------------------|-----------|----------|

| PD                     | 993.3000  | Ω        |

| Gain                   | 1.2195    | _        |

| RF                     | 10.0000   | Ω        |

| RI                     | 8.2000    | Ω        |

| Op amp rail            | 2300.0000 | mV       |

| Op amp input           | 1886.0000 | mV (PK)  |

| Op amp input           | 1333.8048 | mV (RMS) |

| Volt division ratio    | 301.0000  | _        |

| Primary voltage        | 401.4752  | V        |

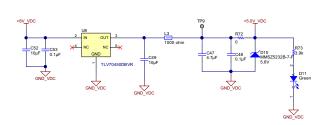

# 2.2.3 Isolated Voltage Measurement Using AMC1200

Figure 10 shows the isolation amplifiers for voltage input.

Copyright © 2016, Texas Instruments Incorporated

Figure 10. Isolation Amplifier With Input Protection and Potential Divider

The AMC1200 and AMC1200B are precision isolation amplifiers with an output separated from the input circuitry by a silicon dioxide (SiO2) barrier that is highly resistant to magnetic interference. This barrier has been certified to provide galvanic isolation of up to 4250 V<sub>PEAK</sub> (AMC1200B) or 4000 V<sub>PEAK</sub> (AMC1200) according to UL1577 and VDE V 0884-10. Used with isolated power supplies, these devices prevent noise currents on a high common-mode voltage line from entering the local ground and interfering with or damaging sensitive circuitry. The common-mode voltage of the output signal is automatically adjusted to either the 3- or 5-V low-side supply. The AMC1200 and AMC1200B are fully specified over the extended industrial temperature range of –40°C to 105°C and are available in a wide-body SOIC-8 package (DWV).

#### Features:

±250-mV input voltage range optimized for shunt resistors

Very low nonlinearity: 0.075% maximum at 5 V

Low offset error: 1.5-mV maximum

Low noise: 3.1 mV<sub>RMS</sub> typical

Low high-side supply current: 8 mA maximum at 5 V

Input bandwidth: 60-kHz minimumFixed gain: 8 (0.5% accuracy)

High common-mode rejection ratio: 108 dB

· 3.3-V operation on low side

Certified galvanic isolation:

UL1577 and VDE V 0884-10 approved

Isolation voltage: 4250 V<sub>PEAK</sub> (AMC1200B)

- Working voltage: 1200  $V_{\text{PEAK}}$

Transient immunity: 10 kV/μs minimum

Typical 10-year lifespan at rated working voltage

Fully specified over the extended industrial temperature range

Find more information at the device's product page: http://www.ti.com/product/AMC1200

This reference design provides the option to measure two isolated voltage inputs. Isolation amplifiers are used to provide the required analog isolation. The isolator used provides basic isolation with a fixed gain of x8. The common-mode output is set to 2.55 V in this design by applying 5-V supply. The AC input is specified to be linear up to ±250 mV input with saturation at ±312 mV. The output of the isolation amplifier is differentially connected to the ADC. The required protection for input overvoltage has been provided.

Table 5 provides calculations for scaling the voltage inputs to the isolation amplifier.

Table 5. Input Voltage Range Calculation for AMC1200

| VOLTAGE MEASUREMENT _ISO AMP _AMC1200 | VALUE     | UNIT |

|---------------------------------------|-----------|------|

| PD                                    | 996.6500  | Ω    |

| Gain                                  | 8.0000    | _    |

| Output                                | 2.0000    | PK   |

| RMS                                   | 1.4144    | V    |

| Input                                 | 0.1768    | V    |

| Volt division ratio                   | 1533.0000 | _    |

| Primary voltage                       | 271.0396  | V    |

# 2.2.4 Reference—LM4040 and Buffer (For DC Common-Mode Level Shift)

The reference and buffers are used to provide the required DC common-mode level shifting for using the ADC range (see Figure 11). Currently, internal ADC is used, and based on the application requirement, external reference can be configured.

Copyright © 2016, Texas Instruments Incorporated

Figure 11. Reference With Buffer for Gain Amplifiers

The LM4040-N precision voltage reference is available in an SOT-23 surface-mount package. The advanced design of the LM4040-N eliminates the need for an external stabilizing capacitor while ensuring stability with any capacitive load, therefore making the LM4040-N easy to use. The minimum operating current increases from 60  $\mu A$  for the 2.5-V LM4040-N to 100  $\mu A$  for the 10-V LM4040-N. All versions have a maximum operating current of 15 mA.

The LM4040-N uses a fuse and Zener-zap reverse breakdown voltage trim during wafer sort to ensure that the prime parts have an accuracy of better than ±0.1% (A grade) at 25°C. Bandgap reference temperature drift curvature correction and low dynamic impedance ensure stable reverse breakdown voltage accuracy over a wide range of operating temperatures and currents.

#### Features:

- No output capacitor required

- Tolerates capacitive loads

- Key specifications (2.5-V LM4040-N)

- Output voltage tolerance (A grade, 25°C): ±0.1% (maximum)

- Low output noise (10 Hz to 10 kHz): 35  $\mu$ V<sub>RMS</sub> (typical)

- Wide operating current range: 60 μA to 15 mA

- Low temperature coefficient: 100 ppm/°C (maximum)

Table 6 lists the LM4040 features.

Table 6. LM4040 Features

| PARAMETER                         | DETAILS               |

|-----------------------------------|-----------------------|

| Part number                       | LM4040AIM3-2.5 / NOPB |

| Reference type                    | Shunt                 |

| Output type                       | Fixed                 |

| Voltage output (minimum or fixed) | 2.5 V                 |

| Current output                    | 15 mA                 |

| Tolerance                         | ±0.1%                 |

| Temperature coefficient           | 100 ppm/°C            |

| Noise: 10 Hz to 10 kHz            | 35 μV <sub>RMS</sub>  |

| Current cathode                   | 65 μA                 |

| Supplier device package           | SOT-23-3              |

The delta-sigma ADC operates with unipolar input or bipolar inputs. For bipolar inputs the reference is zero and for unipolar input the reference must be shifted – typically, the input range divided by 2. The amplifier outputs are level shifted depending on the input configuration. The references can be configured as follows:

1. Use ADC REFP out for DC level shifting the analog input.

R151 and R154 mounted

R153 and R156 not mounted

2. Use external Reference for DC level shifting the analog input.

R153 and R156 mounted

R151 and R154 not mounted

Based on the power supply configuration the reference output to the op amp gain amplifier can be selected as follows:

1. 0-V reference

R118 and R121 mounted

R126 and R129 not mounted

2. 2.5-V reference

R126 and R129 mounted

R118 and R121 not mounted

## 2.3 Power Supply

The delta-sigma ADC has flexible analog power-supply options for operation as follows:

• Unipolar supply: 3.3 to 5.5 V

Bipolar supply: ±2.5 V

Digital supply: 1.65 to 3.6 V

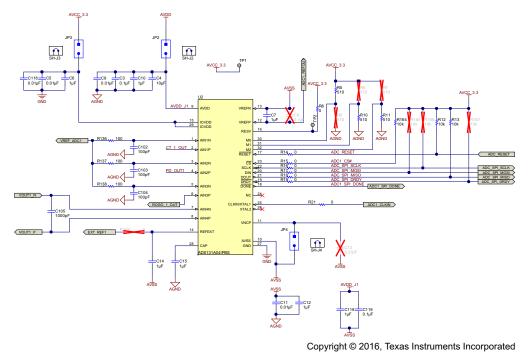

The power supplies required to operate the ADC are provided onboard. The power supply operates from a single positive input voltage (see Figure 12). The required overvoltage protection is provided using Zener diodes. Jumpers J11, J12, and J14 are used to configure the ADC analog supply input range.

Copyright © 2016, Texas Instruments Incorporated

Figure 12. Onboard Positive Power Supply With Protection

#### 2.3.1 Non-Isolated Power

## 2.3.1.1 +5 V (U14)

The TLV704 series of LDO regulators are ultra-low-quiescent current devices designed for extremely power-sensitive applications. Quiescent current is virtually constant over the complete load current and ambient temperature range. These devices are an ideal power-management attachment to low-power MCUs, such as the MSP430. The TLV704 operates over a wide operating input voltage of 2.5 to 24 V. Therefore, the device is an excellent choice for battery-powered systems and industrial applications that undergo large line transients.

## Features:

- Wide input voltage range: 2.5 to 24 V

- Low 3.2-μA quiescent current

- Ground pin current: 3.4 μA at 100-mA I<sub>OUT</sub>

- Stable with a low-ESR, 1-μF typical output capacitor

Table 7 lists the TLV70450 LDO features.

Table 7. TLV70450 LDO Features

| PARAMETER                 | DETAILS          |

|---------------------------|------------------|

| Part number               | TLV70450DBVR     |

| Regulator topology        | Positive fixed   |

| Voltage output            | 5 V              |

| Current output            | 150 mA           |

| Voltage dropout (typical) | 0.85 V at 100 mA |

| Number of regulators      | 1                |

| Voltage input             | Up to 24 V       |

| Current limit (minimum)   | 160 mA           |

| Operating temperature     | -40°C to 125°C   |

| Supplier device package   | SOT-23-5         |

## 2.3.1.2 +3.3 V (U15)

The TPS717xx family of LDO, low-power, linear regulators offers very high power-supply rejection (PSRR) while maintaining very low 45- $\mu$ A ground current in an ultra-small, 5-pin SOT package. The family uses an advanced BiCMOS process and a PMOS pass device to achieve fast start-up, very low noise, excellent transient response, and excellent PSRR performance. The TPS717xx is stable with a 1- $\mu$ F ceramic output capacitor and uses a precision voltage reference and feedback loop to achieve a worst-case accuracy of 3% overall load, line, process, and temperature variations.

#### Features:

- Input voltage: 2.5 to 6.5 V

- Available in multiple output versions:

- Fixed output with voltages from 0.9 to 5 V

- Adjustable output voltage from 0.9 to 6.2 V

- · Ultra-high PSRR:

- 70 dB at 1 kHz, 67 dB at 100 kHz, and 45 dB at 1 MHz

- · Excellent load and line transient response

- Very low dropout: 170 mV typical at 150 mA

- Low noise: 30 μV<sub>RMS</sub> typical (100 Hz to 100 kHz)

Table 8 lists the TPS71733 LDO features.

Table 8. TPS71733 LDO Features

| PARAMETER                 | DETAILS          |

|---------------------------|------------------|

| Part number               | TPS71733DCKR     |

| Regulator topology        | Positive fixed   |

| Voltage output            | 3.3 V            |

| Current output            | 150 mA           |

| Voltage dropout (typical) | 0.17 V at 150 mA |

| Number of regulators      | 1                |

| Voltage input             | Up to 6.5 V      |

| Current limit (minimum)   | 200 mA           |

| Operating temperature     | -40°C to 125°C   |

| Supplier device package   | SC-70-5          |

# 2.3.2 Power Supply Jumper Options

Table 9 shows the connectors configuration for a delta-sigma analog power supply.

Table 9. Power Supply for Delta-Sigma Analog supply

| CONNECTOR | 1-2           | 3-2        |

|-----------|---------------|------------|

| J11       | NA            | NA         |

| J12       | AVDD = 2.5 V  | AVDD = 5 V |

| J14       | AVSS = −2.5 V | AVSS = 0 V |

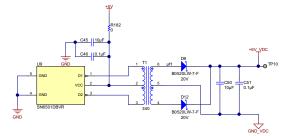

#### 2.3.3 Isolated Power

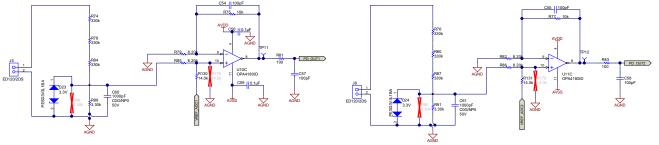

Figure 13 shows the transformer driver and LDO which generate an isolated power supply for the isolation amplifier.

Copyright © 2016, Texas Instruments Incorporated

Figure 13. Isolated Power Supply for Isolation Amplifiers

The SN6501 is a monolithic oscillator and power-driver, specifically designed for small form factor, isolated power supplies in isolated interface applications. The device drives a low-profile, center-tapped transformer primary from a 3.3- or 5-V DC power supply. The secondary can be wound to provide any isolated voltage based on transformer turns ratio. The SN6501 consists of an oscillator followed by a gate drive circuit that provides the complementary output signals to drive the ground referenced N-channel power switches. The internal logic ensures break-before-make action between the two switches.

#### Features:

- Push-pull driver for small transformers

- Single 3.3- or 5-V supply

- High primary-side current drive:

- 5-V supply: 350 mA (maximum)

- 3.3-V supply: 150 mA (maximum)

- Low ripple on rectified output permits small output capacitors

- Small 5-pin SOT-23 package

Find more information at the device's product page: http://www.ti.com/product/SN6501

# 2.4 Delta-Sigma ADC Diagnostics

Table 10 lists the ADC selection table with pin compatibility.

Table 10. ADC Selection Table With Pin Compatibility

| PARAMETER                               | ADC104S021 | ADC084S021 | ADC104S051 | ADC104S101 | ADC124S021 |

|-----------------------------------------|------------|------------|------------|------------|------------|

| Resolution (bits)                       | 10         | 8          | 10         | 10         | 12         |

| Sample rate (maximum) (SPS)             | 200 kSPS   | 200 kSPS   | 500 kSPS   | 1 MSPS     | 200 kSPS   |

| Number of input channels                | 4          | 4          | 4          | 4          | 4          |

| Power consumption (typical) (mW)        | 94         | 1.6        | 2.7        | 3.9        | 2.2        |

| Input range (minimum) (V)               | 0          | 0          | 0          | 0          | 0          |

| Analog voltage<br>AVDD (maximum)<br>(V) | 5.25       | 5.25       | 5.25       | 5.25       | 5.25       |

| SNR (dB)                                | 61.8       | 49.6       | 62.7       | 61.7       | 72         |

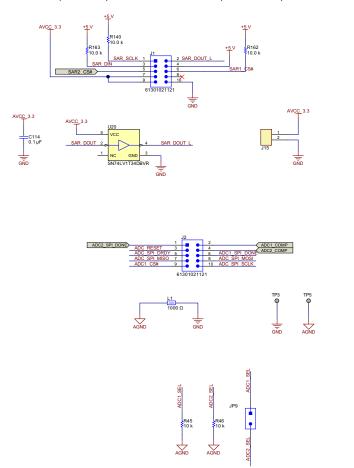

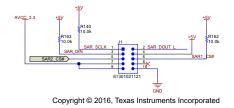

This reference design provides a method to diagnose the delta-sigma ADC. A low-resolution SAR ADC can be used. ADC104S021 10-bit or ADC124S021 12-bit ADC, which are pin compatible can be used in the design. This is a unipolar ADC. The 2.442-V or 2.5-V level shifted input is applied depending on the reference used. The ADC sample output is compared with the delta-sigma ADC output for diagnostics. The reference is diagnosed using comparators. The ADC is interface to the MCU using the SPI. Two chip selects are provided for selecting one of the two ADCs at a given time. The ADC input levels are compatible to the MCU output. To interface to the MCU, 5-V ADC output level must be shifted to 3.3 V. A single-channel level shifter does the level shifting. The ADC operates on 5 V and has internal reference. The SPI input is the clock for the ADC conversion.

#### 2.4.1 SAR ADC—ADC104S021

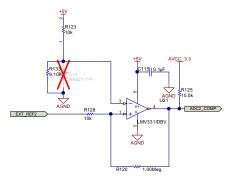

Figure 14 shows the low resolution SAR ADC used for diagnostics interfaced to the MCU.

Copyright © 2016, Texas Instruments Incorporated

Figure 14. SAR ADC2 Configuration for Diagnostics

The ADC104S021 is a low-power, 4-channel CMOS, 10-bit ADC with a high-speed serial interface. The ADC104S021 and ADC104S021Q are fully specified over a sample rate range of 50 ksps to 200 ksps. The converter is based on a successive-approximation register architecture with an internal track-and-hold circuit. The ADC can be configured to accept up to four input signals at inputs IN1 through IN4.

The output serial data is straight binary, and is compatible with several standards, such as SPI™, QSPI™, MICROWIRE, and many common DSP serial interfaces. The ADC104S021 and ADC104S021Q operate with a single supply that can range from 2.7 to 5.25 V.

## Features:

- Specified over a range of sample rates

- Four input channels

- Variable power management

- Single power supply with a 2.7- to 5.25-V range

#### Key specifications:

- DNL: ±0.13 LSB (typical)

- INL: ±0.13 LSB (typical)

- SNR: 61.8 dB (typical)

- Power consumption

- 3-V supply: 1.94 mW (typical)

- 5-V supply: 6.9 mW (typical)

Find more information at the device's product page: http://www.ti.com/product/ADC104S021

# 2.4.2 Comparator LMV331

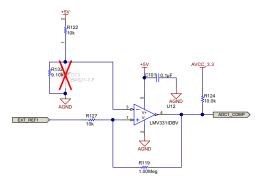

Figure 15 shows the reference diagnostic comparators.

Copyright © 2016, Texas Instruments Incorporated

Figure 15. 2.5-V Reference Diagnostics Comparators

The LMV331 device is the single-comparator version. LMV331 devices are the most cost-effective solutions for applications where low-voltage operation, low power, and space saving are the primary specifications in circuit design for portable consumer products.

#### Features:

- 2.7-V and 5-V performance

- Low supply current

- LMV331 130 μA (typical)

- · Input common-mode voltage range includes ground

- Low output saturation voltage 200 mV (typical)

- Open-collector output for maximum flexibility

Find more information at the device's product page: http://www.ti.com/product/LMV331

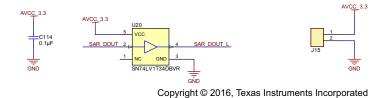

#### 2.4.3 Level Shifter—SN74LV1T34

Figure 16. 5-V to 3.3-V Level Shifter for SAR ADC Interface to MCU

The SN74LV1T34 is a low-voltage CMOS gate logic that operates at a wider voltage range for industrial, portable, telecom, and automotive applications. The output level is referenced to the supply voltage and is able to support 1.8-, 2.5-, 3.3-, and 5-V CMOS levels.

The input is designed with a lower threshold circuit to match 1.8-V input logic at  $V_{\rm CC} = 3.3$  V and can be used in 1.8- to 3.3-V level up translation. In addition, the 5-V tolerant input pins enable down translation (for example, 3.3-V to 2.5-V output at  $V_{\rm CC} = 2.5$  V). The wide  $V_{\rm CC}$  range of 1.8 to 5.5 V allows for generation of desired output levels to connect to controllers or processors. The SN74LV1T34 is designed with a current-drive capability of 8 mA to reduce line reflections, overshoot, and undershoot caused by high-drive outputs.

#### Features:

- Single-supply voltage translator at 5.0 V, 3.3 V, 2.5 V, and 1.8 V  $V_{\text{CC}}$

- Operating range of 1.8 to 5.5 V

- · Up translation

- 1.2 to 1.8 V at 1.8 V  $V_{\rm CC}$

- 1.5 to 2.5 V at 2.5 V  $V_{\rm CC}$

- 1.8 to 3.3 V at 3.3 V  $V_{\rm CC}$

- 3.3 to 5.0 V at 5.0 V  $V_{\rm CC}$

- Down translation

- 3.3 to 1.8 V at 1.8 V  $V_{CC}$

- 3.3 to 2.5 V at 2.5 V  $V_{\rm CC}$

- 5.0 to 3.3 V at 3.3 V  $V_{\rm CC}$

- Logic output is referenced to V<sub>CC</sub>

- · Output drive

- 8.0-mA output drive at 5.0 V

- 7.0-mA output drive at 3.3 V

- 3.0-mA output drive at 1.8 V

- 5.0-V tolerance on input pins

- –40°C to 125°C operating temperature range

Find more information at the device's product page: http://www.ti.com/product/SN74LV1T34

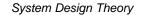

# 2.4.4 SAR ADC to MCU Interface

Figure 17 shows the interface connections between SAR ADC and MSP432P401R MCU

Figure 17. SAR ADC to MCU SPI Connector With Chip Select

# 2.5 Design Enhancements

# 2.5.1 Sampling Rate

This TI Design has been tested with the ADC configured to sample the analog input at 80 samples per cycle. The ADC can provide data rates up to 128 kSPS. There are 16 selectable oversampling ratio (OSR) options to optimize the converter for a specific data rate. Higher data rates are typically used in grid infrastructure applications that implement software resampling techniques to help with channel-to-channel phase adjustment for voltage and current. For more information, see Section 9.3.1, *Clock*, of the data sheet.

# 2.5.2 Using External Reference With ADS131A04

The delta-sigma ADC has an internal reference of 2.442 V. The dynamic range can be increased by using an external reference of 2.5 V. Provision to provide an external reference input to the delta-sigma ADC is provided.

In the ADS131A04 by default, the external reference is selected (INT\_REFEN = 0). If reference output is required for testing before interfacing to the MCU, a low-cost reference can be used.

## 2.5.3 Using 4-V Reference for Analog Input Measurement

The differential input voltage range for ADS131A04 is -VREF / Gain to VREF / Gain. The internal reference can be programmed to either 2.442 V or 4 V. The dynamic range of the ADC can be improved by configuring VREF = 4 V. The  $VREF_4V$  bit can be set to 1, when VAVDD - VAVSS > 4.5 V. In the design the reference has been programmed to 2.442 V and tested. To use the 4-V reference, the ADC must be configured to measure bipolar input. By configuring VREF = 4 V, the input range can be increased from  $\pm 2.442$  V to  $\pm 4$  V, which increases the AC input range by  $\times 1.65$  compared to VREF = 2.442 V.

This configuration can be used when wider current ranges must be measured. The op amps used in the design can work for ±5 V. In this TI Design, ±5-V rails are available onboard. By making these simple changes in the design the input measurement range can be extended. Table 11 provides information to configure the power supply for different reference voltage configuration.

REFERENCE

POPULATE

DEPOPULATE

2.442 V

R186 and R187

—

4 V

Use TP25 and TP26 to connect external voltage up to ±5 V

R186 and R187

Table 11. Changes for Reference Configuration

# 2.5.4 Using ADS8688A for Diagnostics

The diagnostics feature is implemented with a unipolar 0- to 5-V input ADC. In applications with bidirectional input, ADS8688 or ADS8688A can be considered for diagnostics. ADS8688 and ADS8688A measure bidirectional input and operate on a single 5-V analog power supply input.

# 2.6 Board Design Guidelines

## 2.6.1 Delta-Sigma ADC

Recommendations:

- Partition the analog, digital, and power-supply circuitry into separate sections on the PCB.

- Use a single ground plane for analog and digital grounds.

- Place the analog components close to the ADC pins using short, direct connections.

- Keep the SCLK pin free of glitches and noise.

- Verify that the analog input voltages are within the specified voltage range under all input conditions.

- Tie unused analog input pins to GND.

- Provide current limiting to the analog inputs in case overvoltage faults occur.

- Use an LDO regulator to reduce ripple voltage generated by switch-mode power supplies. This

reduction is especially true for AVDD, where the supply noise can affect performance.

- Keep the input series resistance low to maximize THD performance.

- · Do not cross analog and digital signals.

- Do not allow the analog power supply voltages (AVDD AVSS) to exceed 3.6 V under any conditions, including during power up and power down when the negative charge pump is enabled.

- Do not allow the analog power supply voltages (AVDD AVSS) to exceed 6 V under any conditions, including during power up and power down when the negative charge pump is disabled.

- Do not allow the digital supply voltage to exceed 3.9 V under any conditions, including during power-up

#### 2.6.2 ADC101C021 SAR ADC

For best accuracy and minimum noise, the PCB containing the ADC101C021 must have separate analog and digital areas. The areas are defined by the locations of the analog and digital power planes. Both of these planes should be on the same board layer. A single, solid ground plane is preferred if digital return current does not flow through the analog ground area. Frequently, a single ground plane design uses a fencing technique to prevent the mixing of analog and digital ground currents. Separate ground planes must be used only when the fencing technique is inadequate. The separate ground planes must be connected in one place, preferably near the ADC121C021. Take special care to ensure that signals do not pass over power plane boundaries. Return currents must always have a continuous return path below their traces.

The ADC101C021 power supply must be bypassed with 4.7- $\mu$ F and 0.1- $\mu$ F capacitors as close as possible to the device with the 0.1- $\mu$ F capacitor located right at the device supply pin. The 4.7- $\mu$ F capacitor must be a tantalum type and the 0.1- $\mu$ F capacitor must be a low ESL type. The power supply for the ADC101C021 must be used only for analog circuits. Avoid the crossover of analog and digital signals and keep the clock and data lines on the component side of the board. The clock and data lines must have controlled impedances.

#### 2.6.3 AMC1200

See Section 10 Layout in the data sheet for the PCB design and layout guidelines.

## 2.6.4 CDCLVC1102PW

See Section 11 *Power Supply Recommendations* and Section 12 *Layout* in the data sheet for the PCB design and layout guidelines.

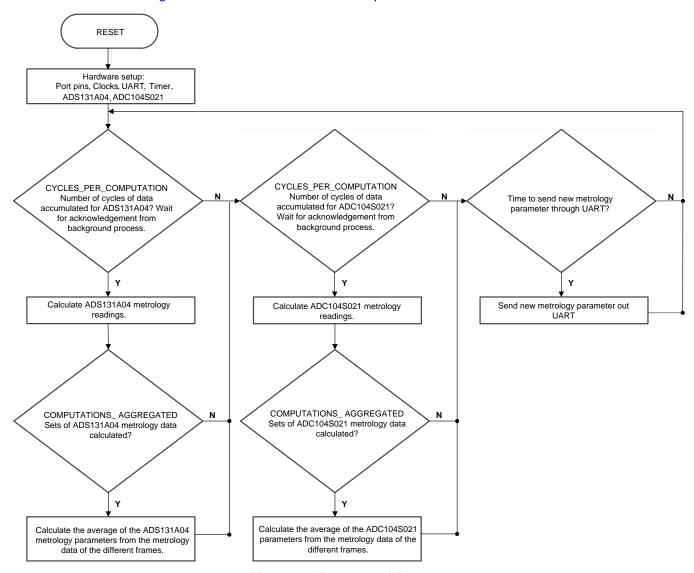

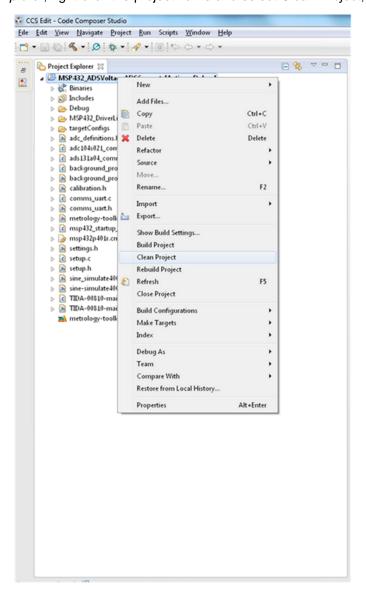

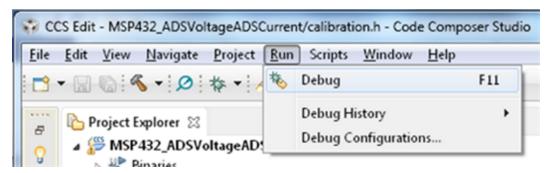

## 2.7 Software Implementation

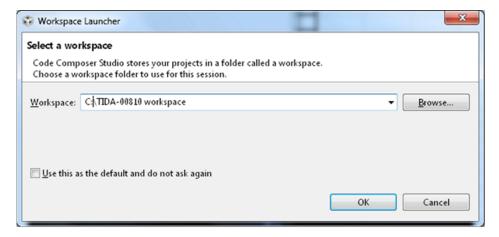

This section discusses the software implementation. The first subsection discusses the software used to setup the MSP432P401R peripherals, ADS131A04 ADC, and ADC104S021 ADC. Subsequently, the metrology software is described as two major processes: the foreground process and background process.

# 2.7.1 Setup Software

## 2.7.1.1 MCU Setup

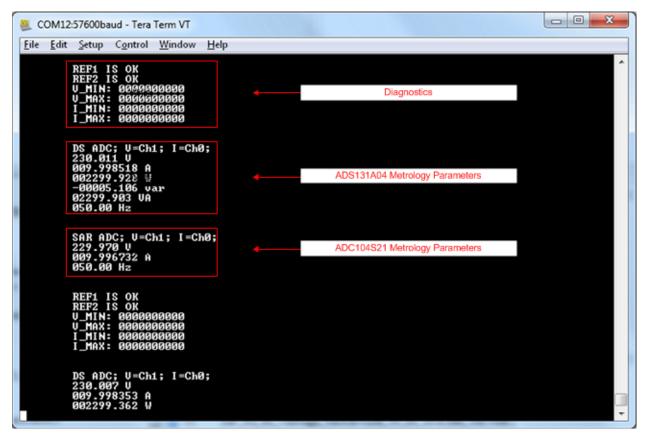

The MCU is used to set up the ADS131A04 and ADC104S021, calculate metrology parameters, and communicate these parameters through RS-232 to a terminal program.

## 2.7.1.1.1 GPIO, SPI, and UART Setup

For communication of the metrology parameters, a UART port is used on the MCU. The UART communication is set to a baud rate of 57600 with 8 data bits, no parity, and a 1 stop bit. By connecting the UART port pins to an isolated UART and then to the RS-232 board (such as TIDA-00163), the metrology parameters calculated by the MCU can be displayed by a PC using a terminal program.

For communication to the ADS131A04 and ADC104S021, two different SPI ports are used. The SPI clock for both of these ports is set to 3 MHz with the MSB shifted out first. These different SPI ports are independent of each other, but are used to communicate to the two devices of a particular ADC. For example, the ADS131A04 uses the same UCB0 port for the two ADS131A04 devices on this board. Similarly, the ADC104S021 uses the same UCB2 port for the two ADC104S021 devices.

In addition to the normal SPI lines used to communicate to the A04, the A04 devices also use additional GPIO lines for communication. One of these additional GPIO pins is used to provide a reset signal to the ADS131A04 to get it to a known state before sending commands. The second GPIO pin is connected to the DRDY pin of the ADS131A04. This pin is used to alert the MCU of a new set of ADS131A04 ADC samples now ready, so that the MCU can query the ADS131A04 devices for these new ADC samples. To immediately alert the MCU of the new ADC samples, the MCU GPIO pin connected to DRDY is configured as an interruptible input.

As a method to determine when there is an issue with the ADC reference of the A04 devices, the board also has comparators which compare the ADS131A04 references to a set voltage threshold. By connecting the output of these comparators to the corresponding interruptible GPIO pins on the MCU, the state of the two ADC references can be logged.

In the application, the GPIO associations listed in Table 12 are used.

**Table 12. GPIO Associations**

| PORT PIN                                     | FUNCTION                                                    |  |  |

|----------------------------------------------|-------------------------------------------------------------|--|--|

| RS-232 GPIO CONFIGURATION                    |                                                             |  |  |

| P3.2 (UCA2 UART port)                        | UART receive for RS-232 communication                       |  |  |

| P3.3 (UCA2 UART port)                        | UART transmit for sending metrology parameters using RS-232 |  |  |

| ADS131A04 GPIO CONFIGURATION                 |                                                             |  |  |

| P5.2                                         | ADS131A04 chip select                                       |  |  |

| P1.5 (UCB0 SPI port)                         | ADS131A04 SPI clock                                         |  |  |

| P1.6 (UCB0 SPI port)                         | ADS131A04 SPI input (SIMO)                                  |  |  |

| P1.7 (UCB0 SPI port)                         | ADS131A04 SPI output (MISO)                                 |  |  |

| P3.0                                         | ADS131A04 DRDY                                              |  |  |

| P4.5                                         | ADS131A04 RESET                                             |  |  |

| ADS131A04 REFERENCE CHECK GPIO CONFIGURATION |                                                             |  |  |

| P2.7                                         | ADCREF1 OK (for status of U2 reference)                     |  |  |

| P2.6                                         | ADCREF2 OK (for status of U4 reference)                     |  |  |

| ADC104S021 GPIO CONFIGURATION                |                                                             |  |  |

| P5.0                                         | Chip select 1 for U1 device on the board                    |  |  |

| P5.1                                         | Chip select 2 for U3 device on the board                    |  |  |

| P3.5 (UCB2 SPI port)                         | ADC104S021SPI clock                                         |  |  |

| P3.6 (UCB2 SPI port)                         | ADC104S021SPI input (SIMO)                                  |  |  |

| P3.7 (UCB2 SPI port)                         | ADC104S021SPI output (MISO)                                 |  |  |

# 2.7.1.1.2 Clocks

The MSP432P401R uses multiple clocks in this application. Table 13 lists the different clock settings used in this application.

**Table 13. Application Clock Settings**

| PORT PIN                                 | FUNCTION                                         |  |  |

|------------------------------------------|--------------------------------------------------|--|--|

| MASTER CLOCK (MCLK, CPU CLOCK)           |                                                  |  |  |

| Clock frequency                          | 48 MHz (clock divider = 1)                       |  |  |

| Number of flash wait states              | 2                                                |  |  |

| Clock source                             | MCU internal DCO                                 |  |  |

| SUBSYSTEM MASTER CLOCK (SMCLK)           |                                                  |  |  |

| Clock frequency                          | 24 MHz (clock divider = 2)                       |  |  |

| Clock source                             | MCU internal DCO                                 |  |  |

| AUXILIARY CLOCK (ACLK)                   |                                                  |  |  |

| Clock frequency                          | 32768 Hz                                         |  |  |

| Clock source                             | 32768 kHz crystal                                |  |  |

| RS-232                                   |                                                  |  |  |

| Speed                                    | 57600 baud                                       |  |  |

| Clock source                             | SMCLK                                            |  |  |

| TIMER FOR UPDATE OF METROLOGY PARAMETERS |                                                  |  |  |

| Timer used                               | Timer A0                                         |  |  |

| Clock source                             | ACLK                                             |  |  |

| Generated interval                       | 1 second (32768 counts)                          |  |  |

| Timer mode                               | Up mode                                          |  |  |

| ADC104S021 SPI CLOCK                     |                                                  |  |  |

| Clock frequency                          | 3 MHz (clock divider = 8)                        |  |  |

| Clock source                             | SMCLK                                            |  |  |

| Clock polarity                           | Inactive state is high (UCCKPL = 1)              |  |  |

| Clock phase                              | Data is valid on clock leading edge (UCCKPH = 0) |  |  |

| ADS131A04 SPI CLOCK                      |                                                  |  |  |

| Clock frequency                          | 3 MHz (clock divider = 8)                        |  |  |

| Clock source                             | SMCLK                                            |  |  |

| Clock polarity                           | Inactive state is low (UCCKPL = 0)               |  |  |

| Clock phase                              | Data is valid on clock leading edge (UCCKPH = 0) |  |  |

# 2.7.1.1.3 Direct Memory Access (DMA)

The DMA module is used to transfer all ADS131A04 and ADC104S021 ADC samples from these devices to the memory of the MCU with minimal bandwidth requirements from the CPU. To get the ADC sample data from the ADC devices, the MCU requires writing data to the SPI transmit buffers to activate the SPI clocks. The DMA module is used to not only transfer the received SPI data to memory, but also to write the dummy data to the SPI transmit buffers of the MCU so that the receive operations can be triggered. As a result, two DMA channels are used for each of SPI port used to communicate to an ADC; one channel is used to send the dummy data from MCU memory to the SPI transmit buffers and the other channel is used to move the received SPI data to the memory of the MCU. Once the transfer is complete, an interrupt is generated to complete any necessary post-transfer processing.

Table 14 lists the DMA channel associations.

**Table 14. DMA Channel Associations**

| DMA CHANNEL NUMBER | FUNCTION                                         |

|--------------------|--------------------------------------------------|

| 0                  | ADS131A04 SPI transmit (for triggering receive)  |

| 1                  | ADS131A04 SPI receive                            |

| 2                  | Not used                                         |

| 3                  | Not used                                         |

| 4                  | ADC104S021 SPI transmit (for triggering receive) |

| 5                  | ADC104S021 SPI receive                           |

| 6                  | Not used                                         |

| 7                  | Not used                                         |

## 2.7.1.1.4 Interrupt Priorities

The software has five interrupts that are prioritized. Table 15 lists these interrupt priorities.

**Table 15. Interrupt Priorities**

| INTERRUPT | SIGNIFICANCE                                                                                                    | PRIORITY CODE |

|-----------|-----------------------------------------------------------------------------------------------------------------|---------------|

| DMA1      | Transfer of ADS131A04 ADC samples to MCU memory is completed.                                                   | 0x20          |

| PORT3     | New ADS131A04 ADC samples are generated so the MCU can now query the ADS131A04 device for new ADC samples.      | 0x40          |

| DMA2      | Transfer of ADC104S021 ADC samples to MCU memory is completed.                                                  | 0x60          |

| TA0_0     | It is time to send a new metrology parameter for RS-232 communication.                                          | 0x80          |

| EUSCIA2   | Transmit buffer for RS-232 communication is empty so a new byte of the RS-232 communication packet can be sent. | 0x80          |

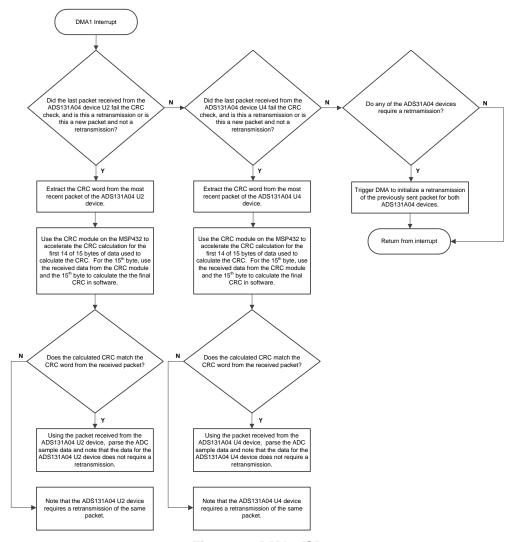

In Table 15, the interrupts with the lower priority code value have higher interrupt priority. In the software, communication to the terminal is a relatively low priority so the TAO\_0 and EUSCIA2 priorities have the highest priority code. The DMA2 interrupt has the next lowest priority because no time-critical processing is required in this interrupt. For the PORT3 interrupt, a high-priority interrupt is selected because this interrupt is where the majority of the sample processing is done. The DMA1 interrupt has the highest priority because a CRC is performed on the sample data received from the ADS131A04 in this interrupt; and if there are any CRC errors are present it must be detected as soon as possible so that the MCU can request and receive the sample data again before the next ADC sample is ready.

# 2.7.1.2 ADS131A04 Setup

For communication to the ADS131A04 devices, the device chaining feature of these devices is enabled so that communication to the two ADS131A04 devices is achieved transparently by concatenating the packets to be sent to the two A04 devices into one merged packet. The merged packed is sent out through the shared SPI lines. This method of chaining does not use two different chip select lines from the MCU like the method used for the ADC104S021 devices.

After reset, the MCU device first sends a reset signal to the ADS131A04 device to get it to a known state. After resetting the ADS131A04 devices, commands are sent to these devices to initialize them. These setup commands are sent out manually to the software so a DMA is not used to transfer this command data to the ADS131A04. The order of commands sent follows:

- Send an UNLOCK command to the ADS131A04 until an UNLOCK ACK is received from both ADS131A04 devices.

- Send a WAKEUP command to the ADS131A04 until a WAKEUP ACK is received from both ADS131A04 devices.

- 3. Send a command to set the ICLK divider of the A04 devices to 2. Keep sending this command until the appropriate ACK is received.

- 4. Send a command to set the OSR to 256 and the Modclk divider to either 8 (for 50-Hz nominal line frequency) or 6 (for 60 Hz nominal line frequency). This setting results in a sample rate of 4000 samples per second whenever the software is configured for a line frequency of 50 Hz and a sample rate of 5333.3 whenever the software is configured for a line frequency of 60 Hz. Keep sending this command until the appropriate ACK is received.

- 5. Send a command to the A04 devices to use the following configuration:

- · High-resolution mode

- Negative charge pump disabled

- Internal reference enabled

Keep sending this command until the appropriate ACK is received.

- Send a command to the A04 devices to use a fixed frame size of six words. In the hardware

configuration of the board, each word is set to be 24 bits long so this results in a communication frame

size of 18 bytes per ADS131A04 device. Keep sending this command until the appropriate ACK is

received.

- 7. Send a command to enable all of the ADS131A04 ADCs. Keep sending this command until the appropriate ACK is received.

- 8. Send a command to the A04 devices to use the following configuration:

- CRC is enabled on all bits received and transmitted.

- Time before the device asserts the done signal after the LSB is shifted out is set to 12 ns.

- Time before the device asserts Hi-Z on Dout after the LSB of the data frame is shifted out is 12 ns.

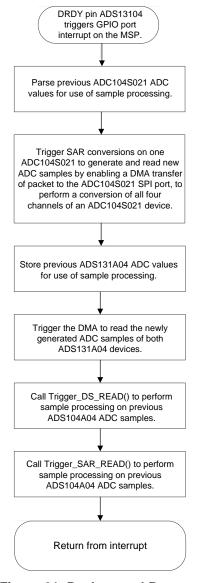

After the ADS131A04 devices are set up, the ADC alerts the MCU of new sample data that is available. This alert is done by providing GPIO interrupts from the DRDY pin of the ADS131A04. After receiving one of these interrupts, the MCU needs only to write dummy data into the SPI transmit buffers so that it can receive the ADC sample data from the ADS131A04 devices. The ADS131A04 automatically sends this sample data out through the SPI port so no command data must be sent to the ADS131A04 once set up.

Due to the chaining of the two ADS131A04 devices, the received data frame consists of the data frames of each A04 device. This means that a total of twelve 24-bit words (36 bytes) are sent from the ADS131A04 devices. The first six words sent correspond to the first ADS131A04 device (designated as U2 on the PCB) and the last six words correspond to the second ADS131A04 device (designated as U4 on the PCB). Figure 18 shows the order of words in a data frame that is received from each individual ADS131A04 device by the MCU.

Figure 18. Words Received From Each ADS131A04 Device