# TI Design: TIDA-00394 Dual Power Path Multiplexer Reference Design

# TEXAS INSTRUMENTS

# **TI Designs**

TI Designs provide the foundation that you need including methodology, testing, and design files to quickly understand, evaluate, and customize a system. TI Designs help you accelerate your time to market.

#### **Design Resources**

TIDA-00394 TPS3701 Reference Design Product Folder

#### **Circuit Description**

Many systems require a backup battery to provide power in the event of a power outage. Switching between the main power and the backup battery power without incurring significant efficiency degradation or cost is a tricky challenge. TIDA-00394 provides a high accuracy, low current solution for systems using a 12 V rail at a lower cost than most existing devices. The primary rail is intended to be the main power supply for the system, and is selected when the rail voltage is above the programmed undervoltage (UVLO) minimum, regardless of the other rail's status. When the primary rail goes below the UVLO minimum, the circuit will switch to the secondary (battery backup) rail if the secondary rail is above its programmed UVLO minimum. When both rails are below the UVLO minimum, neither rail is selected. The back-to-back PMOS switches allow for the input voltages of either rail to be higher than the opposite rail without any risk of conduction.

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

TINA-TI is a trademark of Texas Instruments WEBENCH is a registered trademark of Texas Instruments

# 1 Design Summary

The design requirements are as follows:

- Primary Power Rail Input Voltage:  $12 V \pm 10 \%$

- Secondary Battery Backup Rail Input Voltage: 14.4 V 12.6 V

- Primary Power Rail Under Voltage Lockout Threshold: 10.8 V  $\pm$  2 %

- Secondary Battery Backup Rail Under Voltage Lockout Threshold: 12.6 V  $\pm$  2 %

- Maximum Rail Current: 200 mA

- Multiplexer Current Consumption During Battery Selection Mode: 50 µA max.

| Parameters                                               | Goal   | Measured |  |

|----------------------------------------------------------|--------|----------|--|

| Primary Rail UVLO Threshold,<br>V <sub>UVLOPRI</sub>     | 10.8 V | 10.86 V  |  |

| Secondary Rail UVLO Threshold,<br>V <sub>UVLOSEC</sub>   | 12.6 V | 12.66 V  |  |

| Secondary Iq (Secondary VIN =<br>13.5 V, Primary = 0 V)  | 50 µA  | Α 28 μΑ  |  |

| Secondary Iq (Secondary VIN =<br>13.5 V, Primary = 12 V) | 300 µA | 278 µA   |  |

Table 1: Comparison of Design Goals and Measured Performance

# 2 Theory of Operation

The ubiquitous method for power rail selection between two separate power rails, i.e. a primary power supply and a battery backup, has traditionally been done with two diodes in series from each supply, or, power supply "OR-ing". OR-ing diodes provide an easy solution for the rail selection; however, poor efficiency performance and no enable/disable functionality make basic OR-ing hardly useful for many applications. Additionally, in circuits where the desired rail is not necessarily the highest voltage, such as some battery backup systems, basic OR-ing is not feasible because the battery can continuously backfeed the primary supply.

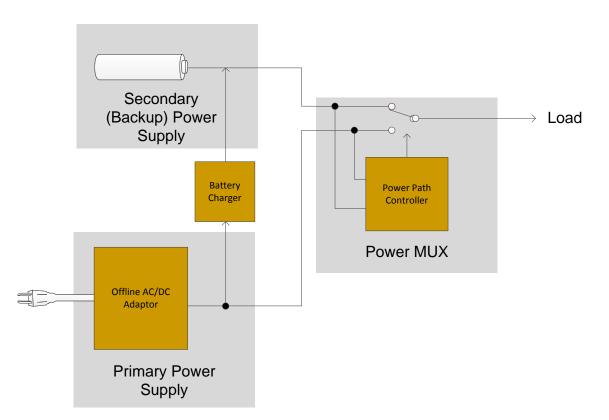

Offline systems that require constant power through power outages often use a battery for backup power when the primary (offline) power source goes down. **Figure 1** shows a common approach for backup multiplexer power – a charging circuit is used from the primary supply to ensure the battery is constantly charged during primary power operation. When the primary power falls below the minimum acceptable supply voltage, the backup battery is switched in to provide power to the load by a Power MUX and the battery charger is disabled. The Power MUX must switch the loads without allowing the supply voltage to the load to drop below critical levels, and operate at very low bias currents when the battery is in use in order to maximize the battery lifetime during power outages.

The TPS3701 is a high voltage window comparator well suited to provide the signal detection required for the power path controller circuitry. Its high voltage capability (36 V max.) yields a robust voltage range for 12 V to 24 V systems. The low Iq (7  $\mu$ A nominal) makes it capable of providing detection with minimal current consumption.

Figure 1: Battery Backup Block Diagram

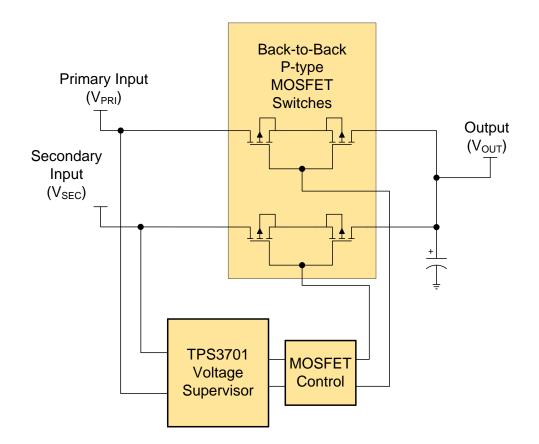

The implementation architecture for the power multiplexer can be seen in **Figure 2**. The switches are implemented with dual P-type MOSFETS with the sources connected to block any positive or negative current flow when the  $V_{GS}$  voltage of the MOSFET is higher than the respective device threshold. The TPS3701 is used to detect the voltages at the primary and secondary rails. The outputs of the voltage supervisor, along with additional circuitry, will control the gates of the switches, ensuring that only one channel is connected at a time and the desired priority logic is enforced.

Figure 2: Power Multiplexer Block Diagram

This simple approach can offer a lower current consumption and higher threshold accuracy than other more expensive solutions. The low nominal Iq of the TPS3701 (7  $\mu$ A) with the additional resistor current consumption of 21  $\mu$ A, gives a total current of only 28  $\mu$ A when the secondary input is selected. The threshold accuracy of the TPS3701 is 0.75%, and assuming 1% resistors are used for the sense resistor divider, the total accuracy of the threshold voltages are approximately 1.75%.

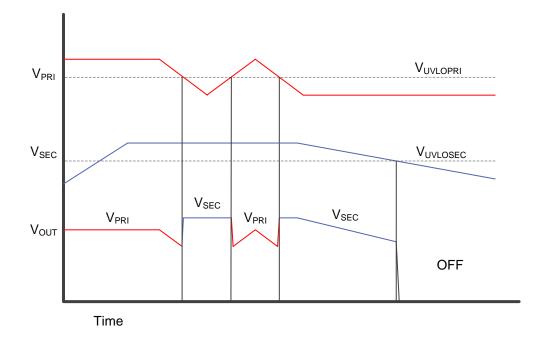

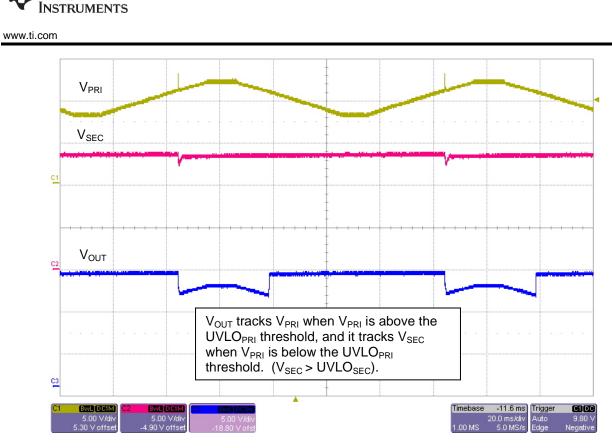

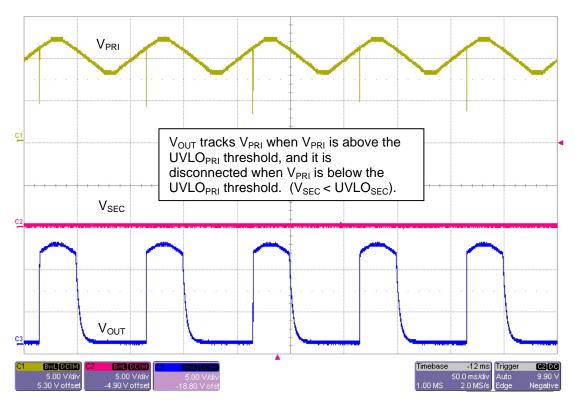

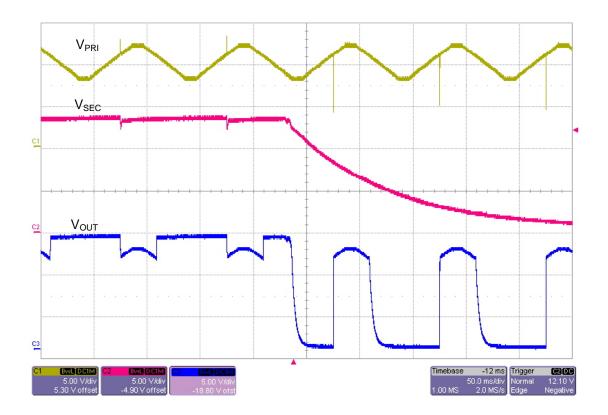

Figure 3: Functional Timing Diagram

The dual power path multiplexer presented in this design features the ability to allow either supply (battery or primary) to operate at a higher voltage. **Figure 3** shows the behavior of the circuit when the  $V_{PRI}$  or  $V_{SEC}$  voltages cross the UVLO threshold voltages. The rail selection is determined by the programmed UVLO threshold voltage levels at each rail with the primary rail given priority; see **Table 2** for the logic states.

| Primary Power Supply                    | Secondary Power Supply                  | Power to Load (V <sub>OUT</sub> ) |

|-----------------------------------------|-----------------------------------------|-----------------------------------|

| V <sub>PRI</sub> > V <sub>UVLOPRI</sub> | V <sub>SEC</sub> > V <sub>UVLOSEC</sub> | V <sub>PRI</sub>                  |

| V <sub>PRI</sub> > V <sub>UVLOPRI</sub> | V <sub>SEC</sub> < V <sub>UVLOSEC</sub> | V <sub>PRI</sub>                  |

| V <sub>PRI</sub> < V <sub>UVLOPRI</sub> | V <sub>SEC</sub> > V <sub>UVLOSEC</sub> | V <sub>SEC</sub>                  |

| V <sub>PRI</sub> < V <sub>UVLOPRI</sub> | V <sub>SEC</sub> < V <sub>UVLOSEC</sub> | Disconnect                        |

| Table 2: Powe | r MUX Rail | Selection | <b>Truth Table</b> |

|---------------|------------|-----------|--------------------|

|---------------|------------|-----------|--------------------|

#### 3 Component Selection

See the schematic in section 4 for the reference designators of each component.

#### 3.1 Threshold Selection

The UVLO threshold voltages are determined by selecting the resistor values for the divider network created by R1/R2 for the primary rail and R3/R4 for the secondary rail. Selecting high value resistors helps reduce the overall current consumption. For this design, R1 and R3 were chosen to be 2 M $\Omega$  and R2 and R4 were calculated from equation 1 below:

$$R_{2,4} = \frac{2 M\Omega \cdot V_{IT}}{V_{UVLO} - V_{IT}}$$

Where

R<sub>2.4</sub> = Resistance value of R2 for primary rail or R4 for secondary rail

$V_{IT}$  = Input threshold voltage for the TPS3701. For the primary rail,  $V_{IT}$  rising is 0.400 V. For the secondary rail,  $V_{IT}$  rising is 0.405 V

V<sub>UVLO</sub> = Desired undervoltage lockout threshold for primary or secondary rail.

#### Equation 1

For additional information on the TPS3701 voltage window comparator, see <u>SBVS240</u>.

#### 3.2 Pullup/Pulldown Resistor Selection

Resistors are required to discharge the PMOS gate to source voltage when the corresponding rail is turned off. Referring to Figure 4, R5, R6 and R7 pull up the gates of Q1, Q2 and Q3, respectively. R8 is used as a "pulldown" resistor – it slows the time that the gate of Q3 is pulled low, or, ON. In addition to current consumption, the timing of the switches are controlled by the pullup/pulldown resistors. A critical timing consideration occurs in the case that the primary rail shuts off and the secondary rail is turning on. In light load conditions, when  $V_{SEC} > V_{PRI}$ , both channels can be turned on simultaneously (known as "cross-conduction"), which can result in  $V_{PRI}$  being pulled high by  $V_{SEC}$ , and ultimately resulting in an oscillation. Selecting R8 to be at least a factor of 10 higher than R5 allows the enhancement of Q3 to be sufficiently delayed, eliminating any cross-conduction in this situation.

Note that delaying the switch conduction will result in a period of time where both switches are off, creating a "break-before-make" condition. During this time, all current to the load must be provided by the output capacitor, C1. C1 must be properly selected to ensure that the load voltage does not drop below the minimum required voltage at the maximum load during these events. Equation 2 can be used to approximate the time required for the secondary switch to enable.

$$t_{EN} = -\frac{R_1 R_2 C_{iss}}{R_1 + R_2} \ln(\frac{-2V_{th}}{V_{SEC}} - 1)$$

Where

$t_{EN}$  = Time from threshold detection to Q3 conduction.

$C_{ISS}$  = Input capacitance parameter of Q3

$V_{TH}$  = Minimum threshold voltage of Q3 (for SI3993 max = -1.0 V, min = -3.0 V)

#### Equation 2

For this design,  $t_{EN}$  is calculated to be 65 µs. Equation 3 gives an approximation of how much output capacitance is necessary to maintain the output voltage within a specified drop for a given  $t_{EN}$ . Note equation 3 assumes a resistive load.

$$C_L = -\frac{t_{EN}}{R_L} \frac{1}{\ln(1 - \frac{\%Drop}{100})}$$

Where

$t_{EN}$  = Time from threshold detection to Q3 conduction.

$C_L$  = Output Capacitance (C1)

R<sub>L</sub> = Output Load Resistance

%Drop = Percentage of output voltage drop that can be tolerated during  $t_{EN}$

#### **Equation 3**

For this design ( $t_{EN}$  = 65 µs,  $R_L$  = 65  $\Omega$ ), a 2.5% drop in VOUT during this time period results in a required 40 µF of capacitance; a 47 µF capacitor was selected.

# 3.3 Power Transistor Selection

Q1 and Q3 are required to conduct the full load current when their respective channels are selected, therefore the power loss associated with the resistance of the FET when fully enhanced ( $R_{DSON}$ ) must be considered when making the FET selection. The devices selected for this design yield a good compromise between size and  $R_{DSON}$ . In addition to  $R_{DSON}$ , the maximum and minimum  $V_{GS}$  and  $V_{DS}$  voltage rating of the device must exceed the maximum input voltage requirement. Devices that tolerate VIN\_MAX for the minimum  $V_{DS}$  rating are common; devices with higher  $V_{GS}$  ratings are less common. This is required for the primary channel because the gate will be pulled to ground when it is enabled, and with the source at VIN. The  $V_{GS}$  min./max. rating for Q1 and Q3 is  $\pm 20$  V.

# 3.4 Logic Transistor Selection

Q2 provides the logic selection of the primary rail, forcing a NAND operation between OUTA and OUTB with the output on the gate of Q3. This ensures that the secondary rail only turns on when both OUTA and OUTB are high. A dual small-signal FET with  $V_{GS}$  and  $V_{DS}$  ratings that exceed VIN\_MAX is suitable for this device; using a low- $R_{DSON}$  FET (i.e. a typical power FET) may have high output capacitance, or,  $C_{OSS}$ , which will slow the response of the gate signal on Q3. No significant current carrying capability is required for Q2.

# 3.5 Diode Selection

D1 provides the highest voltage between the primary or secondary rail to the TPS3701 and the gate pullup resistors. This is required to ensure Q1 and Q3 turn fully off when the opposite channel is enabled. In the case where a high voltage is selected on one channel (i.e. 14.4 V on  $V_{SEC}$ ) and the other channel is at a lower voltage (i.e. 10 V on  $V_{PRI}$ ), the gate pullup resistor must be pulled to the highest voltage because the source voltage on the disabled channel will track VOUT via the body diode of the disabled pass device.

The requirements of D1 are minimal. A small, low cost Shottky diode pair with connected cathodes and a maximum reverse voltage higher than the maximum input voltage is recommended.

# 4 Verification & Measured Performance

# 4.1 Schematic

Figure 4: Schematic

# 4.2 Scope Plots

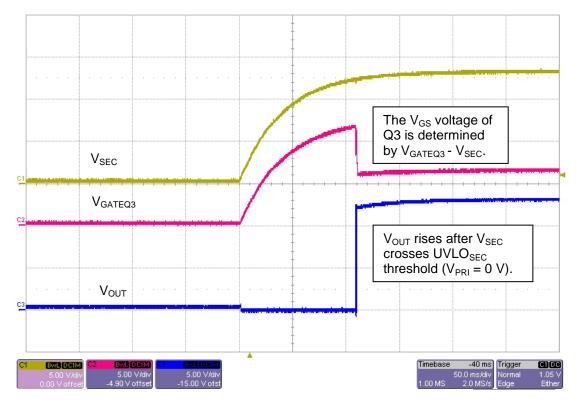

FIGURE 5: V<sub>SEC</sub> Startup. V<sub>PRI</sub> = 0 V, Load = 65  $\Omega$

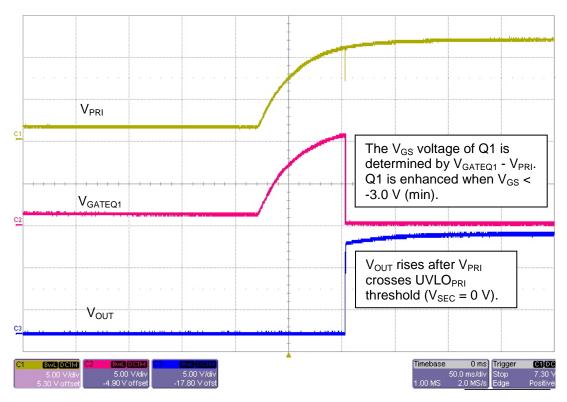

FIGURE 6: V<sub>PRI</sub> Startup. V<sub>SEC</sub> = 0 V, Load = 65  $\Omega$

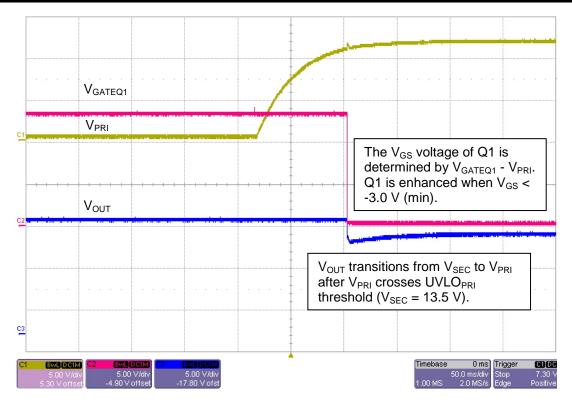

FIGURE 7: V<sub>PRI</sub> Startup. V<sub>SEC</sub> = 13.5 V, Load = 65  $\Omega$

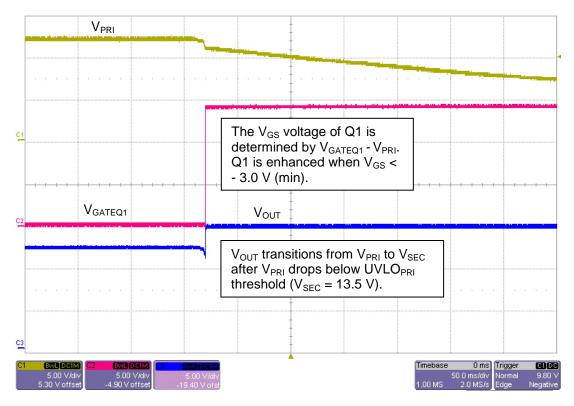

FIGURE 8: V<sub>PRI</sub> Falling. V<sub>SEC</sub> = 13.5 V, Load = 65  $\Omega$

FIGURE 9: V<sub>PRI</sub> Ramp. V<sub>SEC</sub> = 13.5 V, Load = 65  $\Omega$

FIGURE 10: V<sub>PRI</sub> Ramp. V<sub>SEC</sub> = 0 V, Load = 65  $\Omega$

**T**EXAS

FIGURE 11: V<sub>PRI</sub> Ramp. V<sub>SEC</sub> = 13.5 to 0 V, Load = 65  $\Omega$

4.3 BOM

|      | TEXAS<br>INSTRUMENTS                    |                                                                                                 |      |                         |                  |  |  |

|------|-----------------------------------------|-------------------------------------------------------------------------------------------------|------|-------------------------|------------------|--|--|

|      | Bill of Mat<br>TI Designs<br>TIDA-00394 | erials                                                                                          |      |                         |                  |  |  |

| Item | Designator                              | Description                                                                                     | RoHS | Manufacturer            | PartNumber       |  |  |

| 1    | C1                                      | CAP, AL, 47 μF, 25 V, +/- 20%, 0.3 ohm, TH                                                      | Y    | Panasonic               | EEU-FM1E470      |  |  |

| 2    | C2                                      | CAP, CERM, 0.1 µF, 50 V, +/- 10%, C0G/NP0, 0402                                                 | Y    | TDK                     | C1005X7R1H104K   |  |  |

| 3    | C3                                      | CAP, CERM, 0.1 µF, 50 V, +/- 10%, C0G/NP0, 0402                                                 | Y    | TDK                     | C1005X7R1H104K   |  |  |

| 4    | C4                                      | CAP, CERM, 0.1 µF, 50 V, +/- 10%, C0G/NP0, 0402                                                 | Y    | TDK                     | C1005X7R1H104K   |  |  |

| 5    | D1                                      | Diode, Schottky, 40 V, 0.2 A, SOT-323                                                           | Y    | Diodes Inc.             | BAS40W-05-7-F    |  |  |

| 6    | Q1                                      | MOSFET, P-CH, -30 V, -1.8 A, TSOP-6                                                             | Y    | VISHAY                  | SI3993DV-T1-E3   |  |  |

| 7    | Q2                                      | MOSFET, 2N-CH, 50 V, 0.51 A, SSOT-6                                                             | Y    | Fairchild Semiconductor | NDC7002N         |  |  |

| 8    | Q3                                      | MOSFET, P-CH, -30 V, -1.8 A, TSOP-6                                                             | Y    | VISHAY                  | SI3993DV-T1-E3   |  |  |

| 9    | R1                                      | RES, 2.0 M, 5%, 0.063 W, 0402                                                                   | Y    | Vishay-Dale             | CRCW04022M00JNED |  |  |

| 10   | R2                                      | RES, 66.5 k, 1%, 0.063 W, 0402                                                                  | Y    | Vishay-Dale             | CRCW040266K5FKED |  |  |

| 11   | R3                                      | RES, 2.0 M, 5%, 0.063 W, 0402                                                                   | Y    | Vishay-Dale             | CRCW04022M00JNED |  |  |

| 12   | R4                                      | RES, 76.8 k, 1%, 0.063 W, 0402                                                                  | Y    | Vishay-Dale             | CRCW040276K8FKED |  |  |

| 13   | R5                                      | RES, 49.9 k, 1%, 0.063 W, 0402                                                                  | Y    | Vishay-Dale             | CRCW040249K9FKED |  |  |

| 14   | R6                                      | RES, 499 k, 1%, 0.063 W, 0402                                                                   | Y    | Vishay-Dale             | CRCW0402499KFKED |  |  |

| 15   | R7                                      | RES, 100 k, 5%, 0.063 W, 0402                                                                   | Y    | Vishay-Dale             | CRCW0402100KJNED |  |  |

| 16   | R8                                      | RES, 499 k, 1%, 0.063 W, 0402                                                                   | Y    | Vishay-Dale             | CRCW0402499KFKED |  |  |

| 17   | U1                                      | 36V Window Comparator with Internal Reference for Over<br>and Under Voltage Detection, DDC0006A | Y    | Texas Instruments       | TPS3701DDCR      |  |  |

# 5 About the Author

Mike Hartshorne is an applications engineer in the Linear Power business unit. He has worked as an applications engineer in various power product lines and Analog-to-Digital Converter product lines. Mike received a BSEE from the University of San Diego and an M. Eng. from the University of Arizona.

# 6 References

- 1) TPS3701 Data Sheet

- 2) SI3993DV Data Sheet

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated