## Design Guide: TIDA-00176 Interface to Sin/Cos Encoders With High-Resolution Position Interpolation

## Description

This reference design is an EMC compliant industrial interface to Sin/Cos position encoders. Applications include industrial drives, which require accurate speed and position control. The design uses a 16-bit dual sample ADC with drop-in compatible 14- or 12-bit versions available, allowing for optimization of performance and cost. TIDA-00176 is also provides a simple to connection to external processors using SPI and QEP interfaces and allows for the use of optional, embedded ADCs. For quick evaluation an example firmware for Piccolo<sup>™</sup> F28069M MCU LaunchPad<sup>™</sup> is provided, which outputs the measured angle from the Sin/Cos encoder with up to 28-bit resolution through the MCU's USB virtual COM port.

## Resources

| TIDA-00176                    | Design Folder  |

|-------------------------------|----------------|

| ADS8354, THS4531A             | Product Folder |

| TLV3202, OPA2365              | Product Folder |

| REF2033, TPS54040A            | Product Folder |

| TIPD117                       | Tool Folder    |

| Piccolo F28069M MCU LaunchPad | Tool Folder    |

Ask our TI E2E<sup>™</sup> support experts

## Features

- EMC-Compliant Industrial Interface Design for Sin/Cos Encoders With 1-V<sub>PP</sub> Differential Output at 2.5-V Offset, Input Frequencies up to 500 kHz

- High-Resolution Interpolated Position, up to 28-bit Resolution, Cable Length Tested up to 70 m

- Dual Analog Signal Chain for Simultaneous Use of 16-bit Dual SAR ADC and MCU Embedded ADCs Allows for Evaluation of Both Paths and Optimization of One Path for Increased Noise Immunity With Reduced Bandwidth

- Easy to Connect to MCU With SPI and QEP Interface and Option for Cost Optimization Pending Resolution Requirements, Thanks to Drop-in Compatible 14- or 12-bit ADC

- Example Firmware for C2000<sup>™</sup> MCU With High-Resolution Angle Calculated at 16-kHz and Angle Data Send Through USB Virtual COM Port for Easy Performance Evaluation

- Tested for IEC61000-4-2, 4-4, and 4-5 (ESD, EFT, and Surge EMC Immunity Requirements)

## Applications

- AC Drives

- Precision Speed-Variable Drives

- Servo Drives

## **1 System Description**

## 1.1 Design Overview

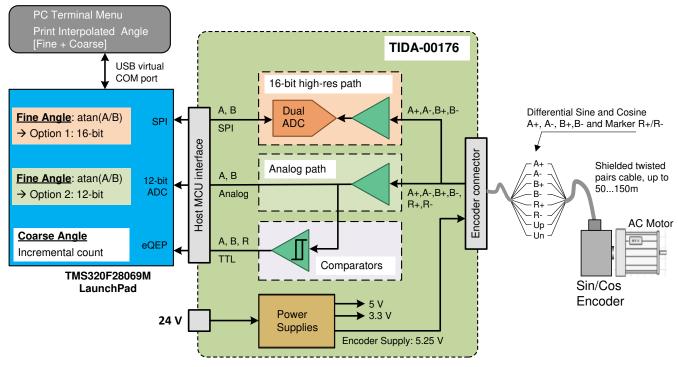

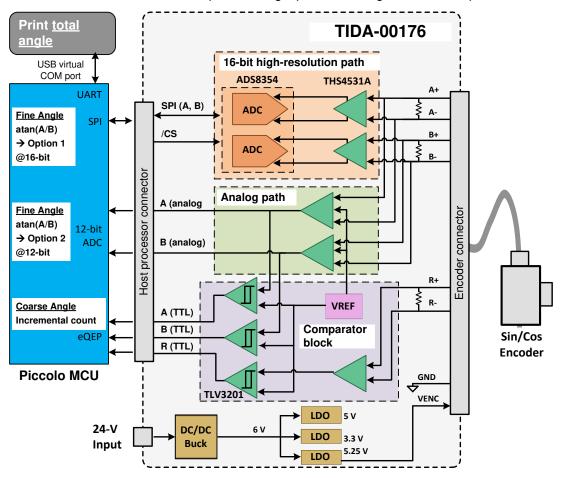

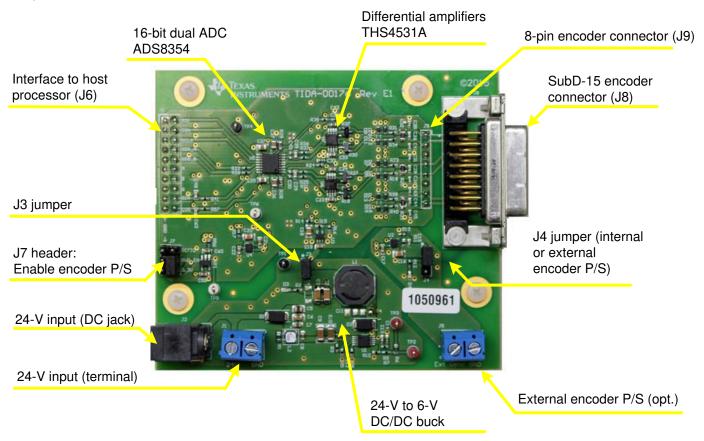

This TI design implements an industrial temperature, EMC-compliant interface to Sin/Cos incremental position encoders with 1-V<sub>PP</sub> differential analog output signals, frequencies up to 500 kHz, and a 5-V supply voltage. The major building blocks of this TI design are the dual path analog signal chain, the high-speed comparator block, the power management block, and the interfaces to the Sin/Cos encoder as well as the interface to a host microcontroller for digital signal processing and high-resolution position calculation. A simplified system block diagram is shown in Figure 1-1, with the TI hardware design represented by the box in light green.

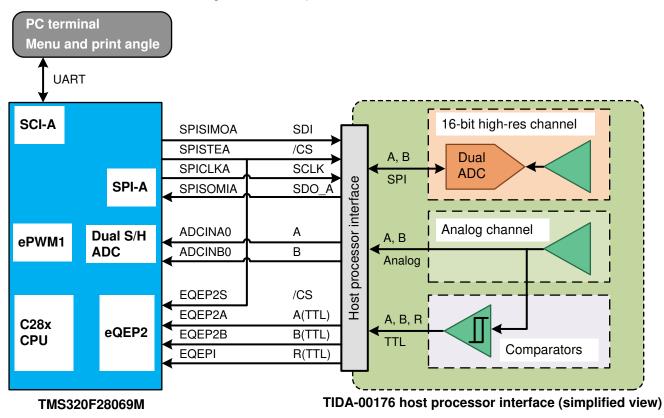

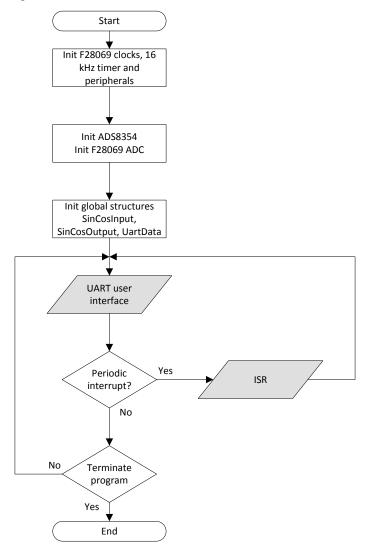

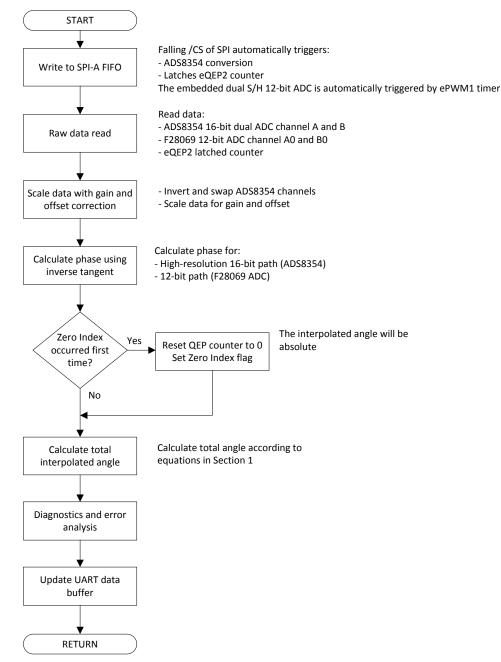

To allow for an easy evaluation of this design guide, an example firmware is provided for the TMS320F28069M InstaSPIN<sup>™</sup>-MOTION LaunchPad. The TMS320F28069M calculates the high-resolution angle position for both analog signal paths. One path is leveraging the external 16-bit dual ADC through SPI. The other path is using the F28069M embedded dual S/H 12-bit ADC. The angle is calculated with up to 28-bit resolution and output for evaluation through USB virtual COM port.

Figure 1-1. Simplified System Block Diagram of TIDA-00176 With Piccolo F28069M LaunchPad

The analog signal chain provides  $120 \cdot \Omega$  termination with EMC protection. The differential 1 V<sub>PP</sub> sine and cosine input signals are amplified and level-shifted, respectively. A dual signal path option is provided with an onboard high-speed, high-resolution dual 16-bit simultaneous sampling ADC with SPI and dual analog single-ended outputs with a 1.65-V bias voltage to interface to a microcontroller with embedded dual S/H ADC like the C2000<sup>TM</sup> Piccolo Real-time MCU family.

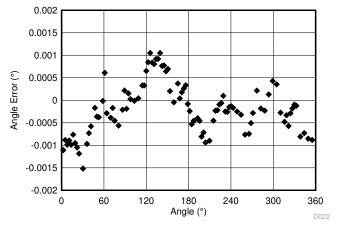

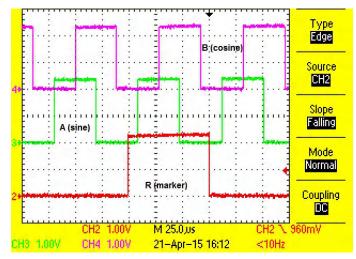

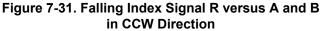

The comparator block features high-speed, low propagation delay and adjustable hysteresis for better noise immunity and converts the analog signals A, B, and the marker R into digital signals with a 3.3-V TTL-level to interface to a quadrature encoder pulse module like the QEP module on the C2000 Piccolo MCU.

The onboard wide-input range 24-V power supply provides the necessary voltages for analog signal chain as well as the 5.25-V supply voltage for the Sin/Cos encoder.

The Sin/Cos encoder can be either connected to a 15-pin shielded Sub-D connector or an 8-pin header. The interface to the host processor provides the analog single-ended signals A and B scaled from 0 to 3.3 V with a 1.65-V bias voltage, the digital signals for SPI and A, B, and R with a 3.3-V I/O. The digital output signals A, B, and R are often referred to as **ABZ** signals.

The design is tested for IEC61000-4-2, 4-4, and 4-5 (ESD, EFT, and Surge) as specified in the IEC 61800-3 standard for EMC immunity requirements and specific test methods applicable in adjustable speed, electrical-power drive systems.

## 1.2 Analog Sin/Cos Incremental Encoder

Incremental rotary or linear position encoders are used in many applications to measure angular or linear position and speed. Depending on the application, encoders with TTL/HTL-output signals or analog sinusoidal output signals are used. The latter is often referred as Sin/Cos encoder. Analog Sin/Cos incremental encoders enable high-resolution position measurement. The high quality of the sinusoidal incremental signals permits high interpolation factors for digital speed control. Application areas include electrical motors, machine tools, printing machines, woodworking machines, textile machines, robots, and handling devices, as well as various types of measuring, testing, and inspection devices.

## 1.2.1 Sin/Cos Encoder Output Signals

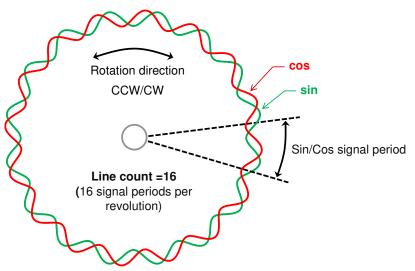

There are typically two sensing methods implemented with encoders, either based on optical or inductive sensing. With optical rotary encoder, the encoder disc modulates a light beam whose intensity is sensed by photo-electrical cells. These produce two 90-degree phase shifted sinusoidal incremental signals A and B. B lags A with clockwise rotating viewed from the shaft of the encoder. The number of periods of the signals A and B over one mechanical revolution equals the line count N of the encoder. A further track carries the reference marker R, which occurs once per mechanical revolution. The reference marker allows for an absolute angle position measurement.

#### Figure 1-2. Simplified Sine and Cosine Signals for a Sin/Cos Encoder Over One Mechanical Revolution for a Line Count of 16

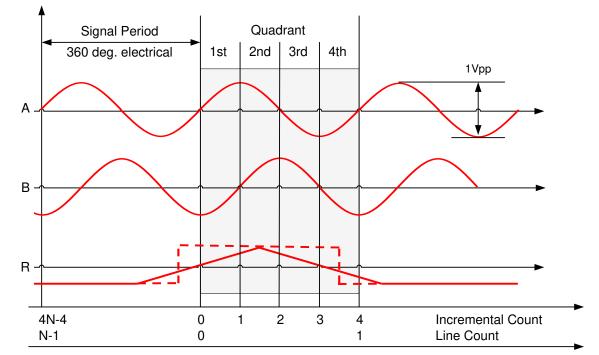

Sin/Cos encoders with a  $1-V_{PP}$  interface provide the differential analog output signals A (A+, A–) and B (B+, B–) with 1 V<sub>PP</sub> and typically a 2.5-V DC-offset. The differential reference mark signal R (R+, R-) is typically slightly lower amplitude and the peak occurs only once per revolution. Figure 1-3 shows the differential output signals A, B, and R. Note that A, B, and R represent the differential signal of A+ minus A–, B+ minus B–, and R+ minus R–, respectively.

Figure 1-3. Output Voltage Signals A, B, and Marker R of Sin/Cos-Encoders With N Line Counts per Revolution

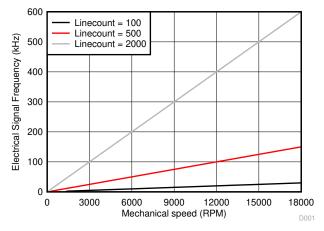

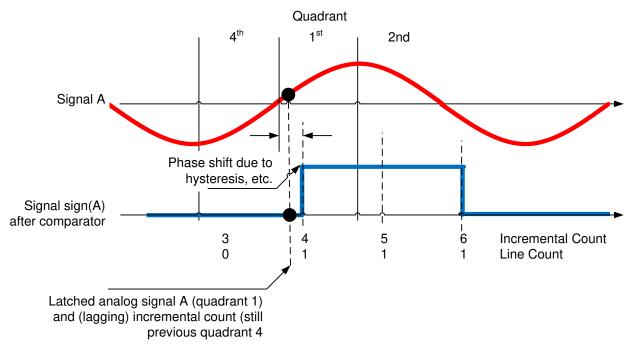

The frequency of the of the Sin/Cos encoder's differential output signal depends on the line count of the encoder as well as the mechanical speed, as outlined in Equation 1:

$$f_{A,B}[Hz] = N \times v[rpm] \times \frac{1}{60}$$

(1)

N represents the Sin/Cos encoder line count and v the encoder shaft mechanical speed in rpm.

Figure 1-4 provides an overview on the output frequency for encoders with line counts N = 100, 1000, and 2000 versus the mechanical speed.

For example, a Sin/Cos encoder with a line count of N=2000 running at a mechanical speed of 12000 rpm, outputs the signals A and B with a frequency of 400 KHz.

## 1.2.2 Sin/Cos Encoder Electrical Parameter Examples

To understand the requirements for an electrical interface module to Sin/Cos encoders, some example industrial Sin/Cos encoder models have been analyzed. The corresponding parameters are listed in Table 1-1.

| SIN/COS ENCODER MODEL | SUPPLY VOLTAGE | CURRENT CONSUMPTION |

|-----------------------|----------------|---------------------|

| 1                     | 5-V ± 0.5-V DC | < 120 mA            |

| 2                     | 5 V ± 10%      | 150 mA              |

| 3                     | 5 V ± 5%       | 70 mA (min)         |

#### Table 1-1. Encoders Supply Voltage Example

The power supply of the Sin/Cos encoder needs to be within this specification.

The analog signal chain need to be specified to at least meet the requirements listed in Table 1-2 with respect to signal amplitudes, offset, and maximum frequency.

| SIN/COS ENCODER<br>MODEL | SIGNAL LEVEL A, B                                      | DC OFFSET     | LINE COUNT N | LIMIT FREQUENCY<br>(–3 dB) |

|--------------------------|--------------------------------------------------------|---------------|--------------|----------------------------|

| 1                        | 0.6 to 1.2 V <sub>PP</sub> , 1 V <sub>PP</sub> typical | 2.5 V ±0.5 V  | 50 to 5000   | ≥180 kHz                   |

| 2                        | 1 V <sub>PP</sub> (+20%,-40%)                          | 2.5 V ±0.5 V  |              | 120 kHz                    |

| 3                        | 1 V <sub>PP</sub> (±10%)                               | 2.5 V ±100 mV | 1024 or 2048 | 400 kHz                    |

#### Table 1-2. Encoder Output Signals A, B Example

#### Table 1-3. Encoder Output Signals Marker R Example

| SIN/COS ENCODER MODEL | USABLE COMPONENT G AT<br>REFERENCE MARK              | QUIESCENT VALUE H OUTSIDE REFERENCE<br>MARK | DC OFFSET |

|-----------------------|------------------------------------------------------|---------------------------------------------|-----------|

| 1                     | 0.5 $V_{\text{PP}}$ typical, 0.2 $V_{\text{PP}}$ min | –1.7 V                                      | 2.5 V     |

#### Table 1-4. Encoder Mechanical Parameter Example

| SIN/COS ENCODER MODEL | SYSTEM ACCURACY        | SHAFT MECHANICAL SPEED |

|-----------------------|------------------------|------------------------|

| 1                     | 1/20 of grating period | < 16000 rpm            |

## 1.3 Method to Calculate High-Resolution Position With Sin/Cos Encoders

## 1.3.1 Theoretical Approach

#### 1.3.1.1 Overview

From a hardware perspective typically two approaches can be realized, which impact mainly the requirements for the A/D converter.

With the "over-sampling method", both sine and cosine signal would be sampled at least four times higher than the maximum sine and cosine frequency. The incremental count as well as the phase calculation would be done by subsequent digital signal processing on a host processor. That method would not need comparators, but rather high-speed dual sampling ADCs.

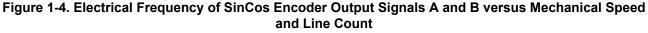

The typically used "under-sampling" method uses separate hardware blocks to calculate the incremental count and the interpolated incremental phase. The advantage of that method is that the sampling frequency and bandwidth of the ADC can be lower compared to the first method, as it does not impact the incremental count but only the interpolated phase. However, the under-sampling method requires a comparator each, for sine and the cosine, to generate the digital quadrature encoded signals A and B, which drive a directional up and down counter, often referred to as quadrature encoded pulse counter. The analog bandwidth of the dual sampling ADC needs to be at least equal to the maximum sine/cosine frequency. The under-sampling method is outlined in Figure 1-5.

Figure 1-5. Signal Processing Block Diagram for Interpolated Angle Calculation

The total interpolated angular position is composed of coarse and fine angle. The interpolated angle is determined by the actual incremental line count and the phase within this incremental line. The phase within the incremental line is derived from the analog sine and cosine signals A and B at any specific time instant. Both the actual incremental count and the actual analog sine and cosine signals have to be latched at the same time, hence synchronously. The incremental line provides the fine angle. The total interpolated angle is a compound of the sine and cosine within that incremental line provides the fine angle. The total interpolated angle is a compound of the coarse and fine angle, as shown with a simplified block diagram in Figure 1-5. The corresponding Equation 2 to Equation 4 are explained in the next paragraph.

#### 1.3.1.2 Coarse Resolution Angle Calculation

The incremental count and hence the incremental coarse angle can be determined by a counter, that counts up when A is the leading sequence and counts down when B is the leading sequence. When digitized, both edges of A and B are counted. Hence one incremental count is equivalent to a 90° phase shift of both signals A and B, see Figure 1-3. The incremental count starts from 0 with the maximum incremental count incr<sub>MAX</sub> per Equation 2, where N is the line count:

$$\operatorname{incr}_{MAX} = (4 \times N) - 1 \tag{2}$$

The incremental position  $\Phi_{incr}$  can be calculated as:

$$\Phi_{\text{incr}} \left[ \text{deg} \right] = \frac{360}{4 \times \text{N}} \times \text{incr} + \Phi_0$$

(3)

Where incr is the actual incremental count, N is the total line count and  $\Phi_0$  the zero angle, determined by the reference marker R, if used.

#### 1.3.1.3 Fine Resolution Angle Calculation

The phase  $\phi_{A,B}$  of the sinusoidal signals A and B is used to interpolate the angle between two consecutive line counts, or four incremental steps, which are equivalent to each other. The phase  $\phi_{A,B}$  can be calculated with Equation 4:

$$\phi_{A,B} \left[ deg \right] = \begin{pmatrix} 90^{\circ} + \tan^{-1} \left( \frac{B}{A} \right) & \text{if } A \ge 0 \\ \\ 270^{\circ} + \tan^{-1} \left( \frac{B}{A} \right) & \text{if } A < 0 \end{cases}$$

(4)

Since only the ratio of the amplitudes of A and B is used, which are a common function of the encoder's rotation speed and supply voltage, this result does not affect the result.

#### 1.3.1.4 Interpolated High-Resolution Angle Calculation

When the incremental count incr is matched to the phase  $\phi_{A,B}$  according to Table 1-5, the total interpolated angle  $\Phi_{TOTAL}$  is calculated with line count N as:

$$\Phi_{\text{TOTAL}} \left[ \text{deg} \right] = \frac{360^{\circ}}{N} \left( \left( \text{incr} >> 2 \right) + \left( \times \frac{\phi_{\text{A,B}}}{360^{\circ}} \right) \right) + \Phi_{0}$$

(5)

7

CAUTION

The sinusoidal signals A and B and the incremental count incr must be latched simultaneously.

#### Table 1-5. Example for Relation between Incremental Count to Phase and Phase Quadrant

| INCREMENTAL COUNT | PHASE             | QUADRANT |

|-------------------|-------------------|----------|

| 0                 | 0 ≤ Phase < 90    | 1        |

| 1                 | 90 ≤ Phase < 180  | 2        |

| 2                 | 180 ≤ Phase < 270 | 3        |

| 3                 | 270 ≤ Phase < 360 | 4        |

| 4                 | 0 ≤ Phase < 90    | 1        |

#### 1.3.1.5 Practical Implementaion for Non-Ideal Synchronization

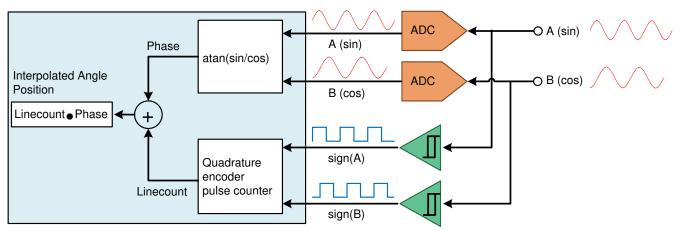

Practically, the digitized signals  $A_{TTL}$  and  $B_{TTL}$ , which are input to the quadrature encoder pulse counter, typically have a phase shift compared to the analog signals. This is mainly due to hysteresis and propagation delay of the comparators, as well as due to non-ideal synchronization between latching the incremental count and sampling the analog inputs A and B.

The impact of the hysteresis on the phase shift is almost independent of the signal frequency, but almost inverse proportional to the signal amplitude. The impact of a propagation delay and a non-ideal synchronization between sampling the analog signal and latching the incremental count is almost independent of the amplitude, but proportional to the frequency. Therefore, the maximum phase shift occurs at maximum Sin/Cos encoder frequency with minimum amplitude.

This means that at each transition to the next quadrant, the incremental counter is not updated immediately because of the phase lag, for example, as shown for the first quadrant in Figure 1-6.

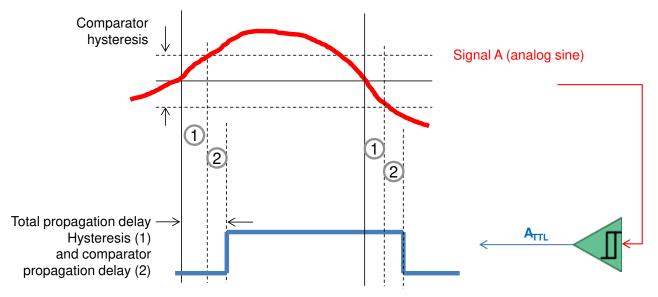

#### Figure 1-6. Phase Shift of A<sub>TTL</sub> versus the Analog Signal A, due to Phase Lag

The factors outlined cannot be omitted and hence a method needs to be applied to detect and correct these corner cases. Due to the ambiguity or the lower two bits of incremental line count and the analog phase, a correction method as outlines in Table 1-6 can be applied, as long as the phase shift remains less than ±90°.

Since only the phase information is used to identify the quadrant, there are only two exceptions to consider, which occur during the transition from quadrant 4 to quadrant 1, or quadrant 1 to quadrant 4, depending on the rotation direction.

| INCREMENTAL COUNT [incr] | PHASE φ <sub>A,B</sub>  | CORRECTION METHOD                                         |  |

|--------------------------|-------------------------|-----------------------------------------------------------|--|

| incr%4 = 3               | () < Dhase < 0()        | incr = incr+1<br>if incr > 4 × N $-$ 1 then incr = 0      |  |

| Incr%4 = 0               | $2/0 \le Phase \le 360$ | incr = incr-1<br>if incr < 0 then incr = $4 \times N - 1$ |  |

| Table | 1-6. | Correction | Method |

|-------|------|------------|--------|

|-------|------|------------|--------|

#### CAUTION

The correction method only works if the phase shift between the analog A and B and the digital signal  $A_{TTL}$  and  $B_{TTL}$  is less than ±90°.

A worst case calculation for this design is outlined in Section 1.4.

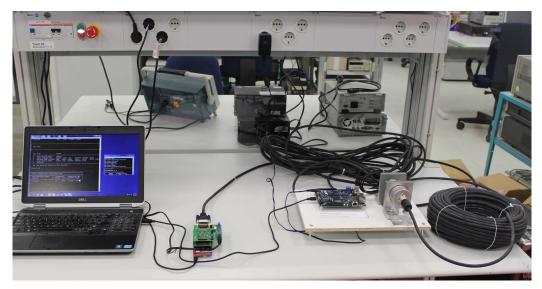

#### 1.3.1.6 Resolution, Accuracy, and Speed Considerations

The ideal interpolated angle resolution is a function of the Sin/Cos encoder's line count and the resolution of the dual ADC. The equivalent interpolated angle resolution can be calculated as:

$\Phi_{\text{RESOLUTION}}[\text{bit}] = \log 2(2 \times \text{N}) + \text{ADC}_{\text{RESOLUTION}}[\text{bit}]$

(6)

9

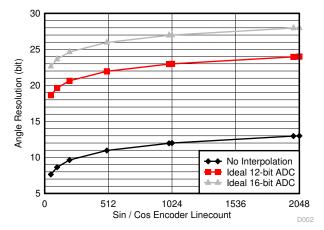

Figure 1-7 illustrates the achievable interpolated angle resolution as a function of the line count for no interpolation, interpolation with an ideal 12-bit, and a 16-bit dual ADC.

Figure 1-7. Ideal Interpolated Angle Resolution versus Line Count versus ADC Resolution

The ideal resolution with a Sin/Cos encoder with 2048 line counts using a 16-bit dual ADC equals 28-bit, if the ADC's full-scale input range is used.

This high resolution is typically not required for position control, but for very precise speed control, especially at lower mechanical speed. Figure 1-8 outlines the ideal speed resolution derived at a sample rate of 1.6 kHz without low-pass filtering. This assumes the industrial drive's speed closed-loop control runs 10 times lower than the current closed-loop control and PWM at 16 kHz.

Figure 1-8. Ideal Speed Resolution versus Mechanical Speed at 1.6-kHz Sample Rate and Encoder With 1000 Line Count

Practically, low-pass filtering will be applied and improves resolution and immunity to noise, but with a filter specific propagation (group) delay or latency.

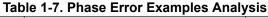

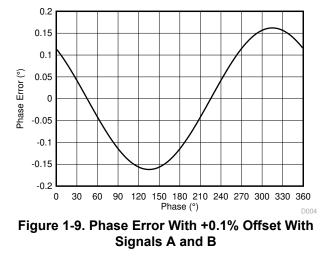

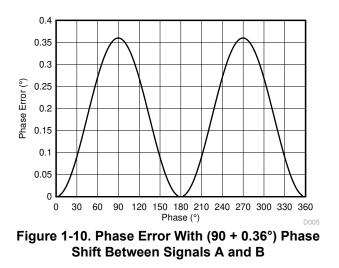

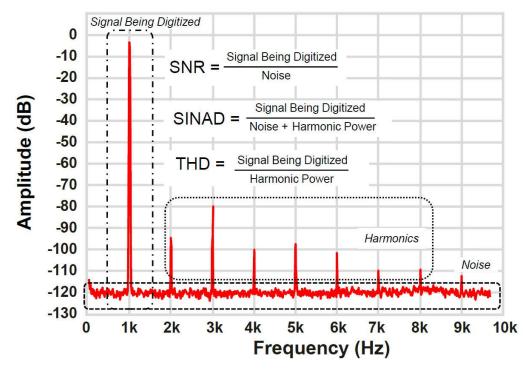

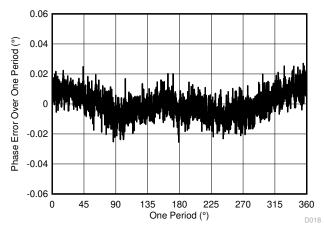

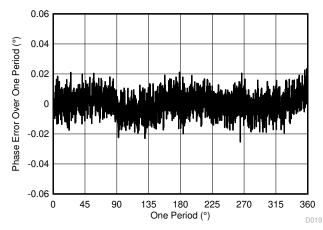

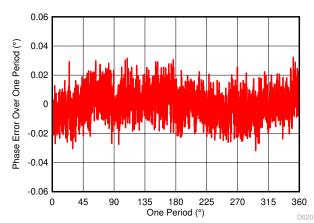

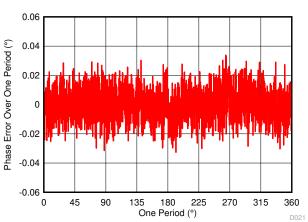

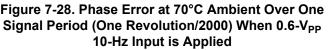

Following the ideal resolution, Table 1-7, Figure 1-9, and Figure 1-10 outline the impact of a quantization, offset, gain, or phase error to the interpolated angle.

| ERROR SOURCE                              | EXAMPLE           | PHASE ERROR [MAX] |  |

|-------------------------------------------|-------------------|-------------------|--|

| Quantization of signals A and B           | 12-bit            | 0.012% [0.045°]   |  |

| Offset error of signals A and B           | 0.1%              | 0.05% [0.18°]     |  |

| Gain error of signals A and B             | 0.1%              | 0.04% [0.15°]     |  |

| Phase shift between input signals A and B | 90 + 0.36° [0.1%] | 0.1% [0.36°]      |  |

Note that the phase error introduced due to a phase shift between the input signals A and B exhibits the double period. This signature can be leveraged for detection and correction of a constant phase shift using signal processing algorithms. However, these are beyond the scope of this design guide.

## 1.4 Sin/Cos Encoder Parameters Impact on Analog Circuit Specification

To specify the analog circuit, as outlined in Section 4, the following Sin/Cos encoder signal parameters (including support for longer cables) have been considered.

- Sin/Cos minimum and maximum peak-to-peak amplitude: Differential 0.3 to 1.2 V<sub>PP</sub>, full-scale input range with at least 50% headroom (1.8 V<sub>PP</sub>)

- Sin/Cos offset voltage range: 2.5 V ±1V

- Sin/Cos maximum frequency: 500 kHz

- Sin/Cos maximum slew rate: >2 V/µs

- Sin/Cos line termination: 120-Ω ±1%

- Encoder supply voltage and current: 5 V ±5%, 200 mA

#### 1.4.1 Analog Signal Chain Design Consideration for Phase Interpolation

The high-resolution analog signal chain shall support 16-bit resolution to provide a high interpolated angle resolution, especially for precision speed control.

The differential analog amplifier's AC noise floor and distortions should match 16-bit resolution. With respect to a  $1-V_{PP}$  input, this equals around 15  $\mu$ V.

- Input voltage noise: 15 µV/SQRT(1 MHz) = 15 nV/SQRT(Hz)

- Input current noise: 15 μV/SQRT(1 MHz)/R<sub>INPUT</sub>, for R<sub>INPUT</sub> = 1k equals 15 pA/SQRT(Hz)

Gain and offset are rather DC parameters and their drift is typically very slow as mainly related to temperature or aging. Initial offset and gain can be calibrated during initialization, with specific algorithms even during run-time. Therefore, the requirements for these parameters can be slightly relaxed. The gain and offset drift over temperature shall be each in the range of 10 LSB. With respect to a 1-V<sub>PP</sub> input signal, this equals around 150  $\mu$ V.

- Offset drift [0 to 85°C]: 150 μV/85°C ~ 2 μV/°C

- Gain drift: [0 to 85°C]: 160 ppm/85°C ~ 2 ppm/°C

For the gain setting, matched resistors (same package) are recommended.

#### 1.4.2 Comparator Function System Design for Incremental Count

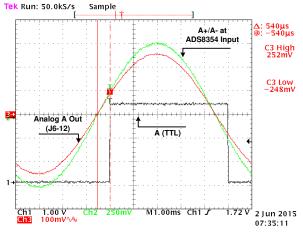

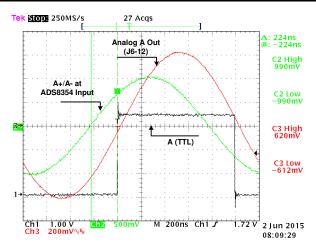

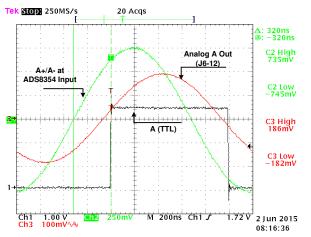

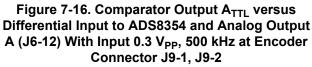

Referring back to Figure 1-5: The total propagation delay between the analog signal and the digital signals ATTL and BTTL at 500 kHz should be less than 90°, equivalent to 500 ns. The hardware should not contribute more than around 50 to 70%; equivalent to 250 to 350 ns to leave headroom for example hardware related offset and temperature drift, phase shift due to analog low-pass/decoupling filters and non-ideal synchronization in the subsequent host processor.

The hysteresis contribution to the delay with a 160-mV hysteresis ( $\pm$ 80 mV) at a minimum 0.3-V<sub>PP</sub> input to the comparator is around 32 degree, or 180 ns at a 500-kHz signal frequency.

The comparator's propagation delay adds on top. The lower the comparator's propagation delay the more headroom is available to increase the hysteresis or apply other means to increase the system's noise immunity.

Figure 1-11. Signal Delay on Comparator With Hysteresis

## 2 Design Features

As outlined in Section 1, this TI design realizes an industrial temperature range, EMC-compliant interface to Sin/Cos incremental position encoders with differential  $1-V_{PP}$  analog output signals A, B, and index marker R with input frequencies up to 500 kHz and a 5-V supply voltage. The major building blocks of this TI design are the dual path analog signal chain, the high-speed comparator block, the power management block and the interfaces to the Sin/Cos encoder as well as the interface to a host microcontroller for digital signal processing and high-resolution position calculation.

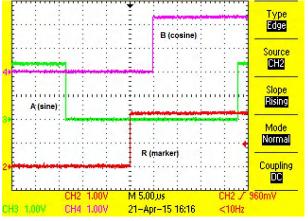

To allow for easy evaluation of this TI design, an example firmware is provided for the TMS320F28069M InstaSPIN-MOTION LaunchPad. The TMS320F28069M calculates the high-resolution angle position for both signal paths, using the external 16-bit ADC through SPI and the analog channel with the internal dual S/H 12-bit ADC and outputs the angle position data with up to 28-bit resolution through a USB virtual COM port.

#### **TIDA-00176 Features Overview**

- Wide input voltage range: 24-V (17 to 36 V) with reverse polarity protection provides the necessary voltages for analog signal chain as well as the 5.25 V for the Sin/Cos encoder.

- Encoder interface: Sub-D15 or 8-pin header interface to 5-V Sin/Cos encoders with differential output signals A, B, and marker R from 0.3 V to 1.2 V<sub>PP</sub> at 2.5-V ±1-V offset, input bandwidth up to 500 kHz.

- Dual path analog signal processing: Dual path option with an onboard high-speed, high-resolution dual 16-bit simultaneous sampling ADC with SPI and dual analog outputs with a 1.65-V bias voltage to interface to an external dual S/H ADC. High-speed, low propagation delay comparators with an adjustable 160-mV hysteresis for better noise immunity to convert the analog signals A, B, and R to 3.3-V TTL signals often referred as ABZ signals.

- High-resolution interpolated angle position, up to 28-bits resolution, cable length tested up to 70 m.

- EMC immunity: The design is tested for tested for IEC61000-4-2, 4-4, and 4-5 (ESD, EFT, and Surge) as specified in the standard IEC 61800-3 EMC immunity requirements and specific test methods applicable in adjustable speed, electrical-power drive systems.

- Interface to host processor with 3.3-V digital interface signals to MCU QEP and SPI and optional singleended analog 0 to 3.3-V outputs for MCU embedded dual S/H ADC.

- Evaluation firmware: Example firmware for Piccolo F28069M MCU with high-resolution dual angle position calculation at 16 kHz. The user interface is through USB virtual COM port for easy performance evaluation.

## 2.1 Sin/Cos Encoder Interface

The design offers either a shielded Sub-D15 female connector compatible to HEIDENHAIN encoder test equipment or an 8-pin header connector to interface to 5-V Sin/Cos encoders with differential output signals A, B, and marker R.

| PARAMETER                                                    | TYPICAL VALUE                                           | COMMENT                                                                                                                                                                           |

|--------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Encoder supply voltage                                       | 5.25 V [±5%], 200 mA                                    | 5.25 V was chosen for an additional 0.25-V<br>margin to compensate for voltage drop over<br>longer cables.<br>Adjustable to, for example, 5 V through<br>feedback resistor change |

| Input signals                                                | A+, A–, B+, B–, R+, R–                                  | 120- $\Omega$ differential line termination                                                                                                                                       |

| Input level and common mode voltage range for A+, A–, B+, B– | $0.3$ -V – $1.2 V_{PP}$ , $2.5 V \pm 1.0 V$ common mode |                                                                                                                                                                                   |

| Input level and common mode voltage range for R+, R–         | 0.2-V – 0.85 V <sub>PP</sub> , 2.5 V ±1.0 V common mode |                                                                                                                                                                                   |

#### Table 2-1. Sin/Cos Encoder Interface

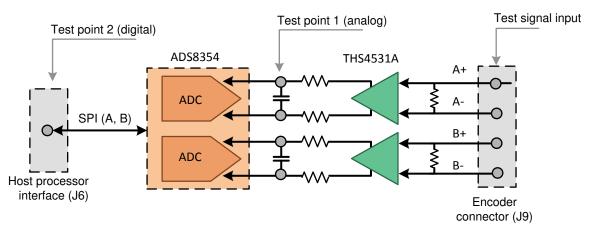

## 2.2 Host Processor Interface

The high-resolution path for signals A+, A– and B+, B– features a high-speed, high-resolution dual 16-bit simultaneous sampling ADC with differential input and SPI output. The main features of this functional block are outlined in Table 2-2.

| PARAMETER                    | TYPICAL VALUE                 | COMMENT                                                                             |

|------------------------------|-------------------------------|-------------------------------------------------------------------------------------|

| Gain A, B                    | 5.0 (0.1%)                    | Matched single package gain setting registers (0.1%)                                |

| Gain drift A, B              | 2 ppm//°C                     | Matched single package resistors                                                    |

| Offset, A, B                 | < 10 LSB (@ 16-bit)           | Uncalibrated                                                                        |

| Offset drift, A, B           | < 0.15 LSB/°C                 |                                                                                     |

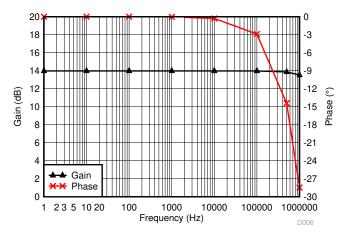

| Bandwidth (–3 dB)            | ≥500 kHz                      |                                                                                     |

| Quantization                 | 16-bit                        | FSR = $\pm 5$ V (ADS8354)<br>Drop-in compatible 14- or 12-bit versions<br>available |

| Sampling frequency           | Up to 700 kSPS                |                                                                                     |

| Data output format A, B      | 16-bit two's complementary    |                                                                                     |

| Serial interface (SPI slave) | 3.3 V, up to 24-Mhz SPI clock | Dual 16-bit data per SPI frame                                                      |

#### Table 2-2. 16-Bit High-Resolution Channel With ADC and SPI Output

The parallel, second path for the signals A+, A– and B+ offers a single-ended analog output for A and B with a 1.65-V bias voltage to interface to an external dual S/H ADC, which is for example embedded in microcontrollers like a C2000 Piccolo.

#### Table 2-3. Analog Channel With Single-Ended Analog Output

| PARAMETER                          | TYPICAL VALUE                           | COMMENT                                                                                    |  |

|------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------|--|

| Single ended analog output A and B | 0-3.3 V, 1.65-V bias voltage [50 ppm/K] | Drop-in compatible 1.5-V reference available to match ADC with 0-3-V input and 1.5-V bias. |  |

| Gain (A,B)                         | 1.66 (0.1%)                             | Adjustable, 0.1% resistors recommended                                                     |  |

| Offset (A,B)                       | < 1 mV                                  | Uncalibrated                                                                               |  |

| Offset drift (A,B)                 | < 2 µV/°C                               |                                                                                            |  |

| Bandwidth (–3 dB)                  | ~ 500 kHz                               | Adjustable LP filter for bandwidth adjustment                                              |  |

The comparator block features high-speed, low-propagation delay comparators with an adjustable 100-mV hysteresis for better noise immunity to converts the analog signals A, B, and R to 3.3-V TTL.

| Table 2-4. Comparators  PARAMETER TYPICAL VALUE COMMENT |                  |                                                                           |  |  |

|---------------------------------------------------------|------------------|---------------------------------------------------------------------------|--|--|

| Digital output signals A, B, and R                      | 3.3-V TTL        |                                                                           |  |  |

| Hysteresis                                              | ~160 mV (±80 mV) | For increased noise immunity, adjustable through feedback resistor change |  |  |

| Propagation delay                                       | ~ 40 ns          | Low propagation delay                                                     |  |  |

| Maximum phase delay (propagation delay and hysteresis)  | < 60°            | at 0.3 V <sub>PP</sub> , 500-kHz input                                    |  |  |

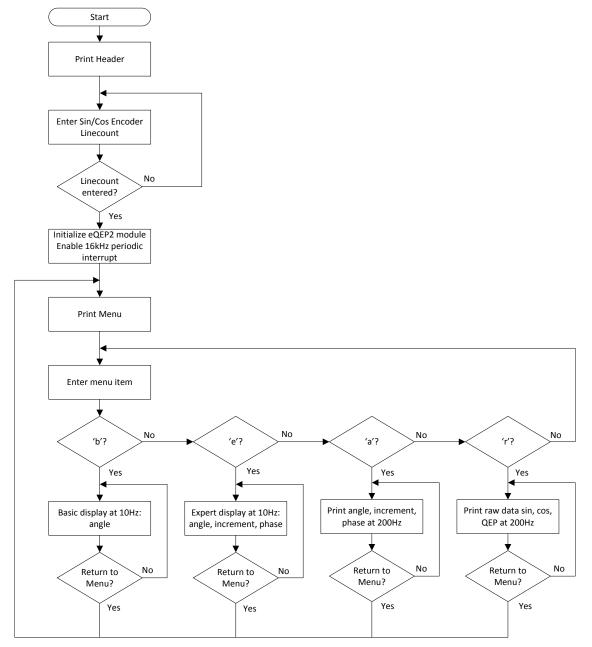

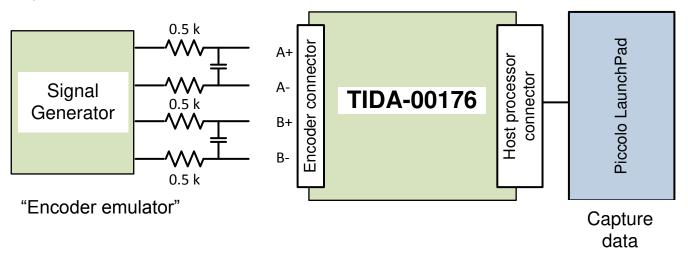

## 2.3 Evaluation Firmware

To allow for quick evaluation of the TIDA-00176 design an example firmware for Piccolo F28069M MCU is provided, where the interpolated high-resolution angle is calculated for both the 16-bit dual ADC ADS8354 and the F28069M MCU's embedded dual S/H 12-bit ADC. A user interface through USB virtual COM port at 115000 baud allows for easy performance evaluation.

The user interface through virtual COM port at 115000 baud supports the following features:

- Selection of Sin/Cos encoder line count: up to 32000

- Hardware and software synchronized sampling of the external dual sampling 16-bit ADC through SPI, the internal 12-bit dual S/H ADC and the incremental counter with a synchronization delay of less than 100 ns

- High resolution angle in 32-bit, fractional Q28 format. Angle scaled per unit from 0 to 0.9999999, up to 28-bit interpolated angle resolution

- · Automatic absolute position initialization after first occurrence of index marker R

- Menu to support display mode at 10 Hz or data dump mode at a 200-Hz update rate for total angle, incremental angle and phase with both, the 16-bit dual ADC (ADS8354) on the TIDA-00176 design, and the C2000 on-chip 12-bit dual S/H ADC

- Diagnostic error message when encoder not connected or when differential input voltage below 0.3 V<sub>PP</sub>

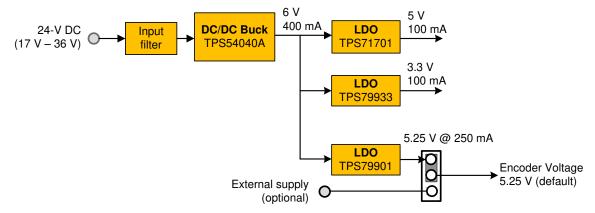

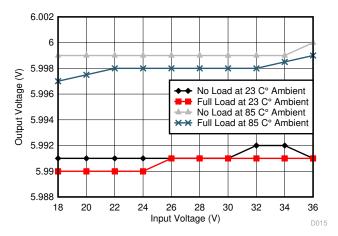

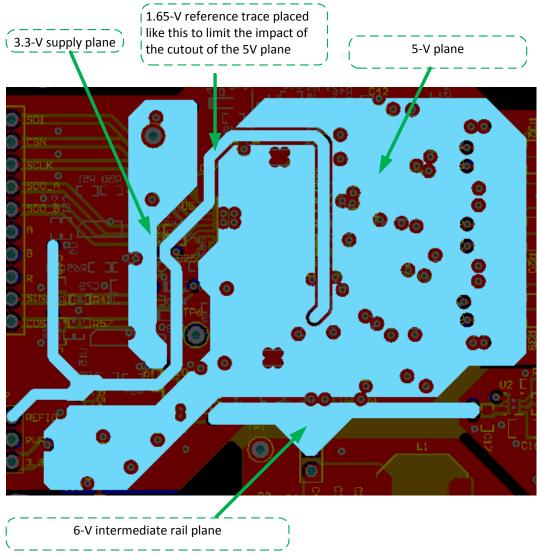

#### 2.4 Power Management

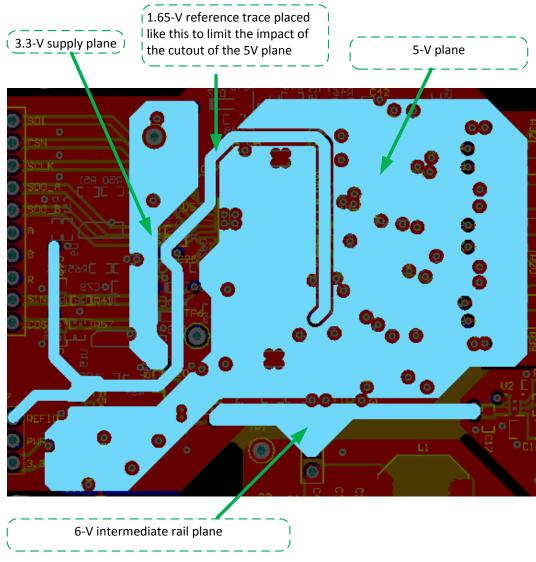

The TI design features a 24-V DC input with wide input voltage range from 17 to 36 V and reverse polarity protection. The onboard power management is split into a DC/DC buck that generates an intermediate 6-V rail and three LDOs, which generate the corresponding 3.3-V, 5-V, and 5.25-V rails.

The 5.25-V encoder supply features a LDO with very low noise and an enable pin. Therefore, the Sin/Cos encoder supply voltage can be turned off through the host processor if desired.

| PARAMETER         | VOLTAGE           | CURRENT | COMMENT                                                                                                                                                              |

|-------------------|-------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input             | 24 V [17 to 36 V] | 150 mA  | Wide input voltage with reverse polarity protect                                                                                                                     |

| Intermediate rail | 6 V [±5%]         | 500 mA  | Intermediate rail. High-efficiency (>80%) DC/DC buck power supply                                                                                                    |

| Encoder supply    | 5 V [±5%]         | 250 mA  | 5.25 V was chosen for an additional 0.25V margin to compensate for voltage drop over longer cables. Adjustable to, for example, 5 V through feedback resistor change |

| 5-V supply rail   | 5 V [±5%]         | 100 mA  | High precision signal chain supply                                                                                                                                   |

| 3.3-V supply rail | 3.3 V [±5%]       | 100 mA  | Low precision signal chain supply                                                                                                                                    |

#### Table 2-5. TIDA-00176 Voltage Rails

## 2.5 EMC Immunity

The design meets ESD, EFT, and Surge requirements per IEC61000-4-2, 4-4, and 4-5 with levels specified in the IEC 61800-3 standard "EMC immunity requirements for adjustable speed, electrical-power drive systems". It is assumed only the subD-15 connector to the position encoder can be accessed and shielded encoder cables are used to connect to the encoder. Because the encoder cable can exceed 30 m, ESD, EFT, and Surge apply per Table 2-6 for use in Environment 2.

| PORT                      | EMC TEST                   | EMC STANDARD | LEVEL                                                                                        | PERFORMANCE<br>(ACCEPTANCE)<br>CRITERION |

|---------------------------|----------------------------|--------------|----------------------------------------------------------------------------------------------|------------------------------------------|

|                           | ESD                        | IEC61000-4-2 | ±4-kV CD or 8-kV AD, if<br>CD not possible                                                   | В                                        |

| Sin/Cos Encoder Interface | Fast transient burst (EFT) | IEC61000-4-4 | ±2 kV/5 kHz, capacitive clamp                                                                | В                                        |

| Connecter                 | Surge 1.2/50 µs, 8/20 µs   | IEC61000-4-5 | ±1 kV. Since shielded<br>cable >20 m, direct<br>coupling to shield (2-Ω<br>source impedance) | В                                        |

The performance (acceptance) criterion is defined, as follows:

#### Table 2-7. Performance Criterion

| PERFORMANCE<br>(ACCEPTANCE)<br>CRITERION | DESCRIPTION                                                                                                                                                                                                               |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A                                        | The module shall continue to operate as intended. No loss of function or performance even during the test                                                                                                                 |

| В                                        | Temporary degradation of performance is accepted. After the test, the module shall continue to operate as intended without manual intervention.                                                                           |

| С                                        | During the test, loss of functions accepted, but no destruction of hardware or software. After the test, the module shall continue to operate as intended automatically, after manual restart, or power off, or power on. |

## 3 Block Diagram

The system block diagram of this design is shown in Figure 3-1. The major building blocks of this TI design are a dual path for the analog signal chain, a high-speed comparator block, the power management and the interfaces to the Sin/Cos encoder and host microcontroller for digital signal processing and high-resolution position calculation. To allow for easy evaluation of the TIDA-00176 design, an example firmware is provided for the F28069M Piccolo LaunchPad, which outputs the angle position through virtual COM port.

Figure 3-1. System Block Diagram of TIDA-00176 With Piccolo F28069M LaunchPad

The analog signal chain provides  $120-\Omega$  termination with EMC protection and amplifies and level shifts the differential  $1-V_{PP}$  sine and cosine input signals, respectively. A dual signal path option is provided with an onboard ADS8354 high-speed, dual 16-bit simultaneous sampling ADC with SPI and an analog path with dual analog outputs with a 1.65-V bias voltage to interface to an external dual S/H ADC, which is for example embedded on MCUs like C2000 Piccolo.

The high-speed, low propagation delay comparator block features adjustable hysteresis for better noise immunity and converts the analog signals A, B, and the marker R into digital signals with 3.3-V TTL-level to interface to a quadrature encoder pulse module like the QEP module on the C2000<sup>™</sup> Piccolo MCU.

The onboard wide-input range 24-V power supply provides the necessary voltages for analog signal chain as well as the 5.25 V for the Sin/Cos encoder.

The Sin/Cos encoder interface offers either a 15-pin shielded Sub-D connector or an 8-pin header. The interface to the host MCU offers digital 3.3-V TTL compliant signals for SPI and A, B, and R as well as analog signals A and B scaled from 0 to 3.3 V with a 1.65-V bias voltage.

## 4 Circuit Design and Component Selection

## 4.1 Analog Signal Chain

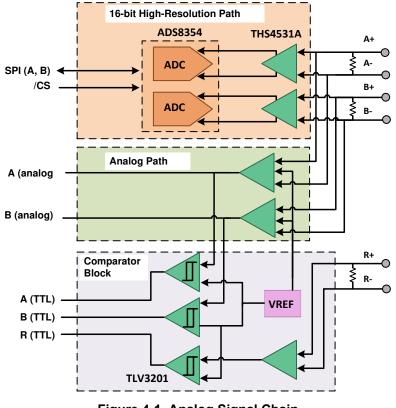

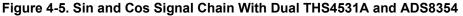

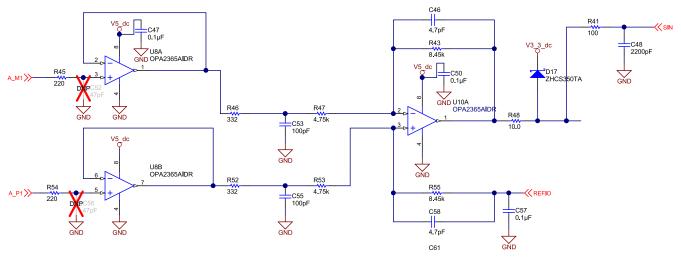

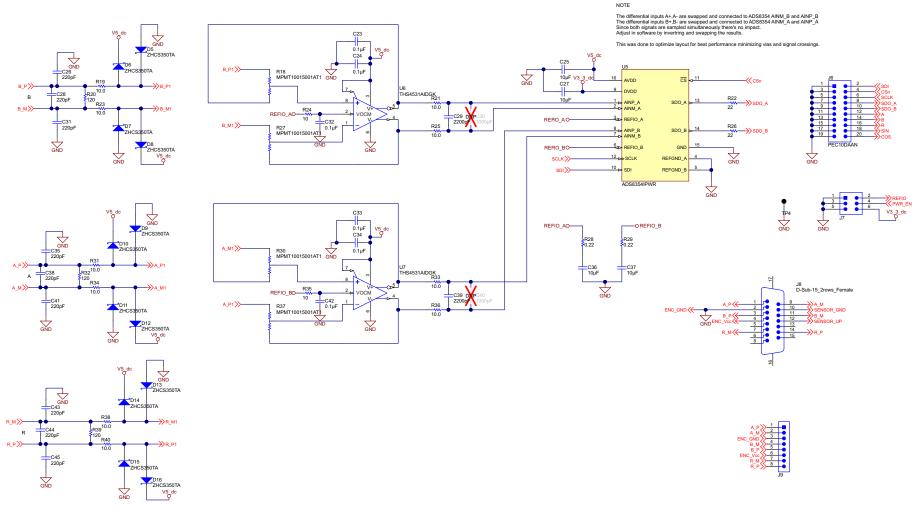

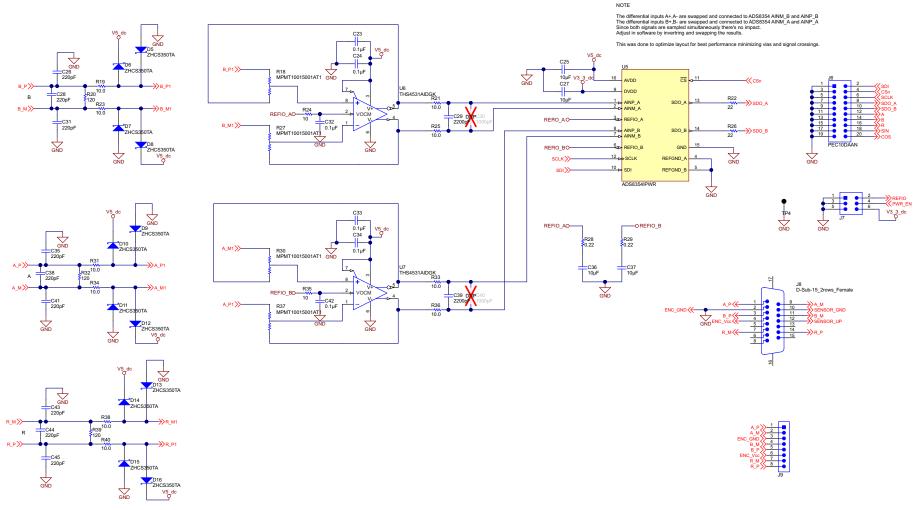

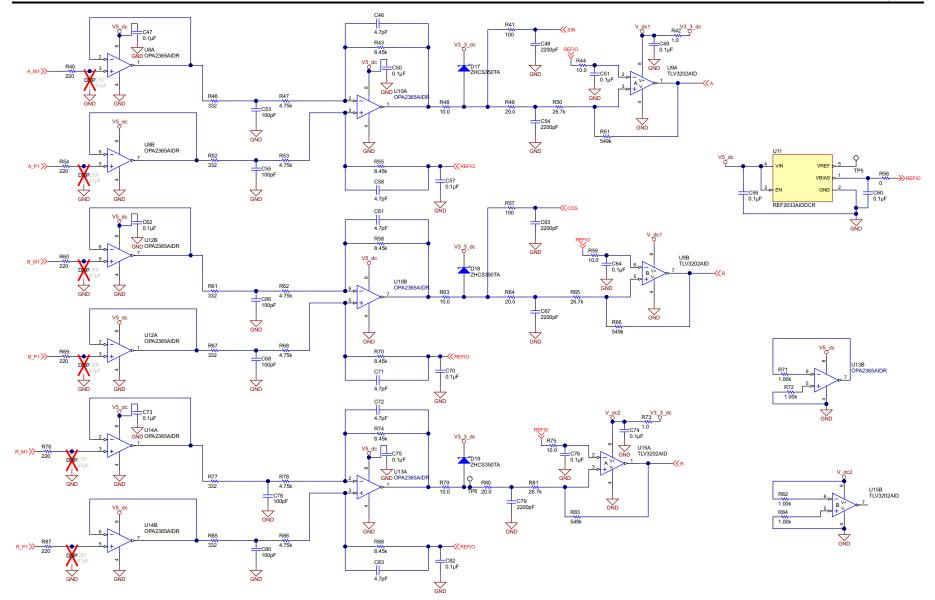

Figure 4-1 provides and overview on the analog signal chain sub-system and the comparator subsystem. For the analog signal chain, two paths are implemented:

- A high resolution signal path with increased common mode noise immunity featuring fully differential amplifiers and fully differential dual 16-bit ADC with an SPI output

- An analog path with differential input to single-ended analog output to drive the comparator and additionally for interface to a host processor with embedded ADC

The dual analog path offers the option to either test the design with the onboard 16-bit dual ADC as part of the high-resolution path, or use the analog differential to single-ended path with an MCU with embedded ADC. Additionally the analog path, since decoupled through a buffer from the high-resolution path, ensures an ideal decoupling of the comparator path. This avoids x-talk into the high-resolution analog path when switching the output level during sine and cosine zero crossing.

Another use case would use both paths. One path would have improved noise immunity with a reduced bandwidth to filter out HF noise, while the other path would have offer standard bandwidth up to maximum speed. The lower bandwidth with improved noise immunity would be dedicated to the high-resolution 16-bit ADC, while the other path with standard bandwidth would be connected to the MCU with embedded ADC. The interpolated phase (arc tangent) would then be taken from the high-resolution path when the motor speed is low (below the configured cut-off frequency), while at higher speed the interpolated phase from the other path would be used. The host processor will decide which angle to use pending motor speed.

The comparator sub-system will generate TTL level outputs for signals A, B, and R, at a very low-propagation delay. Each sub-system is explained in the following sections.

Figure 4-1. Analog Signal Chain

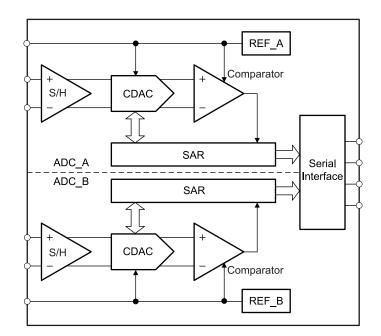

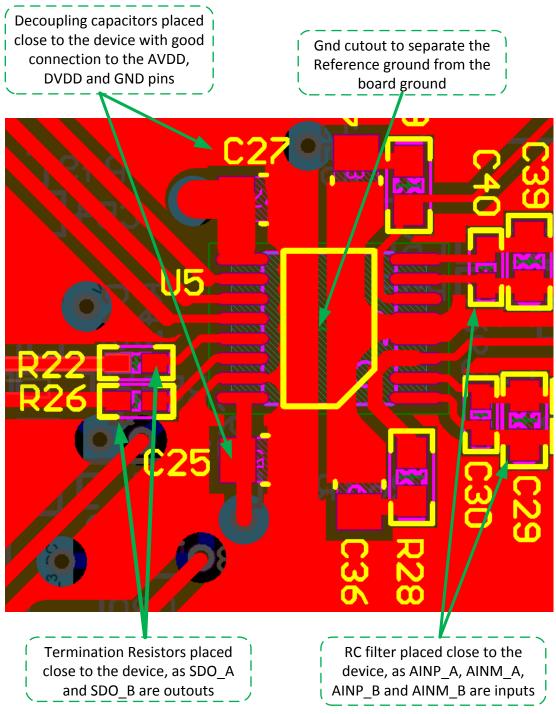

## 4.1.1 High-Resolution Signal Path With 16-Bit Dual Sampling ADC

#### 4.1.1.1 Component Selection

A high-precision dual channel ADC is required to fulfill the design requirements. The ADS8354 has been selected for the following reasons:

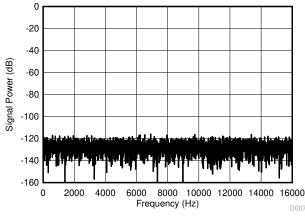

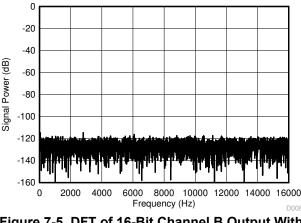

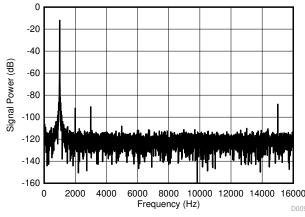

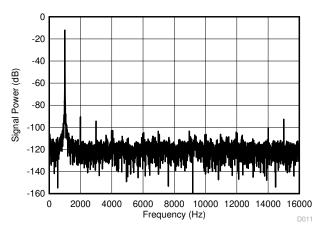

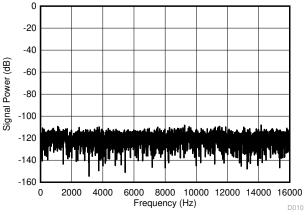

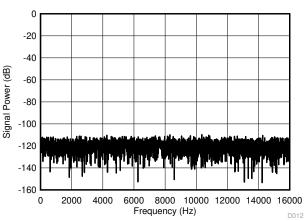

- High resolution (16-bit) with high precision (superb THD and SNR performance of –93 dB SNR, –100 dB THD)

- Drop-in pin-compatible 14-bit and 12-bit versions for flexibility pending required resolution versus cost optimization

- High speed (700 kSPS) and bandwidth to support at least 500-kHz analog input signals

- Dual channel with true differential inputs and dual/independent reference voltages to improve immunity against common mode noise

- Dual channel, simultaneous sampling of two channels to ensure zero phase shift between the sin and cos input signals A and B

- Sample point triggered by hardware (falling edge of /CS) allows host processor to precise synchronize the sample point with the incremental counter latch.

- Sample-and-hold circuit returns to sample mode after completing the conversion process, hence relative long sample times to settle to 16-bit accuracy

- Dual, programmable, and buffered 2.5-V internal reference to provide common mode bias voltage to amplifier to almost cancel offset and offset drift related errors.

- Serial interface to host processor (dual data) with up to 24-MHz clock frequency to minimize latency

- Fully-specified over the extended industrial temperature range: -40°C to 125°C

- Small package

Figure 4-2. ADS8354 Block Diagram

To leverage the ADS8354 performance, a fully differential high-speed amplifier with configurable output common mode voltage, like the THS45xx family, is required.

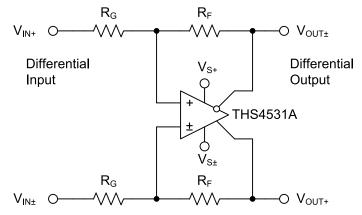

Figure 4-3. Differential Input to Differential Output Amplifier

The signal remains fully differential, the gain and optional filtering is defined by the input and feedback resistors and capacitors. The gain is set by the ration of RF/RG and the output common mode voltage is set by the input signal  $V_{\text{OCM}}$ .

The THS4531A was chosen as it meets the topology, can drive the ADS8354, and meets the AC and DC requirements specified in Section 1.4. A single amplifier topology per package was used instead of the dual differential amplifier per package like the THS4532 for flexibility and easier PCB routing.

The key parameters of the THS4531A for use in this design are:

- Fully differential architecture with adjustable output common mode voltage

- High gain bandwidth: 27 MHz (6 MHz at G = 5)

- Low distortions, THD –120 dBc at 1 kHz (1  $V_{RMS}$ ,  $R_L$ = 2 k $\Omega$ )

- Low input voltage noise: 10 nV/ $\sqrt{Hz}$  (f = 1 kHz)

- Very low offset,  $V_{OS}$ : ±100  $\mu$ V

- Very low offset drift, V<sub>OS</sub> Drift: ±2 μV/°C (Industrial temperature range)

- Single 5-V supply to leverage same supply than the ADS8354

- Rail-to-rail output (RRO) and negative rail input (NRI) to maximize input and output signal swing

#### 4.1.1.2 Input Signal Termination and Protection

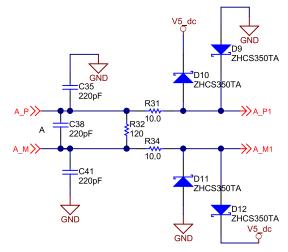

The differential input signals are terminated with  $120-\Omega$  resistors each. COG capacitors are added for differential and common mode HF noise rejection. The differential low-pass filter's cut-off frequency

(-3 dB) is around 6 MHz. The 10- $\Omega$  (1%) pulse-proof resistor in conjunction with Schottky-diodes clamp to the 5-V rail or GND, for ESD protection with input current limitation. Figure 4-4 shows the TIDA-00176 schematics of the input stage for the encoder's differential signals A+ (sine) and A– (cosine).

Figure 4-4. Termination for Analog Inputs

Looking at the encoder signals A+/A- (named " $A_P - A_M$ " in the schematic) signal conditioning block schematic from left to right we can distinguish the following parts/functions:

- The HF noise suppression COG capacitors: C35, C38, and C41. For higher common mode rejection, an

additional 2-nF COG capacitor might be placed in parallel to the 220-pF capacitor from each differential input

to GND. The low-pass cut-off frequency (–3 dB) is around 6 MHz.

- The impedance matching/termination resistor 120 Ω: R32

- Current limiting resistors with pulse proof current: R31, R34

- · Clamping diodes / op-amp input protections (D9 to D12) to the 5-V rail and GND

The LP filters are designed to guarantee the proper functionality and performance at the speed provided in the system specifications.

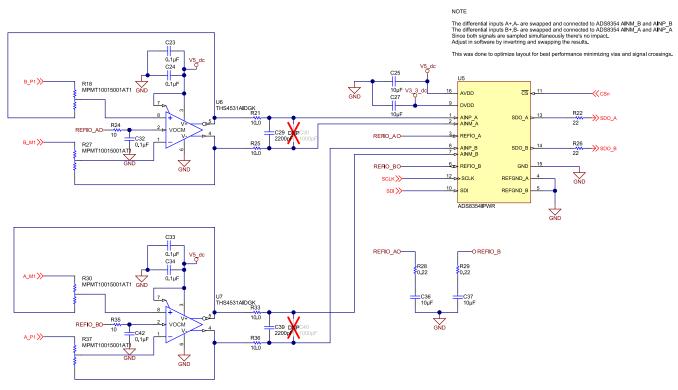

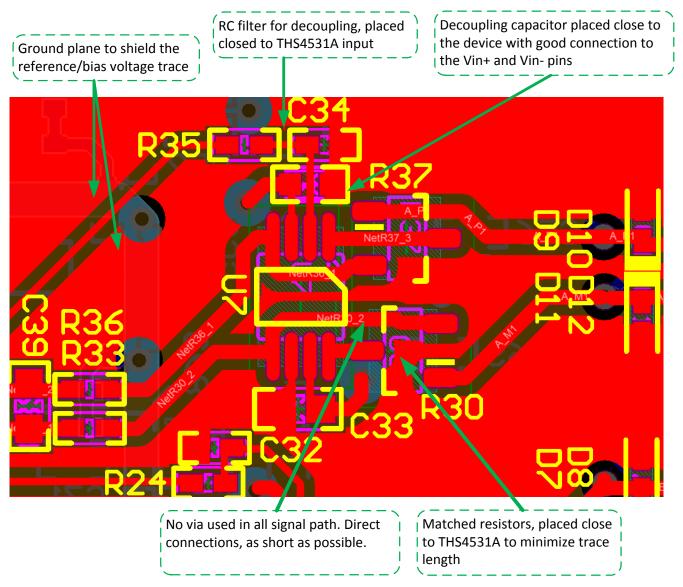

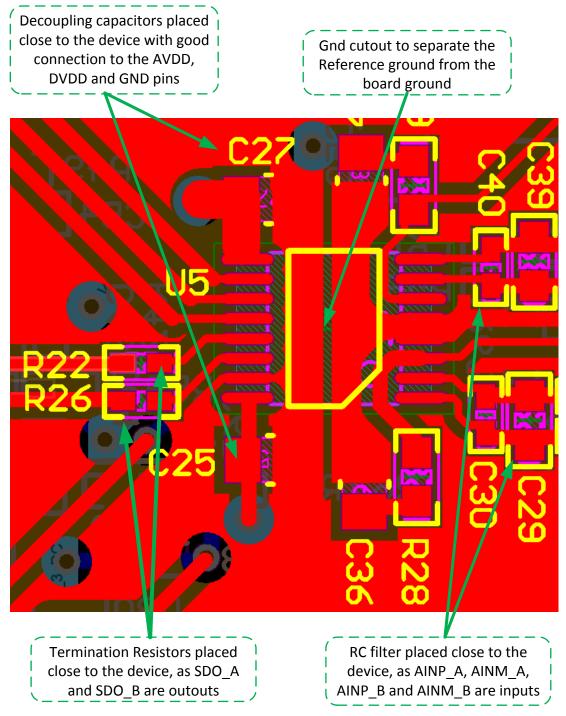

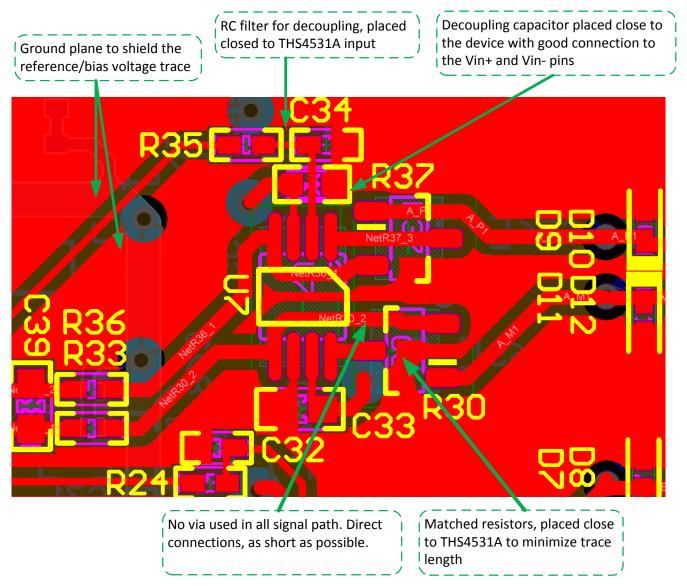

#### 4.1.1.3 Differential Amplifier THS4531A and 16-Bit ADC ADS8354

The two primary circuits, required to maximize the performance of a high-precision, successive approximation register (SAR) ADCs, are the input driver and the reference driver circuits. For details on selecting the amplifier, refer to the ADS8354 datasheet, Section 9.1.

The THS4531A has been minded to work in combination with the ADS8354. Indeed, the common mode or DC-level of the input signal (2.5 V nominal) is provided to the THS4531A directly from the reference output of the ADS8354 itself to minimize potential offset and drift errors.

The differential input full scale range of the ADS8354 was configured to  $\pm 2 \times V_{REF}$ . With the reference voltage of  $V_{REF} = 2.5$  V, this yields a FSR of  $\pm 5$  V. The maximum Sin/Cos encoder's differential input voltage is 1.2  $V_{PP}$ . A voltage of higher than 1.35  $V_{PP}$  should still be detected as failure. A safety margin of 50% is added to the maximum peak-to-peak voltage, which is then 1.8  $V_{PP}$ . To match the ADC full-scale input range, the gain of the THS4531A should be 5.5. However, to remain in the linear output voltage range of the THS4531A at a 5-V supply, which is at least 0.25 to 4.8 V, the gain should be reduced by around 10%, hence the ideal differential amplifier gain would be 5.

To ensure the minimum gain error and especially drift between the channels, high-precision, matched resistors with 0.1% accuracy and 2-ppm/K temperature drift are required. To minimize noise, the feedback resistors should be chosen in the lower k $\Omega$  range (see Section 1.4).

A precision matching resistor divider is used to keep potential gain errors as small as possible. Refer to the MPMT10015001AT1 datasheet for details.

Due to the gain of 5, a typical 1-V<sub>PP</sub> input signal leverages around 50% of the ADC full-scale range (FSR), which results in a loss of 1-bit of precision, therefore yielding an equivalent 15-bit resolution. The lower input voltage of 0.6 V<sub>PP</sub> will leverage around 25% of the FSR, which equals typically 14-bit resolution.

Figure 4-5 shows the schematics of the high-precision analog signal path; the matched gain setting resistors are R18, R27, R30, and R37.

The series  $10-\Omega$  resistors R21, R25 and the 2.2-nF capacitor C29 (R33, R36, and C39 for ADS8354 channel B) from the anti-aliasing filter. The filter capacitor C29 (C39), connected across the ADC inputs, filters the noise from the front end drive circuitry, reduces the sampling charge injection and provides a charge bucket to quickly charge the internal sample-and-hold capacitors during the acquisition process. As a rule of thumb, the value of this capacitor should be at least 10 times the specified value of the ADC sampling capacitance. For these devices, the input sampling capacitance is equal to 40 pF. The capacitor should be a COG- or NPO-type because these capacitor types have a high-Q, low-temperature coefficient, and stable electrical characteristics under varying voltages, frequency, and time. To avoid amplifier stability issues,  $10-\Omega$  series isolation resistors R21, R25 (R31, R39) are used at the output of the amplifiers. For details, refer to the Section 9.1 of the ADS8354 datasheet.

To minimize the impact of an offset drift of the ADC reference REFIO\_A and REFIO\_B, the ADC references are used to bias the common mode output voltage of the THS4531A. To buffer and decouple the  $V_{OCM}$  signal at the THS4531A, small RC filters R24/C32 and R35/C42 R28, R29, C36, and C37 are added close to each pin.

The ADS8354 reference voltages REFIO\_A and REFIO\_B are decoupled with a 10-uF capacitor C36 and C37, respectively and a  $0.22-\Omega$  resistor is added in series to avoid high-frequency oscillations.

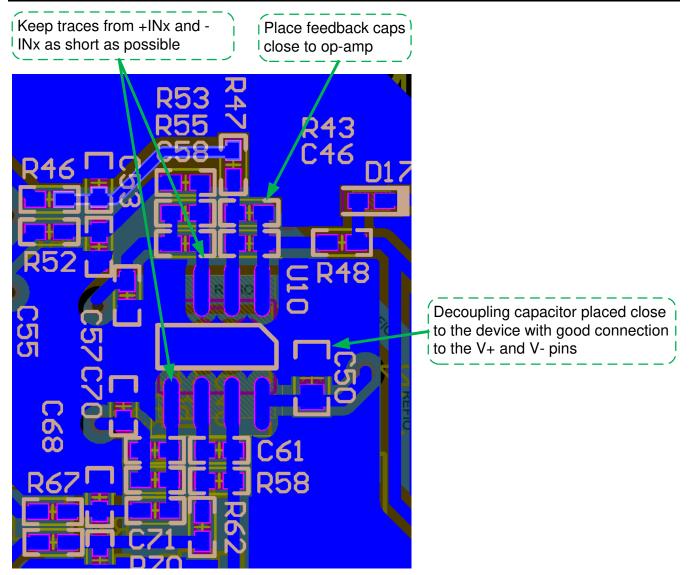

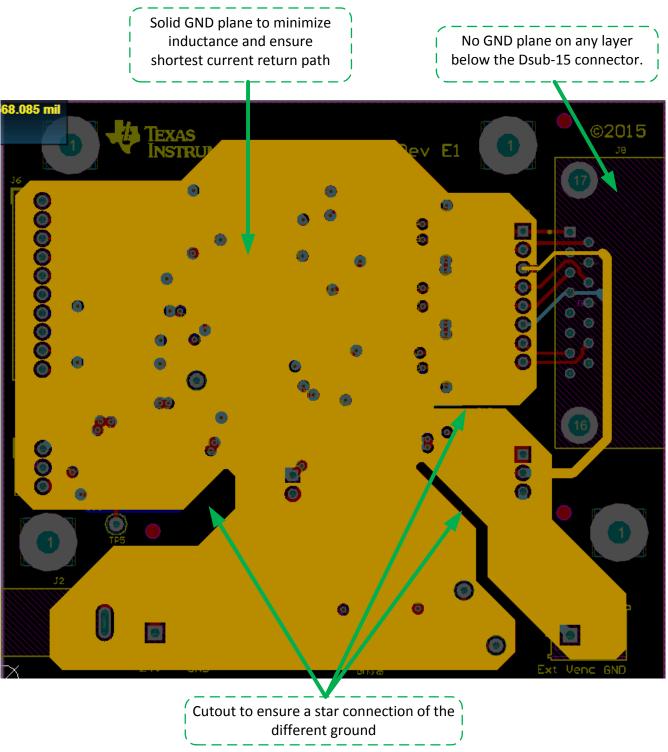

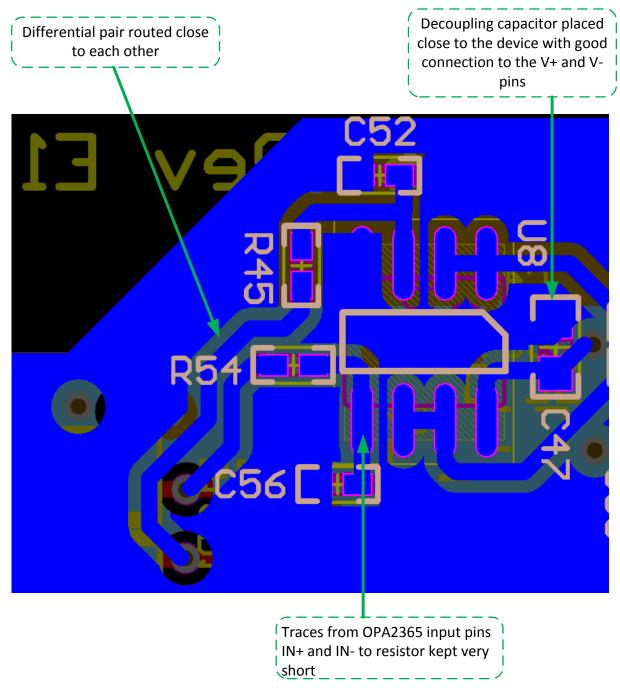

To optimize the layout for cross-talk with minimum use of via for the critical signals A+, A– and B+, B–, the following connections have been made.

- 1. The differential input signal A (A+, A–) has been inverted at the input of the THS4531A and fed into the ADS8354 input channel B.

- 2. The differential output signal of the THS4531A, B+ and B– have been connected inverted to the ADS8354 input pins AINP\_A to B– and AINM\_A to B+

This results in the following hardware relationship: The ADS8354 channel B equals the inverted Sin/Cos encoder signal A; the ADS8354 channel A equals the inverted Sin/Cos encoder signal B.

Note

Channels are inverted and swapped for optimum performance layout and minimize the numbers of vias.

To achieve a higher noise immunity with reduced bandwidth, a capacitor of 10 pF (1% or better) or higher, pending desired bandwidth is recommend in the feedback path in parallel to the 5 k $\Omega$ . See Section 4.5.

The configuration of the ADS8354 registers through serial interface is explained in Section 4.3.

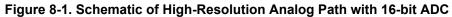

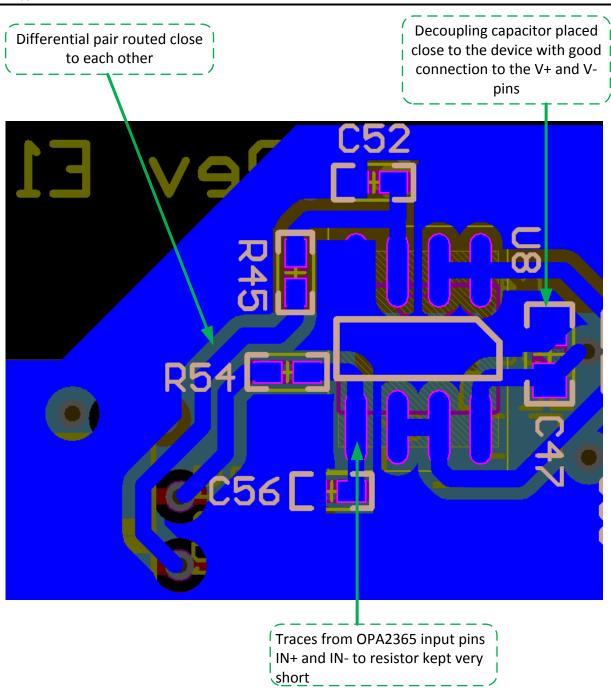

#### 4.1.2 Analog Signal Path With Single-Ended Output for MCU With Embedded ADC

The parallel analog signal path should not impact the high-resolution path and especially the differential amplifier. Therefore, the differential signals A+, A–, B+, and B– are tapped off after the input termination and protection and are buffered using unity gain amplifiers with very low offset and especially offset drift. The following amplifier should convert the differential signals into a single-ended signal. The minimum bandwidth should be least 500 kHz, ideally higher to support incremental encoders with higher than 500-kHz output signals. The phase delay for the path to the comparator should be similar than the high-resolution path to ensure minimum analog signal phase shift.

The supply voltage should be a single supply 5 V.

To match the high-resolution channel, the sum of the offset drift of both op-amps should be at least 12-bit equivalent accuracy, ideally match the analog performance of the high-resolution channel. For the input buffer and the differential to single-ended conversion, the OPA2365 has been selected due to:

- 2.2-V TO 5.5-V operation to leverage 5-V rail

- Rail-to-rail I/O

- Very low offset and offset drift: 200 μV (max) and 1 μV/K (typically)

- Low voltage and current noise: 4.5 nV/SQRT(Hz) and 0.004 pA/SQRT(Hz)

- Excellent THD+N: 0.0004%

- High common mode rejection, CMRR: 100 dB (min)

- Slew rate: 25 V/µs

- Fast settling: 300 ns to 0.01% to drive external ADC

Another option is the OPA2322, which is a lower cost alternative, with 2-mV offset voltage and slightly reduced AC and DC performance.

The analog output voltage should be scaled from 0 to 3.3 V with a 1.65-V common mode. Applying the same criteria in Section 4.1.1 with a maximum 1.8-V<sub>PP</sub> input voltage, and a 10% margin with regards to the 3.3-V FSR, the gain yields 1.66.

Figure 4-6 shows the analog signal chain for channel A. The channel B is identical.

# Figure 4-6. Analog Signal Path With Differential Input to Single-Ended Output for Signal A (sin), Signal B (cos) Not Shown

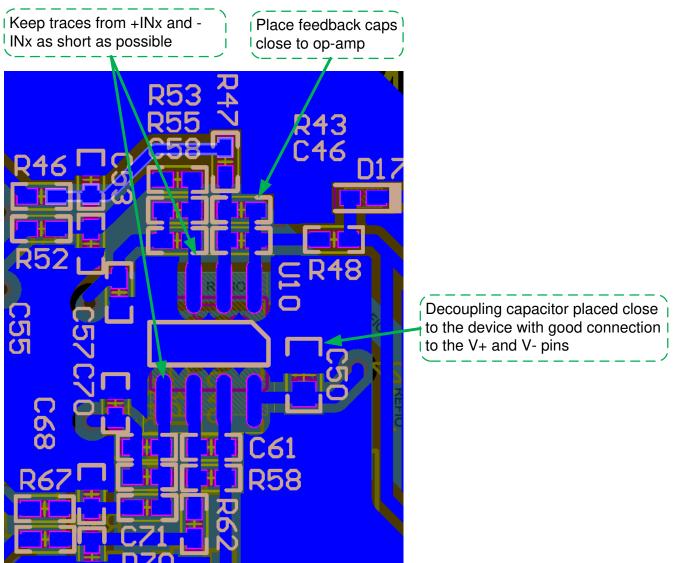

The differential signals A\_P and A\_N are connected through a 220- $\Omega$  resistor to the non-inverting input of the OPA2365 (U8A and U8B). The OPA2365 (U8A and U8B) are configured as unity-gain buffer to avoid loading the source and introducing distortions. The 220- $\Omega$  series resistor limits the current into the non-inverting input of the OPA2365 in case of an over- or undervoltage event. The output of each buffer employs a small, adjustable RC-filter with, for example, R46 and C53 in above picture with f-3dB ~ 5 MHz for high-frequency noise reduction.

The following OPA2365 (U10A) is configured as differential to single-ended amplifier and level shifter. The gain is set to 1.66 and the output common mode voltage to 1.65 V through a low-drift voltage reference REF2033. An adjustable 5.6-pF feedback capacitor is added in parallel to the feedback resistor for HF noise filtering (f-3dB  $\sim$  3.5 MHz), ideally matched to the THS4531A bandwidth. See Section 4.5.

Since the OPA2365 is supplied with 5 V, the output of the amplifier is clamped to 3.3 V (D17) with a series  $10-\Omega$  current limiting resistor (R48). This is to protect the following comparator (TLV3202/1) and an external ADC, which typically are 3.3-V I/O.

An anti-aliasing and decoupling RC network (R41/C48) is added to drive an external ADC. The filter was optimized for use with the embedded 12-bit dual S/H ADC in the C2000 Piccolo MCU family. For other ADCs, the filter has to be adjusted accordingly.

The 1.65-V bias voltage is decoupled with a 100-n capacitor (C57). Furthermore, LP RC filters have been added to reduce more and more HF noise components, in particular the one potentially coming from the switcher TPS54040A.

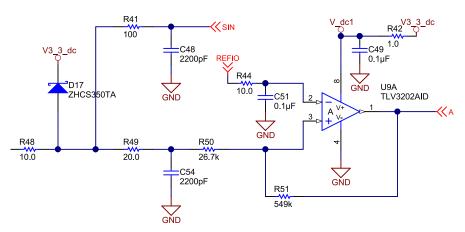

## 4.1.3 Comparator Subsystem for Digital Signals A, B, and R

The comparators are required to detect the zero-crossing of the analog signals A and B, as well as the zero index pulse with the marker R and generate the corresponding digital 3.3-V TTL-compatible signals  $A_{TTL}$ ,  $B_{TTL}$ , and  $R_{TTL}$ , often referred to as ABZ. As outlined in Section 1.4 a low propagation delay comparator offers additional margin to the system.

The comparators selected are the TLV3201 (single) and TLV3202 (dual), 40 ns, microPOWER, push-pull output comparators, with the following main characteristics:

- · Low propagation delay of typical 40 ns

- Low input offset voltage of typical 1 mV, to ensure minimum drift of switching threshold

- Push-pull outputs, to drive the input of a 3.3-V I/O host processor

- Industrial temperature range

The TLC372 dual comparator with 250-ns propagation delay is a lower cost option, depending overall system propagation delay and maximum frequency. The advantage of the TLV320x family is that it allows other components to add more delay while still keep the required 500-ns maximum delay at 500 kHz. For example, a larger hysteresis would increase the propagation delay while improve immunity against noise.

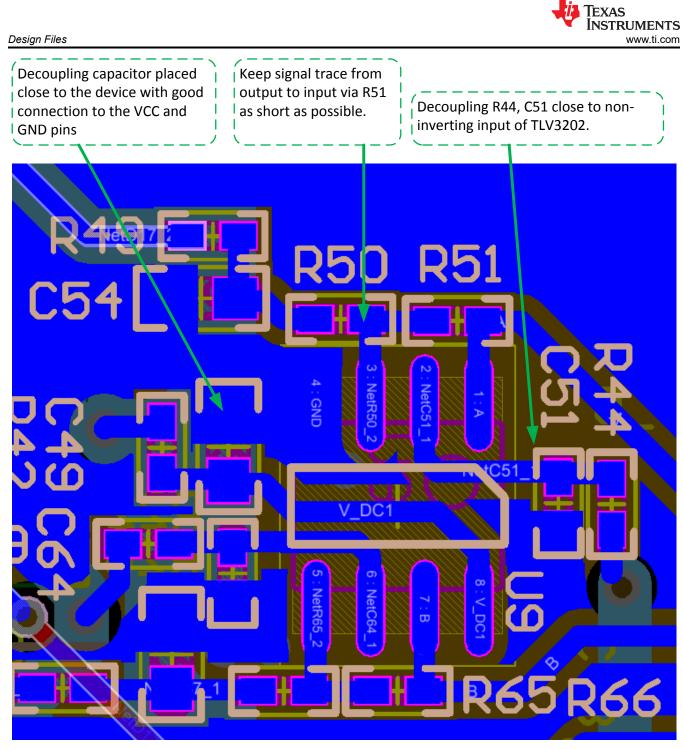

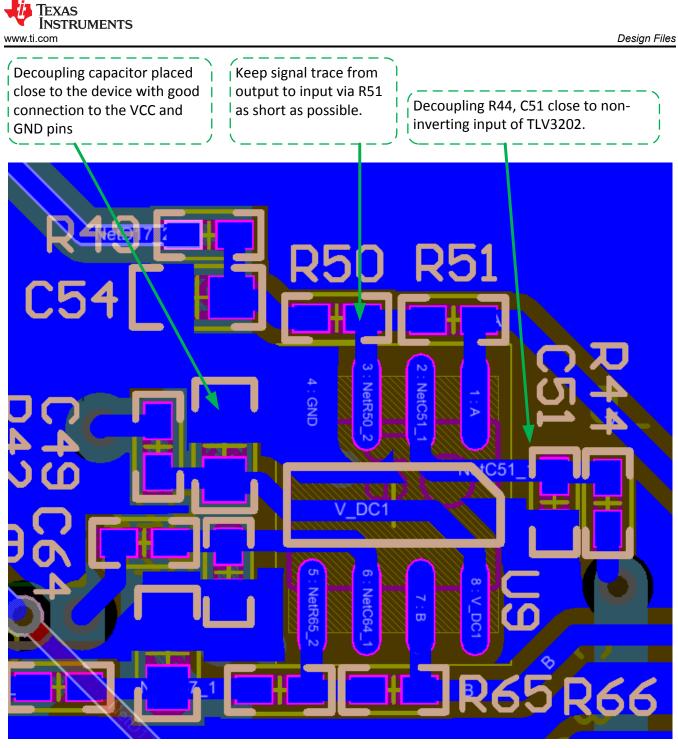

#### 4.1.3.1 Non-Inverting Comparator With Hysteresis

The input signals to all comparators are derived from the output of the single-ended to differential amplifier. The output signal is clamped to 3.3 V, as described earlier, and decoupled with a RC network (like R49, C54 in figure 19 for signal A) to avoid cross-talk to the analog single-ended signals A and B respectively.

The match the phase between the high-resolution path and this path, the RC decoupling network at the input to the comparator matches the RC filter (2×10  $\Omega$  and 2.2 nF) at the THS4531A output.

The TLV370x is configured as non-inverting comparator to detect the zero-crossing of the analog sin and cosine signals A and B as well as the index pulse R. Figure 4-7 shows the corresponding schematics for the signal A.

The switching threshold is set by the reference voltage  $V_{REF} = 1.65 \text{ V}$  (REF2033), which is also used to bias the single-ended analog signals for the differential to single-ended amplifiers. For each comparator, the reference input is taken from the REF2033 and decoupled with a 10- $\Omega$  series resistor and a 100-n capacitor.

A hysteresis is added for better noise immunity. The hysteresis ( $V_{TH+} - V_{TH-}$ ) of a non-inverting comparator can be calculated per Equation 7:

$$V_{\text{Hysteresis}} = \left( V_{\text{Out}_{\text{High}}} - V_{\text{Out}_{\text{Low}}} \right) \times \frac{R_{\text{G}}}{R_{\text{F}}}$$

(7)

with  $V_{Out\_High}$  the high-level and  $V_{Out\_Low}$  the low level comparator output voltage,  $R_F$  the feedback and  $R_G$  the input resistor into the non-inverting comparator input.

For the configuration of this design as outlined in Figure 4-7, the hysteresis has been set to around 160 mV per Equation 8. Since R49 and R48 are magnitudes lower than R50, they can be neglected.

$$V_{\text{Hysteresis}} = 3.3 \text{ V} \times \frac{\text{R50}}{\text{R51}} \sim 160 \text{ mV}$$

(8)

(10)

The upper and lower switching thresholds  $V_{TH+}$  and  $V_{TH-}$  are defined per Equation 9 and Equation 10 with the reference voltage  $V_{REF}$  = 1.65 V.

$$V_{TH+} = 1.65 V \times \left(1 + \frac{R50}{R51}\right) = 1.73 V$$

(9)

$$V_{TH-} = (3.3 \text{ V} - 1.65 \text{ V}) \times (1 - \frac{R50}{R51}) = 1.57 \text{ V}$$

#### CAUTION

The lower threshold is a function of the supply voltage. However, the supply voltage tolerance of this design 5%, as typical with most designs. A ±5% tolerance with the 3.3-V supply voltage would affect the lower threshold by only by ±16 mV, resulting  $V_{TH-}$  range from approximately 1.56 to 1.59-V, hence still acceptable.

Figure 4-7. Signal A Comparator With Hysteresis

The 3.3-V supply of each comparator is decoupled with a 1- $\Omega$  series resistors and 100-nF capacitor to minimize cross-talk through the 3.3-V rail to other comparators. The RC low pass comprised of R49 and C54 is added to decouple the comparators switching node from the analog signal A/sin, which will be connected to an external ADC.

The hysteresis allows for a clean digital signal, which means it avoids fast switching due to noise around the zero crossing point. The hysteresis however introduces an additional propagation delay, which is depending on the analog signal amplitude  $V_{IN}$  PEAK-PEAK at the comparator input.

$$f_{Hysteresis} \sim sin^{-1} \left( \pm \frac{160 \text{ mV}}{V_{IN\_PEAK-PEAK}} \right)$$

(11)

Assuming minimum input voltage of 0.3 V<sub>PP</sub>: The output of the differential- to single-ended amplifier (gain = 1.66) will have an amplitude of 0.5 V<sub>PP</sub> (0 to 100 kHz) and around 0.32 V<sub>PP</sub> at 500 kHz due to low-pass filter attenuation. The hysteresis corresponding phase delay of the digital signals A, B, and R will be around 30 degrees for a 0.32 V<sub>PP</sub> input at the comparator. At 500 kHz, this would translate into a total propagation delay of the comparator of around 170 ns + 40 ns = 210 ns.

Due to the low propagation delay of the TLV3201 with 40 ns only, the overall delay of the comparator block remains below 45 degrees up to 500 kHz.

The comparators for the signals B and R have the same settings. Also the buffering and gain stage for the index marker R is identical to the signals A and B. This is to ensure the phase of the index marker R is exactly in sync with the signal A and B up to a 500-kHz signal frequency. This ensures the zero Index Marker R will occur

as specified, slightly before the rising edge of signals A and B. The index marker R defines the absolute zero position, and hence exact relation to signals A and B is required to avoid any position offset.

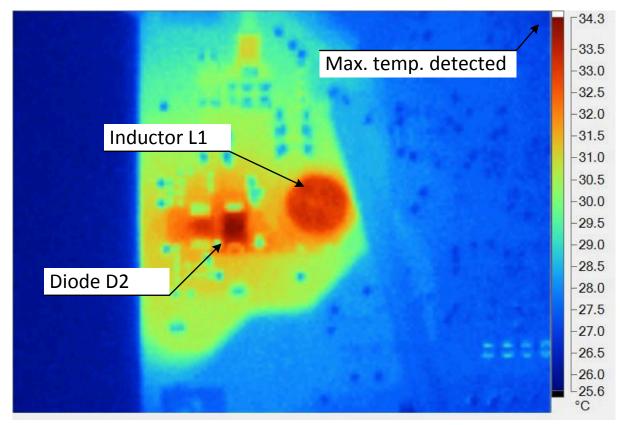

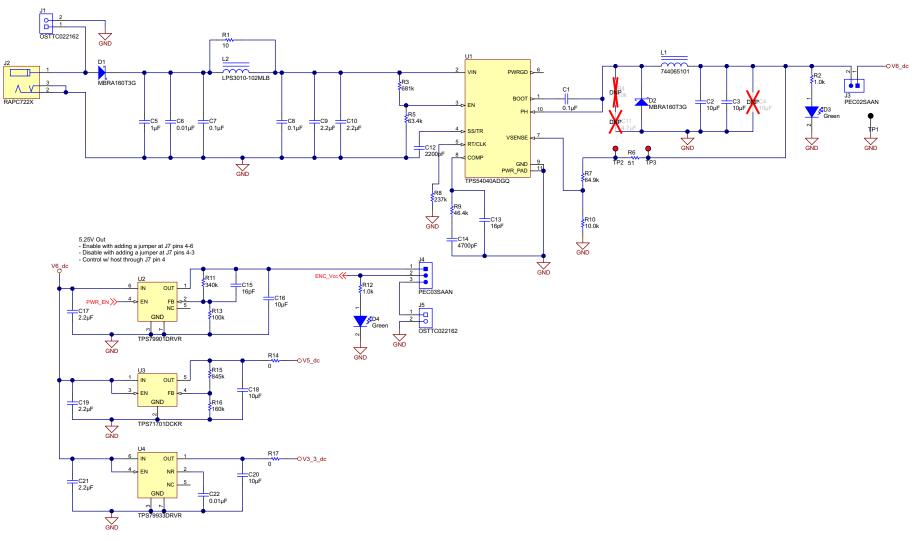

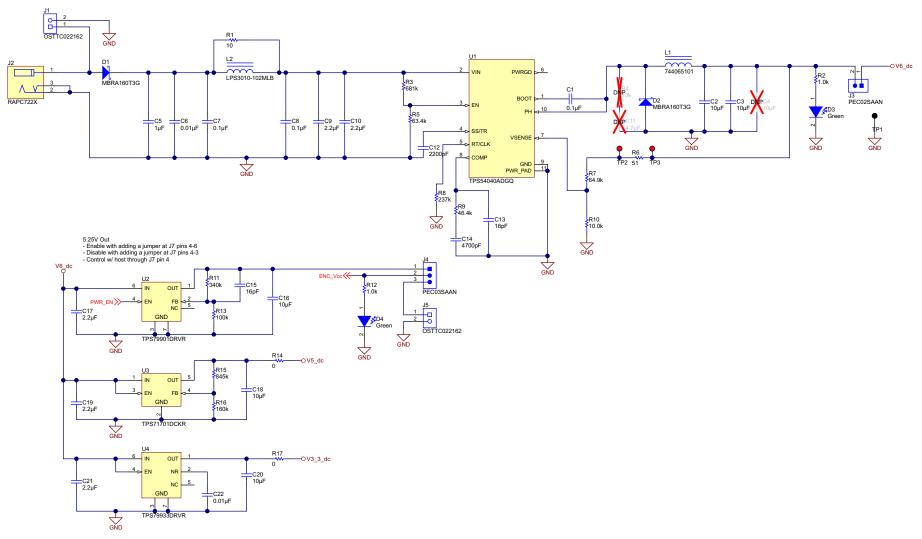

#### 4.2 Power Management

The power management consists DC/DC buck to generate a 6-V intermediate rail from the 24-V input voltage. The encoder supply voltage and the 5-V and 3.3-V rails are derived from the intermediate voltage, as shown in Figure 4-8.

Figure 4-8. Power Management Solution

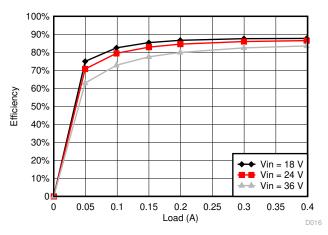

Because of the high performance required by the system and solution, most of the power rails are provided by low-noise LDOs. The drawback is the limited efficiency and low output current capability. The maximum output current is limited by the thermal performance, due to the high power losses.

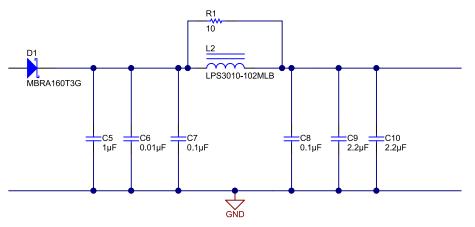

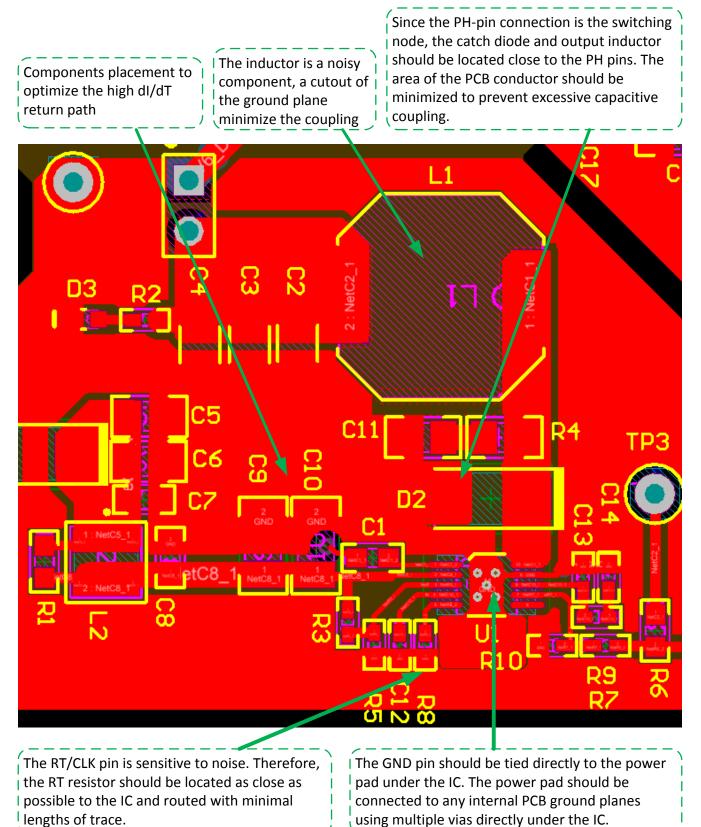

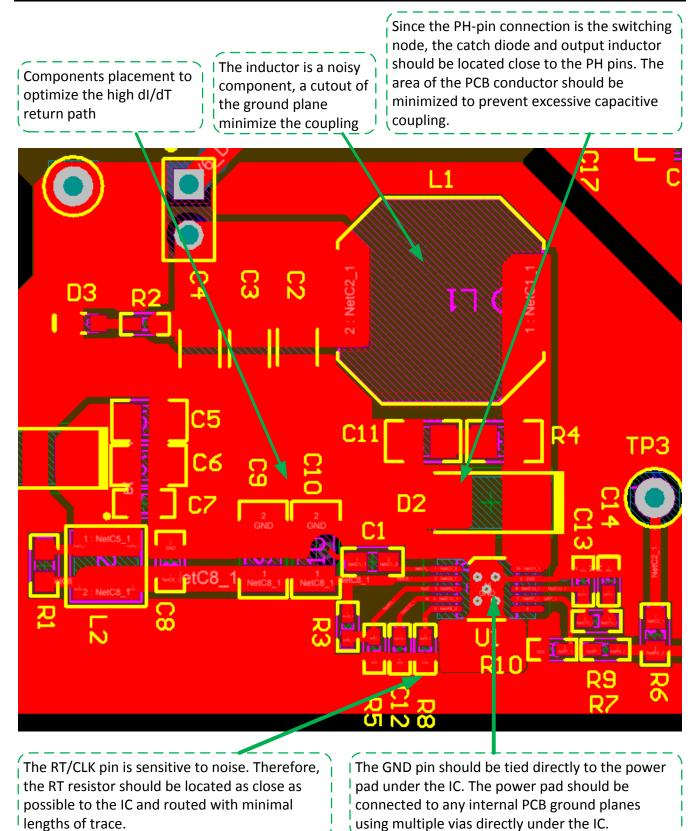

To reduce the voltage drop across the LDO a high-efficiency DC/DC switching converter to generate a 6-V intermediate rail from the 24-V input is us. Pay attention to minimize the noise introduced by the switcher solution by proper layout and component selection.

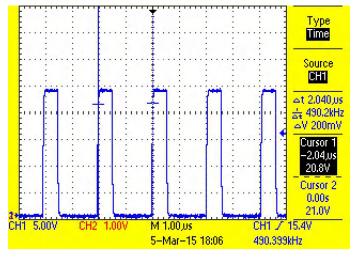

#### 4.2.1 24-V Input to 6-V Intermediate Rail

A switching DC-DC converter is provided to achieve the intermediate voltage rail of 6 V that supplied the three LDOs. This is a basically mandatory choice since the high VIN / VOUT ratio makes any LDO unsuitable for the power conversion. Indeed the efficiency of any LDO could be simply calculated as VOUT / VIN that, in the worst case (maximum VIN) would lead to  $5.25 \text{ V} / 36 \text{ V} \approx 14\%$ . The remaining 86% of the power consumption is dissipated by the LDO package: having indeed a maximum current of 200 mA would lead to  $36 \text{ V} \times 200 \text{ mA} \times 86\% = 6.2$ -W power dissipated on the LDO package that would simply and quickly blow up any reasonable package.

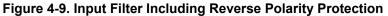

Starting with the input filter, it is widely known that conducted EMI are generated by the normal operation of switching circuits. Large discontinuous currents are generated by the power switches turn on and off very fast. In a buck topology, large discontinuous currents (high di/dt) are present at the input of the converter. The selected values for the input filter are shown in Figure 4-9.

For more details about how to design an input EMI filter, please refer to the application report, AN-2162 Simple Success With Conducted EMI From DC/DC Converters (SNVA489).

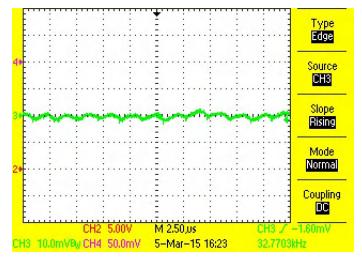

The DC/DC buck converter has been designed to meet the following specifications:

- Input voltage: V<sub>IN</sub> = 17 to 36 V, 24 V nominal

- Output voltage: 6 V @ 500 mA

- Switching frequency: 500 kHz nominal

- Output voltage ripple: 25 mV<sub>PP</sub> max

- Efficiency: > 80% at full load

- Non-isolated topology

The TPS54040A is selected for the purpose: this is a buck converter with an integrated FET, 3.5 to 42-V input voltage, and 0.8 to 39-V output voltage at a 500-mA output current. Its frequency can be adjusted from 100 kHz to 2.5 MHz or can be synchronized with an external clock. It can also be enabled and disabled. These features make the TPS54040A a very good fit to the requirements/specifications listed above.

Note that the TPS54040A is pin-to-pin compatible with the TPS5401, which is a lower cost version of the TPS54040A with similar performance but a less accurate output voltage and enabled threshold.

Also note that the TPS54040A is pin-to-pin compatible also with the TPS54140A, TPS54240, TPS54340, and TPS54540: this widens the part selection and offers the possibility to modulate costs and power level (in case of future system upgrades).

Figure 4-10. Schematic of 24-V to 6-V DC-DC Buck Converter With TPS54040A

For a detailed explanation of the design process, refer to the TPS54040A datasheet or the TI Design TIDA-00180.

On a typical application the output voltage is set thanks to a simple resistor divider network. Equation 12 gives the value of the upper resistor according to the output voltage, the reference voltage (0.8 V for the TPS54040A) and the lower resistor (with R10 usually fixed to 10 k $\Omega$ ).

$$R7 = R10 \times \frac{V_{OUT} - 0.8 V}{0.8 V}$$

With  $V_{OUT}$  = 6 V and R10 = 10 k $\Omega$ , R7 yields 65 k $\Omega$ .

The tolerance of the 6-V output voltage will be 6 V  $\pm$ 4%. This assumes feedback resistors with a 1% tolerance and the internal bandgap tolerance from the TPS54040A of  $\pm$ 2%.

The switching frequency is set with R8 = 237 k $\Omega$  to 500 kHz.

On the TPS54040A schematics, some components are marked as do not populate (DNP). This is the case of the snubber network formed by R4 and C11. The snubber network is not needed with the TPS540040A design. A snubber network is a solution to reduce the ringing on the switch node and overshoot of the MOSFET if needed. For more details of other option, refer to the application note *Ringing Reduction Techniques for NexFETTM High Performance MOSFETs* (SLPA010) on how to use and calculate the snubber network.

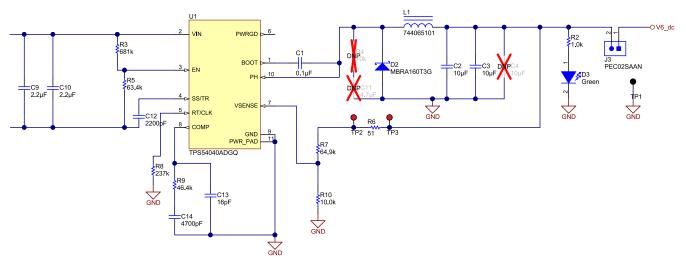

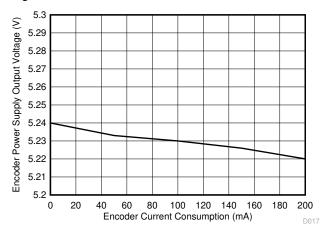

## 4.2.2 Encoder Supply

A 5.25-V supply for the encoder has been selected in order to meet a typical 5-V (±5%) encoder supply specification and have a 0.25-V additional margin to compensate for voltage drop across longer cables used to connect the encoder.

The LDO that provides the 5.25 V to the encoder has to provide also an enable pin. In this way, it is possible to power-cycle the turn-off or power-cycle the encoder supply from a host processor, if desired to for example turn-off the voltage at the encoder connector in case no encoder is connected.

The LDOs do not need specific description, except for the allowed range of output cap/ESR for stability purpose; while the main design involves the SMPS, as this affects all the main performances (noise, EMI, efficiency, cost, and board space).

The TPS79901 has been designed to provide a little higher voltage than the nominal 5 V (5.25 V), using part of the greater accuracy of the LDO to reduce the thermal stress on it. In brief 5.25 V  $\pm$ 2% is within the allowed supply range of the encoder (5 V  $\pm$ 5%). In this way, the power it has to dissipate is

$$P_{LDO,MAX} = (V_{LDO,IN} - V_{LDO,OUT}) \times i_{LDO,MAX} = (6 V - 5.25 V) \times 250 mA = 187 mW$$

(13)

With a 5-V encoder voltage, the maximum power dissipation would increase to 250 mW.

Indeed with a  $R_{thja} \approx 180^{\circ}$ C/W it means that the TPS79901 junction temperature will increase less than 34°C versus ambient temperature when working at maximum load current of 250 mA. For example at 85°C ambient, the junction will be 120°C.

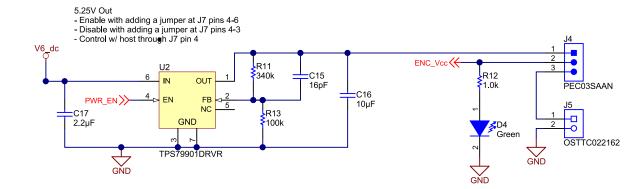

The output voltage of the TPS79901 LDO is set with 1% feedback resistors R11 and R13 according to according to the Equation 13, where 1.193 V is the nominal value of the TPS79901 reference voltage:

$$V_{\text{ENC}_{\text{VCC}}} = 1.193 \text{ V} \times \left(1 + \frac{\text{R11}}{\text{R13}}\right) = 1.193 \times \left(1 + \frac{340\text{k}}{100\text{k}}\right) = 5.25 \text{ V}$$

(14)

Figure 4-11. Schematic of 5.25-V LDO for Encoder Supply

A jumper selects between the 5.25-V LDO output and an optional external supply, if desired. The signal PWR\_EN is default pull-up, but can be asserted to low from a host microcontroller to disable or power-cycle the encoder supply voltage (see Section 4.3).

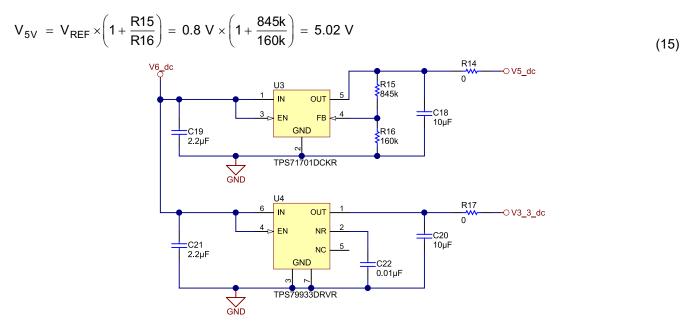

#### 4.2.3 Signal Chain Power Supply 5 V and 3.3 V

Because of the low current demanded by the analog signal chain, as described in Section 4.1, and to achieve high-performance with very low noise, the LDO is again a mandatory choice. Indeed, because of the high PSRR featured by TI LDOs, the AC noise generated by the switcher is blocked and does not affect the noise sensitive analog parts, like the ADCs and the input buffers and amplifiers.

The 5-V rail is dedicated to the analog buffers and amplifiers as well as to the analog supply voltage of the ADS8354 ADC. The 3.3 V is dedicated to the digital supply of the ADS8354 and the comparators to ensure a 3.3-V interface to the host processor without the need for I/O level-shifters. Because of the low power consumptions of the selected components, an LDO each was selected for the 3.3-V and 5-V rail with a nominal output current of 100 mA.

A fixed 3.3-V LDO TPS79933 was used for the 3.3-V rail, the TPS71701 was used for the 5-V rail. The schematic is shown in Figure 4-12. The 5-V output voltage is set by the feedback resistors R15 and R16 with the TPS71701  $V_{REF}$  = 0.8 V, according to Equation 15.

Figure 4-12. Schematic for 5-V and 3.3-V PoL for Signal Chain

## 4.3 Host Processor Interface

## 4.3.1 Signal Description

A 10-pin header interface is available to connect to a host processor. The header provides the necessary signals to calculate the high-resolution interpolated angle for both signal paths, using the ADS8354 dual 16-bit ADC and an embedded dual S/H ADC, if available.

The interface is compliant to 3.3-V I/O systems. To have a solid GND connection, all odd pins are assigned to GND. The signals available are listed in Table 4-1.

| Table 4-1 | . TIDA-00176 Interface | Connector to Host MCU |

|-----------|------------------------|-----------------------|

|           |                        |                       |

| FUNCTION                                       | SIGNALS   | I/O (3.3 V)                                              | COMMENT                                                                                                                                                                                                                              |

|------------------------------------------------|-----------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | SDI (I)   | Digital input                                            | Data input for serial communication.<br>Used for configuration of dual sampling<br>mode                                                                                                                                              |

| 16-bit high-resolution output channel for A, B | /CS (I)   | Digital input                                            | Chip-select signal; active low. Falling<br>edge of /CS latches the analog input<br>(Hold) and initiates a new conversion.<br>Use falling edge of /CS to latch<br>QEP counter on host processor<br>synchronously, like on Piccolo MCU |

| with ADS8354 and SPI (Slave)                   | SCLK (I)  | Digital input, up to 24 MHz                              | Clock for serial communication                                                                                                                                                                                                       |

|                                                | SDO_A (O) | Digital output                                           | Data output for serial communication,<br>channel A and channel B. 16-bit 2's<br>complementary data on each channel<br>A and channel B. Input to output signal<br>gain = 5.                                                           |

|                                                | SDO_B (O) | Digital output                                           | Data output for serial communication channel B                                                                                                                                                                                       |

| Digital guadrature encoded signals A, B and    | ATTL (O)  | Digital output                                           | 160mV hysteresis for A, B, and R, configurable                                                                                                                                                                                       |

| index Marker R                                 | BTTL (O)  | Digital output                                           |                                                                                                                                                                                                                                      |

|                                                | RTTL (O)  | Digital output                                           |                                                                                                                                                                                                                                      |

| Analog single-ended output channel for A and   | A/sin (O) | Analog output: 0 to 3.3 V,<br>1.65-V bias (single-ended) | Nominal output range:<br>0.82 V – 2.48 V (1.65 ±0.83 V) for 1<br>V <sub>PP</sub> , gain = 1.66, bias voltage = 1.65 V                                                                                                                |

| В                                              | B/cos (O) | Analog output: 0 to 3.3 V,<br>1.65-V bias (single-ended) | Nominal output range:<br>0.82 V – 2.48 V (1.65 ±0.83 V) for 1<br>V <sub>PP</sub> , gain = 1.66, bias voltage = 1.65 V                                                                                                                |

For details on the connector pin assignment, refer to Section 6.

## CAUTION

To synchronize the analog input sample of the ADS8354 16-bit dual sampling ADC with a QEP incremental counter module, use the /CS signal to the ADS8354 to latch the QEP counter as well. For an MCU like Piccolo, the /CS need to be connected to the eQEP Strobe input pin EPEPxS, where x is the module number. The Piccolo eQEPx module can be configured to latch the QEP counter on a falling edge of the EQEPxS pin.

#### 4.3.2 High-Resolution Path Using 16-Bit Dual ADC ADS8354 With Serial Output

This section outlines the configuration of the ADS8354 through the serial interface. This is split into programming the full-scale input voltage range with the internal ADS8354 reference as well as the serial data transfer.

#### 4.3.2.1 ADS8354 Input Full Scale Range Output Data Format

For use in this design, the ADS8354 is intended to be configured for  $\pm 2 \times V_{REF}$  input range. The internal reference voltage V<sub>REF</sub> should be set to 2.5 V, to yield a  $\pm 5$ -V FSR.

| INPUT VOLTAGE:<br>AINP_x – AINM_x | MODE                         | INPUT VOLTAGE | OUTPUT CODE (HEX) |

|-----------------------------------|------------------------------|---------------|-------------------|

| < -5 V                            |                              | NFSC          | 8000              |

| –5 V + 1 LSB                      |                              | NFSR          | 8001              |

| -1 LSB                            | $\pm 2 \times V_{REF}$ RANGE | –1 LSB        | FFFF              |

| 0                                 |                              | 0             | 0000              |

| > 5 V – 1 LSB                     |                              | PFSR – 1 LSB  | 7FFF              |

#### Table 4-2. ADS8354 Transfer Characteristic for TIDA-00176

The output date format for each channel A and B is 16-bit signed integer output (2's complementary).

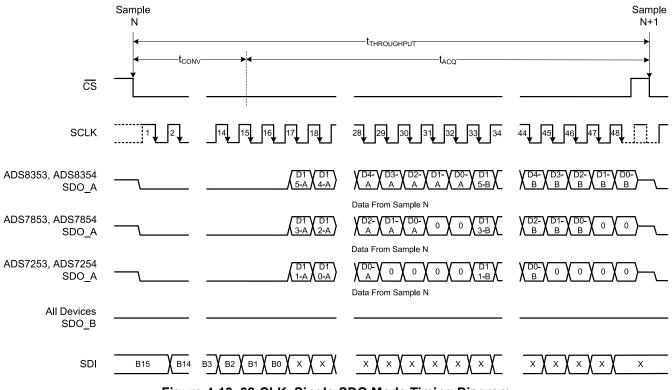

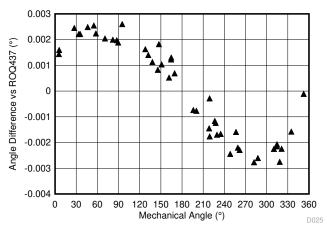

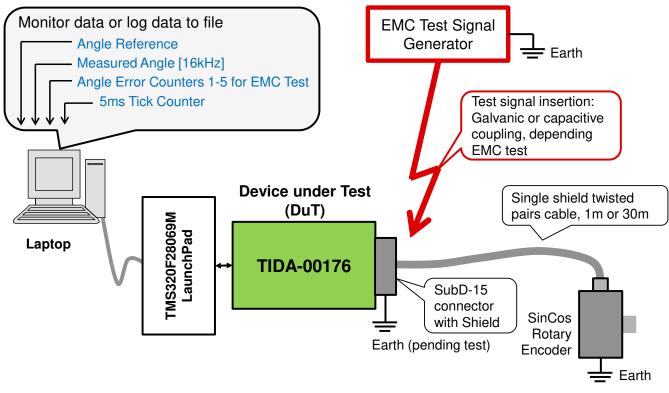

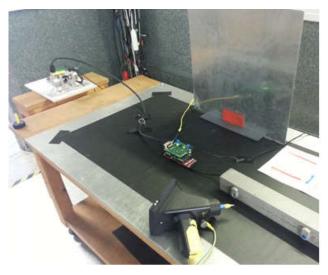

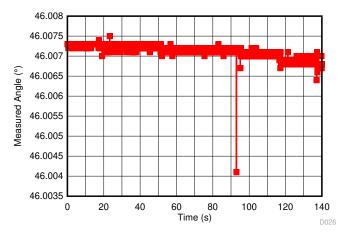

#### 4.3.2.2 ADS8354 Serial Interface