# TIDA-00417 DS125BR820 40GbE/10GbE QSFP Reference Design – User's Guide

Version 2 May 2015

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein and patents which might be granted thereon disclosing or employing the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments. No disclosure of information or drawings shall be made to any other person or organization without the prior consent of Texas Instruments.

### **Table of Contents**

| 1 | Document Revision History                       |    |

|---|-------------------------------------------------|----|

|   | Important Note Regarding TIDA-00417 PCB Routing |    |

|   | Software/Hardware Description and Setup         |    |

|   | 3.1 Procedure                                   | 5  |

|   | 3.2 Hardware notes                              | 8  |

| 4 | Recommended DS125BR820 settings                 |    |

| 5 | EVM Cable Assemblies                            | 12 |

## 1 Document Revision History

| Revision | Comment                                                                                                  | Date        |

|----------|----------------------------------------------------------------------------------------------------------|-------------|

| 1        | Initial creation of user's guide.                                                                        | 16-Dec-2014 |

| 2        | <ul> <li>Added note regarding high-speed layout and the importance of<br/>avoiding crosstalk.</li> </ul> | 05-May-2015 |

## 2 Important Note Regarding TIDA-00417 PCB Routing

This PCB's high-speed signals have been routed using a trace width and trace spacing of ~7 mils and ~15 mils, respectively. As such, the inter-pair coupling (i.e. coupling from one differential pair to an adjacent differential pair) on this PCB is relatively high, which can lead to unwanted crosstalk.

It is therefore recommended to use more tightly-coupled routing with accordingly smaller trace width and spacing. For example, ~6 mil trace width and ~5 mil trace spacing would allow for better inter-pair isolation and reduced crosstalk. Steps should be taken to ensure the desired impedance (i.e.  $100\Omega$  differential) is maintained when adjusting the trace width and spacing.

## 3 Software/Hardware Description and Setup

#### 3.1 Procedure

The general procedure for setting up and testing with the TIDA-00417 Reference Design is as follows:

- 1. **(One-time step)** Install the TI SigCon Architect GUI software:

- a. If your PC already has the National Instruments runtime library, then you can download and install the stand-alone TI SigCon Architect:

http://www.ti.com/lit/zip/snlc055

- b. If your PC does not have the National Instruments runtime library, then you can download and install the combined package: http://www.ti.com/lit/zip/snlc054

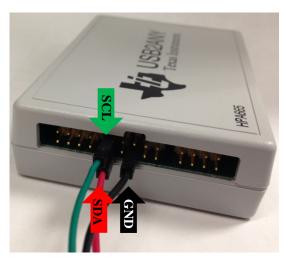

- Connect the EVM to a PC and to the board (connector J1) using a USB2ANY dongle. The pins on the USB2ANY which correspond to I2C/SMBus are highlighted below. Connector J1 on the board has GND on pin 1, SCL on pin 3, and SDA on pin 4.

- Connect power to the board. The DS125BR820 supports either 2.5V or 3.3V supply.

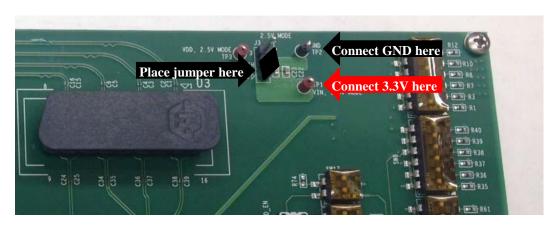

- a. 3.3V use case instructions:

- i. VDD\_SEL pin on the DS125BR820 devices must be connected to GND. **Do this by setting SW9 position 1 to ON.**

- ii. Connect VIH to the VIN pins on the DS125BR820 devices. **Do this** by placing a jumper between pins 1&2 on header J3.

- iii. Connect a 3.3V DC power supply (500mA max) between TP1 (VIN) and TP2 (GND)

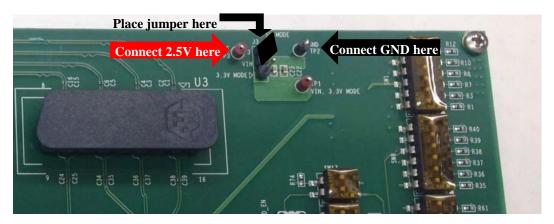

- b. 2.5V use case instructions:

- i. VDD\_SEL pin on the DS125BR820 devices must be floating. Do this by setting SW9 position 1 to OFF.

- ii. Connect VIH to the VDD pins on the DS125BR820 devices. **Do this** by placing a jumper between pins 2&3 on header J3.

- iii. Connect a 2.5V DC power supply (650mA max) between TP3 (VDD) and TP2 (GND)

Figure 1: 3.3V mode connections (Note: SW9 position 1 must also be set to ON)

Figure 2: 2.5V mode connections (Note: SW9 position 1 must also be set to OFF)

4. Connect the high-speed signals between the QSFP+ port and the ASIC or scope. Likewise, connect the high-speed signals between the Huber+Suhner connectors and the ASIC or scope. This connection requires a Huber+Suhner 2x8 MXP cable assembly. Refer to Section 5 for more details.

This reference board has two 8-channel DS125BR820 devices, one to support all ingress signals, and one to support all egress signals from a stacked QSFP+ cage. The following table explains the mapping:

Table 1: Mapping between QSFP+ port and high-speed connectors

| QFSP Port | QSFP Lane | Direction | Host-side<br>Huber+Suhner<br>connector pin<br>P/N | Repeater<br>channel | GUI Repeater<br>address /<br>channel |

|-----------|-----------|-----------|---------------------------------------------------|---------------------|--------------------------------------|

|           | 1         | Ingress   | U4.4 / U4.3                                       | U1.INB_3            | 0xB2, Ch3                            |

|           | l         | Egress    | U4.13 / U4.14                                     | U2.INA_0            | 0xB0, Ch4                            |

|           | 2         | Ingress   | U4.6 / U4.5                                       | U1.INB_2            | 0xB2, Ch2                            |

| Тор       |           | Egress    | U4.9 / U4.10                                      | U2.INA_2            | 0xB0, Ch6                            |

| ТОР       | 3         | Ingress   | U4.2 / U4.1                                       | U1.INA_0            | 0xB2, Ch4                            |

|           |           | Egress    | U4.11 / U4.12                                     | U2.INA_1            | 0xB0, Ch5                            |

|           | 4         | Ingress   | U4.8 / U4.7                                       | U1.INB_1            | 0xB2, Ch1                            |

|           |           | Egress    | U4.15 / U4.16                                     | U2.INB_3            | 0xB0, Ch3                            |

|           | 1         | Ingress   | U3.15 / U3.16                                     | U1.INA_3            | 0xB2, Ch7                            |

|           |           | Egress    | U3.5 / U3.6                                       | U2.INB_2            | 0xB0, Ch2                            |

|           | 2         | Ingress   | U3.11 / U3.12                                     | U1.INA_1            | 0xB2, Ch5                            |

| Bottom    |           | Egress    | U3.3 / U3.4                                       | U2.INB_1            | 0xB0, Ch1                            |

| Bottom    | 3         | Ingress   | U3.13 / U3.14                                     | U1.INA_2            | 0xB2, Ch6                            |

|           |           | Egress    | U3.8 / U3.7                                       | U2.INA_3            | 0xB0, Ch7                            |

|           | 4         | Ingress   | U3.9 / U3.10                                      | U1.INB_0            | 0xB2, Ch0                            |

|           |           | Egress    | U3.1 / U3.2                                       | U2.INB_0            | 0xB0, Ch0                            |

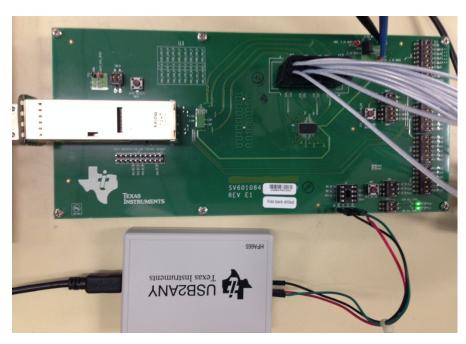

Figure 3: Example of Power, USB2ANY, and high-speed connections to the board

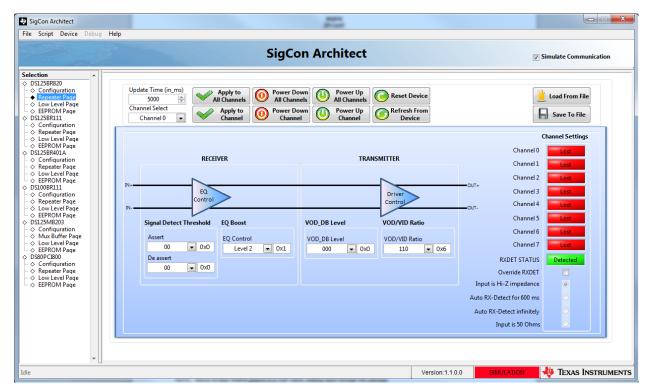

1. Launch the TI SigCon Architect GUI to control the two DS125BR820 devices on the board. As shown in Table 1, the Repeater at address 0xB0 is responsible for all the Egress channels (top and bottom port), and the Repeater at address 0xB2 is responsible for all the ingress channels (top and bottom port). Figure 4 shows an example of the SigCon architect GUI with the recommended default configuration for EQ and VOD.

Figure 4: Example of TI SigCon Architect GUI, showing the recommended default configuration for EQ and VOD

#### 3.2 Hardware notes

TI SigCon Architect GUI is the recommended means of configuring the devices on the board. The devices can also be configured via pin strapping using the switches available on the board. Table 2 lists the switches available, their function, and their recommended default state.

**Table 2: Pin control switches**

| Switch<br># | Switch position(s) | Function                                                               | Recommende d default state | Comment                                                                                                               |  |

|-------------|--------------------|------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

| SW1         | 1-3                | Egress repeater AD3 / EQB pin control                                  | OFF-OFF-ON                 | Used to set SMBus address since default is SMBus slave mode.                                                          |  |

|             | 4-6                | Egress repeater AD2 pin control                                        | OFF-OFF- <b>ON</b>         | Used to set SMBus address since default is SMBus slave mode. This must be 1K to GND in pin mode (OFF-OFF- <b>ON</b> ) |  |

| SW2         | 1-2                | Connects board I2C bus to<br>Egress repeater I2C pins                  | ON-ON                      | Set to OFF if you want to disconnect the Egress repeater from the board I2C bus.                                      |  |

| SW3         | 1-3                | Egress repeater AD1 / VODB0 pin control                                | OFF-OFF-ON                 | Used to set SMBus address since default is SMBus slave mode.                                                          |  |

|             | 4-6                | Egress repeater AD0 / VODB1 pin control                                | OFF-OFF-ON                 | Used to set SMBus address since default is SMBus slave mode.                                                          |  |

| SW4         | 1-3                | Egress repeater VODA0 pin control                                      | OFF-OFF-OFF                | Floating by default since these pins are used as I2C in SMBus                                                         |  |

|             | 4-6                | Egress repeater VODA1 pin control                                      | OFF-OFF-OFF                | slave mode.                                                                                                           |  |

| SW5         | 1-3                | Egress repeater EQA pin control                                        | OFF-OFF-ON                 | EQ will be controlled in registers in SMBus slave mode.                                                               |  |

|             | 4-6                | Egress repeater RESERVED3 pin control                                  | OFF-OFF-ON                 | Can be floating, 1K to VDD, or 1K to GND                                                                              |  |

| SW6         | 1-3                | Egress repeater SD_TH pin control                                      | OFF-OFF- <b>ON</b>         | This pin not used in SMBus slave mode. Triggers EEPROM read in SMBus Master mode.                                     |  |

| SW8         | 1-3                | Egress repeater EN_SMB pin control                                     | ON-OFF-OFF                 | EN_SMB=1 by default, to configure for SMBus slave mode. Set this to OFF-OFF- <b>ON</b> to enter pin control mode.     |  |

|             | 4-6                | Egress repeater RESERVED2 pin control                                  | OFF-OFF-OFF                | Pin is floating by default.                                                                                           |  |

| SW9         | 1                  | VDD select. ON: VDD_SEL=GND → 3.3V mode OFF: VDD_SEL=Float → 2.5V mode | ON                         | 3.3V mode by default.                                                                                                 |  |

|             | 2                  | Egress repeater PWDN pin control                                       | ON                         | Set to ON for normal operation, OFF for powerdown.                                                                    |  |

| SW10        | 1-3                | Ingress repeater AD3 / EQB pin control                                 | OFF-OFF- <b>ON</b>         | Used to set SMBus address since default is SMBus slave mode.                                                          |  |

|             | 4-6                | Ingress repeater AD2 pin control                                       | OFF-OFF- <b>ON</b>         | Used to set SMBus address since default is SMBus slave mode. This must be 1K to GND in pin mode (OFF-OFF- <b>ON</b> ) |  |

| Switch  | Switch      | Function                                            | Recommende      | Comment                                 |

|---------|-------------|-----------------------------------------------------|-----------------|-----------------------------------------|

| #       | position(s) |                                                     | d default state |                                         |

| SW11    | 1-3         | Ingress repeater VODA0 pin                          | OFF-OFF-OFF     | Floating by default since these         |

|         |             | control                                             |                 | pins are used as I2C in SMBus           |

|         | 4-6         | Ingress repeater VODA1 pin                          | OFF-OFF-OFF     | slave mode.                             |

|         |             | control                                             |                 |                                         |

| SW12    | 1-3         | Ingress repeater AD1 /                              | OFF-OFF-ON      | Used to set SMBus address since         |

|         |             | VODB0 pin control                                   |                 | default is SMBus slave mode.            |

|         | 4-6         | Ingress repeater AD0 /                              | OFF-OFF-ON      | Used to set SMBus address since         |

|         |             | VODB1 pin control                                   |                 | default is SMBus slave mode.            |

| SW13    | 1-2         | Connects board I2C bus to                           | ON-ON           | Set to OFF if you want to               |

|         |             | Ingress repeater I2C pins                           |                 | disconnect the Ingress repeater         |

| 0)4/4/4 |             |                                                     | 055 055 011     | from the board I2C bus.                 |

| SW14    | 1-3         | Ingress repeater EQA pin                            | OFF-OFF-ON      | EQ will be controlled in registers      |

|         |             | control                                             | OFF OFF ON      | in SMBus slave mode.                    |

|         | 4-6         | Ingress repeater                                    | OFF-OFF-ON      | Can be floating, 1K to VDD, or 1K       |

| 0)4/45  | 4.0         | RESERVED3 pin control                               | 055 055 055     | to GND                                  |

| SW15    | 1-3         | Ingress repeater SD_TH pin control                  | OFF-OFF-OFF     | This pin not used in SMBus slave mode.  |

| SW17    | 1           |                                                     | ON              | mode.                                   |

| SW17    | 1           | Connects Egress repeater ALL_DONE signal to Ingress | ON              |                                         |

|         |             | repeater READ_EN signal                             |                 |                                         |

|         |             | so that repeaters can read                          |                 |                                         |

|         |             | from EEPROM in                                      |                 |                                         |

|         |             | succession in SMBus Master                          |                 |                                         |

|         |             | mode                                                |                 |                                         |

|         | 2           | Ingress repeater PWDN pin                           | ON              | Set to ON for normal operation,         |

|         | _           | control                                             |                 | OFF for powerdown.                      |

| SW18    | 1-3         | Ingress repeater EN_SMB                             | ON-OFF-OFF      | EN_SMB=1 by default, to                 |

|         |             | pin control                                         |                 | configure for SMBus slave mode.         |

|         |             |                                                     |                 | Set this to OFF-OFF- <b>ON</b> to enter |

|         |             |                                                     |                 | pin control mode.                       |

|         | 4-6         | Ingress repeater                                    | OFF-OFF-OFF     | Pin is floating by default.             |

|         |             | RESERVED2 pin control                               |                 |                                         |

| SW19    | 1-2         | Connects QSFP I2C signals                           | OFF-OFF         | QSFP I2C not connected by               |

|         |             | to the board I2C bus                                |                 | default.                                |

## 4 Recommended DS125BR820 settings

In general, the Egress repeater is used to compensate for a portion of the host channel loss, specifically the loss which exceeds the SFF-8431 host channel specification. The Ingress repeater is also used to compensate for the host channel loss. If necessary, the Ingress repeater can be used to compensate for a portion of the passive copper cable. To avoid having to use settings specific to cable length, it is recommended that the Ingress repeater be configured to compensate only for the host channel loss.

The following settings have been shown to be generally good for most front-port QSFP+ applications.

Table 3: DS125BR820 settings used for Egress and Ingress testing

|         | EQ Setting              | g                                        | VOD Setting |                                         |                                          |                                      |

|---------|-------------------------|------------------------------------------|-------------|-----------------------------------------|------------------------------------------|--------------------------------------|

| Value   | Pin strap               | Equivalent register setting <sup>1</sup> | Value       | Pin strap                               | Equivalent register setting <sup>2</sup> | Comments                             |

| Level 1 | <b>0</b> : 1 kΩ to GND  | $Reg_0xF = 0x00$                         | Level 6     | VODA1= VODB1=1                          |                                          | Different EQ                         |

| Level 2 | <b>R</b> : 20 kΩ to GND | Reg_0xF = 0x01                           |             | (1 kΩ to VIH)<br>VODA0= VODB0= <b>0</b> |                                          | settings used for<br>different input |

| Level 3 | F: Floating             | Reg_0xF = 0x02                           | ]           | (1 kΩ to GND)                           |                                          | channel length.<br>VOD Level 6 used  |

| Level 4 | <b>1</b> : 1 kΩ to VIH  | $Reg_0xF = 0x03$                         |             |                                         |                                          | for all channels.                    |

<sup>&</sup>lt;sup>1</sup>Each channel has its own EQ control register. Reg\_0x0F controls channel 0, Reg\_0x16 controls channel 1, and so on.

<sup>&</sup>lt;sup>2</sup>Each channel has its own VOD control register. Reg\_0x10 controls channel 0. Reg\_0x17 controls channel 1, and so on.

## 5 EVM Cable Assemblies

This reference design uses Huber+Suhner 2x8 MXP cable assemblies to access the host-side signals.

Contact Huber+Suhner to inquire about cable assembly availability and pricing.

There are two part numbers that TI suggests using with this EVM:

- 1. 84098901, MF53/2x8A\_21MXP/11SK/229. This cable assembly is 9in long and terminates in "male" SMA connectors.

- 2. 84098908, MF53/2x8A\_21MXP/21SK\_ergo/305. This cable assembly is 9in long and terminates in "female" SMA connectors.

#### IMPORTANT NOTICE FOR TI REFERENCE DESIGNS

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design. TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have *not* been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.