# TI Designs Self-Powered Isolated RS-232 to UART Interface

# 🦉 Texas Instruments

# **TI Designs**

TI Designs provide the foundation that you need including methodology, testing and design files to quickly evaluate and customize the system. TI Designs help *you* accelerate your time to market.

#### **Design Resources**

| TIDA-00163   | Tool Folder Containing Design Files |

|--------------|-------------------------------------|

| ISO7421      | Product Folder                      |

| TRS3232      | Product Folder                      |

| TPS7633      | Product Folder                      |

| EVM430-F6779 | Product Folder                      |

#### **Design Features**

- High Voltage RS-232 Isolation

- Bit Rates Up to 1 Mbps

- 2-kV Operating Isolation Boundary

- Integrated Power Harvesting for Isolation and RS-232 Transceiver

- Operates with 5-V to 12-V RS-232 drivers

#### **Featured Applications**

- Energy Meters

- Non-Isolated HV Sensing

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

WEBBENCH is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 1 System Description

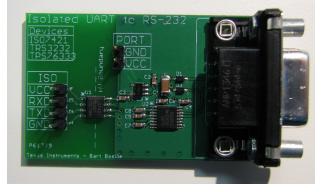

Many sensing applications are designed around low power microcontroller units (MCUs), which do not require isolated power supply designs. In order to save costs, many systems use capacitive-drop power supplies as opposed to transformer-based designs. Using capacitive-drop power designs puts a sensing solution at a very high voltage in relation to a potentially connected host computer. The high voltage creates the need for an isolation boundary.

The RS-232 interface from a host computer is still very popular in the industrial space due to the robust nature of the interface and low cost. However, to facilitate proper RS-232 translation to an embedded system requires an intermediate-level shifting stage. The CMOS TTL voltages are typically in the 3.3-V to 5-V range, while the RS-232 can be near 12 V. Powering the translation on the RS-232 side of the isolation boundary typically requires addition of an isolation power supply to RS-232 interface. The added power supply means unwanted cost to the system. By harvesting power from the RS-232 protocol itself, a fully-isolated, self-powered converter can be implemented.

The TI portfolio offers devices in a broad range of products. Most notably for this industrial design, TI offers products in isolation, interface charge pumps, and power management. By choosing the correct combination of products, a system can be designed to meet the requirements of these isolated industrial interfaces.

#### 2 Design Features

#### 2.1 Power Harvesting

In order to power the data terminal equipment (DTE) side of the isolation boundary and the RS-232 charge pump, there are two choices. The interface can either implement an isolated power supply or harvest power from the RS-232 line. Integrating a power supply adds cost and complexity to the system, which is difficult to justify in low-cost sensing applications.

To implement the second option of harvesting power from the RS-232 port itself, this design utilizes the flow control lines that are ignored in most embedded applications. The RS-232 specification (when properly implemented on a host computer or adapter cable) keeps the RTS and DTR lines high when the port is active. As long as the host has the COM port open, these two lines will have voltage on them. This voltage can vary from 5 V to 12 V, depending on the driver implementation. 5 V to 12 V is sufficient for the usage needed in this design.

The voltage is put through a diode arrangement to block signals from entering back into the pins. The voltage goes through a capacitor to store energy. Then the capacitor release this energy when the barrier and charge pump pull more current than is instantaneously allowed. A simple low dropout (LDO) is sufficient to bring the line voltage down to a working voltage of 3.3 V for the charge pump and isolation device.

The downside of this design is that the total current available to the devices on the RS-232 side of the boundary are limited to only a few mA (~5), largely depending on what type of driver is available on the DTE side of the RS-232 connection. The following segments will discuss designing the remainder of the system to account for the driver type.

#### 2.2 Isolation Boundary

This design uses capacitive galvanic isolation, which has an inherent life span advantage over an optoisolator. Industrial devices are typically pressed into service for much longer periods of time than consumer electronics. Therefore, maintenance of effective isolation over a period of 15+ years is important.

The TI ISO7421 device is a simple dual channel isolator which only draws ~4 mA. The TI ISO7421 device is capable of operating at 3.3 V or 5 V, enabling a wide range of devices to be connected to the DCE side of the interface. The ISO7421 device can simply be inserted into a UART signal path, with the appropriate power supplies on each side to enable operation. The ISO7421 device also maintains 2.5 kV of isolation and 4-kV peak in order to meet UL certification levels.

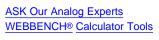

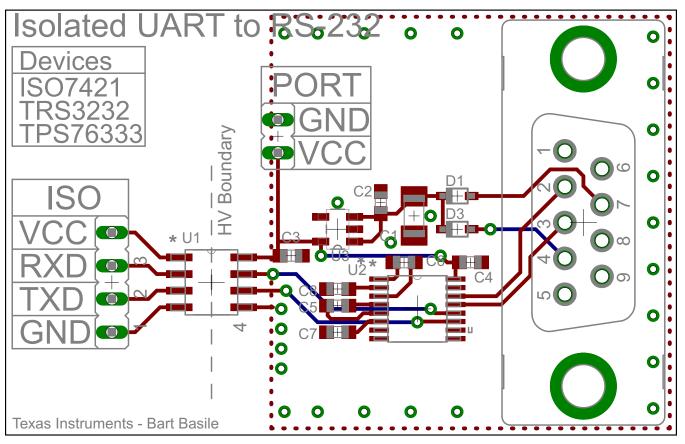

It is important to remember during layout that the traces with high voltage differentials should be kept as far away from each other as possible. Therefore, no signals or ground pours should be placed under the device. All traces should come directly into the device pads. Please see the reference design layout in Section 7.

## 2.3 RS-232 Charge Pump

To properly interface with the RS-232 standard, a voltage translation system is required to go from the 3.3-V domain on the isolated side of the interface and from the 12 V on the port itself. To facilitate the translation, the design uses a TPS3232 device. The TPS3232 device is capable of driving the higher voltage signals on the RS-232 port from only 3.3-V V<sub>cc</sub> via a charge pump system.

## 3 Block Diagram

Figure 1. System Block Diagram

#### 4 Test Setup and Results

#### 4.1 Power Supply Test

To verify the power harvesting design, the board was connected to several off-the-shelf USB to RS-232 converters. Each of these converters can have a different driver device to generate the RS-232 compliant signals, which results in various TTL voltage levels. In testing, each converter had its TTL level measured. This design uses a 5-V and a 12-V model.

Once connected to the DUT and the USB port of a computer, the COM port must be opened in software in order to enable the RTS and DTR lines of the RS-232 port. This design uses Putty, a popular terminal emulation application. At this point, Putty is only used to open the port, not communicate any data. For each of the converters used, the GND and  $V_{cc}$  pins on the board were measured with a multimeter, reading the expected 3.3 V each time.

#### 4.2 Hardware Loopback Test

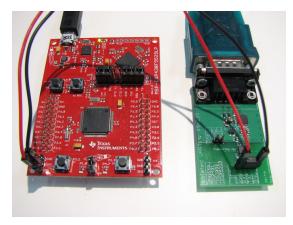

To determine functional operation, a jumper was placed between the RXD and TXD pins on the isolated input headers. Using the jumper results in any character being transmitted to immediately echo back. To power this side of the isolator, a second EVM is used that is capable of producing both 3.3 V and 5 V, in order to evaluate usage for diverse host processors. The connection setup is shown in Figure 2.

Figure 2. Hardware Loopback

The port was reopened in Putty using the standard port settings (9600 baud, 8 data bits, 1 stop bit, no parity, and no flow control) that interacts with embedded system UART protocols well. Via the now open terminal session, a test string was repeatedly sent. On a correct echo, the terminal would read exactly what was sent out on the line. To help observe for errors, the window was sized to easily show a continuous stream of repeated text. The test results are shown in Figure 3.

| PuTTY (inactive) |       |       |     |        |      |     |      |     |   |

|------------------|-------|-------|-----|--------|------|-----|------|-----|---|

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog | ~ |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog | = |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog |   |

| The              | Quick | Brown | Fox | Jumped | Over | The | Lazy | Dog | Ŧ |

Figure 3. Echo Test Output

This test was also repeated with a data rate of 1 Mbaud, and with a 5-V supply on the input connection with no issues. The tests show that from the isolation boundaries' standpoint, the communication remains robust across different host designs.

#### 4.3 Software Connection

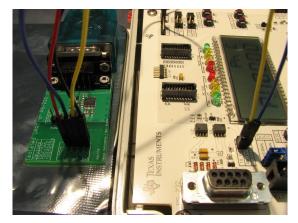

To evaluate integration into a full system, the reference design was connected to a TI EVM430-F6779 emetering EVM. The EVM is powered by a nonisolated capacitive-drop power supply. The EVM has headers for UART communication and power. The EVM comes with software that enables the EVM to communicate with a PC via a serial port. The EVM430-F6779's communication and power features make the EVM a perfect test bed for this isolated reference design.

The EVM was connected as shown in Figure 4. The EVM disconnects the onboard isolated UART and replaces the UART with the daughter board. Once connected, the EVM was able to be used as described in *Implementation of a Three-Phase Electronic Watt-Hour Meter Using the MSP430F677x*, literature number SLAA577.

Figure 4. E-Meter EVM Connection

#### Schematics

www.ti.com

#### 5 Schematics

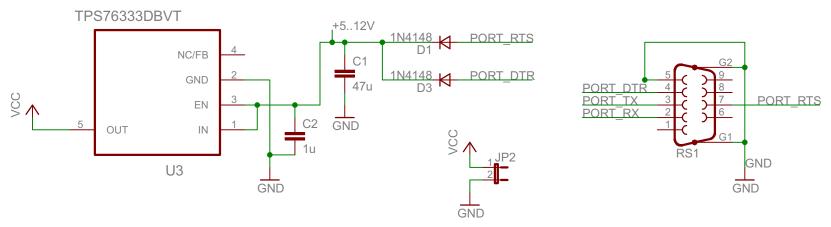

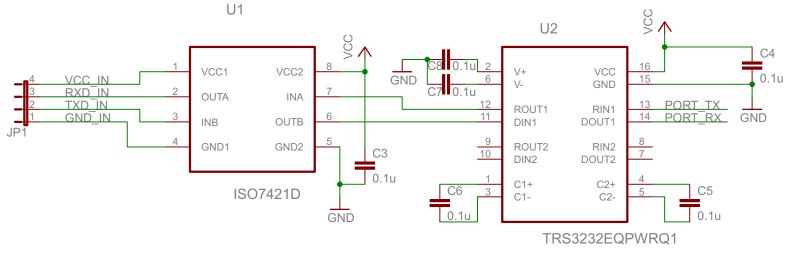

To download the Schematics, see the design files at TIDA-00163.

Figure 5. Schematic

# 6 Bill of Materials

To download the bill of materials (BOM), see the design files at <u>www.ti.com/tool/TIDA-00163</u>. Table 1 shows the BOM for this design.

| DESIGNATOR                | QUANTITY | VALUE          | DESCRIPTION                                        | PACKAGEREFERENCE   | PARTNUMBER          | DISTRIBUTOR |

|---------------------------|----------|----------------|----------------------------------------------------|--------------------|---------------------|-------------|

| RS1                       | 1        |                | SUB-D                                              | F09VP              | A32119-ND           | Digi-Key    |

| JP4                       | 1        |                | JUMPER                                             | JP1                | 609-4434-ND         | Digi-Key    |

| JP2                       | 1        |                | JUMPER                                             | JP2Q               | 609-3201-ND         | Digi-Key    |

| JP1                       | 1        |                | JUMPER                                             | JP4                | 609-3319-ND         | Digi-Key    |

| JP5                       | 1        |                | JUMPER                                             | JP4Q               | 609-3203-ND         | Digi-Key    |

| C4, C5, C6, C7, C8,<br>C9 | 6        | 0.1u           | CAPACITOR, European symbol                         | С0805К             | 445-5956-1-ND       | Digi-Key    |

| D1, D2, D3                | 3        | 1N4148         | DIODE                                              | SOD323             | 1N4148WSFSCT-<br>ND | Digi-Key    |

| R1, R2, R3                | 3        | 1k             | RESISTOR, European symbol                          | R0603              | P1.0KGCT-ND         | Digi-Key    |

| C3                        | 1        | 1u             | CAPACITOR, European symbol                         | С0805К             | 445-5956-1-ND       | Digi-Key    |

| C1, C2                    | 2        | 47u            | CAPACITOR, European symbol                         | С1206К             | 445-8047-1-ND       | Digi-Key    |

| U1                        | 1        | ISO7421D       | Low-Power Dual Digital<br>Isolators                | SOIC127P600X175-8N | 296-25187-5-ND      | Digi-Key    |

| U5                        | 1        | TPS76333DBVT   | Low Power 150mA Low<br>Dropout Linear<br>Regulator | SOT95P280X145-5N   | 296-11021-1-ND      | Digi-Key    |

| U2                        | 1        | TRS3232EQPWRQ1 | RS-232 LINE<br>DRIVER/RECEIVER                     | SOP65P640X120-16N  | 296-24863-1-ND      | Digi-Key    |

Table 1. Bill of Materials

Bill of Materials

Layer Plots

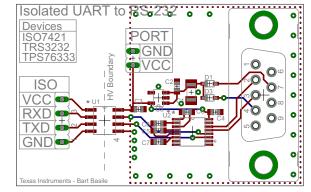

#### 7 Layer Plots

To download the layer plots, see the design files at <u>www.ti.com/tool/TIDA-00163</u>. Figure 6 shows the layer plot for this design.

Figure 6. Layer Plot

# 8 Altium Project

To download the Altium files, see the design files at <u>www.ti.com/tool/TIDA-00163</u>.

#### 9 Gerber Files

To download the Gerber files, see the design files at www.ti.com/tool/TIDA-00163.

#### 10 Software Files

To download the software files, see the design files at <u>www.ti.com/tool/TIDA-00163</u>.

#### 11 About the Author

**BART BASILE** is a systems and applications engineer in the Texas Instruments Smart Grid Solutions Team, focusing on the e-metering and grid infrastructure industries. Bart works across multiple product families and technologies to leverage the best solutions possible for system level application design. Bart received his Bachelors of Science in Electronic Engineering from Texas A&M University.

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have *not* been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2014, Texas Instruments Incorporated