# Power Supply Design Using the AC8025 SoC From AutoChips<sup>™</sup>

Linda Ye, Daoyan Zhao

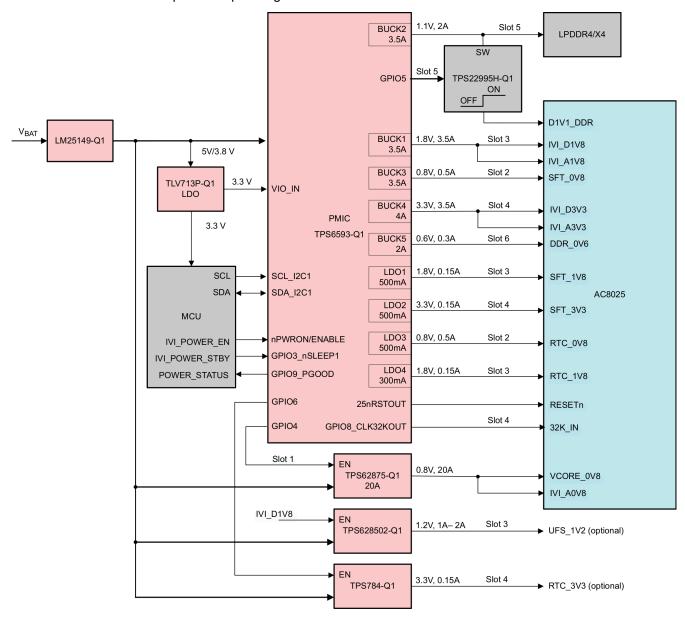

This application brief details the design considerations of the discrete power design for the AC8025 (from AutoChips™) system-on-chip (SoC) power rails with a power-management IC (PMIC) design. The design uses the TPS6593-Q1 PMIC, TPS62875-Q1 synchronous buck converters, and TPS745-Q1 low-dropout (LDO) regulators. The original power source is the battery. Then the battery voltage is converted to regulate the 5V or 3.8V bus. The LM25149-Q1 converts the battery voltage to regulate the bus voltage. All components in this design are automotive-qualified.

The TPS6593-Q1 IC has five buck converters and four LDOs. This PMIC is non-volatile memory (NVM) programmable, meaning the default register values are set in the TI production line to the desired values for this platform without further need for the customer to change settings. The full orderable part number for this one-time-programmable (OTP) spin is TPS6593C4C8RWERQ1. See the Technical Reference Manual for the specific part number for more details on the OTP settings.

This power design is an example of how required rails for AC8025 can be powered with TI PMIC, synchronous buck converters, and LDOs. This power design is possible to customize and optimize based on the actual use case regarding the SoC variant, current requirements, used peripherals, and so forth.

## **Design Parameters**

Table 1 shows the power rails, load requirements, and power group.

Table 1. Power Rails, Load Requirements, and Power Group

| Tuble 1.1 ower Runs, Edua Requirements, and 1 ower Group |             |             |             |

|----------------------------------------------------------|-------------|-------------|-------------|

| Power Rail                                               | Voltage (V) | Current (A) | Power Group |

| LPDDR4, LPDDX4                                           | 1.1         | 2           | 5           |

| D1V1_DDR                                                 | 1.1         |             | 5           |

| IVI_D1V8                                                 | 1.8         | 3.5         | 3           |

| IVI_A1V8                                                 | 1.8         |             | 3           |

| SFT_0V8                                                  | 0.8         | 0.5         | 2           |

| IVI_D3V3                                                 | 3.3         | 3.5         | 4           |

| IVI_A3V3                                                 | 3.3         |             | 4           |

| VDDQ_0V6                                                 | 0.6         | 0.3         | 6           |

| SFT_1V8                                                  | 1.8         | 0.15        | 3           |

| SFT_3V3                                                  | 3.3         | 0.15        | 4           |

| RTC_0V8                                                  | 0.8         | 0.15        | 2           |

| RTC_1V8                                                  | 1.8         | 0.15        | 3           |

| VCORE_0V8                                                | 0.8         | _           | 1           |

| IVI_A0V8                                                 | 0.8         |             | 1           |

| UFS_1V2                                                  | 1.2         | 2           | 3           |

| RTC_3V3                                                  | 3.3         | 0.15        | 4           |

#### **Power Design**

Figure 1 shows a block diagram with LM25149-Q1, TPS6593-Q1, TPS62875-Q1, TPS628502-Q1, and TPS784-Q1 devices powering the AC8025 SoC power rails.

The main features of this power design include the following:

- Power sequencing for AC8025 rails are controlled with PMIC TPS6593-Q1

- The GPIO output on the TPS6593-Q1 device can be used to control the TPS62875-Q1, TPS628502-Q1, and TPS784-Q1 devices for power sequencing

Figure 1. AC8025 Power Tree Block Diagram

#### Sequencing

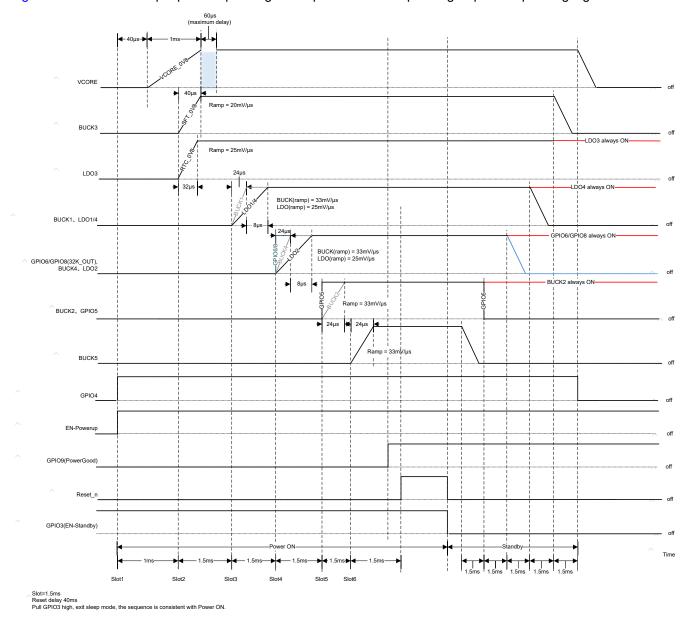

Figure 2 shows an example power-up timing of the power rails and power group corresponding signals.

Figure 2. Power Sequencing

## **Schematic**

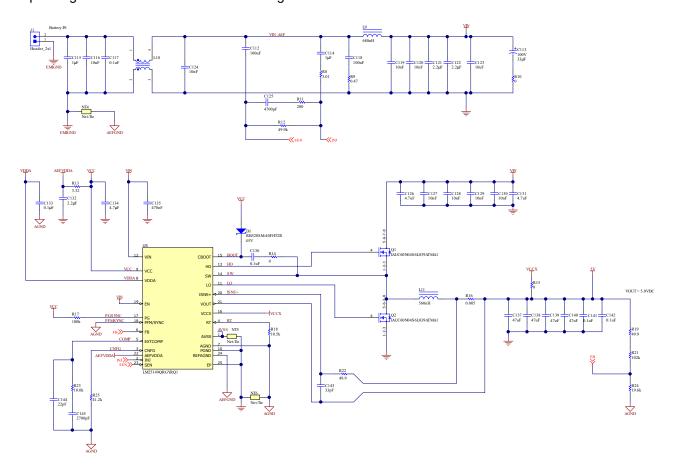

Figure 3 shows the LM25149-Q1 schematic with critical components. For layout guidance, see the corresponding device data sheet and EVM user guide.

Figure 3. LM25149-Q1 Schematic

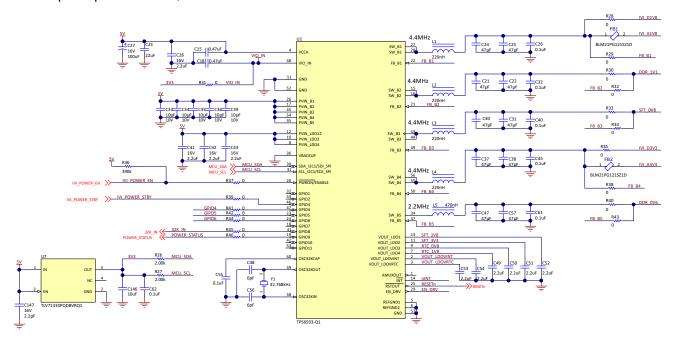

Figure 4 shows the TPS6593-Q1 and the LDO TLV793P-Q1 for MCU power supply schematic with critical components. For layout guidance, see the corresponding device data sheet and EVM user guide. For LDO input and output capacitor values, see the data sheet recommendation.

Figure 4. TPS6593-Q1 and the LDO for MCU Schematic

Figure 5 shows the TPS62875-Q1 schematic with critical components. For layout guidance, see the corresponding device data sheet and EVM user guide.

Figure 5. TPS62875-Q1 Schematic

Trademarks INSTRUMENTS

www.ti.com

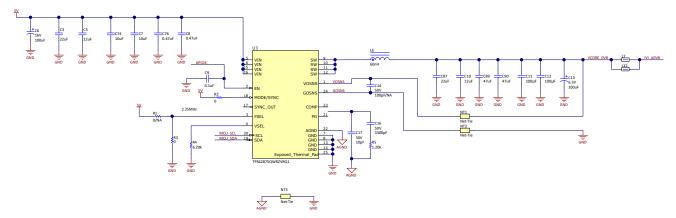

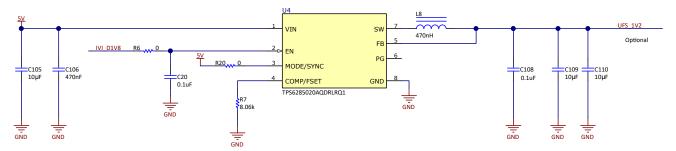

Figure 6 shows the TPS628502-Q1 schematic with critical components. For layout guidance, see the corresponding device data sheet and EVM user guide.

Figure 6. TPS628502-Q1 Schematic

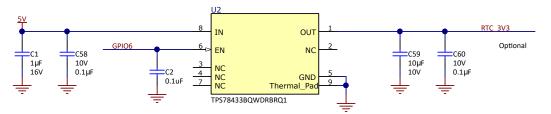

Figure 7 shows the TPS784-Q1 schematic with critical components. For layout guidance, see the corresponding device data sheet and EVM user guide.

Figure 7. TPS784-Q1 Schematic

## **Summary**

The design outlined in this application brief, using the LM25149-Q1, TPS6593-Q1, TPS62875-Q1, TPS628502-Q1, and TPS784-Q1 provides the power requirements for AutoChips AC8025 SoC while maintaining good efficiency. This design is compact due to the minimum number of external components. The I2C control allows for diagnostic testing and other control of the TPS6593-Q1 device.

#### **Trademarks**

AutoChips<sup>™</sup> is a trademark of NavInfo Co., Ltd.

All trademarks are the property of their respective owners.

From AutoChips

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated