# Technical Article **Powering modern AI data centers with industry's first integrated 48V integrated hot swap (eFuse)**

# TEXAS INSTRUMENTS

#### Kshitiz Khatri

As high-performance computing and artificial intelligence continue to grow, data centers demand power-dense, efficient solutions to support the latest central processing units, graphics processing units (GPUs) and hardware accelerators. The need for increased power density and a shift to 48V power architectures to accommodate processing demands introduces new challenges, however, particularly in managing power levels >6kW while maintaining reliability, efficiency and scalability.

Increasing power requirements often lead to larger solution sizes, complex designs, and inefficiencies in fault detection and protection. Additionally, managing high currents while ensuring safe operation and minimal power losses becomes an important concern. Traditional hot-swap controllers combined with discrete field-effect transistors (FETs) face significant limitations in high-power applications.

To address these challenges, TI's 48V hot-swap eFuse device with power-path protection is designed to be a reliable and compact solution for data center applications. Unlike approaches that require external sense resistors and current-sense amplifiers for current monitoring, the TPS1689 and TPS1685 simplifies designs by integrating these functionalities, reducing solution size upto 50% while enabling seamless scalability to support high power levels.

One of the differentiating features of the TPS1689 is the blanking timer, which prevents false tripping by enabling the system to distinguish between peak load currents and actual fault conditions. This feature enhances system reliability and avoids unnecessary shutdowns. The device also supports stacking capabilities for increased current handling, allowing multiple devices to work together in high-power applications.

An integrated black box for fault logging, a guaranteed FET safe operating area, active current sharing and health monitoring further enhance system resiliency. Available in an industry-standard common footprint, the TPS1689 provides a power-management solution that ensures reliable operation.

1

#### Enhancing server protection and performance

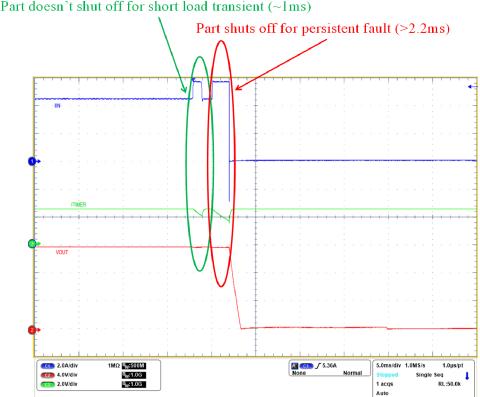

The blanking timer offers advantages in enterprise server systems by striking a balance between system protection and performance optimization. As shown in Figure 1, this feature enables short transient overloads to pass through without triggering a circuit breaker, ensuring that temporary, high-amplitude load pulses common in AI, GPU and processor-intensive applications do not disrupt the system. However, the eFuse promptly shuts down the circuit during sustained overcurrent events.

Other advantages include:

- Cost optimization. The blanking timer minimizes the need for oversized power-supply units (PSUs) and reduces the number of eFuses required in parallel configurations. This significantly lowers bill-of-materials costs while maintaining reliable operation.

- Improved power density. By reducing the number and size of high-current-carrying components, the system can achieve a more compact design, freeing up valuable printed circuit board (PCB) space and improving thermal management.

- Flexibility and customization. Programmable fault intervals enable designers to fine-tune the system response to match specific transient profiles, optimizing performance for unique workloads.

Figure 1. Overcurrent response (circuit breaker) after a user-defined blanking

You can set the overcurrent protection threshold to 1.1 times the thermal design current instead of accounting for maximum transient loads (typically 1.7 times). This approach reduces the size and cost of PSUs compared to conventional designs, which require the PSU to support the peak transient current. These benefits make the blanking timer a pivotal feature for high-performance server systems.

## Advanced stacking and current-sharing solutions

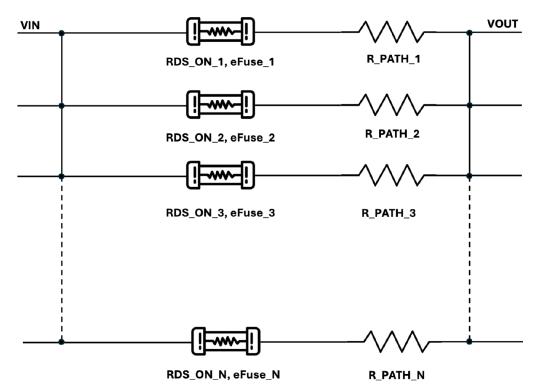

The growing power demands of Al-driven processors and servers have made efficient power distribution systems a requirement, with smart eFuses playing an important role. Traditional parallel operation of eFuses, as shown in Figure 2, presents significant challenges given mismatches in the drain-to-source on-resistance (R<sub>DS (on)</sub>), PCB trace resistances, and comparator thresholds. These mismatches result in uneven current sharing among eFuses (where some eFuses carry more current than others) and often cause premature tripping of individual eFuses, even when the overall system current is below the trip threshold. Such false tripping can lead to unnecessary system downtimes, reduced reliability, and increased operational inefficiencies.

To address these challenges, TI has introduced a total system current-limit approach in its eFuses that leverages interconnected IMON pins. This approach designates one eFuse as the primary controller to monitor the total system current. By relying on the total current rather than individual eFuse currents, the system avoids inaccuracies caused by mismatched path resistances and ensures that the system trips only when necessary, enhancing operational stability.

Figure 2. Parallel stacking of eFuses, enabling support for higher current loads

Active current-sharing technology aids in efficient power distribution by dynamically adjusting the R<sub>DS (on)</sub> of the FETs to achieve balanced current sharing among eFuses. When one eFuse carries a disproportionately higher current, increasing its R<sub>DS (on)</sub> slightly redistributes the current more evenly across all devices. This dynamic regulation minimizes thermal stress on individual eFuses, improving system reliability over extended periods.

Having active current sharing occur near the overcurrent protection threshold ensures that it only operates when necessary to avoid unnecessary power losses at lower currents. By activating active current sharing at the optimal threshold, the system achieves uniform thermal stress distribution during high-current operations, improving long-term reliability.

## Conclusion

With increased power density, a simplified design, enhanced protection and cost optimization, hot-swap eFuse devices enable more efficient and reliable power management for high-performance computing applications. The integration of features such as the blanking timer and stacking capabilities further strengthens these devices' suitability for supporting the growing power needs of modern AI data centers.

3

### Additional resources

- Download the TPS1685x 9V–80V, 3.65mΩ, 20A Stackable Integrated Hotswap (eFuse) With Accurate and Fast Current Monitor Data Sheet.

- Check out the "TPS1685 Evaluation Module for eFuse EVM User's Guide.

#### Trademarks

All trademarks are the property of their respective owners.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated