# TI-PILL TI Power Management Lab Kit LDO Experiment Book

| Name                    |

|-------------------------|

| Name                    |

|                         |

|                         |

| University/Company name |

|                         |

|                         |

| Address                 |

|                         |

|                         |

| Dhara                   |

| Phone                   |

|                         |

|                         |

| E-mail                  |

3 TI Power Management Lab Kit

Many people have collaborated with me in the realization of the TI-PMLK project, in different times, at different levels, in different ways. My sincerest thanks go to the Texas Instruments University Program Team and to the University of Salerno Power Electronics Laboratory Team.

Nicola Femia

# Preface

Felix, qui potuit rerum cognoscere causas... (Happy, he who could capture the origins of things...)

Publio Virgilio Marone, Mantova 70 B.C. – Brindisi 19 B.C.

esign is an exciting and fascinating art. Power electronics, for its interdisciplinarily nature, is a challenging field where the knowledge of *why* makes all the difference in understanding *how* to achieve design goals. The *will* of *learning* and the *means* for *learning* are the two basic ingredients needed to develop the virtuous ability to understand the reality of problems, to select the appropriate techniques and methods to solve them, to make meaningful design decisions and to intelligently evaluate the solutions.

The main purpose of the TI-PMLK collection of Experiment Books is to stimulate the spirit of investigation in students and practicing engineers who are engaged in learning and understanding the design of power supplies. The experiments cover a basic anthology of topics and issues encountered in the design of low power dc-dc non-isolated power supplies, such as power supplies topologies and characteristics, modes of operation, efficiency, control, stability, accuracy, transient response, noise, power magnetics, and more. The experiments can be performed by using the power supply boards of the TI-PMLK suite, which includes low dropout linear regulators and buck, boost and buck-boost switching regulators. The Experiment books are not intended to provide an exhaustive overview of design issues or definitive design hints: rather, it is meant to guide the reader into a multifaceted active learning experience.

All the experiments are based on a logical sequence of steps. They start with the Case Study section, which provides the description of the specific property or feature relevant to the power supply board to be used in the experiment, and illustrates the goal and the type of measurement to be done. The Theory Background section provides a short summary of concepts, models and equations, supporting the interpretation and understanding of the incoming experimental observations. The Measurement Setup section provides the instructions for connecting the instruments needed for the experiments to the board under test. Warnings are provided to prevent main mistakes. The Test section provides instructions on how to execute the measurements, and guidelines on how to analyze and understand the results of the measurements. Each test includes an Answer section, where the user is required to answer questions and to provide a discussion about the behavior of the board under test, relevant to the specific performance under investigation, based on the observation of the measurements results and on the application of concepts and properties illustrated through the various sections of the experiment. The *Discussion* section provides comments to achieve a better understanding of conceptual and practical correlations among system characteristics and operating performance. The final Experimental Plots section illustrates and discusses the results of some sample measurements.

#### Preface (cont.)

The experiments cover a variety of steady-state, transient and dynamic tests. The tests are mostly based on time domain measurements, while some tests focus on the investigation of dynamic properties that are described through frequency response functions, such as the power supply rejection ratio. This allows a user to conduct a complete experience on the characterization and understanding of power supply issues. Most of the experiments require basic laboratory equipment, including a power supply, some multi-meters, an oscilloscope and a load. Some tests require more sophisticated instrumentation, such as a dynamic source, a dynamic load, and a vector network analyzer, for best measurement.

The boards have been designed to allow the investigation of the influence of physical parameters and operating conditions of a power supply on its own performances. Various combinations of power and control components can be selected. Most of them yield operating conditions that fit good engineering standards. Other ones may lead to operating conditions typically undesired in industry applications, such as instability. Thus, the reader can achieve a sound understanding of such real phenomena.

Suggested combinations of power and control parts are provided for each experiment. The user is invited in some experiments to detect combinations that yield a certain operating condition or behavior. The user can select the setup of jumpers and connectors to generate a great variety of conditions. The book provides recommendations and warnings for safe board operation and for effective measurements. Before performing any experiment, the reader is strongly recommended to read carefully all the warnings and the introductory section of the book, where the specific description of the board is

provided and information on settings and performance are given, including forbidden combinations and special operating conditions. The reader is also strongly invited to read the manufacturers' datasheets of all the parts mounted in the boards, especially the control chips, to improve the knowledge and the understanding of each device.

A good knowledge of the power supplies implemented on the boards, supported by the heuristic observations and the models and methods discussed in the book, help the user to distinguish what can be done from what cannot be done.

The level of detail and completeness of models discussed in the *Theory Background* section vary from experiment to experiment. Sometimes the models include certain specific properties, other times they are simplified or approximated. Achieving familiarity with models is a fundamental learning step: a good power supply designer has to be able to grade the importance of modeling certain properties, at device level as well as at system level, in order to assess if they really provide meaningful and influential information to meet the application requirements. Essential formulas and expressions for the basic analysis of the phenomenon under investigation are mostly introduced without step-by-step theoretical derivations, which are beyond the objectives of the book.

The reader is encouraged to test him(her)self in filling this gap, through an in-depth study of models and methods for the analysis and design of power supplies discussed in the cited references.

#### Preface (cont.)

The parameters of semiconductor and passive power components mounted on the boards are provided in the book to allow the application of analysis formulas and design equations. All parameters of power components are affected by uncertainty, due to tolerances, ageing and influence factors like temperature, current, voltage and frequency. The values collected in the books have been extracted from the manufacturers' datasheets in certain reference conditions. The power and control components and sub-circuits of integrated circuits controlling the power supplies, which determine modes of operation and performances, are subjected to the influence of temperature, voltage, current and frequency too. As a consequence, the predictions of formulas and equations provided in the book, based on the parameters of power and control devices, can show different levels of agreement with respect to the results of experimental measurements.

The user is strongly encouraged to read the references provided in the book, to analyze the characteristics and the behavior of integrated circuits and power components of the boards, and to verify if different values of the parameters of components can be used to achieve a better compliance between the results of formulas and the results of experimental measurements. The investigation of real device characteristics and of their influence on overall performance of a power supply is a fundamental component of designers' work.

The ultimate intention of this book is to accompany the reader through an active experience, made of observations, application of physics and mathematics, reality investigation and system level reasoning. That is engineering insight. The Author hopes the reader may fully enjoy this book and the pleasure of being a design engineer, a creative and autonomous thinker, able to acquire and re-elaborate the knowledge to win ever new design challenges.

Know why, know how!

Nicola Femia

Nicola Femia is Professor at the University of Salerno, Italy, where he teaches Power Electronics and Energetic Intelligence, in the Electronic Engineering and Computer Engineering Master Degree Programs. He leads the Power Electronics and Renewable Sources Laboratory. Over the past 25 years, he has promoted and directed worldwide university and industry research activities and education programs on power electronics, photovoltaic systems, and power design. He has been Visiting Professor at the Electrical Engineering Department of the Stanford University, Stanford, CA, where he taught Power Electronics Control and Energy Aware Design.

e-mail: femia@unisa.it;

web: www.unisa.it/docenti/nicolafemia/index

## **Table of Contents**

| Preface                                               | Experiment 3                                                                                |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Instrumentation needed for Experiments                | Impact of line and load conditions and output capacitor on stability and transient response |

| TI-PMLK LDO TPS7A4901 description                     |                                                                                             |

| • Schematic                                           | Experiment 4                                                                                |

| • Bill of Materials                                   | Impact of capacitors on Power Supply Rejection Ratio                                        |

| • Board                                               | riejection riatio                                                                           |

| Connectors, Jumpers and Test Pins                     | Experiment 5                                                                                |

| TI-PMLK LDO TPS7A8300 description                     | Impact of line and load conditions on dropout voltage                                       |

| • Schematic                                           | Experiment 6                                                                                |

| • Bill of Materials                                   | Impact of output capacitor                                                                  |

| • Board                                               | on load-transient response                                                                  |

| • Connectors, Jumpers and Test Pins                   | Appendix A                                                                                  |

| Notes, Warnings and Recommendations                   | References                                                                                  |

| Experiment 1                                          | Appendix B                                                                                  |

| Impact of line and load conditions on drouput voltage | Manufacturers websites                                                                      |

| Experiment 2                                          |                                                                                             |

| Impact of line and load conditions on efficiency37    |                                                                                             |

|                                                       |                                                                                             |

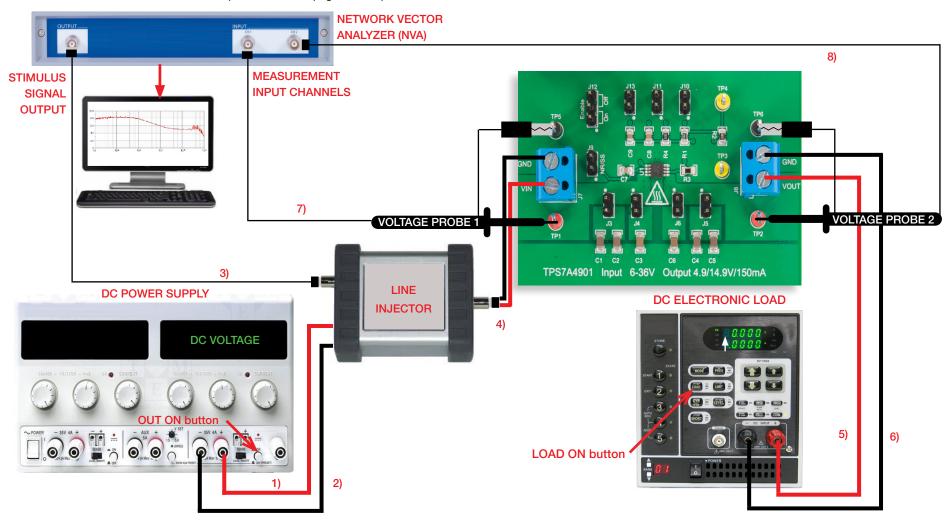

### Instrumentation needed for experiments

The instrumentation recommended for the execution of the Experiments of this Book is comprised of:

- DC power supply 0-50V/4A with dynamic voltage mode capability

- DC electronic load 20V/10A with dynamic current mode capability

- 4 digital multimeters with 41/2 digit resolution

- 250MHz 4-channels Digital Oscilloscope + 2 current probes 20A/50MHz

- 10Hz-10MHz Network Vector Analyzer with line injector

- 10MHz Waveform Generator

The instrumentation used in the lab tests corresponding to the Experimental Plot samples shown in the book is comprised of:

- TTi EX354RT Power Supply 0-70V/4A (used in the experiments where the board under test had to be fed by a constant DC voltage source)

- Keithley 2420 SourceMeter, 63V, 3.15A (used in the experiments where the board under test had to be fed by a dynamic DC voltage source)

- Sorensen Electronic Load SLM-4 mainframe + SLM series electronic load modules 60V/60A

- LeCroy WaveRunner 44Xi 400MHz 4-channels Digital Oscilloscope, with 2 Tektronix TCP 305 50A current probe + Tektronix TCP A300 amplifier

- Omicron Bode 100 1Hz-40MHz Network Vector Analyzer with Picotest J2120A line injector (used in the experiment where the board under test had to be fed by a static DC voltage source with an AC noise injected)

- Agilent 33500b 30MHz Waveform Generator

# **TI-PMLK-LDO**

The TI-PMLK-LDO is an experimental power supply board based on two integrated linear voltage regulators, the ultra-low dropout TPS7A8300 and the ultra-low noise TPS7A4901

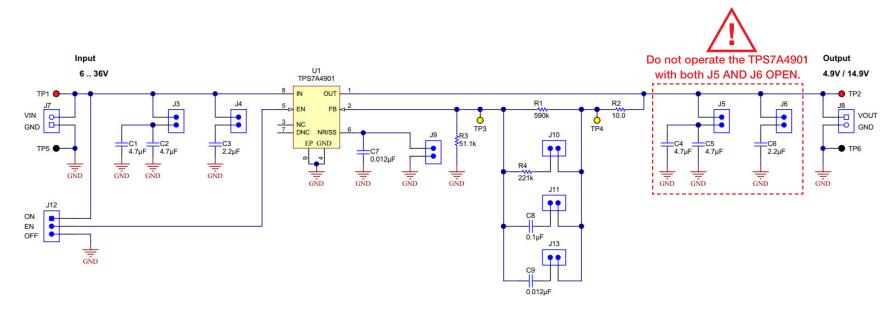

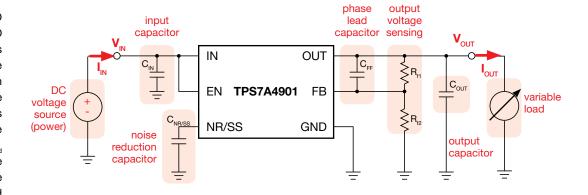

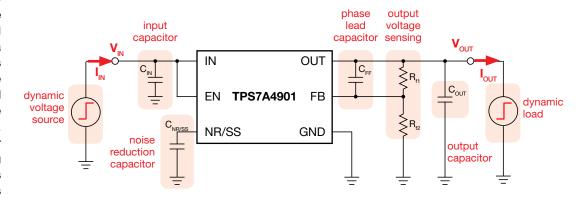

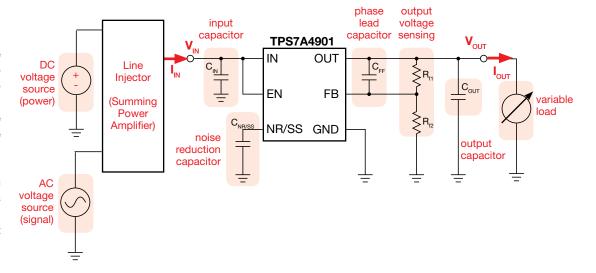

The TI-PMLK TPS7A4901 section of the board accepts input voltages in between 6V and 36V, while regulating output voltage at 5V or 15V with a maximum load current 150mA.

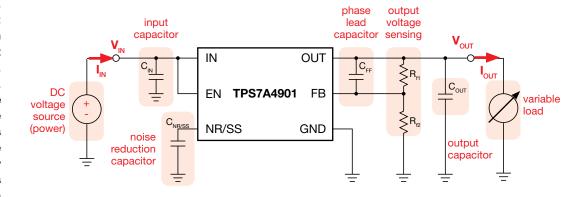

Figure 1. Circuit schematic of TI-PMLK TPS7A4901 LDO regulator

# TI-PMLK TPS7A4901 Bill of Materials

| Designator     | Description                                                                                                                    | Manufacturer      | Part Number        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|

| C1, C2, C4, C5 | ceramic capacitor, 4.7µF, 50V, +/-10%, X7R, 1206                                                                               | Taiyo Yuden       | UMK316AB7475KL-T   |

| C3, C6         | ceramic capacitor, 2.2µF, 50V, +/-10%, X7R, 1206                                                                               | MuRata            | GRM31CR71H225KA88L |

| C7, C9         | ceramic capacitor, 0.012µF, 50V, +/- 10%, X7R, 0805                                                                            | AVX               | 08055C123KAT2A     |

| C8             | ceramic capacitor, 0.1µF, 50V, +/- 10%, X7R, 0805                                                                              | Kemet             | C0805C104K5RACTU   |

| R1             | resistor, 590k $\Omega$ , 1%, 0.125W, 0805                                                                                     | Panasonic         | ERJ-6ENF5903V      |

| R2             | resistor, $10.0\Omega$ , $0.1\%$ , $0.125W$ , $0805$                                                                           | Yageo America     | RT0805BRD0710RL    |

| R3             | resistor, 51.1kΩ, 0.1%, 0.125W, 0805                                                                                           | Susumu Co Ltd     | RG2012P-5112-B-T5  |

| R4             | resistor, 221k $\Omega$ , 1%, 0.125W, 0805                                                                                     | Vishay-Dale       | CRCW0805221KFKEA   |

| U1             | Single Output High PSRR LDO, 150mA,<br>Adjustable 1.2 to 33V Output, 3 to 36V Input,<br>with Ultra-Low Noise, 8-pin MSOP (DGN) | Texas Instruments | TPS7A4901DGNR      |

(use the part numbers of components to retrieve, through the manufacturers websites listed in the references, details about parameters and data that are used in the formulae provided for calculations in each experiment)

# TI-PMLK TPS7A4901 Board

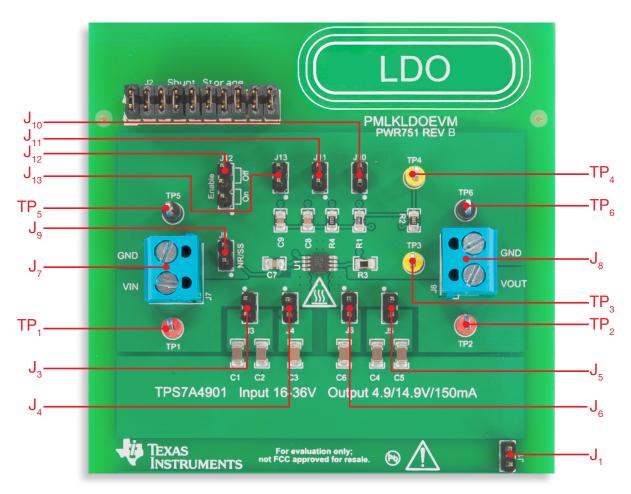

Figure 2. Plain view of TI-PMLK TPS7A4901 LDO regulator board

# TI-PMLK TPS7A4901 Connectors, Jumpers and Test Pins

#### Descriptors and functions for Connectors, Jumpers and Test Pins

#### Connectors

- J, input voltage screw drive connector

- J. output voltage screw drive connector

#### **Jumpers**

- J<sub>1</sub> connects grounds of TPS7A4901 and TPS7A8300 board sections

- J<sub>2</sub> connects C<sub>1</sub> (4.7μF) and C<sub>2</sub> (4.7μF) input capacitors

- J connects C<sub>2</sub> (2.2µF) input capacitor

- $J_{5}$  connects  $C_{4}$  (4.7 $\mu$ F) and  $C_{5}$  (4.7 $\mu$ F) output capacitors

- J<sub>e</sub> connects C<sub>e</sub> (2.2μF) output capacitor

- J<sub>9</sub> connects Noise Reduction/Soft Start pin directly to ground and shorts across C<sub>7</sub> (12nF) noise reduction capacitor

- $J_{10}$  connects R<sub>4</sub> (221k $\Omega$ ) resistor for 5V output voltage operation

- J<sub>11</sub> connects C<sub>s</sub> (100nF) phase lead capacitor

- J<sub>12</sub> enables LDO operation when top pin and center pin are shorted (ON), while it disables the LDO operation when center pin and bottom pin are shorted (OFF)

- J<sub>13</sub> connects C<sub>o</sub> (12nF) phase lead capacitor

#### Test pins

- TP, positive pole of input voltage

- TP<sub>e</sub> ground pole of input voltage

- TP<sub>2</sub> positive pole of output voltage

- TP<sub>a</sub> ground pole of output voltage

- TP<sub>a</sub> feedback voltage

- ${

m TP_4}$  pin for loop gain measurements, can be used together with  ${

m TP_3}$  to inject the ac stimulus into the  $10\Omega$  resistor  ${

m R_2}$

#### **Voltage and Current Measurements**

- use TP, and TP, to measure the input voltage

- use TP, and TP, to measure the output voltage

- use TP<sub>3</sub> and TP<sub>6</sub> to measure the feedback voltage

- hang a current probe to one of the external power wires connected to J<sub>7</sub>

to measure the input current

- hang a current probe to one of the external power wires connected to J<sub>8</sub>

to measure the load current

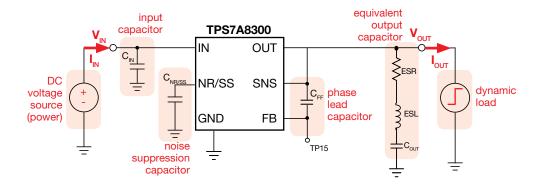

# TI-PMLK TPS7A8300 Schematic

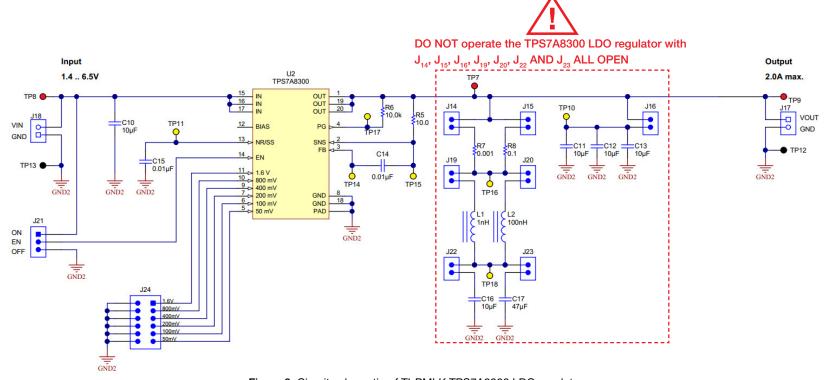

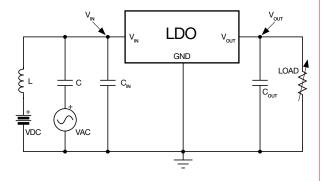

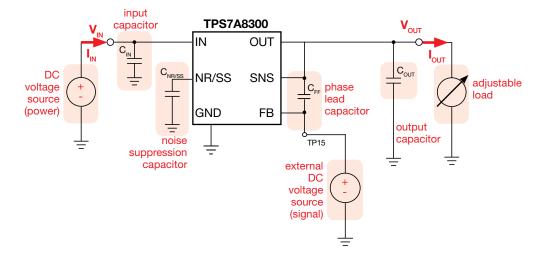

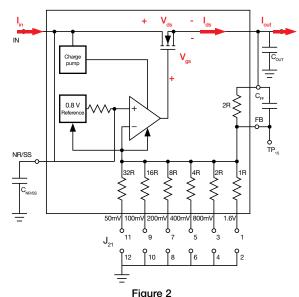

The TI-PMLK TPS7A8300 section of the board accepts input voltages in between 1.4V and 6.5V. The output voltage can be set between 0.8V and 3.95V with onboard jumpers on  $J_{24}$ , with a maximum load current of 2A.

Figure 3. Circuit schematic of TI-PMLK TPS7A8300 LDO regulator

# TI-PMLK TPS7A8300 Bill of Materials

| Designator              | Description                                                                | Manufacturer      | Part Number        |

|-------------------------|----------------------------------------------------------------------------|-------------------|--------------------|

|                         |                                                                            |                   |                    |

| C10, C11, C12, C13, C16 | ceramic capacitor, 10µF, 16V, +/-10%, X5R, 0805                            | MuRata            | GRM21BR61C106KE15L |

| C14, C15                | ceramic capacitor, 0.01µF, 50V, +/-10%, X7R, 0805                          | MuRata            | GRM216R71H103KA01D |

| C17                     | ceramic capacitor, 47µF, 16 V, +/- 20%, X5R, 1210                          | MuRata            | GRM32ER61C476ME15L |

| L1                      | Inductor, Multilayer, Ceramic, 1nH, 0.3A, 0.015 $\Omega$ , SMD             | Taiyo Yuden       | HK16081N0S-T       |

| L2                      | Inductor, Wirewound, Ferrite, 100nH, 2.85A, 0.02 $\Omega$ , SMD            | TDK               | NLCV32T-R10M-PFR   |

| R5                      | resistor, $10.0\Omega$ , 1%, $0.125W$ , $0805$                             | Yageo America     | RC0805FR-0710RL    |

| R6                      | resistor, $10.0 k\Omega$ , $0.1\%$ , $0.125W$ , $0805$                     | Yageo America     | RT0805BRD0710KL    |

| R7                      | resistor, $0.001\Omega$ , 1%, 1W, 1210                                     | Rohm              | PMR25HZPFV1L00     |

| R8                      | resistor, 0.1Ω, 1%, 0.5W, 1210                                             | Rohm              | MCR25JZHFLR100     |

| U2                      | 2-A, Low Noise, RF, LDO Voltage Regulator,<br>20-pin Plastic Quad Flatpack | Texas Instruments | TPS7A8300RGR       |

(use the part numbers of components to retrieve, through the manufacturers websites listed in the references, details about parameters and data that are used in the formulae provided for calculations in each experiment)

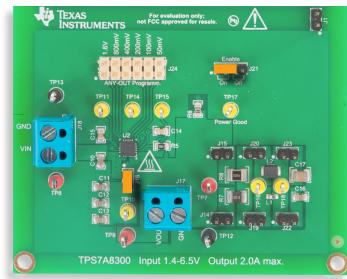

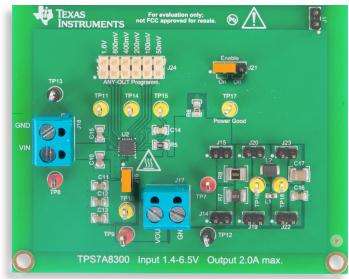

# TI-PMLK TPS7A8300 Board

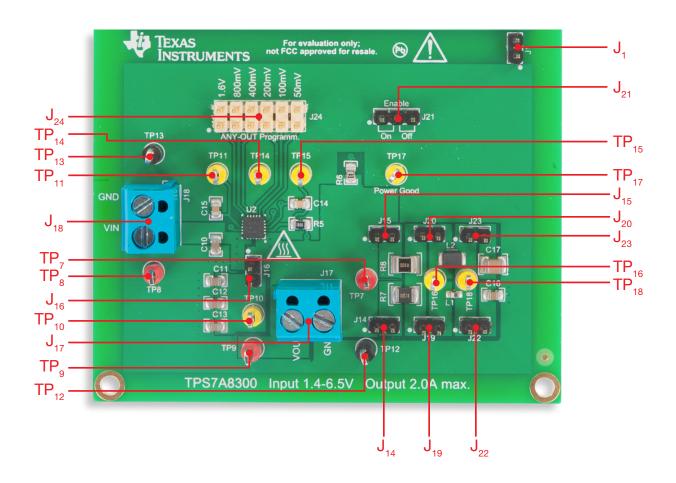

Figure 4. Plain view of TI-PMLK TPS7A8300 LDO regulator board

### TI-PMLK TPS7A8300 Connectors, Jumpers and Test Pins

#### Descriptors and functions for Connectors, Jumpers and Test Pins

#### Connectors

J<sub>18</sub> - input voltage screwdrive connector

J<sub>17</sub> - output voltage screwdrive connector

#### **Jumpers**

$J_{14}$  - connects the resistor  $R_7$  (1m $\Omega$ ) [emulated ESR]

$J_{15}$  - connects the resistor R<sub>o</sub> (100m $\Omega$ ) [emulated ESR]

$J_{16}$  - connects the  $C_{11}$ -  $C_{13}$  (3x10 $\mu$ F) output capacitors

$J_{10}$  - connects the inductor L<sub>1</sub> (1nH,15m $\Omega$ ) [emulated ESL]

$J_{20}$  - connects the inductor L<sub>2</sub> (100nH,20m $\Omega$ ) [emulated ESL]

J<sub>21</sub> - enables LDO operation when ON pin and EN pin are shorted, while it disables the LDO operation when EN pin and OFF pin are shorted

$J_{22}$  - connects the output capacitor  $C_{16}$  (10µF)

$J_{23}$  - connects the output capacitor  $C_{17}$  (47 $\mu$ F)

${\sf J}_{\sf 24}$  - connects the internal resistors of TPS7A8300 to adjust the output voltage

J<sub>1</sub> - connects grounds of the TPS7A4901 and the TPS7A8300 board sections

#### Test pins

TP<sub>8</sub> - positive pole of input voltage

TP<sub>a</sub> - positive pole of output voltage

$TP_{10}$  - voltage on  $C_{11}$ -  $C_{13}$  (3x10µF) output capacitors

TP<sub>11</sub> - noise rejection capacitor voltage

TP<sub>12</sub> - ground pole of output voltage

TP<sub>13</sub> - ground pole of input voltage

TP<sub>14</sub> - feedback voltage

$^{\rm TP}_{\rm 15}$  - connection pin for loop gain measurements, can be used together with  $^{\rm TP}_{\rm 7}$  to inject the AC stimulus into the 10Ω resistor R<sub>5</sub>

$TP_{16}$  - can be used together with  $TP_7$  to sense the voltage across the resistors  $R_7$  (1mΩ) and  $R_8$  (100mΩ) [emulated ESR]

TP<sub>17</sub> - Power Good pin voltage

TP<sub>18</sub> - can be used together with TP<sub>18</sub> to sense the voltage across inductors L<sub>1</sub> (1nH,15mΩ) and L<sub>2</sub> (100nH,20mΩ) [emulated ESL], or to sense the voltage across capacitors C<sub>16</sub> (10μF) and C<sub>17</sub> (47μF)

#### Voltage and Current Measurements

- use TP<sub>8</sub> and TP<sub>13</sub> to measure the input voltage

- use TP<sub>a</sub> and TP<sub>12</sub> to measure the output voltage

- use TP<sub>14</sub> to measure the feedback voltage

- hang a current probe to one of the external power wires connected to J<sub>10</sub> to measure the input current

- hang a current probe to one of the external power wires connected to J<sub>1</sub>, to measure the load current

### Notes, Warnings and Recommendations

#### **NOTES**

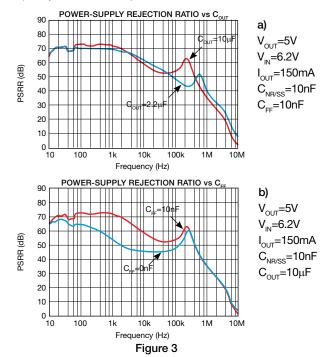

- The jumper J<sub>g</sub> of the TPS7A4901 LDO regulator can be used to connect an external capacitor in parallel to the C<sub>7</sub> (12nF) NR/SS capacitor. Increasing the NR/SS capacitance determines a longer Soft Start time at the start-up, modifies the Power Supply Rejection Ratio (PSRR) and reduces the output voltage noise.

- The jumper J<sub>10</sub> of the TPS7A4901 LDO regulator can be used to connect an external resistor in series to the R<sub>4</sub> (221kΩ) voltage divider resistor. Increasing the resistance in series to R<sub>4</sub> allows to increase the output voltage. The value of the resistance R<sub>x</sub> to put in series to R<sub>4</sub> to get a value V<sub>x</sub> of the output voltage V<sub>out</sub> is given by the following formula:

$$R_{x} = \frac{R_{1}R_{3}(V_{x}-V_{ref})}{(R_{1}+R_{3})V_{ref}-R_{3}V_{x}} - R_{4}$$

- The capacitor  $C_{16}$  (10 $\mu$ F) mounted in the TPS7A8300 board can be connected directly to the output of the TPS7A8300 LDO regulator by shorting the upside pin of the jumper  $J_{14}$  with the downside pin of the jumper  $J_{22}$ .

- The capacitor C<sub>17</sub> (47μF) mounted in the TPS7A8300 board can be connected directly to the output of the TPS7A8300 LDO regulator by shorting the upside pin of the jumper J<sub>15</sub> with the downside pin of the jumper J<sub>12</sub>.

#### WARNINGS AND RECOMMENDATIONS

#### **GENERAL**

- 1) DO NOT exceed input and output voltage and current ratings

- 2) If the board is terminated at the output into an electronic load in constant current mode, the sequence to follow is:

- a) at the turn on: turn on the power supply, then turn on the electronic load b) at the turn off: turn off the electronic load, then turn off the power supply

- 3) Whatever change in the setup of jumpers has to be done, the board has to be shut down first, according to the recommendations given at point 2)

- 4) The board has to be operated at ambient temperature 25°C (maximum 27.5°C)

#### TPS7A4901 LDO REGULATOR

- 1) DO NOT operate the regulator with both J<sub>c</sub> AND J<sub>c</sub> OPEN

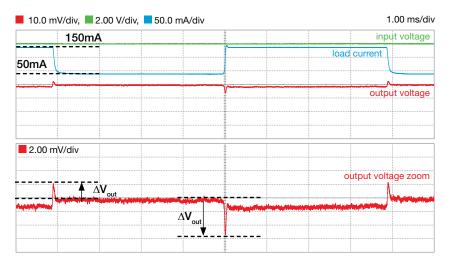

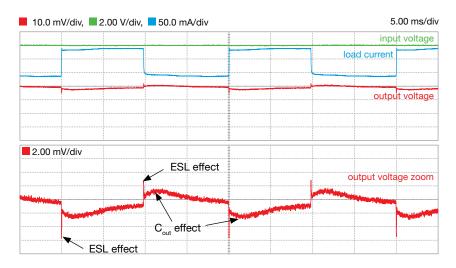

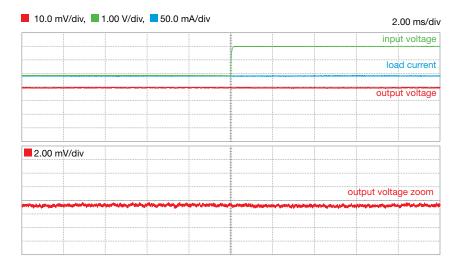

- 2) For an effective load transient response measurement, the use of an electronic load with high slew-rate (>1A/µs) dynamic current sink mode operation is recommended

- 3) For an effective line transient response measurement, a power supply with high slewrate (>1V/µs) dynamic voltage mode operation is suggested

- 4) In the test of PSRR, if a power summing amplifier is used to inject into the input the ac stimulus, be sure that the total dc+ac input voltage never exceeds the maximum voltage rating of the board and that it does not become negative

#### **TPS7A8300 LDO REGULATOR**

- 1) If  $J_{16}$  is OPEN, one of the two capacitors  $C_{16}$  or  $C_{17}$  has to be connected to the output, through  $J_{22}$  or  $J_{23}$ , to one of the two resistors  $R_7$  and  $R_8$ , through  $J_{14}$  and  $J_{15}$ , and to one of the inductors  $L_1$  and  $L_2$ , through  $J_{19}$  and  $J_{20}$

- 2) For an effective load transient response measurement, the use of an electronic load with high slew-rate (>1A/µs) dynamic current sink mode operation is recommended

# Experiment 1

The goal of this experiment is to analyze how the output voltage regulation capabilities of an LDO regulator depend on the line and load conditions. The TPS7A4901 LDO regulator is used for this experiment.

The goal of this experiment is to analyze how the dropout voltage and the output voltage accuracy of an LDO regulator depend on the line and load conditions.

Figure 1 shows the simplified schematic of the TPS7A4901 LDO regulator. Two elements characterize the **regulation capability** of the LDO regulator: the regulation region and the regulation accuracy. The regulation region is identified by the input voltage range  $[V_{\rm INmin}, V_{\rm INmax}]$  and the output current range [I<sub>OLITmin</sub>, I<sub>OLITmax</sub>] wherein the LDO is able to regulate the output voltage. The output current range spans from ~0A to a maximum current I<sub>OUTmax</sub>, which is determined by the maximum temperature rating of the LDO, the power dissipation capabilities of its package and the maximum input voltage of the LDO (I<sub>OUTmax</sub>=150mA for TPS7A4901). The output voltage range spans from the dropout voltage  $V_{DO} = V_{INmin}$ , that depends on the pass device characteristics, to a maximum  $V_{\text{INmax}}$ , that depends on chip technology (V<sub>INmax</sub>=36V for TPS7A4901). The regulation accuracy of the LDO regulator is the percent tolerance  $(V_{out}-V_{outnom})/V_{outnom}x100$  of the output voltage  $V_{out}$  with respect to the nominal value Voutnom. The regulation accuracy depends on the load regulation and line regulation, which is expressed as the output voltage tolerance versus the load current I and versus the input voltage  $V_{IN}$ , over the relevant regulation ranges  $[I_{OLITmin},I_{OLITmax}]$  and  $[V_{INmin},V_{INmax}]$ .

Figure 1. Simplified schematic of the TPS7A4901 LDO regulator

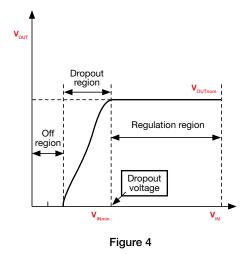

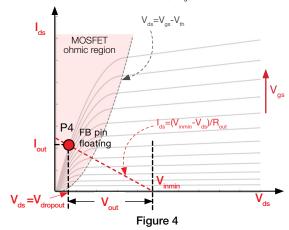

Test#1. We measure the input voltage and the output voltage of the TPS7A4901 LDO regulator while varying the load current. The goal is to determine the dropout voltage of the LDO regulator. To detect the value of the dropout voltage we decrease the input voltage, starting from a value that is sufficiently bigger than the output voltage, and observe the output voltage to see when it begins decreasing with respect to its nominal value. While the input voltage decreases, the operating point of the LDO regulator moves along the curve of Fig.4, sliding from the regulation region to the dropout region.

Test#2. We measure the output voltage of the TPS7A4901 LDO regulator while varying the load current and the line voltage. The goal is to verify the regulation capabilities of the LDO regulator when it is in the regulation region, and to observe if and how the output voltage depends on the load current and line voltage. To verify the regulation capabilities we make two type of measurements. First, we set the input voltage of the LDO regulator at a value higher than the dropout voltage investigated in the previous test, we observe the output voltage while varying the load current, and determine the *load regulation*. Then, we set the load current at a given value and observe the output voltage while varying the input voltage, and determine the *line regulation*.

### Theory Background

The fundamentals of LDO regulators are provided in this section (see [1][4][11][12] for a general discussion of LDO regulators operation and characteristics, and [2] for more details on TPS7A4901 operation and features).

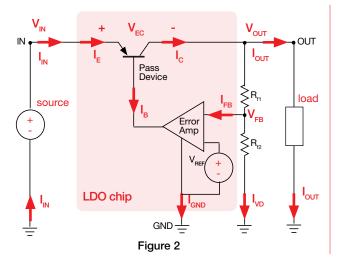

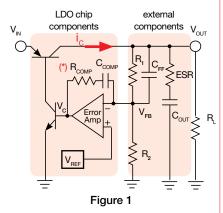

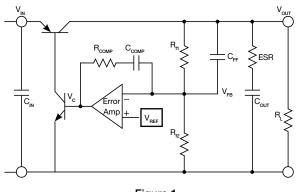

Figure 2 shows the architecture of a low-dropout (LDO) regulator using a PNP bipolar transistor as pass device connected between the input and the output. The output voltage is sensed through the voltage divider  $R_{\rm rl}$ - $R_{\rm r2}$ , that generates the feedback voltage  $V_{\rm FB}$ . The Error Amplifier adjusts the pass device base current until the emitter-collector voltage  $V_{\rm EC}$  equals the difference between the input voltage  $V_{\rm in}$  and the desired regulated output voltage given by the formula (1):

(1)

$$V_{OUT} = V_{ref} (1 + R_{f1} / R_{f2})$$

where  $V_{ref}$  is the internal reference voltage. The base current  $I_B$  is injected into ground, and depends on the line and load conditions. The PNP transistor must work in the active region in order to achieve the output voltage  $V_{\text{OUT}}$  given by (1).

Pass Device

Pass Device

R<sub>11</sub>

R<sub>12</sub>

LDO chip

Figure 2

Figure 3 shows the output characteristic of a PNP bipolar transistor. The PNP transistor works in the active region, thus ensuring a regulated output voltage, provided that the input voltage  $V_{IN}$  is greater than  $V_{INmin} = V_{OUT} + V_{EC,sat}(I_{OUT})$ , where  $V_{EC,sat}(I_{OUT})$  is the saturation emitter-collector voltage at the current  $I_{OUT}$  required by the load. The voltage  $V_{INmin}$  is called **dropout voltage**.

Figure 4 shows the effect of output voltage de-rating caused by the decrease of input voltage below  $V_{\text{INmin}}$ . When  $V_{\text{IN}}$  is lower than the **dropout voltage**  $V_{\text{INmin}}$ , the PNP transistor works in the saturation region of Figure 3, and is not able to deliver the current  $I_{\text{OUT}}$  required by the load. Therefore, the output voltage  $V_{\text{OUT}}$  is derated with respect to the desired nominal value  $V_{\text{OUTnom}}$ . This corresponds to the **dropout region** in Figure 4.

# Good to Know

- In theory, it is possible to find a ratio of resistances  $R_{rf}/R_{r2} = V_{OUTnom}/V_{ref}-1$ , that corresponds to the desired value of the nominal output voltage  $V_{OUTnom}$ . In practice, the values of commercial resistances are standardized, so that in most cases the nominal ratio  $R_{rf}/R_{r2}$  cannot be exactly achieved with the two resistors voltage divider made of  $R_{rf}$  and  $R_{rp}$ , so that the regulated  $V_{OUT}$  does not equal  $V_{OUTnom}$ .

- 2 Commercial resistors are available with different tolerances. Resistors with 0.1% tolerance ensure higher regulation accuracy, but they are more expensive than 1% tolerance resistors, which cause instead a degradation of the accuracy.

- The reference voltage  $V_{ref}$  of the LDO is set inside the IC and can have a tolerance of 1% to 2%, which influences the value of the regulated output voltage  $V_{out}$ .

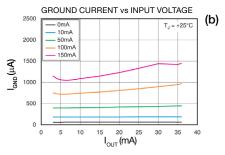

# Experiment set-up: configuration

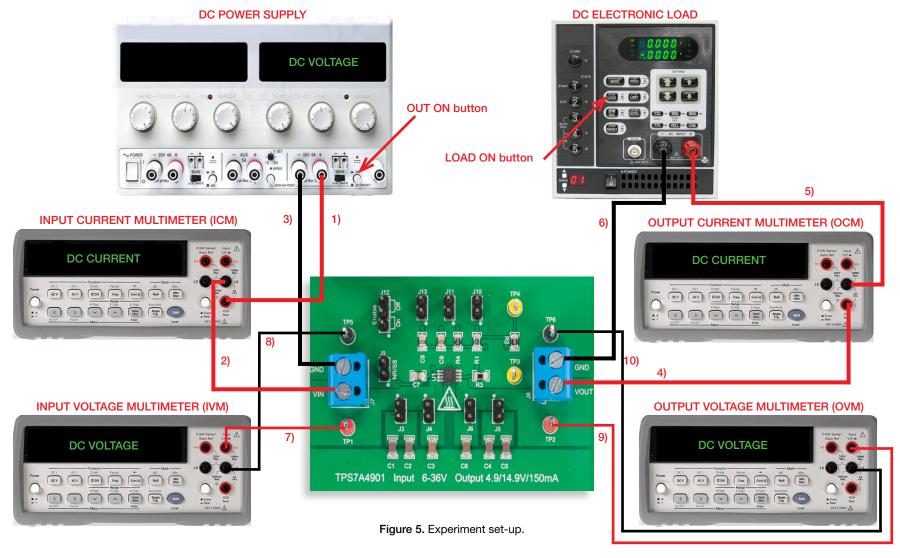

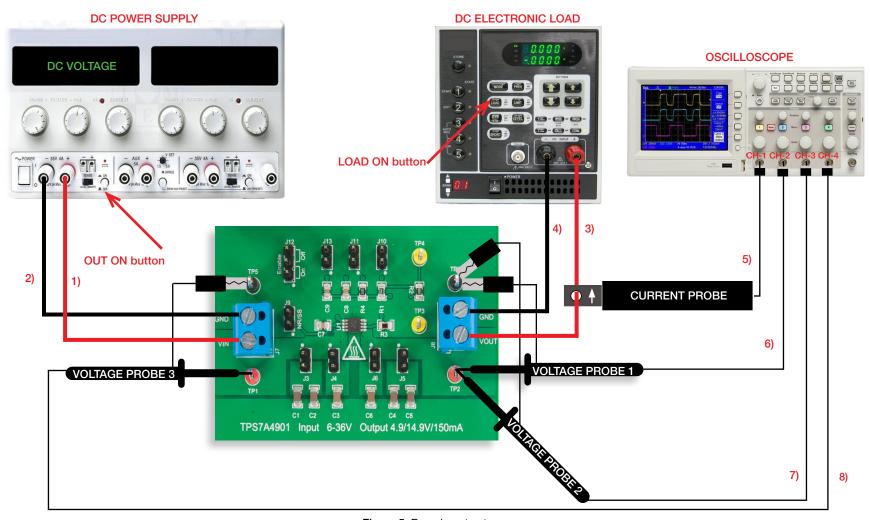

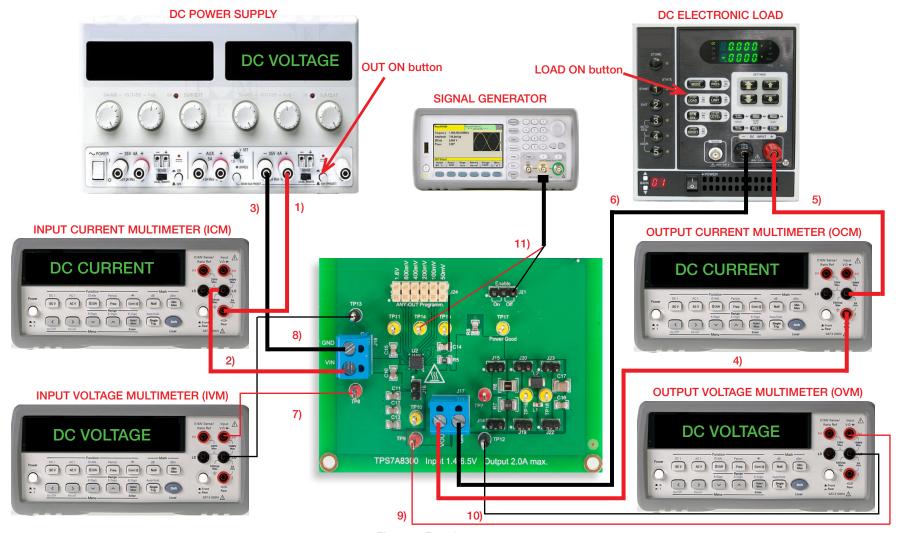

The instruments needed for this experiment are: a DC POWER SUPPLY, four MULTIMETERS and a DC ELECTRONIC LOAD. Figure 5 shows the instruments connections. Follow the instructions provided in next page to set-up the connections.

# Experiment set-up: instructions

With all the instruments turned off, make the following connections:

- 1) connect the POSITIVE (RED) OUTPUT of the DC POWER SUPPLY to the POSITIVE (RED) CURRENT INPUT of the INPUT CURRENT MULTIMETER (ICM)

[WARNING: the positive current input of the multimeter is distinguished from the positive voltage input]

- 2) connect the NEGATIVE (BLACK) CURRENT INPUT of the INPUT CURRENT MULTIMETER (ICM) to the INPUT (VIN) of the J<sub>7</sub> screw terminal of the TPS7A4901 LDO regulator

- 3) connect the NEGATIVE (BLACK) OUTPUT of the DC POWER SUPPLY to the GROUND (GND) of the J, screw terminal of the TPS7A4901 LDO regulator

- 4) connect the OUTPUT (VOUT) of the J<sub>8</sub> screw terminal of the TPS7A4901 LDO regulator to the POSITIVE (RED) CURRENT INPUT of the OUTPUT CURRENT MULTIMETER (OCM) [WARNING: the positive current input of the multimeter is distinguished from the positive voltage input]

- 5) connect the NEGATIVE (BLACK) CURRENT INPUT of the OUTPUT CURRENT MULTIMETER (OCM) to the POSITIVE (RED) INPUT of the ELECTRONIC LOAD

- 6) connect the NEGATIVE (BLACK) INPUT of the ELECTRONIC LOAD to the GROUND (GND) of the J<sub>o</sub> screw terminal of the TPS7A4901 LDO regulator

- 7) connect the POSITIVE (RED) VOLTAGE INPUT of the INPUT VOLTAGE MULTIMETER (IVM) to the TEST PIN TP, which is the VIN of the TPS7A4901 LDO regulator

- 8) connect the NEGATIVE (BLACK) VOLTAGE INPUT of the INPUT VOLTAGE MULTIMETER (IVM) to the TEST PIN TP, which is GND of the TPS7A4901 LDO regulator

- 9) connect the POSITIVE (RED) VOLTAGE INPUT of the OUPUT VOLTAGE MULTIMETER (OVM) to the TEST PIN TP, which is VOUT of the TPS7A4901 LDO regulator

- 10) connect the NEGATIVE (BLACK) VOLTAGE INPUT of the OUTPUT VOLTAGE MULTIMETER (OVM) to the TEST PIN TP which is the GND of the TPS7A4901 LDO regulator

# Test#1: preparation and procedure

Figure 6. TPS7A4901 LDO board: jumpers set-up for Test#1

#### Jumpers set-up (see Figure 6):

- J<sub>10</sub> shorted in ON position → LDO operation enabled

- J<sub>10</sub> shorted → nominal output voltage V<sub>out</sub> = 5V

- J<sub>12</sub> shorted → C<sub>2</sub> (12nF) phase lead capacitor connected

- $J_5$  shorted  $\rightarrow C_4$  (4.7 $\mu$ F) and  $C_5$  (4.7 $\mu$ F) output capacitors connected

- J<sub>a</sub> shorted → C<sub>4</sub> (4.7μF) and C<sub>2</sub> (4.7μF) input capacitors connected

- J<sub>a</sub> open → C<sub>a</sub> (2.2μF) input capacitor disconnected

- $J_{\epsilon}$  open  $\rightarrow C_{\epsilon}$  (2.2 $\mu$ F) output capacitor disconnected

- J<sub>1</sub> open → C<sub>o</sub> (100nF) phase lead capacitor disconnected

- J<sub>o</sub> open → C<sub>7</sub> (12nF) noise reduction capacitor disconnected

#### **Test Procedure:**

- 1) turn on the MULTIMETERS

- 2) set the ICM in DC CURRENT MODE, with range ≤ 1A

- 3) set the OCM in DC CURRENT MODE, with range ≤ 1A

- 4) set the IVM in DC VOLTAGE MODE, with range ≥ 5V

- 5) set the OVM in DC VOLTAGE MODE, with range ≥ 5V

- 6) turn on the POWER SUPPLY (ensure that the "OUT ON" button is OFF)

- 7) set the VOLTAGE of the POWER SUPPLY at 6V

- 8) set the POWER SUPPLY CURRENT LIMIT at 200mA

- 9) turn on the ELECTRONIC LOAD (ensure that the "LOAD ON" button is OFF)

- 10) set the ELECTRONIC LOAD in CONSTANT CURRENT MODE and the DC current at 25mA

- 11) turn ON the POWER SUPPLY "OUT ON" button

- 12) in these conditions you should read about 6V in the IVM display, about 5V in the OVM display, about 0A in the OCM display and 0A in the ICM display (if you don't read these values, turn OFF the "OUT ON" button of the DC POWER SUPPLY and verify the previous steps)

- 13) turn ON the ELECTRONIC LOAD "LOAD ON" button

- 14) in these conditions you should read about 6V in the IVM display, about 5V in the OVM display, 25mA in the OCM display and slightly more than 25mA in the ICM display (if you read values much different than the one listed above, turn OFF the "LOAD ON" button of the ELECTRONIC LOAD and the "OUT ON" button of the DC POWER SUPPLY and verify the previous steps)

- 15) reduce slowly the DC POWER SUPPLY voltage by means of the "fine adjust" knob, watch the output voltage of the TPS7A4901 LDO regulator on the OVM display, stop when you see the voltage to decrease by more than 0.1%, and record the input voltage and the output voltage values in Table 1

- 16) reset the DC POWER SUPPLY voltage at 6V and repeat step 15) for the values of the load current listed in Table 1

- 17) turn OFF the ELECTRONIC LOAD "LOAD ON" button, turn OFF the DC POWER SUPPLY "OUT ON" button

- 18) open jumper  $J_{10}$  to set 15V nominal output voltage  $V_{out}$ , repeat the steps 10) to 16) by setting the initial value of VOLTAGE of the POWER SUPPLY at 16V (the values 6V and 5V now are 16V and 15V), and fill Table 1

- 19) at the end of the measurements, turn OFF the "LOAD ON" button of the ELECTRONIC LOAD and the "OUT ON" button of the DC POWER SUPPLY, then switch off all the instruments

### Test#1: measure and calculate

For each position of jumper  $J_{10}$  (open/shorted), execute the following steps.

- 1) Calculate the nominal output voltage (a) V<sub>outnom</sub> based on the formula (1) provided in the *Theory Background* section, using the R<sub>f1</sub> and R<sub>f2</sub> values provided in the parameters box below, and report the value in Table 1 [NOTE: neglect the tolerances of the sensing resistors].

- 2) For the value of the load current of 25mA, measure the output voltage (b)  $V_{out,1V}$  at  $V_{IN} = V_{outnom} + 1V$ , and report the value in Table 1.

- 3) For each value of the load current of Table 1, measure the value of the input voltage (1)  $V_{inmin}$  at which you observe an output voltage value (2)  $V_{out,0.1\%}$  deviating of more than 0.1% from the value measured at  $V_{IN} = V_{outnom} + 1V$  [e.g. 5mV at 5V], calculate the drop voltage (3)  $V_{drop} = V_{inmin} V_{out,0.1\%}$ , and report the values  $V_{inmin}$ ,  $V_{out,0.1\%}$  and  $V_{drop}$  in Table 1.

- 4) Answer the questions and try to motivate the results of your observation based on the information provided in the *Theory Background* section and in [1][2][4].

Table 1. Dropout voltage of TI-PMLK TPS7A4901 LDO regulator vs load corrent at  $V_{\text{OUT}} = 5V$  and  $V_{\text{OUT}} = 15V$

|                                                                                                         | I <sub>OUT</sub> [mA]                                   | 25  | 50  | 75  | 100 | 125 | 150 |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|-----|-----|-----|-----|-----|

| J <sub>10</sub> shorted (V <sub>outnom</sub> ≈ 5V)                                                      | (1) V <sub>INmin</sub> [V]                              | (1) | (1) | (1) | (1) | (1) | (1) |

| <sup>(a)</sup> $V_{\text{outnom}} = V_{\text{ref}} (1 + R_{\text{f1@J10sh}} / R_{\text{f2}}) = \dots V$ | $V_{OUT,0.1\%}$ [mV]                                    | (2) | (2) | (2) | (2) | (2) | (2) |

| $^{\text{(b)}}V_{\text{out,1V}}@\{V_{\text{IN}}=V_{\text{outnom}}+1V,\ I_{\text{OUT}}=25\text{mA}\}=V$  | (3) $V_{drop} = V_{INmin} - {}^{(2)}V_{OUT,0.1\%}$ [mV] | (3) | (3) | (3) | (3) | (3) | (3) |

| J <sub>10</sub> open (V <sub>outnom</sub> ≈ 15V)                                                        | (1) V <sub>INmin</sub> [V]                              | (1) | (1) | (1) | (1) | (1) | (1) |

| (a) $V_{\text{outnom}} = V_{\text{ref}} (1 + R_{\text{f1@J10op}} / R_{\text{f2}}) = \dots V$            | (2) V <sub>OUT,0.1%</sub> [mV]                          | (2) | (2) | (2) | (2) | (2) | (2) |

| $^{\text{(b)}}V_{\text{out,1V}}@\{V_{\text{IN}}=V_{\text{outnom}}+1V,\ I_{\text{OUT}}=25\text{mA}\}=V$  | $V_{drop} = V_{INmin} - {}^{(2)}V_{OUT,0.1\%} [mV]$     | (3) | (3) | (3) | (3) | (3) | (3) |

#### Sensing resistors:

$J_{10}$  open ( $V_{OUT} = 15V$ ):

$R_{f1} = R_1 = 590 k\Omega$ ,  $\pm 1.0\%$  tolerance

$\boldsymbol{R}_{\text{f2}} = \boldsymbol{R}_{\text{3}} = 51.1 \text{k}\Omega, \pm 0.1\%$  tolerance

$J_{10}$  shorted ( $V_{OUT} = 5V$ ):

$R_{\rm f1} = R_1(590 {\rm k}\Omega, \pm 1.0\% \text{ tolerance})$  in parallel to  $R_4(221 {\rm k}\Omega, 1.0\% \text{ tolerance})$

= 160.8k $\Omega$ ,  $\pm$ 0.5% tolerance

$\boldsymbol{R}_{\text{f2}} = \boldsymbol{R}_{\text{3}} = 51.1 \text{k}\Omega, \pm 0.1\%$  tolerance

#### TPS7A4901 reference voltage:

$V_{ref} = 1.194V \pm 1.5\%$  tolerance

#### Answer:

1 Does the dropout voltage increase or decrease with increasing load current? increases decreases other:

# Test#2: preparation and procedure

Figure 7. TPS7A4901 LDO board: jumpers set-up for Test#2

#### Jumpers set-up (see Figure 7):

- J<sub>12</sub> shorted in ON position → LDO operation enabled

- J<sub>10</sub> shorted → nominal output voltage V<sub>out</sub> = 5V

- J<sub>12</sub> shorted → C<sub>0</sub> (12nF) phase lead capacitor connected

- $J_5$  shorted  $\rightarrow C_4$  (4.7 $\mu$ F) and  $C_5$  (4.7 $\mu$ F) output capacitors connected

- $J_a$  shorted  $\rightarrow C_1$  (4.7 $\mu$ F) and  $C_2$  (4.7 $\mu$ F) input capacitors connected

- J<sub>a</sub> open → C<sub>a</sub> (2.2μF) input capacitor disconnected

- $J_{\epsilon}$  open  $\rightarrow C_{\epsilon}$  (2.2 $\mu$ F) output capacitor disconnected

- J₁, open → C₂ (100nF) phase lead capacitor disconnected

- $J_0$  open  $\to C_7$  (12nF) noise reduction capacitor disconnected

#### Test Procedure:

- 1) turn on the MULTIMETERS

- 2) set the ICM in DC CURRENT MODE, with range ≤ 1A

- 3) set the OCM in DC CURRENT MODE, with range ≤ 1A

- 4) set the IVM in DC VOLTAGE MODE, with range ≥ 10V

- 5) set the OVM in DC VOLTAGE MODE, with range ≥ 20V

- 6) turn on the POWER SUPPLY (ensure that the "OUT ON" button is OFF)

- 7) set the VOLTAGE of the POWER SUPPLY at 6V

- 8) set the POWER SUPPLY CURRENT LIMIT at 200mA

- 9) turn on the ELECTRONIC LOAD (ensure that the "LOAD ON" button is OFF)

- 10) set the ELECTRONIC LOAD in CONSTANT CURRENT MODE and the DC current at 50mA

- 11) turn ON the POWER SUPPLY "OUT ON" button

- 12) in these conditions you should read about 6V in the IVM display, about 5V in the OVM display, about 0A in the OCM display and 0A in the ICM display (if you don't read these values, turn OFF the "OUT ON" button of the DC POWER SUPPLY and verify the previous steps)

- 13) turn ON the ELECTRONIC "LOAD ON" button

- 14) in these conditions you should read about 6V in the IVM display, about 5V in the OVM display, 50mA in the OCM display and slightly more than 50mA in the ICM display (if you read values much different than the ones listed above, turn OFF the "LOAD ON" button of the ELECTRONIC LOAD and the "OUT ON" button of the DC POWER SUPPLY and verify the previous steps)

- 15) read the output voltage on the OVM display, record the value in Table 2 and repeat this step for all the values of the load current listed in Table 2, by changing the ELECTRONIC LOAD DC current set point (you do not need to turn OFF the ELECTRONIC LOAD "LOAD ON" button). Adjust the POWER SUPPLY knob until you read 6V on the IVM display for each value of the load current

- 16) set the ELECTRONIC LOAD DC current at 50mA, read the output voltage on the OVM display, record the value in Table 3 and repeat this step for all the values of the input voltage listed in Table 3, by changing the POWER SUPPLY DC voltage set point (you do not need to turn OFF the POWER SUPPLY "OUT ON" button). Adjust the POWER SUPPLY knob until you read the desired input voltage on the IVM display for each value of the load current

- 17) at the end of the measurements, turn OFF the "LOAD ON" button of the ELECTRONIC LOAD and the "OUT ON" button of the DC POWER SUPPLY, then switch off all the instruments

### Test#2: measure and calculate

- 1) Calculate the nominal output voltage V<sub>out</sub> based on the formula (1) provided in the Theory Background section, using the R<sub>H</sub> and R<sub>P</sub> values provided in the parameters box below.

- 2) With input voltage fixed at  $V_{in} = 6V$ , measure the value of the output voltage  $V_{out}$  for each value of the load current  $I_{out}$  and report the value in Table 2.

- 3) Calculate the percent LOAD REGULATION, by means of the formula (Vout-Voutnom)/Voutnom x100, for each value of the load current Iout and report the value in Table 2.

- 4) With load current fixed at I<sub>out</sub> = 50mA, measure the value of the output voltage V<sub>out</sub> for each value of the input voltage V<sub>in</sub> and report the value in Table 3.

- 5) Calculate the percent LINE REGULATION, by means of the formula  $(V_{out}-V_{outnom})/V_{outnom} \times 100$ , for each value of the input voltage  $V_{in}$  and report the value in Table 3.

- 6) Answer the questions and try to motivate the results of your observation based on the information provided in the Theory Background section and in [1][2][4].

Table 2. Load regulation of TPS7A4901 LDO regulator at Vour = 5V

| V = 6V               | I <sub>OUT</sub> [mA] |    |    |     |     |     |  |

|----------------------|-----------------------|----|----|-----|-----|-----|--|

| V <sub>IN</sub> = 6V | 25                    | 50 | 75 | 100 | 125 | 150 |  |

| V <sub>OUT</sub> [V] |                       |    |    |     |     |     |  |

| load regulation [%]  |                       |    |    |     |     |     |  |

Table 3. Line regulation of TPS7A4901 LDO regulator at  $V_{OUT} = 5V$

| L _ 50mA                | V <sub>IN</sub> [V] |   |    |    |    |    |  |

|-------------------------|---------------------|---|----|----|----|----|--|

| I <sub>OUT</sub> = 50mA | 6                   | 9 | 12 | 15 | 18 | 21 |  |

| V <sub>ουτ</sub> [V]    |                     |   |    |    |    |    |  |

| line regulation [%]     |                     |   |    |    |    |    |  |

#### Sensing resistors:

$J_{10}$  open ( $V_{OUT} = 15V$ ):

$R_{f1} = R_1 = 590 k\Omega$ , ±1.0% tolerance

$R_{12} = R_3 = 51.1 \text{k}\Omega, \pm 0.1\%$  tolerance

$J_{10}$  shorted ( $V_{OUT} = 5V$ ):

$R_{f1} = R_1(590k\Omega, \pm 1.0\% \text{ tolerance})$  in parallel to  $R_4(221k\Omega, 1.0\% \text{ tolerance})$

= 160.8k $\Omega$ , ±0.5% tolerance

$R_{f2} = R_3 = 51.1k\Omega$ ,  $\pm 0.1\%$  tolerance

#### TPS7A4901 reference voltage:

$V_{rot}$ = 1.194V±1.5% tolerance

#### Answer:

In Test#1 we are interested in investigating correlations between the value of the dropout voltage and the values of the load current and of the input voltage.

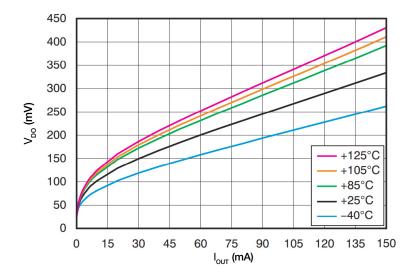

The LDO dropout voltage increases as the output current increases, as shown in the plot of Figure 8. This is determined by the increase of the emitter-to-collector voltage of the bipolar PNP pass device operating in saturation, as the current passing through the device increases. An LDO regulator characterized by a lower dropout voltage is able to work with a smaller difference between the input voltage and the output voltage (see *Experiment 5* for dropout voltage discussion relevant to N-channel MOSFET LDO regulators). This has two main positive consequences: the regulation region is expanded and the maximum efficiency of the LDO regulator increases (see *Experiment 2* for efficiency analysis of LDO regulators).

In Test#2 we are interested in investigating correlations between the value of the output voltage and the values of the load current and of the input voltage.

The plots of line and load regulation of TPS7A4901 LDO regulator are shown in Figures 10 and 11. The line and load regulation are a measure of the steady-state tolerance of the LDO regulator. A smaller value of line regulation or load regulation means that the regulated output voltage is less sensitive to the input voltage or to the load current, respectively. In other words, the LDO regulator is able to neutralize the effects of input voltage and load current variations. Such ability is the result of various influence factors, such as the type and characteristics of the pass device, the type and characteristics of the operational amplifier used to realize the feedback error amplifier, the characteristics of the voltage reference generator, the characteristics of voltage divider resistors. For a given pass device, a high open-loop gain operational amplifier is the primary requisite to achieve good line/load regulation. The line regulation and load regulation contribute to the definition of the LDO regulator accuracy, which includes the cumulative effects of line/load regulation, reference voltage, op-amp, voltage divider resistors, and temperature (see [2] for more details on thermal characteritics of TPS7A4901 LDO regulator and [12] for more details on the LDO regulator accuracy).

The plots collected in the Figures 8 to 11 show the typical characteristics of TPS7A4901 LDO regulator (see [2] for further details).

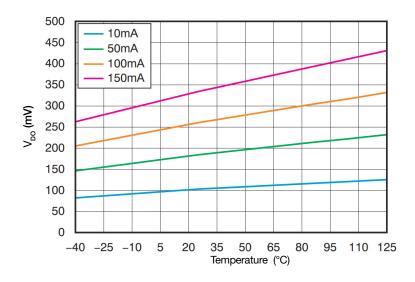

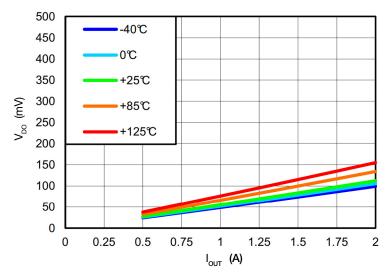

Figure 8. Dropout voltage of TPS7A4901 vs load current

Figure 9. Dropout voltage of TPS7A4901 vs temperature

The dropout voltage also depends on the LDO chip junction temperature T<sub>i</sub>. The plots of Figures 8 and 9 show how the droupout voltage of the TPS7A4901 LDO regulator changes with the junction temperature. The junction temperature,  $T_i = T_a + R_{ija}P_d$ , depends on three main factors: the LDO chip power dissipation  $P_d$  determined by the current/voltage operating conditions, the ambient temperature  $T_a$  and the junction-to-ambient thermal resistance  $R_{\theta_{ia}}$  of the LDO regulator package (it is about  $R_{\theta_{ia}} = 55^{\circ}\text{C/W}$  for TPS7A4901). Therefore, the measured dropout voltage changes with the ambient temperature (see [2] for more details on thermal characteristics of TPS7A4901 LDO regulator and Experiment 2 for further insight in thermal analysis of TPS7A4901 LDO regulator).

# Experimental plots

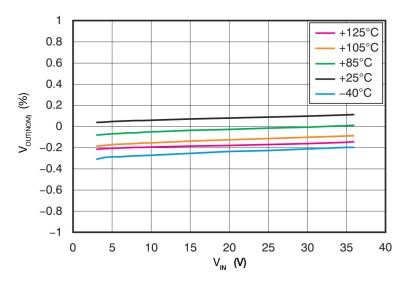

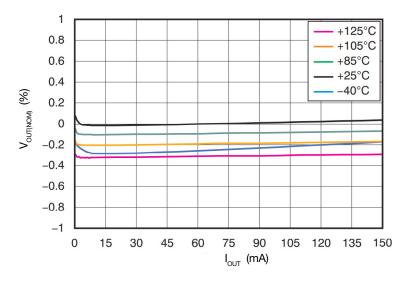

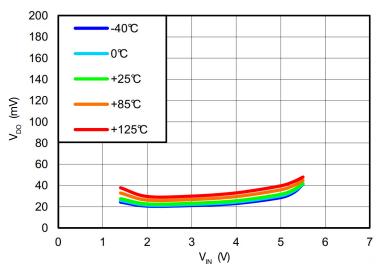

Figure 10. Line regulation of TPS7A4901, with temperature dependency

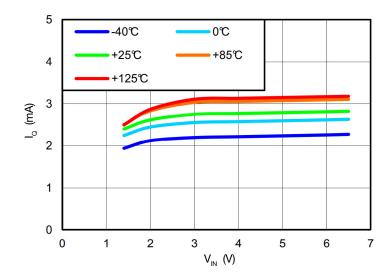

Figure 11. Load regulation of TPS7A4901, with temperature dependency

The plots of Figures 10 and 11 show the line regulation and load regulation of the TPS7A4901 LDO regulator, and their dependency on the LDO chip junction temperature. It can be observed that the both the line regulation and the load regulation are worse at very low temperature (below 0°C) and at very high temperature (above 100°C). The first situation is of interest in aerospace applications, where the ambient temperature is extremely low and the semiconductor devices inside the LDO regulator chip operate at a junction temperature below 0°C despite of their power dissipation. The second situation is of interest in automotive applications, if the LDO regulator is part of electronics located inside the engine compartment where the ambient temperature can be up to 80°C and more, or when the LDO regulator operates with a big difference between the input voltage V<sub>IN</sub> and the output voltage V<sub>OUT</sub>, which causes a high power dissipation inside the LDO regulator (see [2] for more details on thermal characteristics of TPS7A4901 LDO regulator and Experiment 2 for further insight in efficiency analysis of TPS7A4901 LDO regulator). It is interesting to note that in all the aforementioned situations, the line and load regulation become both negative. This means that the output voltage is always lower than the required nominal value. If a high accuracy is required by the specifications given for the application, it is possible to improve the line and load regulation by selecting a couple of resistors of the feedback voltage divider with appropriate values of resistances R<sub>I1</sub> and R<sub>I2</sub>, which allow to partially compensate the output voltage derating caused by the extreme temperature conditions. In order to make this solution really feasible, resistors with 0.01% to 0.1% tolerance are required, which may have some impact on the cost of the LDO solution.

# Experiment 2

The goal of this experiment is to analyze how the efficiency of an LDO regulator depends on the line and load conditions. The TPS7A4901 LDO regulator is used for this experiment.

The goal of this experiment is to analyze the correlations between the efficiency of the LDO regulator and the values of the load current and of the input voltage.

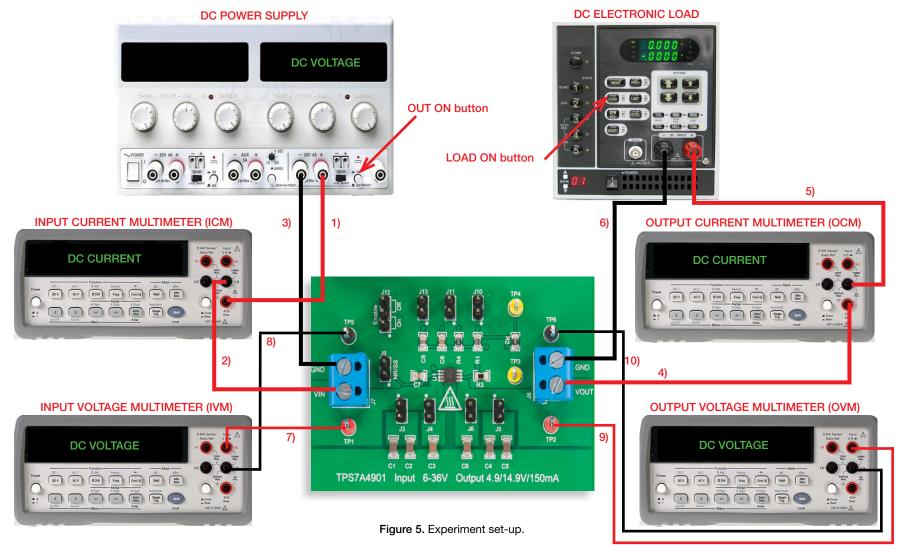

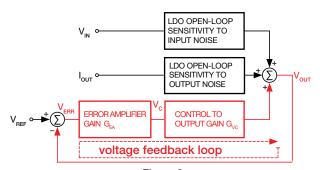

The subject of investigation in this experiment is the efficiency of LDO regulators. Figure 1 shows the simplified schematic of the TPS7A4901 LDO regulator. The main contributors that affect the efficiency of LDO regulators are: the pass device, the LDO architecture and the operating conditions. The pass device of LDO regulators is characterized by power dissipation which increases when the difference between input voltage and output voltage increases. The LDO architecture influences the efficiency as it determines the ground current  $I_{gnd}$ , also called quiescent current, which is the difference between the LDO regulator input and output currents. The ground current  $I_{gnd}$  consists of several components, determined by the band-gap reference, the sensing resistors, the error amplifier, and the pass device drive current. The ground current and the voltage drop across the pass device are determined by the load current and input voltage operating conditions. LDO regulators efficiency calculation is discussed in detail in the *Theory Background* section.

Figure 1. Simplified schematic of the TPS7A4901 LDO regulator

Test#1. We measure the input voltage  $V_{IN}$ , the input current  $I_{IN}$ , output voltage  $V_{OUT}$  and output current  $I_{OUT}$  of the TPS7A4901 LDO regulator while varying the load current. The goal is to evaluate the percent efficiency of the LDO regulator, and to observe if and how it depends on the load current. The test is repeated at different values of the input voltage to detect its influence on the efficiency.

Test#2. We measure the input voltage V<sub>IN</sub>, the input current I<sub>IN</sub>, the output voltage V<sub>OUT</sub> and output current I<sub>OUT</sub> of the TPS7A4901 LDO regulator while varying the input voltage. The goal is to evaluate the percent efficiency of the LDO regulator, to observe if and how it depends on the input voltage and to compare the measured efficiency with the results of efficiency calculation realized by means of formulae provided in the *Theory Background* section, including a basic thermal analysis. The test is repeated at different values of the output current.

# Theory Background

The fundamentals of LDO loss analysis are provided in this section (see [1][4][12] for a general discussion of LDO regulators operation and characteristics, and [2] for more details on TPS7A4901 operation and features).

Figure 2 shows an LDO regulator using a PNP bipolar transistor pass device. The pass device voltage  $V_{\rm EC}$  equals the difference between the input voltage  $V_{\rm IN}$  and the output voltage  $V_{\rm OUT}$ . The total LDO regulator power dissipation is given by the formula (1):

(1)

$$P_d = P_{IN} - P_{OUT} = V_{IN} I_{IN} - V_{OUT} I_{OUT}$$

The dissipation is determined by the LDO chip and by the voltage divider resistors  $R_{f1}$  and  $R_{f2}$ . The LDO regulator input current fulfills the equation (2):

(2)

$$I_{IN} = I_{OUT} + I_{GND} + I_{VD}$$

Based on formula (1), given the output voltage  $V_{OUT}$  and the output current  $I_{OUT}$ , the LDO regulator power dissipation increases if the input voltage increases. The PNP pass device is the main contributor to the power dissipation. Figure 3 shows the output characteristic of a PNP bipolar transistor. The output voltage regulation is ensured provided that the input voltage is higher than the dropout voltage (see Experiment 1). In this case, the PNP transistor operates in the active region and its voltage  $V_{EC}(I_{OUT}) = V_{IN} - V_{OUT}$  is higher than the saturation voltage  $V_{EC,sat}(I_{OUT})$ .

Figure 3

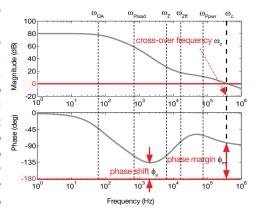

The LDO regulator efficiency  $\eta$  is given by the formula (3):

(3)

$$\eta = P_{OUT} / P_{IN} = V_{OUT} I_{OUT} / [V_{IN} (I_{OUT} + I_{GND} + I_{VD})] \times 100$$

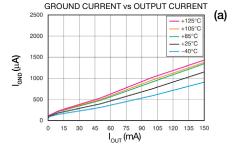

where  $I_{VD} = V_{re}/R_{F2}$  and the  $I_{GND}$  depends on LDO input voltage  $V_{IN}$ , load current  $I_{OUT}$  and junction temperature  $T_{j}$ , as shown in Figure 4. The LDO junction temperature  $T_{j}$  depends in turn on the LDO chip power losses  $P_{IDO}$  according to formula (4):

$$(4) \quad T_i = T_a + R_{\theta ia} P_{LDO}$$

where  $\mathbf{R}_{\text{\tiny BJA}}$  is the LDO chip thermal resistance,  $\mathbf{T}_{\text{a}}$  is the ambient temperature and:

(5)

$$P_{IDO} = V_{IN} I_{IN} - V_{OUT} I_{OUT} - (R_{ff} + R_{ff}) I_{VD}^2$$

The LDO ground current I<sub>GND</sub> depends on the base current needed to bias the pass device, on the error amplifier op-amp, on the voltage reference and on the junction temperature. Figure 4 shows the ground current vs output current and input voltage for the TPS7A4901 LDO regulator.

Figure 4

Good to Know

The LDO regulator sinks a quiescent current  $I_Q$  from the line, even when it is not delivering current to the load (see [1][2][12] for details).

# Experiment set-up: configuration

The instruments needed for this experiment are: a DC POWER SUPPLY, four MULTIMETERS and a DC ELECTRONIC LOAD. Figure 5 shows the instruments connections. Follow the instructions provided in next page to set-up the connections.

# Experiment set-up: instructions

With all the instruments turned off, make the following connections:

- 1) connect the POSITIVE (RED) OUTPUT of the DC POWER SUPPLY to the POSITIVE (RED) CURRENT INPUT of the INPUT CURRENT MULTIMETER (ICM)

[WARNING: the positive current input of the multimeter is distinguished from the positive voltage input]

- 2) connect the NEGATIVE (BLACK) CURRENT INPUT of the INPUT CURRENT MULTIMETER (ICM) to the INPUT (VIN) of the J<sub>7</sub> screw terminal of the TPS7A4901 LDO regulator

- 3) connect the NEGATIVE (BLACK) OUTPUT of the DC POWER SUPPLY to the GROUND (GND) of the J, screw terminal of the TPS7A4901 LDO regulator

- 4) connect the OUTPUT (VOUT) of the J<sub>s</sub> screw terminal of the TPS7A4901 LDO regulator to the POSITIVE (RED) CURRENT INPUT of the OUTPUT CURRENT MULTIMETER (OCM) [WARNING: the positive current input of the multimeter is distinguished from the positive voltage input]

- 5) connect the NEGATIVE (BLACK) CURRENT INPUT of the OUTPUT CURRENT MULTIMETER (OCM) to the POSITIVE (RED) INPUT of the ELECTRONIC LOAD

- 6) connect the NEGATIVE (BLACK) INPUT of the ELECTRONIC LOAD to the GROUND (GND) of the J<sub>s</sub> screw terminal of the TPS7A4901 LDO regulator

- 7) connect the POSITIVE (RED) VOLTAGE INPUT of the INPUT VOLTAGE MULTIMETER (IVM) to the TEST PIN TP, which is the VIN of the TPS7A4901 LDO regulator

- 8) connect the NEGATIVE (BLACK) VOLTAGE INPUT of the INPUT VOLTAGE MULTIMETER (IVM) to the TEST PIN TP, which is GND of the TPS7A4901 LDO regulator

- 9) connect the POSITIVE (RED) VOLTAGE INPUT of the OUPUT VOLTAGE MULTIMETER (OVM) to the TEST PIN TP, which is VOUT of the TPS7A4901 LDO regulator

- 10) connect the NEGATIVE (BLACK) VOLTAGE INPUT of the OUTPUT VOLTAGE MULTIMETER (OVM) to the TEST PIN TPs which is the GND of the TPS7A4901 LDO regulator

# Test#1: preparation and procedure

Figure 6. TPS7A4901 LDO board: jumpers set-up for Test#1

## Jumpers set-up (see Figure 6):

- J₁₂ shorted in ON position → LDO operation enabled

- J<sub>10</sub> shorted → nominal output voltage V<sub>out</sub> = 5V

- J₁₂ shorted → C₂ (12nF) phase lead capacitor connected

- J<sub>5</sub> shorted → C<sub>4</sub> (4.7μF) and C<sub>5</sub> (4.7μF) output capacitors connected

- $J_a$  shorted  $\rightarrow C_1$  (4.7 $\mu$ F) and  $C_2$  (4.7 $\mu$ F) input capacitors connected

- J<sub>a</sub> open → C<sub>a</sub> (2.2μF) input capacitor disconnected

- $J_{\epsilon}$  open  $\rightarrow C_{\epsilon}$  (2.2 $\mu$ F) output capacitor disconnected

- J₁, open → C₂ (100nF) phase lead capacitor disconnected

- J<sub>o</sub> open → C<sub>7</sub> (12nF) noise reduction capacitor disconnected

### **Test Procedure:**

- 1) turn on the MULTIMETERS

- set the ICM in DC CURRENT MODE, with range ≤ 1A

- 3) set the OCM in DC CURRENT MODE, with range ≤ 1A

- 4) set the IVM in DC VOLTAGE MODE, with range ≥ 5V

- 5) set the OVM in DC VOLTAGE MODE, with range ≥ 5V

- 6) turn on the POWER SUPPLY (ensure that the "OUT ON" button is OFF)

- 7) set the VOLTAGE of the POWER SUPPLY at 8V

- 8) set the POWER SUPPLY CURRENT LIMIT at 200mA

- 9) turn on the ELECTRONIC LOAD (ensure that the "LOAD ON" button is OFF)

- 10) set the ELECTRONIC LOAD in CONSTANT CURRENT MODE and the DC current at 25mA

- 11) turn ON the POWER SUPPLY "OUT ON" button

- 12) in these conditions you should read about 8V in the IVM display, 5V in the OVM display, 0A in the OCM display and 0A in the ICM display (if you don't read these values, turn OFF the "OUT ON" button of the DC POWER SUPPLY and verify the previous steps). Adjust the POWER SUPPLY knob until you read 8V on the IVM display

- 13) turn ON the ELECTRONIC LOAD "LOAD ON" button

- 14) in these conditions you should read about 8V in the IVM display, about 5V in the OVM display, 25mA in the OCM display and slightly more than 25mA in the ICM display (if you read values much different than the one listed above, turn OFF the "LOAD ON" button of the ELECTRONIC LOAD and the "OUT ON" button of the DC POWER SUPPLY and verify the previous steps)

- 15) read the output voltage and the input current of the TPS7A4901 LDO regulator on the OVM display and ICM display respectively, record the output voltage and the input current values in Table 1, and repeat this step for all the values of the load current listed in Table 1 (Adjust the POWER SUPPLY knob until you read 8V on the IVM display for each value of the load current)

- 16) change the POWER SUPPLY DC voltage set point to 10V (you do not need to turn OFF the POWER SUPPLY "OUT ON" button), and repeat the step 15)

- 17) at the end of the measurements, turn OFF the "LOAD ON" button of the ELECTRONIC LOAD and the "OUT ON" button of the DC POWER SUPPLY, then switch off all the instruments

# Test#1: measure and calculate

- For each value of the nominal input voltage and of the nominal load current indicated in Table 1, measure the input voltage V<sub>N</sub>, the input current I<sub>N</sub>, the output voltage V<sub>OLT</sub>, the output current lour, and collect the results in Table 1. [NOTE: the measured input voltage and the measured output current are the values that you read on the IVM and OCM MULTIMETERS: they might not be exactly equal to the the nominal input voltage and the nominal output current indicated in Table 1 due to resolution of the DC POWER SUPPLY and of the DC ELECTRONIC LOAD; in each measurement adjust the DC POWER SUPPLY and the DC ELECTRONIC LOAD set points so as the values you read in the IVM and OCM MULTIMETERS are as close as possible to the nominalinput voltage and the nominal output current indicated in Table 1].

- Calculate the percent efficiency by means of the formula  $\eta = V_{OLT} I_{OLT} I_{OLT}$

- 3) Analyze the measurement results, answer the questions and try to motivate the results of your observation based on the information provided in the *Theory Background* section and in [1][2][4].

Table 1. Efficiency of TI-PMLK TPS7A4901 LDO regulator vs load corrent, at output voltage V<sub>OLT</sub> = 5V.

| (1 | ) <b>V</b> <sub>IN</sub> [V] (2) I <sub>IN</sub> [mA] |     |     |     |     |     |     |     |     |     |     |     |     |

|----|-------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| (3 | *OUT [*1]                                             |     | 25  | 5   | 0   | 7   | '5  | 1(  | 00  | 1:  | 25  | 1:  | 50  |

| (5 | η [%]                                                 | _   |     |     |     |     |     |     |     |     |     |     |     |

|    |                                                       | (1) | (2) | (1) | (2) | (1) | (2) | (1) | (2) | (1) | (2) | (1) | (2) |

|    | $V_{IN} = 8V$                                         | (3) | (4) | (3) | (4) | (3) | (4) | (3) | (4) | (3) | (4) | (3) | (4) |

|    |                                                       | (5) |     | (5) |     | (5) |     | (5) |     | (5) |     | (5) |     |

|    |                                                       | (1) | (2) | (1) | (2) | (1) | (2) | (1) | (2) | (1) | (2) | (1) | (2) |

|    | $V_{IN} = 10V$                                        | (3) | (4) | (3) | (4) | (3) | (4) | (3) | (4) | (3) | (4) | (3) | (4) |

|    |                                                       | (5) |     | (5) |     | (5) |     | (5) |     | (5) |     | (5) |     |

## Sensing resistors:

$J_{10}$  open ( $V_{OUT} = 15V$ ):

$R_{f1} = R_1 = 590k\Omega$ ,  $\pm 1.0\%$  tolerance

$R_{f2} = R_3 = 51.1 \text{k}\Omega, \pm 0.1\%$  tolerance

$J_{10}$  shorted ( $V_{OUT} = 5V$ ):

$R_{s} = R_{s}(590k\Omega, \pm 1.0\% \text{ tolerance})$  in parallel to  $R_{s}(221k\Omega, 1.0\% \text{ tolerance})$

= 160.8k $\Omega$ ,  $\pm$ 0.5% tolerance

$R_{12} = R_3 = 51.1 \text{k}\Omega, \pm 0.1\%$  tolerance

## TPS7A4901 reference voltage:

$V_{ref} = 1.194V \pm 1.5\%$  tolerance

## Answer:

it depends on: \_\_\_\_\_ Does the line current equal the load current? yes no

Which operating parameter has the greatest influence on the efficiency? the line voltage the load current it depends on:

# Test#2: preparation and procedure

Figure 7. TPS7A4901 LDO board: jumpers set-up for Test#2

## Jumpers set-up (see Figure 7):

- J₁₂ shorted in ON position → LDO operation enabled

- J<sub>10</sub> open → nominal output voltage V<sub>out</sub> = 15V

- J₁₂ shorted → C₂ (12nF) phase lead capacitor connected

- $J_5$  shorted  $\rightarrow C_4$  (4.7 $\mu$ F) and  $C_5$  (4.7 $\mu$ F) output capacitors connected

- $J_a$  shorted  $\rightarrow C_1$  (4.7 $\mu$ F) and  $C_a$  (4.7 $\mu$ F) input capacitors connected

- J<sub>a</sub> open → C<sub>a</sub> (2.2μF) input capacitor disconnected

- $J_{\epsilon}$  open  $\rightarrow C_{\epsilon}$  (2.2 $\mu$ F) output capacitor disconnected

- J₁, open → C₂ (100nF) phase lead capacitor disconnected

- $J_0$  open  $\rightarrow C_7$  (12nF) noise reduction capacitor disconnected

### **Test Procedure:**

- 1) turn on the MULTIMETERS

- 2) set the ICM in DC CURRENT MODE, with range ≤ 1A

- 3) set the OCM in DC CURRENT MODE, with range  $\leq 1A$

- 4) set the IVM in DC VOLTAGE MODE, with range ≥ 15V

- 5) set the OVM in DC VOLTAGE MODE, with range ≥ 30V

- 6) turn on the POWER SUPPLY (ensure that the "OUT ON" button is OFF)

- 7) set the VOLTAGE of the POWER SUPPLY at 16V

- 8) set the POWER SUPPLY CURRENT LIMIT at 200mA

- 9) turn on the ELECTRONIC LOAD (ensure that the "LOAD ON" button is OFF)

- 10) set the ELECTRONIC LOAD in CONSTANT CURRENT MODE and set the DC current at 10mA

- 11) turn ON the POWER SUPPLY "OUT ON" button

- 12) in these conditions you should read about 16V in the IVM display, 15V in the OVM display, 0A in the OCM display and 0A in the ICM display (if you don't read these values, turn OFF the "OUT ON" button of the DC POWER SUPPLY and verify the previous steps). Adjust the POWER SUPPLY knob until you read 16V on the IVM display

- 13) turn ON the ELECTRONIC "LOAD ON" button

- 14) in these conditions you should read about 16V in the IVM display, about 15V in the OVM display, 10mA in the OCM display and slightly more than 25mA in the ICM display (if you read values much different than the one listed above, turn OFF the "LOAD ON" button of the ELECTRONIC LOAD and the "OUT ON" button of the DC POWER SUPPLY and verify the previous steps)

- 15) read the output voltage and the input current of the TPS7A4901 LDO regulator on the OVM display and ICM display respectively, use the values for the calculations required in Table 2, and repeat this step for all the values of the input voltage listed in Table 2 (adjust the POWER SUPPLY knob until you read the desired input voltage value on the IVM display)

- 16) change the ELECTRONIC LOAD DC current set point to 50mA (you do not need to turn OFF the ELECTRONIC LOAD "LOAD ON" button), and repeat the step 15

- 17) at the end of the measurements, turn OFF the "LOAD ON" button of the ELECTRONIC LOAD and the "OUT ON" button of the DC POWER SUPPLY, then switch off all the instruments

# Test#2: measure and calculate

- 1) For each value of the input voltage and of the load current indicated in Table 2, measure the input current I<sub>IN</sub> and the output voltage V<sub>OUT</sub>, calculate the experimental percent efficiency by means of the formula η<sub>exp</sub> [%] = V<sub>OUT</sub> I<sub>OUT</sub> / (V<sub>IN</sub> I<sub>IN</sub>) x 100 and report the result in Table 2.

- 2) Calculate the theoretical percent efficiency by means of the formula (3) provided in the *Theory Background* section and report the result in Table 2 [NOTE: use the plots of Figure 4(b) to determine the ground current I<sub>GND</sub> of TPS7A4901 LDO regulator].

- 3) Calculate the LDO power losses P<sub>LDO</sub> by means of the formula (5) provided in the *Theory Background* section, calculate the LDO chip junction temperature *T<sub>j</sub>* by means of the formula (4) provided in the *Theory Background* section and report the result in Table 2 [NOTE: assume that the ambient temperature *T<sub>a</sub>* is 25°C, or use a value of the ambient temperature measured nearby the LDO chip, if available].

- 4) Use the plots of Figure 4(a) to update the value of the ground current  $I_{GND}$ , based on the calculated junction temperature  $T_{ij}$ , and to refine the value of the theoretical efficiency  $\eta_{theo}$  [%] calculated at point 2).

- 5) Answer the questions and try to motivate the results of your observation based on the information provided in the *Theory Background* section and in [1][2][4].

Table 2. Experimental vs theoretical efficiency of TI-PMLK TPS7A4901 LDO regulator vs input voltage, at output voltage V<sub>OUT</sub> = 15V

| (1) | exp η <sub>exp</sub> [%] | (2) | theo η <sub>theo</sub> [%] |     | $V_IN$ |     |     |     |     |     |     |     |     |     |    |

|-----|--------------------------|-----|----------------------------|-----|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|

| (3) | loss P <sub>d</sub> [mW] | (4) | temp T <sub>j</sub> [°C]   | 10  | 6V     | 18  | 3V  | 20  | VC  | 22  | 2V  | 24  | 4V  | 2   | 6V |

|     | I <sub>out</sub> = 10mA  |     | (1)                        | (2) | (1)    | (2) | (1) | (2) | (1) | (2) | (1) | (2) | (1) | (2) |    |

|     |                          |     | (3)                        | (4) | (3)    | (4) | (3) | (4) | (3) | (4) | (3) | (4) | (3) | (4) |    |

|     | I <sub>оит</sub> = 50mA  |     | (1)                        | (2) | (1)    | (2) | (1) | (2) | (1) | (2) | (1) | (2) | (1) | (2) |    |

|     |                          |     | (3)                        | (4) | (3)    | (4) | (3) | (4) | (3) | (4) | (3) | (4) | (3) | (4) |    |

### Sensing resistors:

$J_{10}$  open ( $V_{OUT} = 15V$ ):

$R_{_{f1}}$  =  $R_{_{1}}$  =  $590k\Omega,~\pm1.0\%$  tolerance

$\boldsymbol{R}_{\text{f2}} = \boldsymbol{R}_{\text{3}} = 51.1 \text{k}\Omega, \pm 0.1\%$  tolerance

$J_{10}$  shorted ( $V_{OUT} = 5V$ ):

$R_{t1} = R_1(590k\Omega, \pm 1.0\% \text{ tolerance})$  in parallel to  $R_1(221k\Omega, 1.0\% \text{ tolerance})$

= 160.8k $\Omega$ , ±0.5% tolerance

$\boldsymbol{R}_{\text{f2}} = \boldsymbol{R}_{\text{3}} = 51.1 \text{k}\Omega, \pm 0.1\%$  tolerance

## TPS7A4901 reference voltage:

$V_{ref}$ = 1.194V±1.5% tolerance

## Answer:

2 Which are the input voltage and output current conditions allowing to achieve the maximum efficiency?

In Test#1 we are interested in investigating correlations between the efficiency of the LDO regulator and the values of the load current.

Both the input voltage  $V_{IN}$  and the load current  $I_{OUT}$  have an impact on the LDO regulator efficiency. However, you may observe from experimental measurements that the input voltage  $V_{IN}$  has a much higher influence on the efficiency than the output current  $I_{OUT}$ . In fact, given the LDO regulator output voltage  $V_{OUT}$  and load current  $I_{OUT}$ , an increase of the input voltage  $V_{IN}$  directly translates into an increase of the pass device voltage  $V_{EC}$ , thus having a strong impact on the difference between the input power  $P_{IN}$  and the output power  $P_{OUT}$  of the LDO regulator, as highlighted in the formula (1) provided in the *Theory Background* section. Instead, given the LDO regulator output voltage  $V_{OUT}$  and input voltage  $V_{IN}$ , an increase of the load current  $I_{OUT}$  directly translates into an increase of the input current  $I_{IN}$  too, thus making the effect on the power losses limited to the increase of the LDO chip ground current  $I_{CND}$ , as highlihted in the formula (2) provided in the *Theory Background* section. (see *Experiment 5* for ground current discussion relevant to *N*-channel MOSFET LDO regulators).

In Test#2 we are interested in investigating correlations between the efficiency of the LDO regulator and the values of the input voltage, taking into account the thermal properties of the LDO regulator.

The results of measurements should highlight that the main factor of influence on the efficiency is the ratio between the input voltage  $V_{IN}$  and the output voltage  $V_{OUT}$ , whereas the LDO chip ground current  $I_{GND}$  has minor influence, for the same reasons relevant to Test#1 discussed above. It should be noted that the ground current  $I_{GND}$  increases with the LDO chip junction temperature  $T_{j}$ , which in turn is higher when the input voltage  $V_{IN}$  is higher, due to the higher LDO losses  $P_{LDO}$ . Therefore, the increase of the input voltage  $V_{IN}$  boosts the ground current  $I_{GND}$ , thus having a two fold influence on the degradation of the effciency (see [2] for more details on thermal characteritics of TPS7A4901 LDO regulator).

# Experimental plots

The plots collected in the Figures 8 to 11 show the typical characteristics of TPS7A4901 LDO regulator (see [2] for further details).

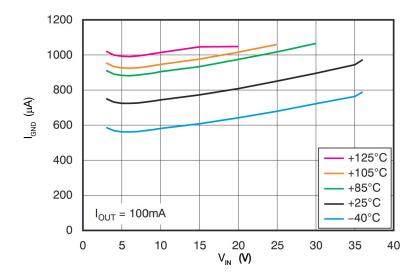

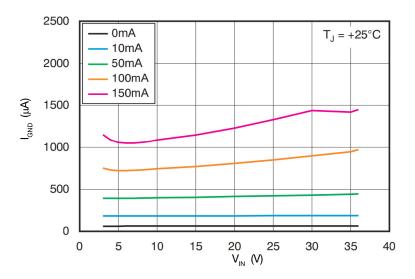

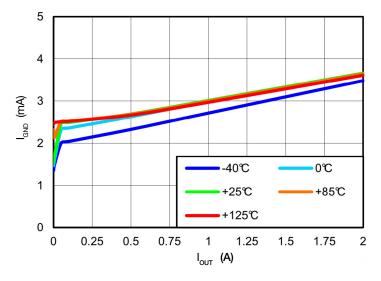

Figure 8. Ground current of TPS7A4901 LDO regulator vs input voltage at 100mA

Figure 9. Ground current of TPS7A4901 LDO regulator vs input voltage at 25°C

The plots of Figures 8 and 9 provide a synoptic view of how the LDO chip ground current  $I_{QND}$  depends on input voltage  $V_{IN}$ , load current  $I_{QUT}$ , and junction temperature  $T_{j}$ . The voltage divider current  $I_{VD}$  has a very little influence on the efficiency, provided that its value is very small, as in the case of the TPS7A4901 LDO regulator. The voltage divider current  $I_{VD}$  depends on the LDO chip voltage reference  $V_{ref}$  and on the resistance  $R_{pp}$  of the output voltage divider, as shown in the *Theory Background* section.

# Experimental plots

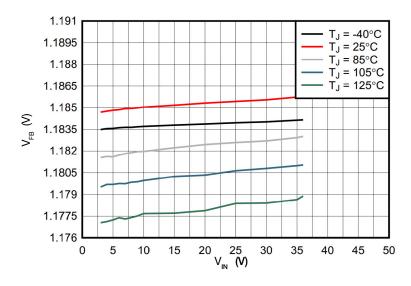

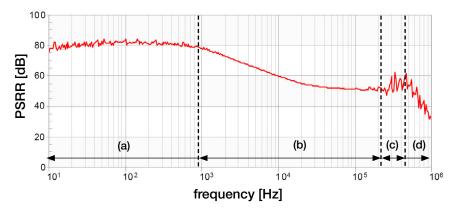

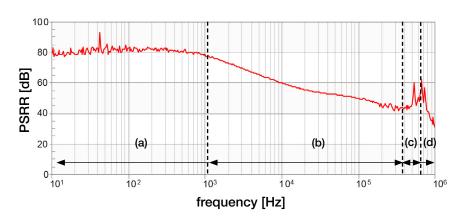

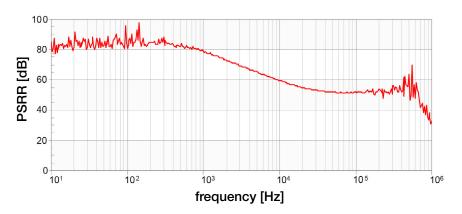

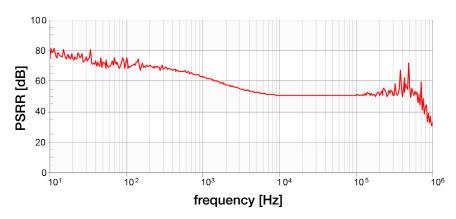

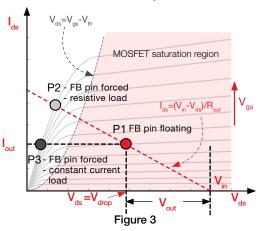

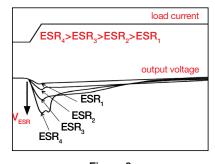

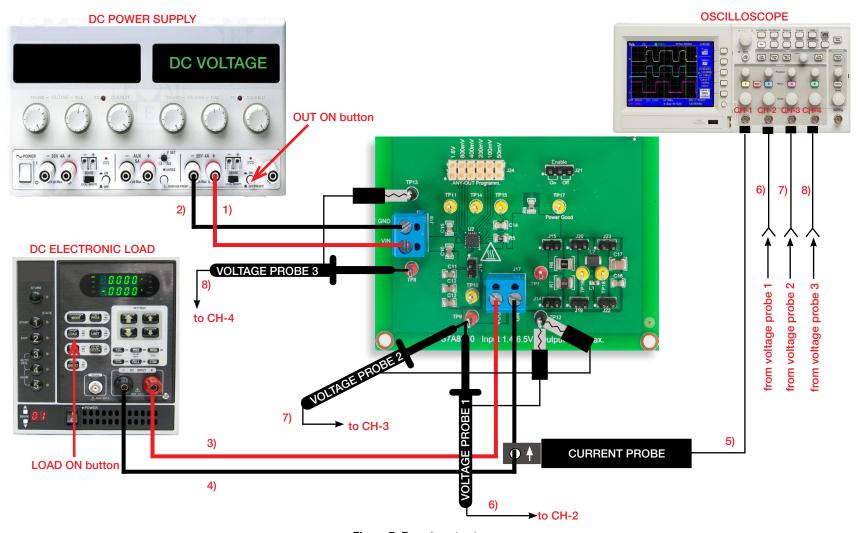

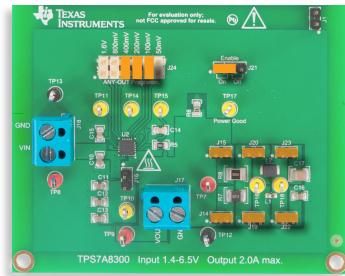

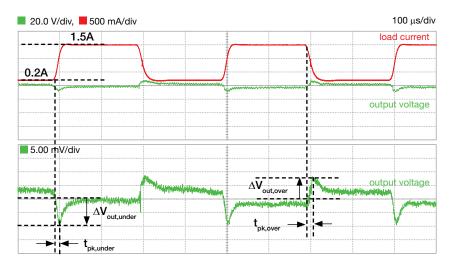

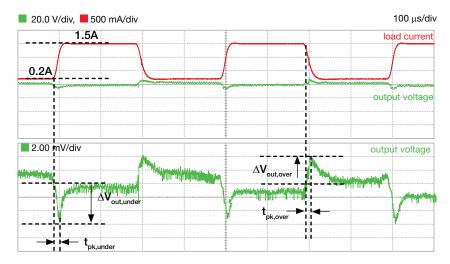

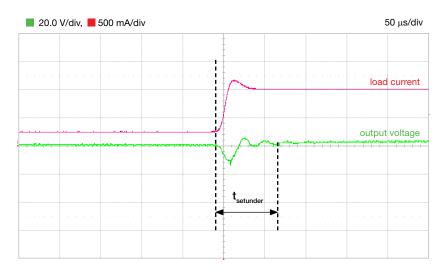

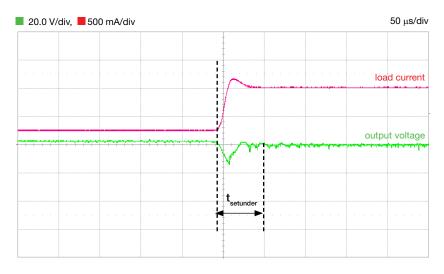

Figure 10. Feedback pin voltage of TPS7A4901 LDO regulator vs input voltage