# TMS320C6670 Multicore Fixed and Floating-Point System-on-Chip Silicon Revision 1.0, 2.0

# **Silicon Errata**

Literature Number: SPRZ332F May 2014

## **Release History**

| Release  | Date           | Description/Comments                                                                                                                                                                                             |

|----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPRZ332F | May 2014       | • Updated Advisory 9 - HyperLink Temporary Blocking Issue (Page 21)                                                                                                                                              |

|          |                | • Added Advisory 37 - False DDR3 Write ECC Error Reported Under Certain Conditions (Page 68)                                                                                                                     |

| SPRZ332E | December 2013  | • Updated that Advisory 10 BCP DNT Support for 10ms TTI With Spreading Factor Two Issue does not apply to revision 2.0 (Page 10)                                                                                 |

|          |                | • Added Step 8 in workaround 2 of Adivosry 24 (Page 43)                                                                                                                                                          |

|          |                | • Added Usage Note 29: Incorrect Output from TAC for Certain Channels When Configuring TAC_Gn_DATA_FETCH and TAC_Gn_HEAD_FETCH Registers with Values Having a Difference of 8 or 16 Usage Note (Page 100)        |

| SPRZ332D | July 2013      | Added Advisory 36: BCP Soft Slicer Lock-Up (Page 67)                                                                                                                                                             |

|          |                | • Updated the description of Usage Note 2: AIF2 Protocol Encoder Registers Usage Note (Page 69)                                                                                                                  |

|          |                | • Added Usage Note 28: DDR3 Class of Service Feature Can Cause Higher Than Expected Latency Usage Note (Page 99)                                                                                                 |

| SPRZ332C | June 2013      | Added Advisory 32: Single MFENCE Issue (Page 54)                                                                                                                                                                 |

|          |                | Added Advisory 33: Read Exception and Data Corruption Issue (Page 56)                                                                                                                                            |

|          |                | <ul> <li>Added Advisory 34: Incorrect Output from TAC for HS-PDSCH and P-CCPCH Channels in Certain Spreader Allocation<br/>Sequences Issue (Page 60)</li> </ul>                                                  |

|          |                | <ul> <li>Added Advisory 35: Incorrect Output from TAC for a Fetching Spreader on a Collision between Input Header's Fetch<br/>Write to the Spreader's SPM and Software's Write to SPM Issue (Page 62)</li> </ul> |

|          |                | • Added Usage Note 21: POR and RESETFULL Sequence Usage Note (Page 86)                                                                                                                                           |

|          |                | • Added Usage Note 22 Revised PLL Programming Sequence Usage Note (Page 87)                                                                                                                                      |

|          |                | • Added Usage Note 23 Core Wake Up on RESETz Usage Note (Page 88)                                                                                                                                                |

|          |                | Added Usage Note 23 BCP RX BSS Port Aliasing Usage Note (Page 89)                                                                                                                                                |

|          |                | Added Usage Note 24 BSDL Testing Support Usage Note (Page 91)                                                                                                                                                    |

|          |                | Added Usage Note 26: AIF2 CPRI FastC&M Restrictions and Usage Note (Page 93)                                                                                                                                     |

|          |                | Added Usage Note 27: Initial Voltage Level Setting of CVDD Rail Power Supplies Usage Note (Page 95)                                                                                                              |

| SPRZ332B | May 2012       | • Added Usage Note 20: IDMA1 Performance Limitation Usage Note (Page 74)                                                                                                                                         |

|          |                | • Added Usage Note 19: CAS Write Latency at Low Speed Bins in DDR3 Multi-rank Configuration (Page 73)                                                                                                            |

|          |                | <ul> <li>Added Usage Note 18: Current Flow Between VDDT and VDDR Rails During Power Sequencing of DSP Usage Note<br/>(Page 72)</li> </ul>                                                                        |

|          |                | Added Advisory 31: DDR3 Incremental Write Leveling Issue (Page 53)                                                                                                                                               |

|          |                | Added Advisory 30: DDR3 Automatic Leveling Issue (Page 49)                                                                                                                                                       |

|          |                | • Added Usage Note 17: Packet DMA Does Not Update RX PS Region Location Bit Usage Note (Page 71)                                                                                                                 |

|          |                | Added Usage Note 16: The Clock Input To NETCP Usage Note (Page 70)                                                                                                                                               |

|          |                | Added Usage Note 15: Sticky Bits in PCIe MMRs Usage Note (Page 69)                                                                                                                                               |

|          |                | Added Usage Note 14: PCIe BAR5 Window Size Configuration in Boot ROM Usage Note (Page 68)                                                                                                                        |

| SPRZ332A | January 2012   | <ul> <li>Added Advisory 29: Power Domains Hang During Powering Up at The Same Time As a RESETZ (Hard Reset) Received<br/>Issue (Page 48)</li> </ul>                                                              |

|          |                | • Added Advisory 28: System Reset Operation Disconnects SoC from CCS Issue (Page 47)                                                                                                                             |

|          |                | Added Advisory 27: SerDes AC-JTAG (1149.6) Receiver Sensitivity Issue (Page 44)                                                                                                                                  |

|          |                | • Added Advisory 26: AIF2 Line Code Violation Error from B8 SerDes to B4 SerDes Lanes Cross Connection Issue (Page 43)                                                                                           |

|          |                | • Added Advisory 25: Data Corruption on C66x CorePAC Initiated PCIe MMRs Read in Big Endian Mode Issue (Page 42)                                                                                                 |

|          |                | • Added Advisory 24: L2 Cache Corruption During Block and Global Coherence Operations Issue (Page 40)                                                                                                            |

|          |                | Added Advisory 23: AIF2 CPRI 8x UL Peak Bandwidth Issue (Page 39)                                                                                                                                                |

|          |                | Added Usage Note 13: AIF2 LTE 3MHz and 1.4MHz Support Usage Note (Page 66)                                                                                                                                       |

|          |                | Added Advisory 22: HyperLink Data Rate Limited to 40Gbaud/s Issue (Page 38)  Added Hanna Ness 13: DDB3 Performance Limited to 1333MT/s Hanna Ness (Page 35)                                                      |

|          |                | Added Usage Note 12: DDR3 Performance Limited to 1333MT/s Usage Note (Page 65)                                                                                                                                   |

| SPRZ332  | September 2011 | Initial Release                                                                                                                                                                                                  |

#### Contents

| Introduction                                                                                          |                    |

|-------------------------------------------------------------------------------------------------------|--------------------|

| Device and Development Support Tool Nomenclature                                                      |                    |

| Package Symbolization and Revision Identification                                                     |                    |

| Silicon Updates                                                                                       |                    |

| Advisory 1— SRIO Packet Forwarding Issue                                                              |                    |

| Advisory 2— SRIO Messaging in Highly Oversubscribed System Issue                                      |                    |

| Advisory 3— SRIO Direct I/O NREAD Data Corruption Issue                                               |                    |

| Advisory 4— SRIO Reset Isolation Not Functional Issue                                                 |                    |

| Advisory 5— SRIO Register Aliasing Issue                                                              |                    |

| Advisory 6— Potential L2 Cache Corruption During Block Coherence Operations Issue                     |                    |

| Advisory 7— Queue Manager External Linking RAM Location Issue                                         |                    |

| Advisory 8— AIF2 AIF_TX_MONO_MODE Not Compatible With Other Navigator Modules Issue                   |                    |

| Advisory 9— HyperLink Temporary Blocking Issue                                                        |                    |

| Advisory 10— BCP DNT Support for HSUPA 10ms TTI With Spreading Factor Two Issue                       |                    |

| Advisory 11— BCP DIO Reading From DDR Memory Issue                                                    |                    |

| Advisory 12— AIF2 CPRI LTE Ingress Antenna Carrier Packing Issue                                      |                    |

| Advisory 13— DDR3 Excessive Refresh Issue                                                             |                    |

| Advisory 14— TAC P-CCPCH QPSK Symbol Data Mode with STTD Issue                                        |                    |

| Advisory 15— AIF2 GSM T1, T2, T3 Miscalculation Issue                                                 |                    |

| Advisory 17— AIF2 Multiple DBMR Operation issue                                                       |                    |

| Advisory 18— AIF2 SerDes Comma Alignment Failure Issue                                                |                    |

| Advisory 19— SRIO Control Symbols Are Sent More Often Than Required Issue                             |                    |

| Advisory 20— Corruption of Control Characters In SRIO Line Loopback Mode Issue                        |                    |

| Advisory 21— SerDes Transit Signals Pass ESD-CDM up to ±150 V Issue                                   |                    |

| Advisory 22— HyperLink Data Rate Limited to 40Gbaud/s Issue                                           |                    |

| Advisory 23— AIF2 CPRI 8x UL Peak Bandwidth Issue                                                     |                    |

| Advisory 24— L2 Cache Corruption During Block and Global Coherence Operations Issue                   |                    |

| Advisory 25— Data Corruption on C66x CorePAC Initiated PCIe MMRs Read in Big Endian Mode Issue        |                    |

| Advisory 26— AIF2 Line Code Violation Error from B8 SerDes to B4 SerDes Lanes Cross Connection Issue. |                    |

| Advisory 27— SerDes AC-JTAG (1149.6) Receiver Sensitivity Issue                                       |                    |

| Advisory 28— System Reset Operation Disconnects SoC from CCS Issue                                    |                    |

| Advisory 29— Power Domains Hang During Powering Up at The Same Time As a RESET (Hard Reset) Rece      |                    |

| Advisory 30— DDR3 Automatic Leveling Issue                                                            |                    |

| Advisory 31— DDR3 Incremental Write Leveling Issue                                                    | 55                 |

| Advisory 32— Single MFENCE Issue                                                                      | 56                 |

| Advisory 33— Read Exception and Data Corruption Issue                                                 | 58                 |

| Advisory 34— Incorrect Output from TAC for HS-PDSCH and P-CCPCH Channels in Certain Spreader Alloc    | ation Sequences    |

| lssue                                                                                                 |                    |

| Advisory 35— Incorrect Output from TAC for a Fetching Spreader on a Collision between Input Header's  | Fetch Write to the |

| Spreader's SPM and Software's Write to SPM Issue                                                      | 64                 |

| Advisory 36— BCP Soft Slicer Lock-Up                                                                  |                    |

| Advisory 37— False DDR3 Write ECC Error Reported Under Certain Conditions                             |                    |

| Usage Note 1— AIF2 GSM Compressed Mode and Multi-mode Usage Note                                      |                    |

| Usage Note 2— AIF2 Protocol Encoder Registers Usage Note                                              |                    |

| Usage Note 3— TAC DL TPC Timing Usage Note                                                            |                    |

| Usage Note 4— Packet DMA Clock-Gating for AIF2 and Packet Accelerator Sub-system Usage Note           |                    |

| Usage Note 5— VCP2 Back-to-Back Debug Read Usage Note                                                 |                    |

| Usage Note 6— DDR3 ZQ Calibration Usage Note                                                          |                    |

| Usage Note 7—1 <sup>2</sup> C Bus Hang After Master Reset Usage Note                                  |                    |

| Usage Note 8— MPU Read Permissions for Queue Manager Sub-system Usage Note                            |                    |

| Usage Note 9— Queue Proxy Access Usage Note                                                           |                    |

| Usage Note 10— TAC E-AGCH Diversity Mode Usage Note                                                   |                    |

| Usage Note 11— Minimizing Main PLL Jitter Usage Note                                                  |                    |

| Usage Note 12— DDR3 Performance Limited to 1333MT/s Usage Note                                        |                    |

| Usage Note 13— AIF2 LTE 3MHz and 1.4MHz Support Usage Note                                            | 82                 |

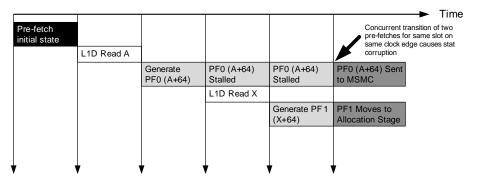

Usage Note 14— PCIe BAR5 Window Size Configuration in Boot ROM Usage Note .......84 Usage Note 18— Current Flow Between VDDT and VDDR Rails During Power Sequencing of DSP Usage Note.............88 Usage Note 19— CAS Write Latency (CWL) at Low Speed Bins in DDR3 Multi-rank Configuration Usage Note ........................89 Usage Note 20— IDMA1 Performance Limitation Usage Note ......90 Usage Note 24— BCP RX BSS Port Aliasing Usage Note .......94 Usage Note 29— Incorrect Output from TAC for Certain Channels When Configuring TAC Gn\_DATA\_FETCH and **List of Figures** Figure 1 Figure 2 Figure 3 Figure 4 Figure 5 Figure 6 Figure 7 Figure 8 Figure 9 Figure 10 Simplified SerDes receiver block diagram depicting relative placement of major receiver components ......46 Figure 11 Figure 12 Figure 13 Figure 14 Figure 15 Timing Details of Writing Leveling Sequence ......55 Figure 16 Initial state of pre-fetch buffer ......59 Figure 17 Sequence Diagram ......60 Figure 18 Symbol Processing on Ingress .......82 Figure 19 Symbol Processing on Egress ......83 **List of Tables** Table 1 Table 2 Table 3 Table 4 Table 5 Affected SRIO MAC Registers That May Need to Be Written After Initialization and Require Special Handling.......17 Table 6 Table 7 Table 8 Table 9 Table 10 Possible outcomes depending on relative timing of subsequent pre-fetchable data access to X+64, PF0 return Table 11 Table 12 Table 13 Cyclic Prefix Length for Each LTE Bandwidth......82

| ww | w. | tı. | co | m |

|----|----|-----|----|---|

| Table 14 | IDMA1 Transaction Performance           | 90  |

|----------|-----------------------------------------|-----|

| Table 15 | Expected Mapping for TX/RX BSS Ports    | 94  |

| Table 16 | Actual Mapping for TX/RX BSS Ports      | 94  |

| Table 17 | Register Information for the Peripheral |     |

| Table 18 | TAC Registers Configuration             | 103 |

| Table 19 | TAC Registers Configuration             | 103 |

## TMS320C6670 Multicore Fixed and Floating-Point System-on-Chip Silicon Revision 1.0, 2.0

#### Introduction

This document describes the silicon updates to the functional specifications for the TMS320C6670 fixed-/floating-point digital signal processor. See the device-specific data manual, *TMS320C6670 Multicore Fixed and Floating-Point System-on-Chip* data manual (literature number SPRS689) for more information.

#### **Device and Development Support Tool Nomenclature**

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all DSP devices and support tools. Each DSP commercial family member has one of three prefixes: TMX, TMP, or TMS (e.g., TMS320C6670CYP). Texas Instruments recommends one of two possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX) through fully qualified production devices/tools (TMS/TMDS).

Device development evolutionary flow:

TMX Experimental device that is not necessarily representative of the final device's electrical specifications

TMP Final silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification

**TMS** Fully-qualified production device

Support tool development evolutionary flow:

TMDX Development-support product that has not yet completed Texas Instruments internal qualification testing

**TMDS** Fully-qualified development-support product

TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:

#### Developmental product is intended for internal evaluation purposes.

TMS devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (TMX or TMP) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

#### **Package Symbolization and Revision Identification**

The device revision can be determined by the lot trace code marked on the top of the package. The location of the lot trace code for the CYP package is shown in Figure 1. Figure 1 also shows an example of C6670 package symbolization.

Figure 1 Lot Trace Code Example for TMS320C6670 (CYP Package)

Silicon revision correlates to the lot trace code marked on the package. This code is of the format #xx-######. Note that there may be an additional leading character (not shown in this example) and xx may actually be two or three characters. If xx is **10A**, then the silicon is revision 1.0. Table 1 lists the silicon revisions associated with each lot trace code for the C6670 devices.

Table 1 Lot Trace Codes

| Lot Trace Code (xx) | Silicon Revision | Comments                 |  |  |

|---------------------|------------------|--------------------------|--|--|

| 10A                 | 1.0              | Initial silicon revision |  |  |

| 20C                 | 2.0              | Silicon revision 2.0     |  |  |

| End of Table 1      |                  |                          |  |  |

The C6670 device contains multiple read-only register fields that report revision values. The JTAG ID (JTAGID), C66x CorePac Revision ID (MM\_REVID) and CPU Control Status (CSR) registers allow the customer to read the current device and CPU level revision of the C6670.

The JTAG ID register (JTAGID) is a read-only register that identifies to the customer the JTAG/Device ID. The value in the VARIANT field of the JTAG ID Register changes based on the revision of the silicon being used.

The C66x CorePac Revision ID register (MM\_REVID) is a read-only register that identifies to the customer the revision of the C66x CorePac. The value in the VERSION field of the C66x CorePac Revision ID Register changes based on the version of the C66x CorePac implemented on the device. More details on the C66x CorePac Revision ID register can be found in the *TMS320C6670 Multicore Fixed and Floating-Point System-on-Chip* data manual (literature number SPRS689).

The CPU Control Status Register (CSR) contains a read-only REVISION\_ID field that identifies to the customer the revision of the CPU being used. More information about the CPU Control Status Register can be found in the *C66x CPU and Instruction Set Reference Guide* (literature number SPRUGH7).

Table 2 shows the contents of the CPU Control Status Register CPU\_ID and REVISION\_ID fields, C66x CorePac MM\_REVID Register REVISION field, and the JTAGID register VARIANT field for each silicon revision of the C6670 device.

Table 2 Silicon Revision Variables

| Silicon<br>Revision | CPU CSR<br>Register    | C66x CorePac<br>MM_REVID Register | C6670 JTAGID<br>Register |

|---------------------|------------------------|-----------------------------------|--------------------------|

| 1.0                 | CSR[CPU_ID] = 15h      | Rev. 1.0                          | JTAGID[VARIANT] = 0h     |

|                     | CSR[REVISION_ID] = 00h | MM_REVID[REVISION] = 0000h        | JIAGID[VARIANT] = UII    |

| 2.0                 | CSR[CPU_ID] = 15h      | Rev. 2.0                          | JTAGID[VARIANT] = 1h     |

|                     | CSR[REVISION_ID] = 00h | MM_REVID[REVISION] = 0001h        | JIAGID[VARIANI] = IN     |

| End of Table 2      |                        |                                   |                          |

More details on the JTAG ID and CorePac Revision ID Registers can be found in the *TMS320C6670 Multicore Fixed and Floating-Point System-on-Chip* data manual (literature number SPRS689).

## **Silicon Updates**

Table 3 lists the silicon updates applicable to each silicon revision. For details on each advisory, click on the link below.

Table 3 Silicon Revision Updates (Part 1 of 2)

|                                                                                                                                                             |             | Applies To Silicon Revision |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------|-----|

| Silicon Update Advisory                                                                                                                                     | See         | 1.0                         | 2.0 |

| SRIO Packet Forwarding Issue                                                                                                                                | Advisory 1  | Х                           |     |

| SRIO Messaging in Highly Oversubscribed System Issue                                                                                                        | Advisory 2  | Х                           |     |

| SRIO Direct I/O NREAD Data Corruption Issue                                                                                                                 | Advisory 3  | Х                           |     |

| SRIO Reset Isolation Not Functional Issue                                                                                                                   | Advisory 4  | Х                           |     |

| SRIO Register Aliasing Issue                                                                                                                                | Advisory 5  | Х                           |     |

| Potential L2 Cache Corruption During Block Coherence Operations Issue                                                                                       | Advisory 6  | Х                           |     |

| Queue Manager External Linking RAM Location Issue                                                                                                           | Advisory 7  | Х                           | Х   |

| AIF2 AIF_TX_MONO_MODE Not Compatible With Other Navigator Modules Issue                                                                                     | Advisory 8  | Х                           |     |

| HyperLink Temporary Blocking Issue                                                                                                                          | Advisory 9  | Х                           | Х   |

| BCP DNT Support for HSUPA 10ms TTI With Spreading Factor Two Issue                                                                                          | Advisory 10 | Х                           |     |

| BCP DIO Reading From DDR Memory Issue                                                                                                                       | Advisory 11 | Х                           | Х   |

| AIF2 CPRI LTE Ingress Antenna Carrier Packing Issue                                                                                                         | Advisory 12 | Х                           |     |

| DDR3 Excessive Refresh Issue                                                                                                                                | Advisory 13 | Х                           | Х   |

| TAC P-CCPCH QPSK Symbol Data Mode with STTD Issue                                                                                                           | Advisory 14 | Х                           | Х   |

| AIF2 GSM T1, T2, T3 Mis-calculation Issue                                                                                                                   | Advisory 15 | Х                           |     |

| AIF2 Multiple DBMR operation Issue                                                                                                                          | Advisory 16 | Х                           |     |

| BCP CRC Failure Issue                                                                                                                                       | Advisory 17 | Х                           |     |

| AIF2 SerDes Comma Alignment Failure Issue                                                                                                                   | Advisory 18 | Х                           |     |

| SRIO Status Control Symbols are sent more often than required Issue                                                                                         | Advisory 19 | Х                           | Х   |

| Corruption of Control Characters in SRIO line loopback mode Issue                                                                                           | Advisory 20 | Х                           | Х   |

| SerDes Transit Signals Pass ESD-CDM up to +/-150V Issue                                                                                                     | Advisory 21 | Х                           | Х   |

| HyperLink Data Rate Limited to 40Gbaud/s Issue                                                                                                              | Advisory 22 | Х                           | Х   |

| AIF2 CPRI 8x UL Peak Bandwidth Issue                                                                                                                        | Advisory 23 | Х                           | Х   |

| L2 Cache Corruption due to Block and Global Coherence Operations Issue                                                                                      | Advisory 24 |                             | Х   |

| Data Corruption on C66x CorePAC Initiated PCIe MMRs Read in Big Endian Mode Issue                                                                           | Advisory 25 | Х                           |     |

| AIF2 Line Code Violation Error from SerDes B8 to SerDes B4 Lanes Cross Connection Issue                                                                     | Advisory 26 | Х                           |     |

| SerDes AC-JTAG (1149.6) Receiver Sensitivity Issue                                                                                                          | Advisory 27 | Х                           | Х   |

| System Reset Operation Disconnects SoC from CCS Issue                                                                                                       | Advisory 28 |                             | Х   |

| Power Domains Hang on Powering Them up at The Same Time as a RESET Received Issue                                                                           | Advisory 29 | Х                           | Х   |

| DDR3 Incremental Write Leveling Issue                                                                                                                       | Advisory 30 | Х                           | Х   |

| DDR3 Automatic Leveling Issue                                                                                                                               | Advisory 31 | Х                           | Х   |

| Single MFENCE Issue                                                                                                                                         | Advisory 32 | Х                           | Х   |

| Read Exception and Data Corruption Issue                                                                                                                    | Advisory 33 | Х                           | Х   |

| Incorrect Output from TAC for HS-PDSCH and P-CCPCH Channels in Certain Spreader Allocation Sequences Issue                                                  | Advisory 34 | Х                           | Х   |

| Incorrect Output from TAC for a Fetching Spreader on a Collision between Input Header's Fetch Write to the Spreader's SPM and Software's Write to SPM Issue | Advisory 35 | Х                           | Х   |

| BCP Soft Slicer Lock-Up                                                                                                                                     | Advisory 36 | Х                           | Х   |

#### Table 3 Silicon Revision Updates (Part 2 of 2)

|                                                                                                                                                                         |               | Applies To Si | licon Revisior |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|----------------|

| Silicon Update Advisory                                                                                                                                                 | See           | 1.0           | 2.0            |

| False DDR3 Write ECC Error Reported Under Certain Conditions                                                                                                            | Advisory 37   | Х             | Х              |

| AIF2 GSM Compressed Mode and Multi-mode Issue                                                                                                                           | Usage Note 1  | Х             |                |

| AIF2 Protocol Encoder Registers Usage Note                                                                                                                              | Usage Note 2  | Х             |                |

| TAC DL TPC Timing Usage Note                                                                                                                                            | Usage Note 3  | Х             | Х              |

| Packet DMA Clock-Gating for AIF2 and Packet Accelerator Sub-system Usage Note                                                                                           | Usage Note 4  | Х             | Х              |

| VCP2 Back-to-Back Debug Read Usage Note                                                                                                                                 | Usage Note 5  | Х             | Х              |

| DDR3 ZQ Calibration Usage Note                                                                                                                                          | Usage Note 6  | Х             | Х              |

| I <sup>2</sup> C Bus Hang After Master Reset Usage Note                                                                                                                 | Usage Note 7  | Х             | Х              |

| MPU Read Permissions for Queue Manager Sub-system Usage Note                                                                                                            | Usage Note 8  | Х             | Х              |

| Queue Proxy Access Usage Note                                                                                                                                           | Usage Note 9  | Х             | Х              |

| TAC E-AGCH Diversity Mode Usage Note                                                                                                                                    | Usage Note 10 | Х             | Х              |

| Minimizing Main PLL Jitter Usage Note                                                                                                                                   | Usage Note 11 | Х             | Х              |

| DDR3 Performance Limited to 1333MT/s Usage Note                                                                                                                         | Usage Note 12 | Х             | Х              |

| AIF2 LTE 3Mhz and 1.4Mhz Support Usage Note                                                                                                                             | Usage Note 13 | Х             | Х              |

| PCIe Bar5 Windows Size Configuration in Boot ROM Usage Note                                                                                                             | Usage Note 14 | Х             |                |

| Sticky Bits in PCIe MMRs Usage Note                                                                                                                                     | Usage Note 15 | Х             | Х              |

| The Clock Input to NETCP Usage Note                                                                                                                                     | Usage Note 16 | Х             | Х              |

| Packet DMA Does Not Update RX PS Region Location Bit Usage Note                                                                                                         | Usage Note 17 | Х             | Х              |

| Current Flow Between VDDT and VDDR Rails During Power Sequencing of DSP Usage Note                                                                                      | Usage Note 18 | Х             | Х              |

| CAS Write Latency (CWL) at Low Speed Bins in DDR3 Multi-rank Configuration Usage Note                                                                                   | Usage Note 19 | Х             | Х              |

| IDMA1 Performance Limitation Usage Note                                                                                                                                 | Usage Note 20 | Х             |                |

| POR and RESETFULL Sequence Usage Note                                                                                                                                   | Usage Note 21 | Х             | Х              |

| Revised PLL Programming Sequence Usage Note                                                                                                                             | Usage Note 22 | Х             | Х              |

| Core Wake Up on RESET Usage Note                                                                                                                                        | Usage Note 23 |               | Х              |

| BCP RX BSS Port Aliasing Usage Note                                                                                                                                     | Usage Note 24 | Х             |                |

| BSDL Testing Support Usage Note                                                                                                                                         | Usage Note 25 | Х             | Х              |

| AIF2 CPRI FastC&M Restrictions and Usage Note                                                                                                                           | Usage Note 26 | Х             | Х              |

| Initial Voltage Level Setting of CVDD Rail Power Supplies Usage Note                                                                                                    | Usage Note 27 | Х             | Х              |

| DDR3 Class of Service Feature Can Cause Higher Than Expected Latency Usage Note                                                                                         | Usage Note 28 | Х             | Х              |

| Incorrect Output from TAC for Certain Channels When Configuring TAC_Gn_DATA_FETCH and TAC_Gn_HEAD_FETCH Registers with Values Having a Difference of 8 or 16 Usage Note | Usage Note 29 | Х             | Х              |

| End of Table 3                                                                                                                                                          |               |               |                |

#### Advisory 1 SRIO Packet Forwarding Issue

Revision(s) Affected: 1

1.0

**Details:**

When a high volume of SRIO packets with varying priorities are arriving at a device and are being forwarded on to another device, there is a possibility that the local SRIO module will lockup and stop processing incoming packets. The logic in the SRIO module places all packets to be forwarded in the same internal queue, allowing the possibility that a high volume of lower priority packets may block a higher priority packet and cause all packet processing to stop.

Workaround:

Pace the packet forwarded traffic so that congestion is avoided and make all packet forwarded traffic the same priority. This priority should be higher than the other incoming traffic destined for the local device.

#### **Advisory 2**

#### SRIO Messaging in Highly Oversubscribed System Issue

Revision(s) Affected:

1.0

**Details:**

When the SRIO message-passing mode is used in a highly oversubscribed system, it is possible for the number of available TX contexts to decrease over time and eventually cause the module to stop transmitting TX packets. An oversubscribed system is one where the number of RXU contexts required in any of the devices tends to exceed the maximum number of RXU contexts in that device. There are 16 RXU contexts per device.

There are two scenarios that can cause the failure. In the first, a retry that happens at nearly the same time as a DONE response can trigger an error in the internal logic that causes a TX context to become unusable. In the second, an error/timeout condition can cause a TX context to be incorrectly cleared twice, making it unusable. In either case, all TX contexts may eventually become unavailable and cause the SRIO module to stop transmitting TX packets.

To reduce the possibility of a system being oversubscribed, there should be at least one RXU context in a receiving device for every TXU in the other devices that may send a message to the receiving device. If any of the TXUs are using Type 11 messages, they should be allocated 1.25 RXU contexts in the receiving device due to possible delays in the message responses that may cause slightly more RXU contexts to be used in the receiving device.

Workaround:

None.

### Advisory 3 SRIO Direct I/O NREAD Data Corruption Issue

Revision(s) Affected: 1.0

Details: When SRIO direct I/O traffic in a system causes error conditions like timeouts or error

responses to be generated, it is possible that an error in the SRIO module's internal logic will cause NREAD commands to return their read data to an incorrect address, thus potentially causing data corruption in the system. The issue occurs only when

multiple LSUs are in use.

Workaround 1: Limit the size of all NREAD transactions to 256 bytes so they fit in a single SRIO

message. This will avoid the internal error in the SRIO module that causes the issue.

Workaround 2: Use only one LSU within the system. This will prevent the corruption of LSU data used

to return the NREAD payload to the correct address.

#### **Advisory 4**

#### **SRIO Reset Isolation Not Functional Issue**

Revision(s) Affected:

1.0

**Details:**

The SRIO module has the capability via reset isolation to continue forwarding SRIO packets intended for other devices while the rest of the local device containing the SRIO module is in reset. However, the SRIO reset isolation feature is available to a limited extent.

If the SRIO reset isolation feature is activated when any SRIO traffic is present, part of the logic in the SRIO module may not properly enter the reset isolation state. This may cause potential instability in the system when the SRIO block comes out of reset isolation.

Workaround:

A workaround for the issue is to perform a controlled reset for the device where all SRIO traffic going to and from the device (including forwarded traffic) is stopped before issuing the device reset. This will allow the SRIO module to enter reset isolation mode correctly.

#### **Advisory 5**

#### SRIO Register Aliasing Issue

Revision(s) Affected:

1.0

**Details:**

Due to an error in a portion of the address decoding logic in the SRIO module, writes to SRIO MAC registers with an address offset in the range of 1B400h to 1B9FCh will cause the same data to also be written to the SRIO RXU mapping register with an address offset in the range of 00400h to 009FCh and whose address has the same lowest 12 bits. This issue can potentially make the RXU mapping registers have random values that might permit spurious messages to enter a mailbox or not permit valid messages to enter a mailbox.

Workaround:

The MAC registers affected should be initialized before initializing the RXU registers, so that after all the initialization is done, the RXU registers still have the correct value. These affected MAC registers should be written only during initialization. If they are written again later, they will corrupt the corresponding RXU registers.

There are some SRIO MAC registers that may need to be written after initialization for normal operation. They are listed in the two following tables, along with their corresponding RXU mapping register. To allow these MAC registers to be written after initialization, the corresponding RXU mapping entries cannot be used by the application. This means that the affected RXU mapping registers cannot be used for normal operation and should be avoided by the application software. The Type 9 RXU mapping registers affected are RXU\_TYPE9\_MAP{45, 47, 49, 50, 52}. The Type 11 RXU mapping registers affected are RXU\_MAP{01, 12, 22}.

The RXU mapping registers listed in Table 4 should be disabled during initialization by writing a value of 11b to the tt field in the RXU\_MAPxx\_H or RXU\_TYPE9\_MAPxx\_1 register for that RXU mapping entry. The base address of the SRIO block must be added to the register offsets given in the table to obtain the full address of each register.

Table 4 Affected SRIO MAC Registers That May Need to Be Written After Initialization

| MAC Register Offset | MAC Register Name | RXU Register Offset | RXU Register Name |

|---------------------|-------------------|---------------------|-------------------|

| 1B490h              | TLM_SP2_STATUS    | 00490h              | RXU_MAP12_L       |

| 1B510h              | TLM_SP3_STATUS    | 00510h              | RXU_MAP22_QID     |

| 1B924h              | EM_PW_EN          | 00924h              | RXU_TYPE9_MAP45_2 |

| 1B934h              | EM_DEV_PW_EN      | 00934h              | RXU_TYPE9_MAP47_0 |

| 1B93Ch              | EM_MECS_STAT      | 0093Ch              | RXU_TYPE9_MAP47_2 |

| 1B94Ch              | EM_MECS_REQ       | 0094Ch              | RXU_TYPE9_MAP49_0 |

| 1B960h              | EM_RST_PORT_STAT  | 00960h              | RXU_TYPE9_MAP50_2 |

| 1B970h              | EM_RST_PW_EN      | 00970h              | RXU_TYPE9_MAP52_0 |

The two MAC registers in Table 5 may also need to be written after initialization, but because they end up writing data to the corresponding RXU\_MAPxx\_H or RXU\_TYPE9\_MAPxx\_1 register directly, they require special handling. The two RXU mapping registers listed should still be disabled during initialization like the other registers above.

Table 5 Affected SRIO MAC Registers That May Need to Be Written After Initialization and Require Special Handling

| MAC Register Offset | MAC Register Name | RXU Register Offset | RXU Register Name |

|---------------------|-------------------|---------------------|-------------------|

| 1B410h              | TLM_SP1_STATUS    | 00410h              | RXU_MAP01_H       |

| 1B950h              | EM_MECS_PORT_STAT | 00950h              | RXU_TYPE9_MAP49_1 |

However, in order to make sure they stay disabled, the two reserved bits in the MAC register that match the bit indices of the **tt** field in the corresponding RXU mapping register must be set to a value of **11b** whenever the MAC register is written. For example, bits [14:13] of the TLM\_SP1\_STATUS register must be written with a value of 11b because those bits match the tt field location in the RXU\_MAP01\_H register. Also, bits [14:13] of the EM\_MECS\_PORT\_STAT register must be written with a value of 11b because those bits match the tt field location in the RXU\_TYPE9\_MAP49\_1 register. The base address of the SRIO block must be added to the register offsets given in the table to obtain the full address of each register.

#### **Advisory 6**

# Potential L2 Cache Corruption During Block Coherence Operations Issue

Revision(s) Affected:

1.0

#### **Details:**

A potential L2 cache corruption issue during block coherence operations has been identified. Under a specific set of circumstances, L1D or L2 block coherence operations can cause L2 cache corruption. The problem arises when the following four actions happen back-to-back in the same L2 set:

- 1. L1D write miss

- 2. Writeback or invalidate or writeback-with-invalidate due to block coherence operations

- 3. Write allocate for some address

- 4. Read or write allocate for some address

This issue applies to all the block coherence operations listed below:

- L1D writeback

- L1D invalidate

- L1D writeback with invalidate

- L2 writeback

- L2 invalidate

- L2 writeback with invalidate

#### Workaround:

The workaround requires that the memory system be idle during the block coherence operations. Hence programs must wait for block coherence operations to complete before continuing. This applies to L1D and L2 memory block coherence operations. To issue a block coherence operation follow the sequence below.

- 1. Disable interrupts.

- 2. Write the starting address to the corresponding BAR register.

- 3. Write the word count to the corresponding WC register.

- 4. Wait for completion by one of the following methods:

- a. Issue an MFENCE instruction (preferred).

- b. Poll the WC register until the word count field reads as 0.

- 5. Perform 16 NOPs

- 6. Restore interrupts.

For further information about the cache control registers (BAR and WC) see the *TMS320C66x DSP CorePac User Guide* (SPRUGW0). The MFENCE instruction is new to the C66x DSP. It stalls the DSP until all outstanding memory operations complete. For further information about the MFENCE instruction, see the *C66x DSP and Instruction Set Reference Guide* (SPRUGH7).

#### Advisory 7 Queue Manager External Linking RAM Location Issue

Revision(s) Affected: 1.0, 2.0

**Details:** When the Queue Manager is setup to use an external linking RAM and the external

linking RAM is placed in the same memory endpoint as the packet descriptors or data buffers, then the Queue Manager may encounter a stall from which it cannot recover.

The different memory endpoints are L2RAM, MSMC SRAM, and DDR3.

**Workaround:** The Queue Manager's external linking RAM must be placed in a different memory

endpoint from the packet descriptors or data buffers. As an example, if the external linking RAM is placed in MSMC SRAM, then the packet descriptors and data buffers must be placed in L2RAM and/or DDR3. Note that the packet descriptors and data

buffers do not have to be placed in the same memory endpoints.

#### **Advisory 8**

# AIF2 AIF\_TX\_MONO\_MODE Not Compatible With Other Navigator Modules Issue

Revision(s) Affected:

1.0

Details:

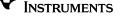

When the AIF2 is used in Packet DMA mode, there is an optional setting that can be enabled for the AIF2 Packet DMA called AIF\_TX\_MONO\_MODE. This special mode enables an internal optimization in the AIF2 that requires the use of a specific format of monolithic packet that has a 16-byte header immediately followed by data. This special mode is described in more detail in the *KeyStone Architecture Antenna Interface 2 (AIF2)* user guide (literature number SPRUGV7), *KeyStone Architecture Multicore Navigator* user guide (literature number SPRUGR9), and *Connecting AIF2 to FFTC Guide for KeyStone Devices* application report (literature number SPRABF3). One additional requirement is that the TX packets sent to the AIF2 must be sent with a descriptor size field (found in the lowest 4 bits of the value written when pushing a descriptor onto a queue) that is set to 64 bytes.

It is possible for other Navigator-compliant modules (such as FFTC, SRIO, and the Packet Accelerator) to send output packets directly to the AIF2 without any DSP intervention. However, when the monolithic packet format described above is used, the Packet DMA in the module sending the data uses a descriptor size field of 16 bytes. This means that the special AIF\_TX\_MONO\_MODE of the AIF2 Packet DMA cannot be used for AIF2 TX queues that are receiving packets directly from any of the Navigator-compliant modules.

Workaround:

Make sure the AIF\_TX\_MONO\_MODE setting (bit 24 in the TX Channel N Global Configuration Register B in the AIF2 Packet DMA, see the Navigator user guide for more details) is set to *Normal Monolithic Mode* (value = 0) for each of the AIF2 TX queues that are expected to receive packets directly from any of the Navigator-compliant modules.

www.ti.cor

#### Advisory 9 HyperLink Temporary Blocking Issue

Revision(s) Affected: 1.0, 2.0

**Details:**

A temporary blocking condition can occur on HyperLink on a Keystone I local (slave) device while returning high read activity initiated by a remote device (master.) If the read accesses are sufficiently high from the remote devices, the responses from the local device can keep the response path continuously busy. As a result, the local device that is returning the read data cannot issue any commands to the remote device since the read return data is highest priority. This is called arbitration head of line blocking (HOLB). Usually to initiate such high read activity, it is expected that the remote device is using master peripheral like EDMA issuing the reads, where the read burst size is 64 byte or higher, there needs to be multiple outstanding read requests and the read accesses are initiated to high speed memory like L2 or MSMC on the local device. Typically read accesses initiated to external memory (DDR3) will not see this issue, as the read responses are slower relative to on chip memory, additionally if the read accesses are initiated by CPU, it is not expected to cause HOLB, as the CPU waits for read response data prior to issuing subsequent read commands, which limits both the read activity and number of outstanding transactions.

Workaround 1: Use a push messaging model instead of pull, if possible.

Workaround 2: If a pull model is required, use CPU for reading instead of EDMA for local

(high speed/low latency) memories, so the schedule breaks when the return path is

continuously busy and HOLB is avoided.

| Advisory 10           | BCP DNT Support for HSUPA 10ms TTI With Spreading Factor Two Issue                                                                                          |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision(s) Affected: | 1.0                                                                                                                                                         |  |  |

| Details:              | The BCP DNT (de-interleaver) submodule does not support HSUPA data with a 10ms TTI using a spreading factor of two. Higher spreading factors are supported. |  |  |

| Workaround:           | None. The HSUPA de-interleaving operation should be performed by the DSP instead of the BCP for this scenario.                                              |  |  |

#### **Advisory 11**

#### **BCP DIO Reading From DDR Memory Issue**

Revision(s) Affected:

1.0, 2.0

**Details:**

The BCP Direct I/O (DIO) submodule and the DIO interface in the Rate De-matcher (RD) submodule only support start addresses that are multiples of 64 bytes when reading data from DDR memory. The addresses only need to be a multiple of 16 bytes when reading from L2RAM or MSMC SRAM.

Workaround:

The DIO interface used in the RD submodule is used for uplink HARQ data for LTE, HSUPA, and WiMAX. If DDR memory is used, the application software should always allocate the HARQ buffers so they start on 64-byte boundaries.

The stand-alone DIO submodule is used only for WCDMA Rel-99 downlink processing, where it performs the transport channel multiplexing. If DDR memory is used, the normal flow of writing and reading the data via DIO cannot be used since the Interleaver (INT) submodule will place the radio frames on 16-byte boundaries instead of 64-byte boundaries. Instead, the DIO can still write the data, but the transport channel multiplexing can be performed by using the BCP PacketDMA to read the data for the physical channel processing instead of the DIO. A set of TX descriptors can be setup so each one points to the current radio frame of each of the transport channels. These descriptors can then be linked together using the "Next Descriptor Pointer" field in each descriptor. When the head descriptor is pushed onto one of the BCP TX queues, the BCP PacketDMA will read the data for each of the linked descriptors, thus performing the transport channel multiplexing just like the DIO would have done.

#### **Advisory 12**

#### AIF2 CPRI LTE Ingress Antenna Carrier Packing Issue

Revision(s) Affected:

1.0

Details:

In order to fully support the CPRI protocol for LTE, the AIF2 module should allow flexible antenna carrier sample packing for the multiple antenna carrier use-case. For example, if the user sets the dual bit map (DBM) X value to 16 and transfers two antenna carriers, the user can choose any packing pattern for the CPRI basic frame. Several examples are shown as follows where AxC0 and AxC1 are antenna carriers 0 and 1, respectively.

- {Control, AxC0, AxC1, AxC0, AxC1}

- {Control, AxC0, AxC0, AxC1, AxC1, AxC0, AxC0, AxC1, AxC1, AxC0, AxC0, AxC1, AxC1, AxC0, AxC1, AxC1,

- {Control, AxC0, AxC0, AxC0, AxC1, AxC1, AxC1, AxC1, AxC0, AxC0, AxC0, AxC0, AxC1, AxC1,

- {Control, AxC0, AxC0, AxC0, AxC0, AxC0, AxC0, AxC0, AxC0, AxC1, AxC1,

- {Control, AxC0, AxC0, AxC0, AxC1, AxC1, AxC1, AxC1, AxC1, AxC0, AxC0, AxC0, AxC0, AxC0, AxC1, AxC1, AxC1}

However, the current AIF2 protocol decoder supports only one type of packing pattern for CPRI incoming (ingress) frames. It is the default packing order and allows only complete interleaving, where each sample from one antenna carrier is followed by a sample from the next antenna carrier (like AIF1 supported) and does not allow a DBM X value greater than the number of antenna carriers. The following is an example of this pattern for two antenna carriers (DBM X value is two).

• {Control, AxC0, AxC1, AxC0, AxC1}

#### Workaround:

The AIF2 ingress (output) packet should be configured as a super packet, which contains all the samples of an OFDM symbol for all the antenna carriers of the link. Because the antenna packing pattern is regular, the EDMA can be used to de-interleave the data without CPU intervention. Based on system bandwidth and link rate, the EDMA parameters can be set statically.

Upon reception of the super packet, a system event is generated to trigger the EDMA to deinterleave the data. The user can use an accumulator queue as the AIF2 output queue to trigger EDMA. Alternatively, an AT event can be used to trigger EDMA. Because the AT event is not tied with the availability of the super packet in system memory, enough headroom needs to be used to guarantee the availability of the super packet. When the EDMA de-interleaving is done, the EDMA can be used to clear the system event.

Here is an example for a system that uses a 20-MHz LTE bandwidth with 8× link rate. Figure 2 shows the antenna carrier packing used, where four antenna carriers are interleaved in clumps of eight samples each.

Figure 2 Antenna Carrier Packing

|         | Big Endian |          |          |          |  |

|---------|------------|----------|----------|----------|--|

|         |            |          |          |          |  |

| Address | 0          | 4        | 8        | С        |  |

| 0x00    | AxC0 s0    | AxC0 s1  | AxC0 s2  | AxC0 s3  |  |

| 0x10    | AxC0 s4    | AxC0 s5  | AxC0 s6  | AxC0 s7  |  |

| 0x20    | AxC1 s0    | AxC1 s1  | AxC1 s2  | AxC1 s3  |  |

| 0x30    | AxC1 s4    | AxC1 s5  | AxC1 s6  | AxC1 s7  |  |

| 0x40    | AxC2 s0    | AxC2 s1  | AxC2 s2  | AxC2 s3  |  |

| 0x50    | AxC2 s4    | AxC2 s5  | AxC2 s6  | AxC2 s7  |  |

| 0x60    | AxC3 s0    | AxC3 s1  | AxC3 s2  | AxC3 s3  |  |

| 0x70    | AxC3 s4    | AxC3 s5  | AxC3 s6  | AxC3 s7  |  |

| 0x80    | AxC0 s8    | AxC0 s9  | AxC0 s10 | AxC0 s11 |  |

| 0x90    | AxC0 s12   | AxC0 s13 | AxC0 s14 | AxC0 s15 |  |

| 0xA0    | AxC1 s8    | AxC1 s9  | AxC1 s10 | AxC1 s11 |  |

| 0xB0    | AxC1 s12   | AxC1 s13 | AxC1 s14 | AxC1 s15 |  |

|         |            |          |          |          |  |

In this case, a set of PaRAM entries are linked together where each PaRAM entry is set up to de-interleave all the antenna carriers in a single OFDM symbol time. At least seven PaRAM entries are needed to be able to differentiate long cyclic prefix (CP) and short CP in the LTE normal CP case. Figure 3 shows examples of long CP and short CP PaRAM entries.

Figure 3 Long CP and Short CP PaRAM Entries

PaRAM for long CP

| OPT=(ABSYNC , ITCCHEN) |              |  |  |

|------------------------|--------------|--|--|

| SRC                    |              |  |  |

| BC NT=276              | ACNT=32      |  |  |

| DST                    |              |  |  |

| DSTBIDX =32            | SRCBIDX =128 |  |  |

| BCNTRLD=276            | LINK         |  |  |

| DSTCIDX=8832           | SR CCID X=32 |  |  |

| Rsvd                   | CCNT=4       |  |  |

PaRAM for short CP

| OPT=(ABSYNC,ITCCHEN) |             |  |  |

|----------------------|-------------|--|--|

| SRC                  |             |  |  |

| BCNT=274             | ACNT=32     |  |  |

| DST                  |             |  |  |

| DSTBIDX=32           | SRCBIDX=128 |  |  |

| BCNTRLD=274          | LINK        |  |  |

| DSTCIDX=8768         | SRCCIDX=32  |  |  |

| Rsvd                 | CCNT=4      |  |  |

Depending on the buffer management, more PaRAM entries may be needed to be statically configured to avoid CPU intervention. In the case of a ping-pong buffer, 14 PaRAM entries are needed. The PaRAMs are linked to each other based on symbol number. If the antenna carriers are set up differently, up to 14 \* num\_antenna\_carriers PaRAM entries could be required for a ping-pong buffer. De-interleaved buffers can be pre-linked with descriptors. When the de-interleaving is done, the EDMA can be used to push the descriptors to an FFTC TX queue for further processing.

Here are some additional notes on the workaround.

- Regular packets can still be used for egress (input) packets when using super packets on ingress (output).

- Special notes for TDD

- If all antenna carriers on the same link have the same TDD configuration, then the AIF2 TDD mode can be used to output only the super packet as needed.

- If antenna carriers on the same link have different TDD configuration, then AIF2 TDD mode cannot be used. The EDMA needs to be set up to de-interleave only the useful part.

- If the antenna carriers on the same link have different offsets, then the current workaround cannot be used.

- Additional internal memory is needed because of the EDMA de-interleaving.

- Internal memory is preferred because the de-interleaved data needs to be sent to FFTC for processing, which would have lower throughput if the input packet is in DDR.

- A symbol-based ping-pong buffer may be enough to serve as the de-interleaved buffer. For example, for one sector of a 20-MHz 4 RX antenna system, 71k bytes memory is needed.

www.ti.con

#### Advisory 13

#### DDR3 Excessive Refresh Issue

Revision(s) Affected:

1.0, 2.0

**Details:**

DDR3 JEDEC standard specifies that at any given time, a maximum of 16 refresh commands can be issued within a  $2 \times$  tREFI interval ( $2 \times 7.8 = 15.6 \,\mu$ s). Failing to meet this requirement could result in a high current draw and the possibility of DDR3 device failure. The DDR3 controller will violate the above requirement if the following actions occur:

- 1. The DDR3 memory is put in to self-refresh mode by setting the LP\_MODE field in the Power Management Control register to 0x2.

- 2. One or more read/write commands are sent by the DDR3 controller while the DDR3 memory is in self-refresh such that the memory exits self-refresh to execute commands.

- 3. After command execution is complete and there are no more commands to execute, the DDR3 controller is then idle for a certain number of DDR clock cycles before putting the external memory in self-refresh mode. The number of idle DDR clock cycles is defined by SR\_TIM value field in the Power Management Control register.

- 4. Because the DDR3 controller issues one refresh command on self-refresh entry and another refresh command on self-refresh exit, if this sequence repeats more than eight times within a 2 × tREFI interval, the DDR3 controller will issue more than 16 refresh commands in a 2 × tREFI interval and violate the JEDEC requirement.

Note if SR\_TIM value is greater than or equal to 0x9, the DDR3 controller does not violate the JEDEC requirement. This is because the DDR3 controller will wait for at least 4096 clock cycles of idle time before putting DDR3 memory into self-refresh mode. Therefore, the only possible way the above scenario could occur is by setting the LP\_MODE field to 0x2 to put the DDR3 memory in self-refresh mode with the SR\_TIM value field less than 0x9, and then sending periodic read/write commands.

Workaround:

When using LP\_MODE=0x2 to enter self-refresh mode, SR\_TIM needs to be programmed greater than or equal to 0x9. For further information about the Power Management Control register see the *KeyStone Architecture DDR3 Memory Controller User Guide* (literature number SPRUGV8).

#### Advisory 14 TAC P-CCPCH QPSK Symbol Data Mode with STTD Issue

Revision(s) Affected: 1.0, 2.0

Details: When processing P-CCPCH channels on the TAC (Transmit Accelerator) using QPSK

symbol data format mode with STTD enabled, the P-CCPCH channel output is incorrect. The QPSK+DTX symbol data format mode is not affected by this issue.

Workaround: To work around this issue, the QPSK+DTX symbol data format mode can be used for

P-CCPCH all of the time, or at least when STTD is enabled. As the P-CCPCH uses a spreading factor of 256, ten additional DTX 32-bit all-zero DTX words need to be interleaved by the application software to use the QPSK+DTX symbol data format.

#### Advisory 15

#### AIF2 GSM T1, T2, T3 Miscalculation Issue

Revision(s) Affected:

1.0

**Details:**

The GSM T1, T2, and T3 counters in the AIF2 timer are designed to increment by one every time the radio timer frame count increments by 1. However, this is not correct operation because the GSM uses 104 as a symbol number terminal count to make it align with the 60-ms Phy frame boundary, even though the original GSM frame has only13 symbols inside. As a result, the T counters have a much longer period between steps.

The GSM has a group of three timers that are incremented on a GSM frame-by-frame basis. They will be incremented every time the symbol (GSM slot) counter wraps around. These are the T1, T2, and T3 timers, and they are fixed as shown:

- T1 = modulo 2048

- T2 = modulo 26

- T3 = modulo 51

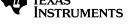

Figure 4 shows how T1, T2, and T3 counters operate with the radio timer.

Figure 4 Radio Timer with GSM Time

However, one architecture problem was found while running the GSM system level test. The radio timer frame counter is programmed to count 60 ms, which is 13 GSM frame lengths. This configuration had to be done, because 60 ms is the first n  $\times$  10 ms frame boundary which aligns to the OBSAI/CPRI PHY frame boundary (10 ms). In this case, the radio timer should have 104 as a symbol terminal count because there are a total of 104 GSM time slots within 60 ms. In this case, the radio timer should have 104 as a symbol terminal count because there are 104 GSM time slots within 60 ms. With a 104 symbol terminal count, there are not enough calculations to show the correct values on the T1, T2, and T3 counters.

To fix this problem, it is necessary to add a mod 8 counter that increases its value every radio symbol time. When the mod 8 count wraps around, the T1, T2, and T3 counters are incremented by 1. As a safety feature, the mod 8 counter resets to 0 every time the radio frame count is incremented by 1. The T1, T2, and T3 counters reset only when the radio timer is fully re-synchronized. Figure 5 shows how the current GSM T counter design should be changed.

▶ loads Frame counter, clears symbol and clock counters, clears lut index clears T1,T2,T3 SWmmr frame RP1 radio frame SW mmr frame RP1 radio frame Ld frame Clock counter 19bit Frame counter Symbol counter 8bit symbol TC Frame TC mod 8 (fixed count) Clock TC lut 19 bits wide Χ lut index 128 locations address count 7bit lut index TC TC\_T2 count SW readable T2 mod 26 count T3 mod 51 count TC T2 & TC T3 T1 mod 2048

Figure 5 GSM T Counter Design Change

Workaround:

An additional AT event can be assigned to generate an event every GSM slot time. The ISR may check mod 8 count per visit and the T2 and T3 count array can be updated manually when the mod 8 count wraps around. TC\_T1 count can be calculated by a bitwise AND operation between TC\_T2 and TC\_T3.

www.ti.con

#### Advisory 16

#### AIF2 Multiple DBMR Operation Issue

Revision(s) Affected:

1.0

**Details:**

The antenna streams for a link can be separated into multiple rules (modulo and dual bitmap rule (DBMR)). Each rule uses multiple entries (AxC or packet channels) in its lookup table. The lookup table index was reset to 0 after each visit for all but the last rule when users use multiple numbers of rules together within one link.

For OBSAI (Open Base Station Architecture Initiative), the protocol encoder supports two kinds of transmission rules—modulo and DBRM—to interleave multiple channel data into one link. There are 64 modulo rules and 64 DBMR rules. When using both rules together they share the same index numbers. If the user sets only one modulo rule and DBMR for a specific link, it does not cause any lookup table confusion and perfectly supports multiple numbers of entries (channels) with the correct interleaving. However, if the user assigns multiple numbers of rules with multiple entries (channels), the operation does not work correctly. The lookup table index always resets to 0 after visiting the rules except for the last rule pair.

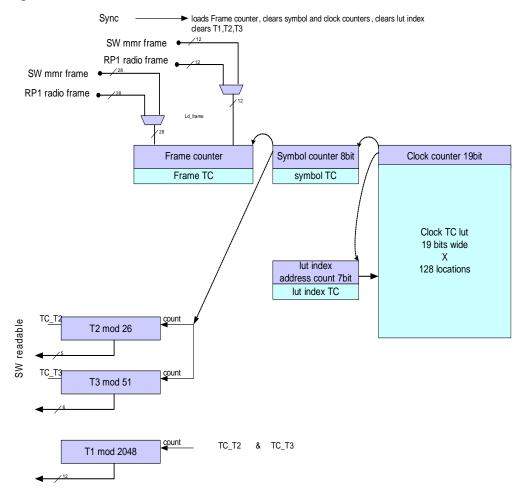

Figure 6 shows the expected framing order for a modulo and DBMR pair and the actual framing order using the current hardware.

Figure 6 OBSAI Message Frame Ordering for Two Rule Pairs

Expected framing order: **AxC0**, AxC1, **AxC2**, AxC3, **AxC4**, AxC5, **AxC6**, AxC7

Framing order of current hardware **AxC0**, AxC1, **AxC0**, AxC3, **AxC0**, AxC5, **AxC0**, AxC7

This is a very simple example of a two rule pair case. In the case of rule 0, only AxC0, which is in entry 0, is inserted into the frame and AxC2, AxC4, AxC6 data is ignored. The entry index works perfectly only with the last rule.

Workaround:

None.

#### **Advisory 17**

#### **BCP CRC Failure Issue**

Revision(s) Affected:

1.0

**Details:**

The Bitrate Coprocessor (BCP) Cyclic Redundancy Check (CRC) sub-module sometimes fails to perform the CRC operation. On pushing packets to the BCP transmit queue, the PktDMA reads the input data and sends it to the CRC sub-module through the TM submodule. Sometimes the CRC sub-module fails to process the data and Rx destination queue does not get the processed packet.

The End-of-Packet signal in the CRC which is responsible for controlling data processing in the CRC sub-module is not initialized correctly. The CRC sub-module state machine thinks that it is currently processing a packet and therefore it will not accept a new incoming packet. Incoming packets are blocked on entering the CRC sub-module and BCP will not make progress in processing the packets.

The data logger does not show the output packet count incrementing for the CRC submodule. The behavior is random and it is based on the initialized value of the End-of-Packet signal at the time of reset. So it might happen that sometimes it works and sometimes it does not work.

Workaround:

The workaround is to implement the CRC operation in the software and bypass the CRC sub-module when using the BCP.

Software for implementing CRC operation in the application is available. Please contact local field support team.

#### Performance Impact Due to Software Workaround:

The computational overhead of a software-based CRC calculation for DL (Downlink) processing is estimated for LTE 20MHz to be around 2% @1GHz and 1.7% @1.2GHz on a single core and the chip level impact is less than 0.5% of the overall throughput.

The similar impact for UL (Uplink) processing worst case impact seen for LTE 20MHz is  $\sim$ 1.7% @ 1GHz and  $\sim$ 1.4% @1.2GHz on one core and the chip level impact is less than 0.5% of the overall throughput.

www.ti.con

#### Advisory 18

#### AIF2 SerDes Comma Alignment Failure Issue

Revision(s) Affected:

1.0

Details:

Data corruption encountered on AIF2 lane0 to lane5 (any one or multiple lanes at a time) causes a loss of frame synchronization. The AIF2 SerDes incorporates a comma (K28) alignment mechanism to identify symbol boundaries in 8B10B-encoded data. Comma detection can be disabled after alignment has been achieved. Due to a circuit design issue, disabling the comma detection can corrupt the data alignment. If AIF2 RM (Receive Media Access Control) sd\_auto\_align\_en is enabled, RM disables comma detection after frame sync is achieved. Due to this issue, the data alignment is corrupted and AIF2, once again, goes out of frame sync.

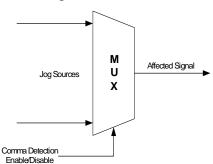

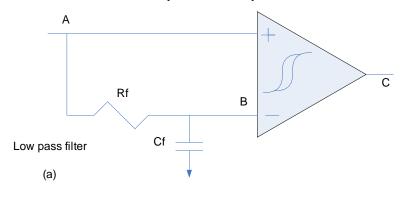

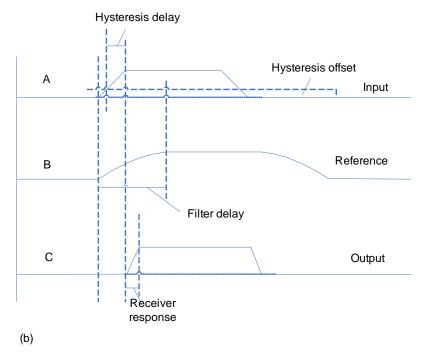

SerDes alignment is achieved by *jogging* one bit at a time until the required alignment is achieved. As an alternative to the comma alignment mechanism, jogs can be requested directly. As shown in Figure 7, the jog request source is selected by a mux, which is controlled by whether comma detection is enabled or disabled.

Figure 7 Affected Signal

The jog request (mux output), which is shown as Affected Signal in Figure 7, is fed to a synchronizer located elsewhere in the SerDes. This signal can glitch while disabling comma detection. Depending on the PVT and line frequency, this glitch can be misinterpreted as a spurious jog request, which can corrupt the alignment. PVT dependency is such that not all devices will exhibit the issue.

All the six lanes are affected with this issue. AIF2 has two SerDes modules inside. One module has lane0 to lane3 and the other has lane4 and lane5. The glitch is dependent on layout differences between these two macros so it is possible that only some of the six lanes will show this issue and some will not.

No other peripherals that are using similar SerDes are affected by this. SRIO does not disable the comma detection. HyperLink does not use the SerDes comma alignment.

All alignment is handled internal to HyperLink module. NetCP and PCIe have a different SerDes module than the one that is used in the AIF2 and it is not affected by this issue.

Workaround:

A software workaround is described below.

Keep the RM SD auto\_align\_en disabled and keep the SD ALIGN enabled. This can be done by setting the sd\_auto\_align\_en bit field of the RM\_LK\_CFG0 register to 0 for each link and by setting the ALIGN field of the SD\_RX\_R1\_CFG register to 01b for each link.

Table 6 and Table 7, show the RM Link Config and SD Rx Config register and bit-field snapshots from the *AIF2 User Guide*:

Table 6 RM Link Config Register Snapshot

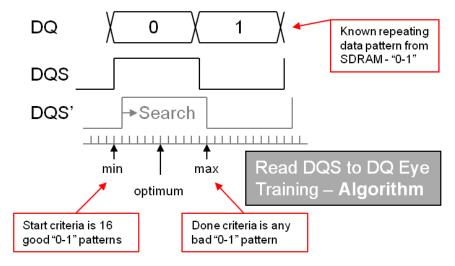

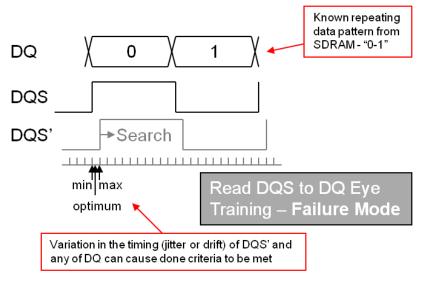

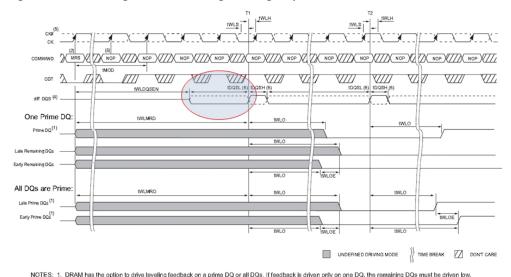

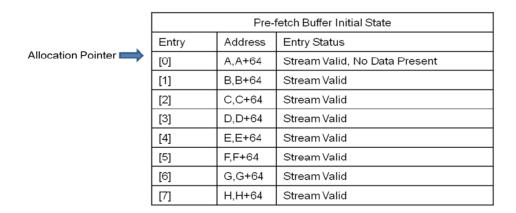

| Bits          | Field Name       | Туре       | Description                                                                                                                                                              |  |