## WHITE PAPER

Gaganjot Maur, Applications Engineer, Texas Instruments

# Efficient fixed- and floating-point code execution on the TMS320C674x core delivers faster code development and reduces system cost with improved performance

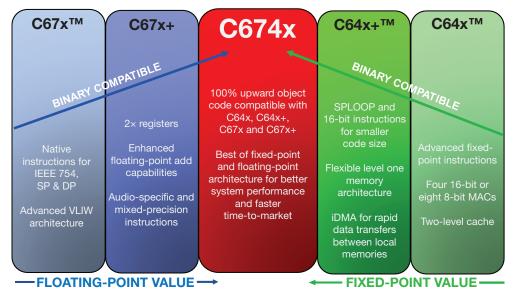

The TMS320C674x core is not a dual-core implementation. It is a single core that combines the capabilities of the floating-point TMS320C67x+ core and fixed-point TMS3320C64x+<sup>TM</sup> core. This means the C674x instruction set is a superset of the C64x+<sup>TM</sup> instruction set and C67x+ instruction set. On every instruction cycle, the C674x can either execute the advanced fixed-point instructions supported by the C64x+ core, the floating-point instructions supported by the C67x+ core, or both.

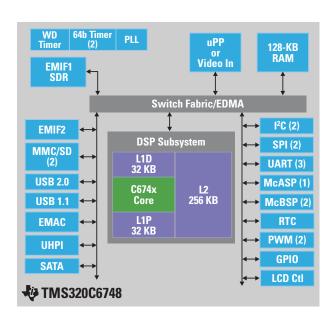

The first TI chips based on the C674x core (TMS320C6742, TMS320C6743, TMS320C6745, TMS320C6746, TMS320C6747 and TMS320C6748 DSPs, OMAP-L137 and OMAP-L138 processors) add a set of carefully selected peripherals to complement varying end applications. For example, the C6748 DSP has an integrated universal parallel port (uPP), Serial ATA (SATA), video interface, 10/100 Ethernet MAC (EMAC), USB 2.0/1.1 and UART for connectivity as well as a memory card (MMC/SD), NAND and USB for data storage. This results in a unique, highly-integrated platform that speeds software development by eliminating the need for additional external peripherals.

Figure 1 shows the C674x core and the peripherals integrated into the C6748 DSP.

Figure 1. TMS320C6748 DSP block diagram

## **Executive summary**

DSP chip design has followed two distinct paths – utilizing either fixed-point or floatingpoint instruction sets to create processors targeted at different applications and performance goals. Floating-point DSPs deliver high dynamic range, high precision and a simplified programming environment. Additionally, since a majority of PC-based development tools generate floating-point code, developers can easily migrate from PC-based development environments to DSP. Fixed-point devices, on the other hand, traditionally dominate markets and applications in which low power, low cost and a high degree of connectivity with peripherals are paramount. With the new TMS320C674x core from Texas Instruments (TI), that handles both fixed- and floating-point operations, designers now have access to a new breed of signal-processing platforms that reduce bill of materials (BOM) cost, facilitate faster time-to-market and deliver a unified software development environment. Processors based on the C674x core are upward code compatible with all TMS320C6000<sup>™</sup> fixed- and floating-point devices. The C674x core provides several cost- and time-saving features. It also provides features that boost performance. Key features are listed below:

- Native support for IEEE 754 single- and double-precision floating-point formats

- An advanced software pipeline loop (SPLOOP) buffer

- Enhanced system events handling including support of exceptions

- Improved cache coherence mechanism

- A two-level system of privileged program execution with supervisor and user mode

- An internal DMA controller

# Performance enhancements

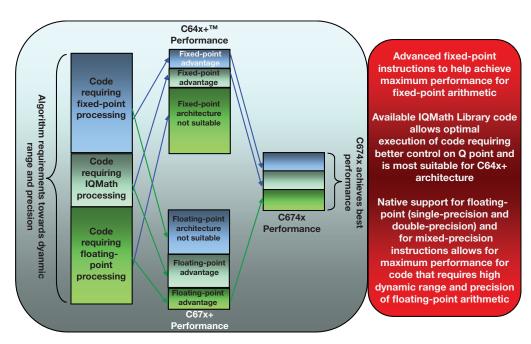

The C674x generation's ability to execute both fixed-point and floating-point math adds a new dimension to the capabilities available to the algorithm developer. By selectively using the advanced fixed-point instruction set and the floating-point instruction set, the developer can achieve significantly higher performance for their algorithm.

Availability of advanced fixed-point instruction set in combination with floating-point support enhances the quality and performance of key audio codecs. For example, there is a 20 to 30 percent improvement with the C674x core over C674x+ core for the Digital Theatre System-HD (DTS-HD) audio codec. These improvements free up processing bandwidth that can be used for innovation and differentiation for applications like set-top boxes, portable medical diagnostics, public safety radios, power protection systems and many more.

Figure 2.

To optimize floating-point performance, the C674x core implements native support for IEEE 754 single-precision and double-precision instructions. In addition to conforming to the IEEE standard, mixed-precision instructions result in highest-performance audio algorithms, which in turn deliver the highest-quality sound.

Fixed-point performance is significantly enhanced through the C674x instruction set, which includes support for the following operations per clock cycle: two  $32 \times 32$ -bit multiplies; four  $16 \times 16$ -bit multiplies or eight  $8 \times 8$ -bit multiplies. Additional instructions are included to support complex multiplies allowing up to eight 16-bit multiply/add/subtracts per clock cycle.

Memory utilization always plays a major role in achieving top performance metrics and architectural flexibility is a key feature for optimizing memory utilization. The C674x core implements a memory architecture in which the L1 or L2 memories can be configured as cache for flexibility and ease of development but can also be configured as RAM for more control and improved performance. The configuration can be changed dynamically thus providing additional flexibility.

Core enhancements result in performance improvements for core signal-processing kernels that are key to various applications, such as power-protection systems, software-defined radios and home theatre systems. For instance, with a single-precision floating-point complex-FFT kernel, there is a 20 percent performance improvement with the C674x core when compared to the C67x+ core.

#### Code size

Software pipelining is a technique that takes advantage of the eight execution units of the C674x CPU to schedule instructions from a loop so that multiple iterations of the loop execute in parallel. The C674x core includes a software pipeline buffer that implements the software pipelining in hardware.

The software pipeline loop (SPLOOP) feature offers several advantages. For example, employing software pipelining requires a prolog (the number of cycles "getting ready" for the loop) and epilog (the number of cycles spent "cleaning up" after the loop is completed). Previously, the prolog and epilog required additional code to be inserted. With hardware support, offered by SPLOOP, there is no need to explicitly code the prolog and epilog. As a result, code size is significantly reduced.

Two additional SPLOOP benefits are: (1) memory bandwidth and power requirements are reduced because instructions in the loop do not need to be fetched on each cycle and (2) the C674x core's SPLOOP implementation allows the kernel to be interrupted, which results in lower interrupt latency (non-SPLOOP kernels in most cases cannot be interrupted).

Code size is further reduced by adding support that replaces 32-bit instructions with 16-bit compact equivalents. This feature has been added without having a negative impact on either functionality or speed. Additionally, the code-generation tools automatically leverage the instruction packing feature of the C674x core to provide code size equivalence for eight instructions executed serially or in parallel. In addition to reducing code size, this feature speeds program fetches and reduces power consumption.

Figure 3.

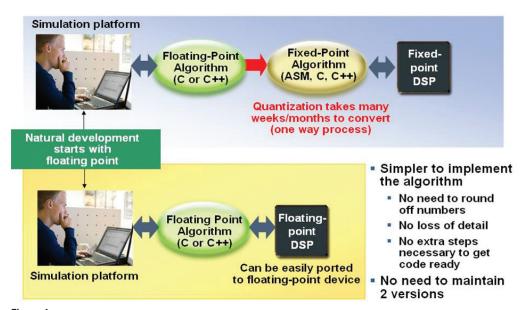

# Simplified code development

Typically, signal-processing algorithms are developed on host development platforms because they commonly support visual-programming interfaces. The generated code from these development platforms is typically using floating-point arithmetic but for cost and performance reasons, system developers are usually constrained to choose fixed-point DSPs when migrating to an embedded platform.

The downside of this practice is the significant effort required to modify floating-point code to fixed-point. The continuing cost of code maintenance for two platforms afterwards is also something designers would prefer to avoid. The C674x DSP's native support for industry standard floating-point formats – it supports IEEE 754 single-precision and double-precision floating-point instructions – makes the migration to an embedded platform virtually transparent to the algorithm designer.

Figure 4.

## Faster time-to-market

Cache coherence, privileged program execution, an internal DMA (iDMA) controller and support for non-aligned memory access all contribute to making it easier for designers to develop code for the C674x platform.

- The C674x core supports two-level cache memory architecture. Cache coherence feature increases system performance by automatically synchronizing the C674x core's internal cache and level two memory.

- Privileged program execution allows the ability to design more robust and safe end equipments, particularly in conjunction with exceptions support. Also, it allows the system to implement features such as memory protection. These features not only help make the system robust, they also reduce the development time by aiding in the debug of complex system issues during development phase.

- When something unexpected happens, the last thing a designer wants the chip to do is to end up in a state from which it can't recover. By implementing exceptions handling in its CPU, the C674x DSP provides recovery mechanisms. Support consists of error detection and subsequent redirection to errorhandling routines, thus saving the designer time and resources to debug the issue. Support includes exceptions generated inside or outside the CPU.

- The internal DMA (iDMA) controller is a dedicated DMA engine for the CPU. The primary advantage of iDMA is that it handles data transfers between the L2 RAM and the faster L1D data memory without requiring CPU intervention. Since it operates in the background of CPU processing, latency is reduced and stalls due to slow cache response are minimized. The iDMA controller also provides a fast means of paging data sections to any memory-mapped RAM local to the CPU.

- Efficient access of data is an important factor in optimizing processor performance. Access of aligned 32-bit (word) and 64-bit (double word) data in most processors is efficient. However, performance is degraded for non-aligned data array accesses because unaligned accesses require multiple load and store operations. The C674x core has added support for these non-aligned data accesses. In addition to restoring performance, this feature also reduces code size because multiple load/store instructions are no longer required.

## **Conclusion**

Until now, system designers have had to choose between the benefits of floating-point and fixed-point architectures. Fixed-point devices were typically less expensive and consumed less power but did not offer the mathematical precision and dynamic range of floating-point devices.

The increased usage of PC-based algorithm development tools complicated the choice. Since these tools develop floating-point algorithms, system developers had to convert them to fixed point to run on fixed-point DSPs and maintain two versions of the code through product generations and updates.

The C674x core resolves these long-standing design issues by supporting both fixed- and floating-point operations. It ushers in a new breed of DSPs that combine high precision, dynamic range and ease-of-use with low-power, cost-efficient connectivity.

Important Notice: The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to Tl's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about Tl products and services before placing orders. Tl assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute Tl's approval, warranty or endorsement thereof.

C64x+, TMS320C64x+ and TMS320C6000 are trademarks of Texas Instruments Incorporated. All other trademarks are the property of their respective owners.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com DLP® Products Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Military Interface www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated