# TMS320F2837x, TMS320F2838x, TMS320F28P65x Migration to TMS320F29H85x

#### **ABSTRACT**

This migration guide describes the hardware and software differences to consider when moving between F2837x, F2838x, F28P65x and F29H85x C2000™ MCUs, where F28P65x is used as the example of a Gen 3 device in individual sections. While the CPU system from C28x to C29x has improved, the block diagram is not shown between the two MCUs as a visual representation on what blocks are similar or different. As there will be huge differences, there is a section sharing the improvement on the architecture in C29x. It also highlights the features that are unique between the devices for all available packages in a device comparison table. To facilitate application and hardware migration between Gen3 and Gen4 devices, the new PCB hardware section provides guidance on how to proceed with the new design for F29H85x. As there are many new features being offered on this device, there are sections showing the new changes that have been made and what value each feature adds. This serves as a reference for hardware design and signal routing when considering a move between the devices.

# **Table of Contents**

| 1 Feature Differences Between F2837x, F2838x, F28P65x and F29H85x      |                  |

|------------------------------------------------------------------------|------------------|

| 1.1 F28x to F29x Feature Change Overview                               | 3                |

| 2 C29x Architecture                                                    | 7                |

| 2.1 C29x Architecture Overview                                         | 7                |

| 2.2 C28x vs C29x Architecture Overview                                 | 11               |

| 3 PCB Design Consideration                                             | 12               |

| 3.1 VSSOSC                                                             |                  |

| 3.2 JTAG                                                               |                  |

| 3.3 VREF                                                               | 12               |

| 4 Feature Differences for System Consideration                         | 13               |

| 4.1 New Features in F29H85x                                            |                  |

| 4.2 Communication Module Changes                                       | 23               |

| 4.3 Control Module Changes                                             | 24               |

| 4.4 Analog Module Differences                                          | 25               |

| 4.5 Power Management                                                   | 26               |

| 4.6 Memory Module Changes                                              | 27               |

| 4.7 GPIO Multiplexing Changes                                          | <mark>2</mark> 9 |

| 5 Software Development with F29H85x                                    |                  |

| 5.1 Migration Report Generation Tool                                   | 29               |

| 6 References                                                           | 30               |

| List of Figures                                                        |                  |

| Figure 1-1. F29H85x Block Diagram                                      | 3                |

| Figure 2-1. PIE Architecture                                           |                  |

| Figure 2-2. PIPE Architecture                                          | 8                |

| Figure 2-3. SSU-CPU Coupled Interface                                  | 9                |

| Figure 2-4. RTDMA Block Diagram                                        | 10               |

| Figure 3-1. JTAG Connection Diagram (Connecting to 14-Pin JTAG Header) | 12               |

| Figure 4-1. DLT Block Diagram                                          |                  |

| Figure 4-2. SENT Block Diagram                                         |                  |

| Figure 4-3. WADI Block Diagram                                         |                  |

| Figure 4-4. F28P65x ePWM X-BAR Architecture                            | 18               |

|                                                                        |                  |

|           | INSTRUMEN |

|-----------|-----------|

| rademarks | www.ti.co |

| Figure 4-5. F29H85x ePWM X-BAR Architecture          | 18 |

|------------------------------------------------------|----|

| Figure 4-6. ESM-SS Block Diagram                     |    |

| Figure 4-7. Error Aggregator Block Diagram           |    |

| Figure 4-8. Device High-Level Block Diagram          |    |

|                                                      |    |

| List of Tables                                       |    |

| Table 1-1. IP Differences                            | 4  |

| Table 1-2. 100-pin IO and Analog Channel Counts      | 5  |

| Table 1-3. 176-pin IO and Analog Channel Counts      | 6  |

| Table 1-4. 256-pin IO and Analog Channel Counts      | 6  |

| Table 2-1. C29 Major Feature                         | 7  |

| Table 2-2. PIE vs PIPE                               | 9  |

| Table 2-3. DMA vs RTDMA                              | 10 |

| Table 2-4. Lockstep Module CPU Configuration         | 11 |

| Table 2-5. C29x Improvement                          | 11 |

| Table 4-1. Main Changes in F29H85x                   | 13 |

| Table 4-2. Bootrom Comparison                        |    |

| Table 4-3. List of Cryptographic Accelerator Engines | 22 |

| Table 4-4. Communication Module Instances            | 23 |

| Table 4-5. Control Module Differences                | 24 |

| Table 4-6. Analog Module Differences                 | 25 |

| Table 4-7. RAM and Flash Memory Changes              |    |

| Table 4-8. Memory Configuration                      | 28 |

| Table 4-9. Flash Mode for F29H85x                    | 28 |

| Table 4-10. Memory Module Differences                | 29 |

# **Trademarks**

C2000<sup>™</sup> and Code Composer Studio<sup>™</sup> are trademarks of Texas Instruments. All trademarks are the property of their respective owners.

# 1 Feature Differences Between F2837x, F2838x, F28P65x and F29H85x

Drop-in pin compatibility is not supported when migrating from Gen 3 devices to F29H85x. Users are expected to map the pin resources accordingly when migrating to F29H85x.

#### Note

This comparison guide focuses on the superset devices: F2837x, F2838x, F28P65x and F29H85X as other part numbers in these product series have reduced feature support. For details specific to certain part numbers, see the device-specific data sheet.

# 1.1 F28x to F29x Feature Change Overview

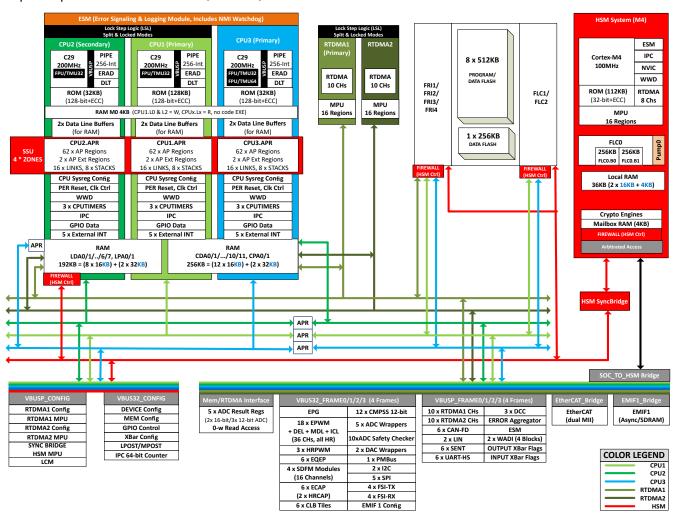

The Figure 1-1, shows the new CPU sub-system and associated peripherals. The feature comparison of the superset part numbers for F2837x, F2838x, F28P65x and F29H85x devices is shown in Table 1-1.

Figure 1-1. F29H85x Block Diagram

### Table 1-1, IP Differences

|                                      |                                | Table                  | 1-1. IP Differenc         | es                                                |                                               |

|--------------------------------------|--------------------------------|------------------------|---------------------------|---------------------------------------------------|-----------------------------------------------|

| F                                    | eature                         | F2837x                 | F2838x                    | F28P65x                                           | F29H85x                                       |

|                                      |                                | C20                    | 00 CPU Subsystem          |                                                   |                                               |

| CPU Type                             |                                | C28x                   | C28x                      | C28x                                              | C29x                                          |

| Number of CPU                        |                                | 2                      | 2                         | 2                                                 | 3                                             |

| CPU Frequency (                      | MHz)                           | 200                    | 200                       | 200                                               | 200                                           |

| 32-bit and 64-bit f<br>(FPU)         | Floating-Point Unit            | Yes                    | Yes                       | Yes                                               | Yes (CPU1/2 - 32-bit, CPU3 - 32-bit & 64-bit) |

| CPU Lockstep                         |                                | No                     | No                        | Yes (Lockstep<br>between CPU2 and<br>Shadow-CPU2) | Yes (CPU1/CPU2 are Lockste capable)           |

|                                      |                                | Re                     | lative Performance        |                                                   |                                               |

| Signal Chain Perf                    | ormance                        |                        | -                         |                                                   | 3x faster                                     |

| FFT Performance                      |                                |                        | -                         |                                                   | 5x faster                                     |

| Interrupt Respons                    | se                             |                        | -                         |                                                   | 4x faster                                     |

| General Purpose                      | Code                           |                        | -                         |                                                   | 3x faster                                     |

|                                      |                                | ı                      | Memory                    |                                                   | I                                             |

| Flash                                |                                | 1MB                    | 1MB                       | 1.28MB                                            | 4MB + 256KB (Data Bank)                       |

| RAM                                  |                                | 204KB                  | 216KB                     | 248KB                                             | 452KB                                         |

|                                      |                                | l                      | System                    | 1                                                 | 1                                             |

| CLA                                  |                                | 2                      | 2                         | 1 (CPU1 only)                                     | No                                            |

| External Memory                      | Interface (FMIF)               | 2                      | 2                         | 1                                                 | 1                                             |

| DMA                                  | ,                              | 1 per CPU (6 channels) | 1 per CPU (6<br>channels) | 1 per CPU (6<br>channels)                         | 2 - Real-time DMA (10 channels each)          |

| Data Logger and Trace (DLT)          |                                | No.                    | No                        | No                                                | Yes                                           |

| Embedded Pattern Generator (EPG)     |                                | No                     | No                        | Yes                                               | Yes                                           |

| Enhanced Real-ti<br>Diagnostic (ERAD | me Analysis and                | No                     | Yes                       | 1 per CPU (Type 2)                                | 1 per CPU (Type 5)                            |

| CPU Timer                            | ·                              | 3 per CPU              | 3 per CPU                 | 3 per CPU                                         | 3 per CPU                                     |

|                                      |                                | Α                      | nalog Peripherals         | ·                                                 |                                               |

| ADC 16/12-bit                        | Number of ADCs                 | 4                      | 4                         | 3                                                 | 2                                             |

|                                      | 16-bit MSPS                    | 1.1                    | 1.1                       | 1.19                                              | 1.19                                          |

|                                      | 16-bit Conversion<br>Time (ns) | 915                    | 915                       | 840                                               | 840                                           |

|                                      | 12-bit MSPS                    | 3.5                    | 3.5                       | 3.92                                              | 3.92                                          |

|                                      | 12-bit Conversion<br>Time (ns) | 280                    | 280                       | 255                                               | 255                                           |

| ADC 12-bit                           | Number of ADCs                 | No                     | No                        | No                                                | 3                                             |

|                                      | MSPS                           | -                      | -                         | -                                                 | 3.92                                          |

|                                      | Conversion Time (ns)           | -                      | -                         | -                                                 | 255                                           |

| Temperature Sen                      |                                | 1                      | 1                         | 1                                                 | 1                                             |

| Buffered DAC - Ty                    |                                | 3                      | 3                         | 2                                                 | 2                                             |

| CMPSS - Type 6                       |                                | 8                      | 8                         | 11                                                | 12                                            |

|                                      |                                |                        | ontrol Peripherals        | • • •                                             | 1                                             |

|                                      | Total Modules                  | 6 - Type 0             | 7 - Type 2                | 7                                                 | 6                                             |

| eCAP - Type 3                        | HRCAP Capable                  | 0 - Type 0<br>0        | 2 (eCAP6, eCAP7)          | 2 (eCAP6, eCAP7)                                  | 2 (eCAP5, eCAP6)                              |

|                                      | Total Channels                 | 24 - Type 4            | 32 - Type 4               | 36                                                | 36                                            |

| ePWM - Type 5                        | HRPWM Capable                  | 24 - Type 4<br>16      | 32 - Type 4<br>16         | 36                                                | 36                                            |

|                                      | TINE VVIVI Capable             | 3                      | 3                         | 6                                                 | 6                                             |

| eQEP - Type 2                        |                                |                        |                           |                                                   |                                               |

**Table 1-1. IP Differences (continued)**

| Feature                                                  | F2837x       | F2838x              | F28P65x                      | F29H85x                         |

|----------------------------------------------------------|--------------|---------------------|------------------------------|---------------------------------|

|                                                          | F203/X       | F2030X              |                              |                                 |

| Sigma-Delta Filter Module (SDFM)<br>Channels - Type 2    | 8 - Type 0   | 8                   | 16 Channels (4 SDFM Modules) | 16 Channels (4 SDFM<br>Modules) |

|                                                          | Comm         | unication Periphera | als                          |                                 |

| Ethernet for Control Automation<br>Technology (EtherCAT) | No           | Yes                 | Yes                          | Yes                             |

| Controller Area Network (CAN) 2.0B - Type 0              | 2            | 2                   | 1                            | No                              |

| CAN with Flexible Data-Rate (CAN-FD) - Type 2            | 0            | 1                   | 2                            | 6                               |

| Fast Serial Interface (FSI) RX - Type 2                  | 0            | 8 - Type 1          | 4                            | 4                               |

| Fast Serial Interface (FSI) TX - Type 2                  | 0            | 2 - Type 1          | 2                            | 4                               |

| Inter-Integrated Circuit (I2C)                           | 2 (Type 0)   | 2 (Type 0)          | 2 (Type 1)                   | 2 (Type 2)                      |

| Local Interconnect Network (LIN) - Type                  | 0            | 0                   | 2                            | 2                               |

| Power Management Bus (PMBus) 1.1 - Type 0                | 0            | 1                   | 1                            | 1                               |

| High Speed UART (HS-UART) - Type 1                       | 0            | 1 (CM)              | 2                            | 6                               |

| Single Edge Nibble Transmission (SENT) - Type 1          | 0            | 0                   | No                           | 6                               |

| Serial Peripheral Interface (SPI) - Type 2               | 3            | 4                   | 4                            | 5                               |

| Serial Communications Interface (SCI) - Type 0           | 4            | 4                   | 2 - UART Compatible          | No                              |

| Universal Serial Bus (USB) - Type 0                      | 1            | 1                   | 1                            | No                              |

|                                                          | Sa           | fety and Security   |                              |                                 |

| Dual-zone Code Security Module (DCSM)                    | No           | Yes                 | Yes                          | No                              |

| Error Signaling Module (ESM)                             | No           | No                  | No                           | Yes                             |

| Hardware Security Module (HSM)                           | No           | No                  | No                           | Yes                             |

| Logic Power-on Self-test (LPOST)                         | No           | No                  | No                           | Yes                             |

| Memory Power-on Self-test (MPOST)                        | No           | No                  | No                           | Yes                             |

| Safety and Security (SSU) Module                         | No           | No                  | No                           | Yes                             |

| Waveform Analysis and Diagnostics (WADI)                 | No           | No                  | No                           | Yes                             |

| Functional Safety                                        | ASIL B/SIL 2 | ASIL B/SIL2         | ASIL B/SIL2                  | ASIL D/SIL3                     |

Table 1-2. 100-pin IO and Analog Channel Counts

|                                                | table : _ rec pin to and rinancy ename. |         |                                  |                                   |

|------------------------------------------------|-----------------------------------------|---------|----------------------------------|-----------------------------------|

| IO Type                                        | F2837x                                  | F2838x  | F28P65x                          | F29H85x                           |

|                                                |                                         | Digital |                                  |                                   |

| AIO (analog with digital inputs)               |                                         | -       | 13                               | 16                                |

| AGPIO (analog with digital inputs and outputs) |                                         | -       | 11                               | 8                                 |

| Additional GPIO                                | 41                                      | -       | 4 (2 from JTAG and 2 from X1/X2) | 5 (ERRORSTS, TDI, TDO,<br>X1, X2) |

| Standard GPIO                                  |                                         | -       | 49                               | 41                                |

| Total GPIO                                     |                                         | -       | 60                               | 46                                |

| Total GPIO + AIO                               |                                         | -       | 73                               | 70                                |

| Analog                                         |                                         |         |                                  |                                   |

| ADC Channels (single-<br>ended, all modules)   | 24                                      | -       | 24                               | 24                                |

Table 1-2. 100-pin IO and Analog Channel Counts (continued)

| IO Type                                | F2837x | F2838x | F28P65x | F29H85x |

|----------------------------------------|--------|--------|---------|---------|

| ADC Channels<br>(differential, ADC AB) | 12     | -      | 11      | 6       |

Table 1-3. 176-pin IO and Analog Channel Counts

|                                                | table : or the printer and randon evaluation |         |                                  |                                   |

|------------------------------------------------|----------------------------------------------|---------|----------------------------------|-----------------------------------|

| IO Type                                        | F2837x                                       | F2838x  | F28P65x                          | F29H85x                           |

|                                                |                                              | Digital |                                  |                                   |

| AIO (analog with digital inputs)               |                                              |         | 14                               | 28                                |

| AGPIO (analog with digital inputs and outputs) |                                              |         | 22                               | 26                                |

| Additional GPIO                                | 97                                           | 97      | 4 (2 from JTAG and 2 from X1/X2) | 5 (ERRORSTS, TDI, TDO,<br>X1, X2) |

| Standard GPIO                                  |                                              |         | 106                              | 81                                |

| Total GPIO                                     |                                              |         | 128                              | 86                                |

| Total GPIO + AIO                               |                                              |         | 142                              | 140                               |

|                                                |                                              | Analog  |                                  |                                   |

| ADC Channels (single-<br>ended, all modules)   | 20                                           | 20      | 36                               | 54                                |

| ADC Channels<br>(differential, ADC AB)         | 9                                            | 9       | 18                               | 13                                |

Table 1-4. 256-pin IO and Analog Channel Counts

| IO Type                                        | F2837x | F2838x  | F28P65x                          | F29H85x                        |  |

|------------------------------------------------|--------|---------|----------------------------------|--------------------------------|--|

|                                                |        | Digital |                                  |                                |  |

| AIO (analog with digital inputs)               | -      | -       | 18                               | 54                             |  |

| AGPIO (analog with digital inputs and outputs) | -      | -       | 22                               | 26                             |  |

| Additional GPIO                                | -      | -       | 4 (2 from JTAG and 2 from X1/X2) | 5 (ERRORSTS, TDI, TDO, X1, X2) |  |

| Standard GPIO                                  | -      | -       | 163                              | 105                            |  |

| Total GPIO                                     | -      | -       | 185                              | 110                            |  |

| Total GPIO + AIO                               | -      | -       | 203                              | 190                            |  |

|                                                | Analog |         |                                  |                                |  |

| ADC Channels (single-<br>ended, all modules)   | -      | -       | 40                               | 80                             |  |

| ADC Channels<br>(differential, ADC AB)         | -      | -       | 19                               | 16                             |  |

www.ti.com C29x Architecture

# 2 C29x Architecture

With the solid basis of the real-time feature and fast-signal chain, the C28x core is evolving to a new generation C29x core. This change in C29x helps improve the overall performance and increase the market share of all kinds of real-time applications. This section shows the new architecture of C29x, and an overview of the new features that have been added and improved from C28x.

### 2.1 C29x Architecture Overview

The C29 CPU is an enhanced VLIW (Very Long Instruction Word) architecture with a fully protected pipeline. C29 supports multiple instruction sizes (16, 32, and 48 bits) and a variable instruction packet size which contains instructions that execute in parallel. This is enabled by multiple functional units inside the CPU which can execute concurrently. A total of 64 working registers support the parallel operations in the CPU. In addition to the working registers, the CPU contains multiple status registers which maintain different execution and interrupt context related information. The major features in C29x are specified in Table 2-1.

Table 2-1. C29 Major Feature

| Feature Comment                       |                                                                                                                                                                                                                                                                                                                                           |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ease of Use                           | Byte addressable CPU     Linear and unified memory map with 4GB address range     Fully protected pipeline     Deterministic execution without cached memories                                                                                                                                                                            |  |  |

| Improved Parallelism                  | <ul> <li>Execute 1 to 8 instructions in parallel</li> <li>Execute fixed-point, floating point, and addressing operations in parallel</li> <li>Specialized instructions for decision making code and real-time control (example: if-then-else statements, trigonometric and multiphase vector translation operations)</li> </ul>           |  |  |

| Improved Bus Throughput               | <ul> <li>Capable of fetching up to 128-bit instruction word every cycle</li> <li>Capable of performing 8, 16, 32, 64-bit dual reads and single writes per cycle</li> <li>Improved addressing modes which reduce overhead in accessing memory and peripheral resources</li> </ul>                                                          |  |  |

| Code Efficiency                       | <ul> <li>Supports variable length instruction set (16-bit, 32-bit, and 48-bit)</li> <li>Critical operations are encoded as 16-bit and 32-bit opcodes for improving the code density</li> <li>Rich instruction set optimizes operations in smallest instructions</li> </ul>                                                                |  |  |

| ASIL-D Safety Capability              | <ul> <li>Support for both Lockstep and split lock modes</li> <li>Integrated ECC logic enables end to end safe interconnect</li> <li>Separate code threads can be fully isolated including stack using SSU</li> <li>Zero CPU overhead switching from one thread to other in HW automatically enabled best real-time performance</li> </ul> |  |  |

| Multi-zone Security                   | <ul> <li>Run time content protection and IP protection of code</li> <li>Individual passwords for each zone to control access</li> </ul>                                                                                                                                                                                                   |  |  |

| Enhanced Debug and Trace Capabilities | <ul> <li>Specialized data logging and code flow trace instructions</li> <li>Trace data capable of being logged in on-chip RAM or exported through serial communication peripherals</li> </ul>                                                                                                                                             |  |  |

Besides from the C29x's feature improvement, there are several new IPs that is used for faster signal chain and safer environment around the CPU.

C29x Architecture Www.ti.com

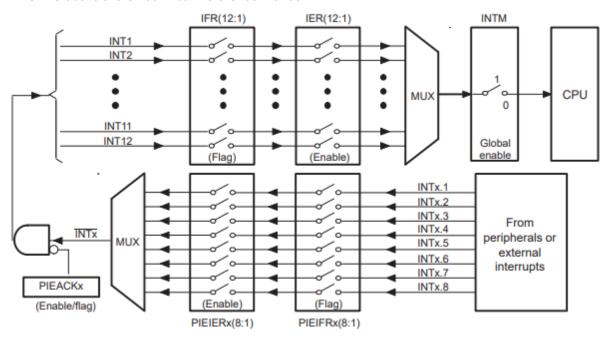

### 2.1.1 Peripheral Interrupt Priority and Expansion (PIPE)

In C28x, the primary interrupt controller was the Peripheral Interrupt Expansion (PIE). In C29x, the primary interrupt controller is the Peripheral Interrupt Priority and Expansion (PIPE). The PIPE module arbitrates peripheral interrupts across the device. All asserted interrupts are arbitrated each clock cycle, with the highest priority interrupt asserted to the appropriate CPU interrupt line (NMI, RTINT, or INT). The PIPE module is responsible for providing vector addresses to the CPU for NMI, RTINT, INT and RESET. The PIPE is capable custom ordering of interrupts and hardware nesting. For more information, see the *F29H85x and F29P58x Real-Time Microcontrollers Technical Reference Manual*.

Figure 2-1. PIE Architecture

Figure 2-2. PIPE Architecture

www.ti.com C29x Architecture

# Table 2-2. PIE vs PIPE

| Feature                    | C28x PIE              | C29x PIPE                    |

|----------------------------|-----------------------|------------------------------|

| Hardware Prioritization    | No (Software only)    | Yes                          |

| Hardware Arbitration       | No (Software only)    | Yes                          |

| Hardware Nesting           | No                    | Yes (can block using groups) |

| Peripheral Interrupt Type  | 1                     | 2 (RTINT/INT)                |

| Stack Overflow Tracking    | No                    | Yes                          |

| Peripheral Interrupt Count | 192 (on most devices) | 256                          |

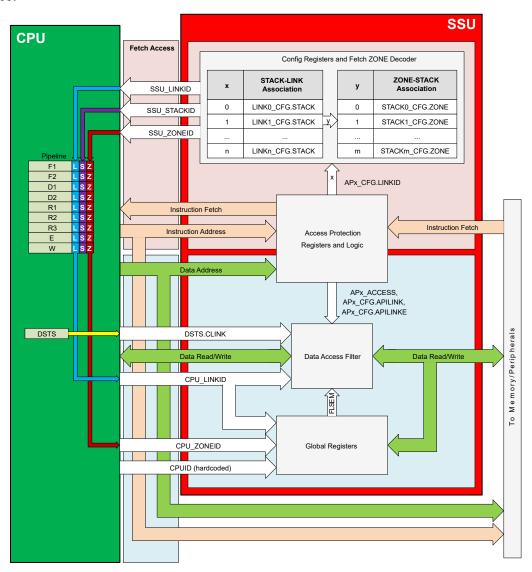

### 2.1.2 Safety and Security Module (SSU)

The Safety and Security Unit (SSU) acts as a firewall between the C29 CPUs and the memory and peripherals. The primary role of the SSU is to enforce run-time safety and security protections during every CPU access to peripherals and memory on the chip. In addition, the SSU governs debug access and flash controller operations on the device.

Figure 2-3. SSU-CPU Coupled Interface

C29x Architecture www.ti.com

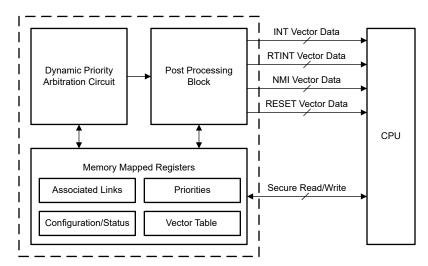

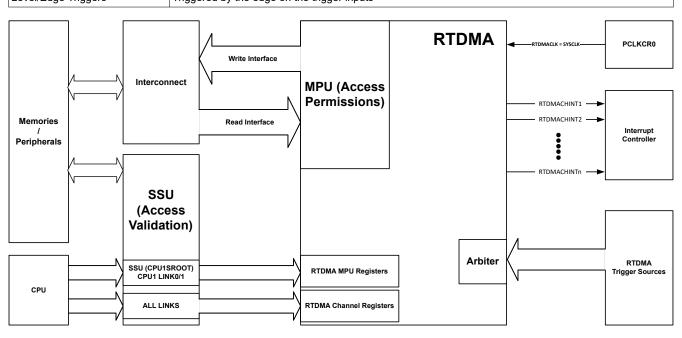

### 2.1.3 Real-Time DMA (RTDMA)

The Real-Time (RTDMA) provides a hardware method of transferring data between peripherals and memory without intervention from the CPU in real time. Each of the (2) F29H85x RTDMA modules has ten independent, user-configurable RTDMA channels with an corresponding PIPE vector mapped interrupt to inform the CPU when a RTDMA transfer has either started or completed. All ten channels can be configured at one of four priority levels with one selected channel at a higher priority than the others. Table 2-3 shows the differences between the C28x DMA and the new C29x RTDMA. For more information, see the F29H85x and F29P58x Real-Time Microcontrollers Technical Reference Manual.

| Feature              | C28x DMA                                               | C29x RTDMA                                                                                  |  |  |

|----------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|

| Number of channels   | (6) channels with fixed priority level                 | (10) channels with (4) software configurable priority levels                                |  |  |

| Burst Mode           | No                                                     | Yes (for data transfer through EMIF)                                                        |  |  |

| Data Transfer Size   | 16 and 32-bit data transfers                           | 8, 16, 32, and 64-bit data transfers                                                        |  |  |

| Read/Write Interface | (1) Read/Write bus – 3 cycles/word without arbitration | (2) Independent Read/Write busses – 1 cycle/word without arbitration                        |  |  |

| Trigger Source       | System Level Only                                      | System Level, Internal channel to channel linking                                           |  |  |

| Safety               | N/A                                                    | Integrated Memory Protection Unit configured by system level Safety and Security Unit (SSU) |  |  |

| Security             | N/A                                                    | Integrated channel specific secure zones                                                    |  |  |

| Transfer Control     | Linear and Circular Addressing Mode (One Shot          | t, Continuous, Channel Interrupt)                                                           |  |  |

| Level/Edge Triggers  | Triggered by the edge on the trigger inputs            | Triggered by the edge on the trigger inputs                                                 |  |  |

Table 2-3, DMA vs RTDMA

Figure 2-4. RTDMA Block Diagram

# 2.1.4 Lock-step Compare Module (LCM)

CPU1 and CPU2 instances, including the integrated PIPE and RTDMA will be supported by lock-step mode configuration to detect permanent and transient faults for safety-critical applications. The CPU can be configured as single module (CPU2 not present on the device) or lockstep (CPU1 and CPU2 in lockstep mode) or dual module (CPU1 and CPU2 operating as independent cores, also known as split-lock mode). The lock-step feature is only available on certain device variants. For the device variants that can support lock-step, see the *Device Comparison* table in the device-specific data sheet. For the full details of the *Lock-step Comparator Module* section, see the *F29H85x and F29P58x Real-Time Microcontrollers Technical Reference Manual*.

www.ti.com C29x Architecture

There are several IPs that are covered by LCM:

- C29 CPU Subsystem (Includes C29x CPUs, PIPE, Timer, ERAD, and DLT)

- RTDMA

**Table 2-4. Lockstep Module CPU Configuration**

| CPU1 and CPU2   | CPU1                                         | CPU2             |

|-----------------|----------------------------------------------|------------------|

| Single Core     | Available                                    | Clock Gated      |

| SL (Split-lock) | Independent Core                             | Independent Core |

| LS (Lock-step)  | Cores operate as single CPU1 in Lock-step Me | ode              |

# 2.2 C28x vs C29x Architecture Overview

C29x as a new generation CPU, there are several improvements made in architectures, which has enhanced on the efficiency and the overall performance when executing instructions. Table 2-5 shows the organized improvement in C29x. For more detailed CPU information, please refer to C2000 C29x CPU and Instruction Set.

Table 2-5. C29x Improvement

|              | Table 2-5. C29x li                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Category     | C28x                                                                                                                                                                                                              | C29x                                                                                                                                                                                                                                                                                                                                                                                                              |

| Architecture | <ul> <li>16-bit addressable</li> <li>FPU32, FPU64</li> <li>TMU32</li> <li>NLPID</li> <li>Fast Integer Division</li> <li>1x 32-bit program bus</li> <li>1x 32-bit read bus</li> <li>1x 32-bit write bus</li> </ul> | <ul> <li>Very Long Instruction Word architecture (VLIW)</li> <li>Byte-addressable</li> <li>FPU32, FPU64 (CPU3 only)</li> <li>TMU32, TMU64 (CPU3 only)</li> <li>NLPID</li> <li>Fast Integer Division</li> <li>1x 128-bit program bus</li> <li>2x 64-bit read bus</li> <li>1x 64-bit write bus</li> </ul>                                                                                                           |

| Parallelism  | <ul> <li>1 instruction per cycle</li> <li>Protected pipeline (not extended to coprocessors)</li> </ul>                                                                                                            | <ul><li>Up to 8 instructions per cycle</li><li>Fully protected pipeline</li></ul>                                                                                                                                                                                                                                                                                                                                 |

| Performance  | -                                                                                                                                                                                                                 | <ul> <li>CPU running at same frequency:</li> <li>2x to 3x signal chain performance increase (motor control, power control)</li> <li>5x faster FFT performance (system diagnostics, system tuning, arc detection)</li> <li>4x faster interrupt response and reduced latency (support for real time interrupts)</li> <li>2x to 3x improvement in general purpose code (if then else, command processing)</li> </ul> |

| Interrupt    | <ul> <li>Peripheral Interrupt Expansion (PIE)</li> <li>INT, NMI</li> <li>Real time interrupt latency: 40+ cycles</li> </ul>                                                                                       | <ul> <li>Peripheral Interrupt Priority and Expansion (PIPE)</li> <li>INT, RTINT, NMI</li> <li>Interrupt latency: 11 cycles</li> <li>Dedicated HW stack for real-time interrupt <ul> <li>HW saves/restores the context</li> </ul> </li> </ul>                                                                                                                                                                      |

| Security     | Dual Code Security Module (DCSM)                                                                                                                                                                                  | <ul><li>Safety and Security Unit (SSU)</li><li>Hardware Security Module (HSM)</li></ul>                                                                                                                                                                                                                                                                                                                           |

| Safety       | ASIL B     MPOST                                                                                                                                                                                                  | <ul> <li>ASIL D</li> <li>MPOST, LPOST</li> <li>ECC / Parity protection for bus and registers</li> <li>MPU-like SSU enables freedom from interference enabled</li> </ul>                                                                                                                                                                                                                                           |

# 3 PCB Design Consideration

F29H85x has four package types (256ZEX, 176 PTS, 144RFS, and 100PZS). Due to the various enhancements in the F29H85x device series, there is no compatibility between the PCB designs. The following sections include recommendations on how to start designing a new PCB, in general.

### 3.1 VSSOSC

In F28P65x, the VSSOSC is used for connections for the crystal oscillator (X1 and X2) ground. If an external crystal is not used, the VSSOSC can be connected to the board ground, but is not required.

In F29H85x, the VSSOSC must be grounded, so that VSSOSC and VSS are on the same plane, for proper device operation.

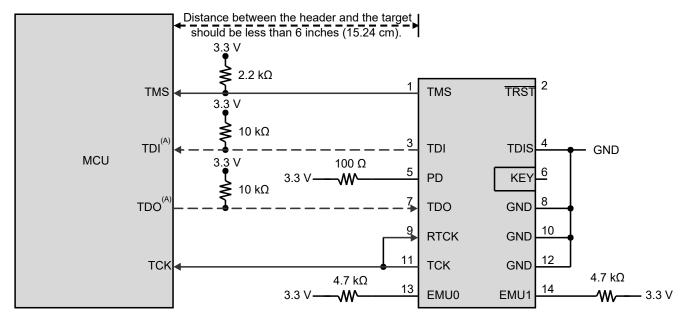

### **3.2 JTAG**

The JTAG architecture from F28P65x to F29H85x remains the same except for one functional difference. Both devices support the same 4-wire (JTAG protocol). For 2-wire mode, F29H85x only supports the Serial Wire Debug (SWD) Protocol while F28P65x only supports cJTAG (compact JTAG).

Figure 3-1. JTAG Connection Diagram (Connecting to 14-Pin JTAG Header)

### **3.3 VREF**

F29H85x has two dedicated VREFHI pins. One is for both ADCA and ADCB (12-bit/16-bit ADCs) and the other is for ADCC, ADCD, and ADCE (12-bit ADCs). These VREFHI pins should not be tied together but instead be supplied independently to minimize coupling between the different ADC types and modes of operation to achieve optimum performance.

In addition, it is important to keep low inductance connections in the reference path allows the reference driving circuit to remain stable and settled during the conversion phase.

# 4 Feature Differences for System Consideration

This section showcases the similarities and differences in features when moving between the F28P65x and F29H85x devices.

Table 4-1. Main Changes in F29H85x

| Category            | Peripheral Information                                           |

|---------------------|------------------------------------------------------------------|

| CPU Subsystem       | C29x CPU Section 2.1                                             |

| Managana            | RAM Section 4.6                                                  |

| Memory              | FLASH Section 4.6                                                |

|                     | Peripheral Interrupt Priority and Expansion (PIPE) Section 2.1.1 |

|                     | Data Logger and Trace (DLT) Section 4.1.2                        |

| Court and           | Real-Time DMA (RTDMA) Section 2.1.3                              |

| System              | BOOTROM Section 4.1.6                                            |

|                     | Enhanced Real-Time Analysis and Diagnostic (ERAD) Section 4.1.7  |

|                     | Crossbar (XBAR) Section 4.1.8                                    |

| Analog              | Analog Subsystem Section 4.1.1                                   |

| Control             | Enhanced Pulse Width Modulator (EPWM) Section 4.1.5              |

| Communication       | Single Edge Nibble Transmission (SENT) Section 4.1.3             |

|                     | Waveform Analyzer Diagnostics (WADI) Section 4.1.4               |

|                     | Error Signaling Module (ESM) Section 4.1.9                       |

|                     | Safety and Security Module (SSU) Section 2.1.2                   |

|                     | Hardware Security Module (HSM) Section 4.1.11                    |

|                     | Cryptographic Accelerators Section 4.1.11.1:                     |

| Safety and Security | Symmetric Cryptography                                           |

|                     | Asymmetric Cryptography                                          |

|                     | Hashing Function                                                 |

|                     | Safe Interconnect End-to-End Safing Section 4.1.12               |

|                     | MMR Safing with Parity Section 4.1.13                            |

|                     | Logic Power-On Self-Test (LPOST) Section 4.1.14                  |

#### 4.1 New Features in F29H85x

This section outlines new features introduced in the F29H85x device series. For more information, see the F29H85x and F29P58x Real-Time Microcontrollers Technical Reference Manual..

# 4.1.1 Analog Subsystem

From F28P65x to F29H85x, the number of ADCs has increased from 3 to 5 along with the SOC doubling from 16 to 32. Within these 5 ADCs, two of them are 12-bit and 16-bit selectable, and three of them are 12-bit only. The ADC has been enhanced with capability of hardware oversampling and undersampling.

The PPB block has also been updated with aggregation features in hardware to support data processing for oversampling and undersampling which would otherwise require software running in lengthy repetitive loops. When the PPB delta is enabled, the ADC automatically calculates the delta between the current conversion and the last conversion for that SOC. This can speed up control loop computations in certain cases. PPB digital filter is a windowed filter can now be configured for the limit compare and zero-crossing logic in the PPB. This filter works just like the digital filter in the CMPSS, to prevent false events. Limit compare/zero-crossing can be used to generate events e.g. to trip the PWM.

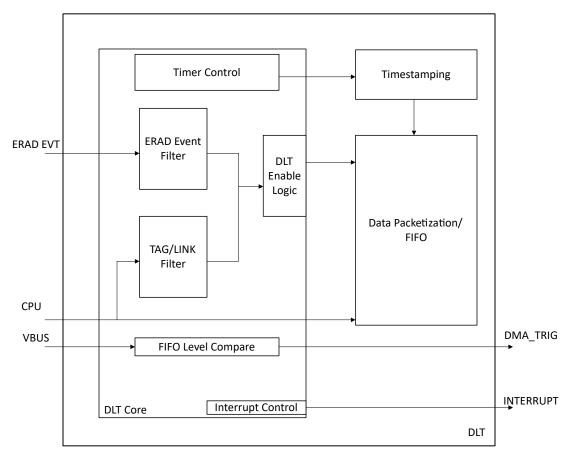

### 4.1.2 Data Logger and Trace (DLT)

The Data Logger and Trace (DLT) module has the ability to control what data gets logged, when to start data-logging, and how much data to data-log for critical CPU run-time content. Critical run-time content can include any information that needs to be monitored as the content is computed. When data-logging, the DLT is non-intrusive meaning there is no impact to run-time or CPU core behavior. The ability to view intermediate values of computation in a critical task, such as a control loop, can help users fine-tune the loop. The DLT module can generate interrupts to the interrupt controller, issue DMA transfer requests, and interact with ERAD event triggers. The DLT makes it possible to collect, time-stamp, pre-filter, export, and do real-time and post analysis of data.

Figure 4-1. DLT Block Diagram

### 4.1.3 Single Edge Nibble Transmission (SENT)

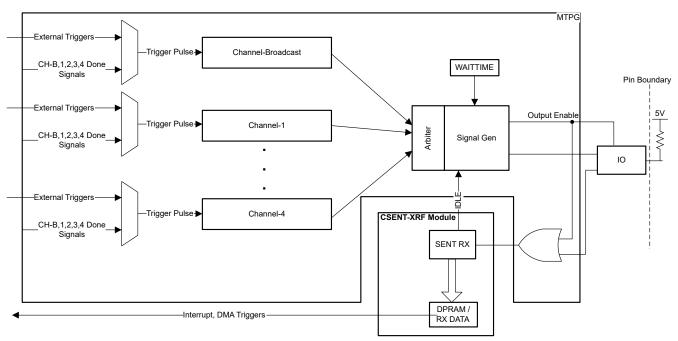

In F29H85x, SENT module for communication has been added. The SENT protocol is unidirectional and uses single wire between two or more points to transmit signals from one or more sensors to a controller. SENT uses an open standard SAE J2716 released by the Society of Automotive Engineers (SAE), and is mainly used for automotive applications. This protocol can transmit high resolution data at a low cost to the system. The SENT module utilizes a Master Trigger Pulse Generator to control and receive data from one or more sensors, using a configurable pulse signal. The received data can be stored directly into memory or a FIFO and read by the CPU or DMA.

Figure 4-2. SENT Block Diagram

# 4.1.4 Waveform Analyzer Diagnostic (WADI)

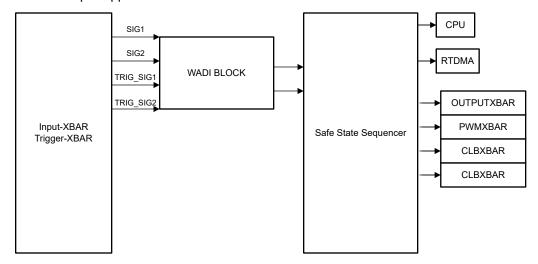

The WADI blocks analyze signal waveforms and characterize pulse width, frequency, dead-band, phase shift. If the signal waveforms are analyzed to be incorrect, it creates a sequence of events to drive the signals to a safe state. WADI is primarily used for safety applications, where deviant waveforms applied to power switches can be detected and corresponding course of action can be either taken by WADI or MCU subsystem. Each WADI block can perform comparison between two signals and have the override capabilities of the signals. Safety mechanisms of WADI can be tuned with appropriate Safe State Sequencer (SSS) configurations. SSS creates a safe sequence of chained events depending on the signals. Both the fail operational as well as fail safe solutions can be implemented as per application need and available resources.

Figure 4-3. WADI Block Diagram

### 4.1.5 EPWM

There is now a dedicated XLINK region in the memory map to support writes to any of the ePWM registers to reflect in other ePWM instances

In addition, the HRPWM's resolution in F28P65x has been with 150ps delay-line, and now in F29H85x, that is being supported with 75ps delay-line.

#### 4.1.6 Bootrom

For bootrom differences between F28P65x and F29H85x see Table 4-2.

### Table 4-2. Bootrom Comparison

| Module                 | F28P65x                                                               | F29H85x                                                                                        |

|------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| ROM Memory             | Standard and secure bootrom                                           | Start at 0x00000000 and is divided into Reset vector, NMI vector, LINK0, User tables and LINK1 |

| Security Module        | DCSM initialization done through dummy reads                          | SSU initialization, no dummy reads                                                             |

| MPOST                  | Can execute at 150MHz, 75MHz PLL output clock as well as INTOSC clock | MPOST and LPOST are performed by HSM and not by CPU1                                           |

| PLL                    | Option to enable/disable PLL during bootrom execution                 | PLL is enabled by HSM, and CPU1 runs at PLL clock                                              |

| Watchdog Timer         | Disabled by default                                                   | Enabled by default                                                                             |

| Error Status Pin       | GPIO configured as Error Status Pin                                   | GPIO configured as Error Status Pin and ESM configuration to influence error status pin        |

| Peripheral Bootloaders | Executed at bypass clock                                              | Executed at PLL clock                                                                          |

Table 4-2. Bootrom Comparison (continued)

| Module                          | F28P65x                                          | F29H85x                                                                                                                     |  |

|---------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Peripheral Boot Modes Supported | CAN, MCAN, I2C, SPI, SCI, USB, GPIO              | CAN, MCAN, I2C, SPI, UART-HS, GPIO                                                                                          |  |

| Critical Trim Loading Method    | Bootrom loads                                    | Hardware CTL module loads                                                                                                   |  |

| Bootload Image Format           | Key followed by image data organized into blocks | X509 certificate followed by the image data                                                                                 |  |

| Boot Process                    | Involves downloading of image from peripheral    | Involves handshaking with HSM for X509 certificate and image sharing with HSM for integrity check or authentication         |  |

| IPC                             | IPC is based on C2000 IPC interface              | IPC between CPU1 and HSM is<br>heterogeneous involving C2000 IPC interface<br>on CPU1 and Mailbox based interface on<br>HSM |  |

| NMI                             | NMI is enabled at a later point in the boot flow | NMI is enabled by default throughout the boot flow                                                                          |  |

| ОТР                             | Single user OTP available                        | Dual SECCFG sectors are available                                                                                           |  |

| Lockstep                        | Lockstep is disabled during boot flow            | Lockstep is enabled during boot flow                                                                                        |  |

#### 4.1.7 ERAD

C29 Embedded Real-time analysis and Diagnostics (ERAD) block is mainly comprised of two major blocks to aid with debug and system analysis capabilities. This is primarily tied to the C29 CPU and these capabilities can be used either with the debugger connected or as part of real-time application too. The two main components are the enhanced bus comparator (EBC) and the system event counter block (SEC), with an optional PC trace module.

ERAD can generate hardware breakpoints, watch points, interrupts or just a trigger output to be used by other resources like profiling counters and configurable logic block (CLB).

ERAD can be used for various types of system scenarios like counting of system events (like interrupts, critical system events and so forth), measuring minimum and maximum time taken between a pair of events measured over multiple iterations, and so forth.

Program Counter trace block helps keep track of PC discontinuity/jumps, which can in turn help track the complete sequence of software that got executed at any given point of time.

### 4.1.8 XBAR

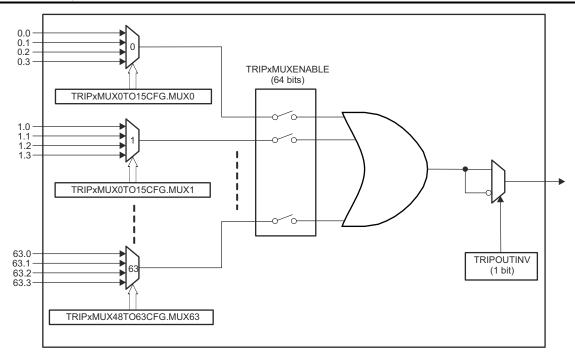

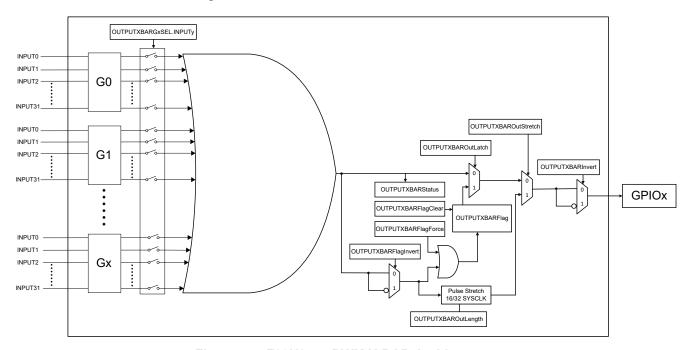

The crossbars (XBAR) provide flexibility to connect device inputs, outputs, and internal resources in a variety of configurations. F29H85x contains several XBARs, including Input X-BAR, Output X-BAR, CLB X-BAR, ePWM X-BAR, MINDB X-BAR, and ICL X-BAR. In F29H85x, there is an architectural improvement compared to F28 family. Figure 4-4 shows that the input signals are directed into a MUX, where users can only choose one input within the same MUX. However, Figure 4-5 shows that the inputs are grouped (G0...Gx) instead of muxed, which solves the scenario when users want to select multiple inputs within the same group. Now, they can enable any combination of inputs, even if they are within the same group, to be ORed together to produce the output signal of the X-BAR. This architecture is used across all XBAR modules with the exception of Input X-BAR, which has the same architecture as C28 Input X-BAR.

Figure 4-4. F28P65x ePWM X-BAR Architecture

Figure 4-5. F29H85x ePWM X-BAR Architecture

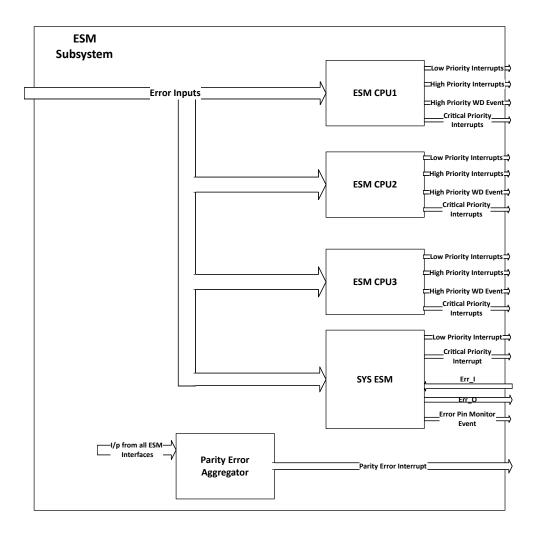

# 4.1.9 Error Signaling Module (ESM)

The Error Signaling Module (ESM) provides a systematic consolidation of responses to error events throughout the device into one location. The error classification in the ESM is determined by programmed configuration for each individual error input. The module can signal high or low priority interrupts to the processor to respond to an error event and/or manipulate an I/O error pin to signal an external hardware that an error has occurred. This external controller is then able to reset the device and/or keep the system in a safe, known state.

Figure 4-6. ESM-SS Block Diagram

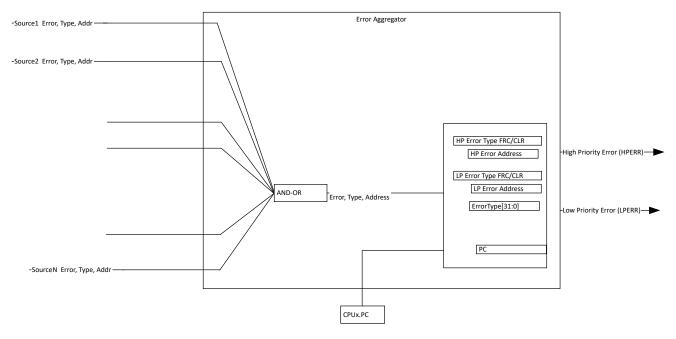

# 4.1.10 Error Aggregator

The error aggregator is an interface module between certain peripherals that generate specific errors including the C29, RTDMA, Memory controllers, Peripheral bridges, Read Interfaces and ESM. Main purpose of the Error Aggregator is to accumulate various errors from various sources and provide aggregated error output to ESM module. The module also logs the error status, error address and error type information while segregating high priority errors and low priority errors for ESM to generate appropriate action to alert CPU.

Figure 4-7. Error Aggregator Block Diagram

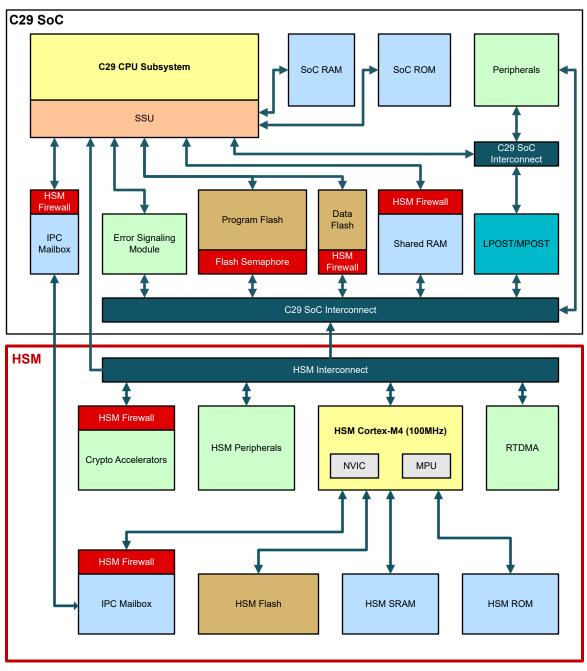

### 4.1.11 Hardware Security Module (HSM)

The Hardware Security Module (HSM) is a self-contained subsystem within the device that provides security and cryptographic functions. The host C29 subsystem interfaces with the HSM subsystem to perform the cryptographic operations required for code authentication, secure boot, secure firmware upgrades, secure debug, and encrypted run-time communications. The HSM also includes several hardware accelerators to efficiently execute key cryptographic algorithms. These engines are described in the Table 4-3.

Figure 4-8. Device High-Level Block Diagram

### 4.1.11.1 Cryptographic Accelerators

Table 4-3. List of Cryptographic Accelerator Engines

| Type of Cryptography    | Cryptographic Engine | Feature Supporte                                                                                                                                                                                                                                              | d                                          |  |

|-------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|

| Symmetric Cryptography  | AES                  | Symmetric Algorithms: AES-128, AES-192, AES-256<br>Cipher Modes: ECB, CTR, CBC, GCM<br>Authentication: CBC-MAC, CMAC                                                                                                                                          |                                            |  |

|                         | SM4                  | Symmetric Algorith                                                                                                                                                                                                                                            | Symmetric Algorithms: SM4                  |  |

| Asymmetric Cryptography | PKE                  | High-performance PKE (Public Key Engine) for large-vector math/modulus operation Asymmetric Algorithms: RSA-2048, RSA-3092, RSA-4096, ECC (Curve25519, X25519, SecP256r1, SecP256k1, SecP384k1, Brain Pool, and more), SM2 Side-channel protection (DPA, FIA) |                                            |  |

|                         |                      | НМАС                                                                                                                                                                                                                                                          | Hash Algorithms: SHA-256, SHA-384, SHA-512 |  |

| Hashing Function        | Hashing Engine       | SHA                                                                                                                                                                                                                                                           | Keyed Hashing: HMAC-SHA256, HMAC-SHA512    |  |

|                         |                      | MD5                                                                                                                                                                                                                                                           |                                            |  |

|                         | SM3                  | Hash Algorithms: SM3 (256 bits, 384 bits, 512 bits)                                                                                                                                                                                                           |                                            |  |

# 4.1.12 Safe Interconnect End-to-End (E2E) Safing

The Safe Interconnect mechanism detects any faults that occur in the bus interconnect on the F29H85x. The bus interconnect includes C29 buses (control and data), address decodes, memory controllers, and peripheral bridges. Any data corruption in memory is detected and this is achieved by storing ECC along with data in memory. To achieve safe interconnect, there are checks that are implemented inside and outside the CPU.

# 4.1.13 Critical MMR Safing With Parity

Parity detection identifies single bit errors in a read access. The parity circuitry sets the parity bits when the location of the byte is written and verifies that there are no single bit errors in the word when it is read back. This is done during each read and write cycles, so no CPU overhead is involved. When the parity circuitry identify an error, it generates a high priority interrupt to the CPU.

The IPs covered by MMR Safing with Parity include the following:

- ADC

- Analog Subsystem

- ESM

- · Error Aggregator

- Flash

- LCM

- LPOST

- PIPE

- SYSCTRL

- WADI

### 4.1.14 LPOST

F29H85x introduces the Logic Power-On Self-Test (LPOST) which addresses the start-up logic self-test requirements for functional safety applications. Coverage is configurable (60%, 80%, 90%) based on the application requirements. The higher the coverage required, the higher will be the impact on boot time. The LPOST test is triggered through software on power-up and/or during functional operation. Once the test is initiated, the device will enter scan test mode, perform the logic self-test, logs the status of the test, enter functional mode and issue a chip to reset. The reset issued after LPOST clears up any random data shifted in by the scan operation.

For power-on self-test, application code does not need to invoke the test. The test will be invoked by the Boot-ROM based on the OTP configuration. Upon completion of the boot process and test status, the application needs to take the appropriate safety action.

#### Note

All analog modules (except the ones required for the POST execution) shall be powered down during test.

# 4.2 Communication Module Changes

Communication module changes between the F28P65x and F29H85x devices affect the number of modules and migration. Module functionality is mostly maintained between both devices. Table 4-4 shows the module instances and major register differences which should be considered when migrating applications between F28P65x and F29H85x.

**Table 4-4. Communication Module Instances**

| Module | Category  | F28P65x                                                  | F29H85x                                         | Notes                                   |  |

|--------|-----------|----------------------------------------------------------|-------------------------------------------------|-----------------------------------------|--|

| SCI    | Number    | 2 - SCIA, SCIB                                           | Not Present                                     |                                         |  |

| I2C    | Number    |                                                          | 2 - I2CA, I2CB                                  |                                         |  |

| LIN    | Number    |                                                          | 2 - LINA, LINB                                  |                                         |  |

| CAN    | Number    | 1 - CANA                                                 | Not Present                                     |                                         |  |

| CAN-FD | Number    | 2 - MCANA, MCANB                                         | 6 - MCANA, MCANB, MCANC, MCAND, MCANE, MCANF    |                                         |  |

| SPI    | Number    | 4 - SPIA, SPIB, SPIC,<br>SPID                            | 5 - SPIA, SPIB, SPIC, SPID, SPIE                |                                         |  |

| PMBUS  | Number    |                                                          | 1 - PMBUSA                                      |                                         |  |

| EMIF   | Number    | 1 - EMIF1                                                |                                                 |                                         |  |

| USB    | Number    | 1 - USBA                                                 | 1 - USBA Not Present                            |                                         |  |

| ECAT   | Number    |                                                          | 1- ECATA                                        |                                         |  |

| SENT   | Number    | Not Present 6 - SENTA, SENTB, SENTC, SENTD, SENTE, SENTF |                                                 |                                         |  |

|        | Number    | 2 - UARTA, UARTB                                         | 6 - UARTA, UARTB, UARTC, UARTD, UARTE,<br>UARTF |                                         |  |

| UART   |           | -                                                        | GLB_INT_CLR                                     | UART Global Interrupt<br>Clear Register |  |

| UARI   | Registers | -                                                        | GLB_INT_EN                                      | UART Global Interrupt<br>Flag Register  |  |

|        | -         | GLB_INT_FLG                                              | UART Global Interrupt<br>Flag Register          |                                         |  |

| FSI    | Number    | 4 - FS                                                   | SIRXAD,2 - FSITXA, FSITXB                       |                                         |  |

# 4.3 Control Module Changes

There are changes in the control modules between the F28P65x and F29H85x devices. The biggest changes come from the EPWM and ECAP on the F29H85x device. Table 4-5 shows the module instances differences that should be considered when migrating applications between F28P65x and F29H85x.

**Table 4-5. Control Module Differences**

| Module | Category  | F28P65x                                                       | F29H85x            | Notes                                                          |

|--------|-----------|---------------------------------------------------------------|--------------------|----------------------------------------------------------------|

| SDFM   | Number    | 16 - SD1_D1C1D4C4, SD2_D1C1D4C4,<br>SD3_D1C1D4C4,SD4_D1C1D4C4 |                    |                                                                |

|        | Registers | -                                                             | SDINTMODE          | SD Interrupt Mode register                                     |

| eQEP   | Number    | 6 - E0                                                        | QEP16              |                                                                |

|        | Number    | 7 - ECAP17                                                    | 6 - ECAP1 6        |                                                                |

|        |           | -                                                             | HRCALPRD           | High-Res Calibration Period Register                           |

|        |           | -                                                             | HRCLKCAP           | High-Res Calibration HRCLK Capture Register                    |

|        |           | -                                                             | HRCLKCTR           | High-Res Calibration HRCLK Counter Register                    |

|        |           | -                                                             | HRCLR              | High-Res Calibration Interrupt Clear Register                  |

| eCAP   | Registers | -                                                             | HRCTL              | High-Res Control Register                                      |

|        | Registers | -                                                             | HRFLG              | High-Res Calibration Interrupt Flag Register                   |

|        |           | -                                                             | HRFRC              | High-Res Calibration Interrupt Force Register                  |

|        |           | -                                                             | HRINTEN            | High-Res Calibration Interrupt Enable Register                 |

|        |           | -                                                             | HRSYSCLKCAP        | High-Res Calibration SYSCLK Capture Register                   |

|        |           | -                                                             | HRSYSCLKCTR        | High-Res Calibration SYSCLK Counter Register                   |

| HRCAP  | Number    | 2 - HRCAP6, HRCAP7                                            | 2 - HRCAP5, HRCAP6 |                                                                |

|        | Number    | 18 - EF                                                       | PWM118             |                                                                |

| ePWM   | Registers | XLINK                                                         | -                  | EPWMx Link Register (Present in SysCtl registers in F29H85x)   |

|        |           | XLINK2                                                        | -                  | EPWMx Link 2 Register (Present in SysCtl registers in F29H85x) |

| HRPWM  | Number    | 18 - HRPWM118                                                 |                    |                                                                |

# 4.4 Analog Module Differences

This section outlines the analog differences between F28P65x and F29H85x. The ADC on F29H85x has a lot of new features compared to the ADC on F28P65x. Table 4-6 shows the differences.

**Table 4-6. Analog Module Differences**

| Module | Table 4-6. Analog Module Differences    Category   F28P65x   F29H85x   Notes |                  |                   |                                                        |  |  |

|--------|------------------------------------------------------------------------------|------------------|-------------------|--------------------------------------------------------|--|--|

| ouuio  | Number                                                                       | 3 - ADCA to ADCC | 5 - ADCA to ADCE  | notes                                                  |  |  |

|        | Nullibel                                                                     | 3 - ADCA IO ADCC | PPBTRIP1FILCLKCTL | ADCEVT1 Trip High Filter Prescale Control              |  |  |

|        |                                                                              | -                |                   |                                                        |  |  |

|        | -                                                                            | -                | PPBTRIP1FILCTL    | ADCEVT3 Trip High Filter Pressels Central              |  |  |

|        | -                                                                            | -                | PPBTRIP2FILCLKCTL | ADCEVT2 Trip High Filter Prescale Control              |  |  |

|        |                                                                              | -                | PPBTRIP2FILCTL    | ADCEVT2 Trip High Filter Control Register              |  |  |

|        |                                                                              | -                | PPBTRIP3FILCLKCTL | ADCEVT3 Trip High Filter Prescale Control              |  |  |

|        |                                                                              | -                | PPBTRIP3FILCTL    | ADCEVT3 Trip High Filter Control Register              |  |  |

|        |                                                                              | -                | PPBTRIP4FILCLKCTL | ADCEVT4 Trip High Filter Prescale Control              |  |  |

|        |                                                                              | -                | PPBTRIP4FILCTL    | ADCEVT4 Trip High Filter Control Register              |  |  |

|        |                                                                              | -                | RESULT16          | ADC Result 16 Register                                 |  |  |

|        |                                                                              | -                | RESULT17          | ADC Result 17 Register                                 |  |  |

|        |                                                                              | -                | RESULT18          | ADC Result 18 Register                                 |  |  |

|        |                                                                              | -                | RESULT19          | ADC Result 19 Register                                 |  |  |