# Safety Manual for TDA3x Automotive Vision safety-critical Applications Processors

## **User's Guide**

Literature Number: SPRUIG2 September 2017

## **Contents**

| Pref | ace   |         |                                                                         | . 6 |

|------|-------|---------|-------------------------------------------------------------------------|-----|

| 1    | Intro | duction |                                                                         | . 7 |

|      | 1.1   | Overvi  | ew                                                                      | . 7 |

|      | 1.2   | Produc  | et Scope                                                                | . 7 |

|      |       | 1.2.1   | Purpose of the Product and Safety Constraints                           | . 7 |

|      |       | 1.2.2   | Application Sectors                                                     |     |

|      |       | 1.2.3   | Product Overview                                                        |     |

| 2    | TI C+ |         | DSP Development Process                                                 |     |

| _    | 2.1   |         | ew                                                                      |     |

| _    |       |         |                                                                         |     |

| 3    |       |         | ety Architecture and User Requirements                                  |     |

|      | 3.1   | -       | Function Overview                                                       |     |

|      | 3.2   |         | cal Specifications and Environment Limits                               |     |

|      | 3.3   |         | nical Environment Constraints                                           |     |

|      | 3.4   | •       | ing Frequency Limits                                                    |     |

|      | 3.5   |         | Foreseeable Environment Disturbances                                    |     |

|      | 3.6   | •       | Application Overview                                                    |     |

|      | 3.7   | Derivat | tion of Technical Safety Concept Based on Identified Safety Goals       |     |

|      |       | 3.7.1   | Front Camera Analytics System (FCA)                                     |     |

|      |       | 3.7.2   | Rear View Camera Analytics System (RVC)                                 |     |

|      |       | 3.7.3   | Surround View System (SRV)                                              |     |

|      |       | 3.7.4   | Radar and Camera Fusion System (RAD)                                    |     |

|      |       | 3.7.5   | Camera Mirror Replacement System (CMS)                                  |     |

|      |       | 3.7.6   | System and Software Level Diagnostics Details in FMEDA, With Fail Modes |     |

|      |       | 3.7.7   | Operating States                                                        |     |

|      |       | 3.7.8   | Management of Errors                                                    |     |

|      | 3.8   | Discus  | sion About Conceptual Safety Mechanisms and Assumptions of Use          |     |

|      |       | 3.8.1   | Power Supply                                                            | 85  |

|      |       | 3.8.2   | Power Management                                                        |     |

|      |       | 3.8.3   | Software Diagnostic for Configuration Checks                            | 85  |

|      |       | 3.8.4   | Clocks                                                                  | 86  |

|      |       | 3.8.5   | Reset                                                                   | 87  |

|      |       | 3.8.6   | PRCM and Control Module                                                 | 87  |

|      |       | 3.8.7   | CPU Subsystems                                                          | 88  |

|      |       | 3.8.8   | Network-on-Chip L3 Interconnect Subsystem                               | 92  |

|      |       | 3.8.9   | On-Chip RAM Subsystem                                                   | 92  |

|      |       | 3.8.10  | General-Purpose Timer Subsystem                                         | 94  |

|      |       | 3.8.11  | Interprocessor Communication (IPC)                                      | 94  |

|      |       | 3.8.12  | Serial Peripheral Interface (SPI)                                       | 95  |

|      |       | 3.8.13  | Controller Area Network                                                 | 95  |

|      |       | 3.8.14  | (LP)DDR2/3 Memory Controller (EMIF)                                     |     |

|      |       | 3.8.15  | Enhanced Direct Memory Access (EDMA)                                    |     |

|      |       | 3.8.16  | Video Input Port (VIP)                                                  |     |

|      |       | 3.8.17  |                                                                         | 98  |

|      |       | 3.8.18  |                                                                         | 98  |

|      |       | 3.8.19  | Inter-Integrated Circuit                                                |     |

|      |       |         | •                                                                       | _   |

2

#### www.ti.com

|   |       | 3.8.20 General-Purpose Input/Output (GPIO)                                    | . 99 |

|---|-------|-------------------------------------------------------------------------------|------|

|   | 3.9   | Tester On Chip (TesOC)                                                        | . 99 |

|   | 3.10  | Memory Cyclic Redundancy Check Module                                         | 100  |

|   | 3.11  | Dual-Clock Comparator                                                         | 100  |

|   | 3.12  | Error Signaling Module                                                        | 100  |

|   | 3.13  | Embedded ADC                                                                  | 101  |

| 4 | Softv | vare Diagnostic Library                                                       | 102  |

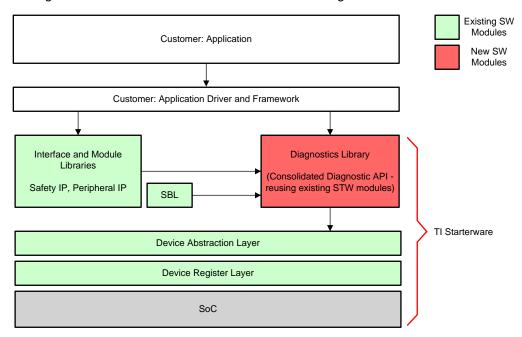

|   | 4.1   | TI Diagnostics Library Architecture                                           | 102  |

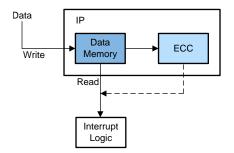

|   | 4.2   | ECC Fault Injection Test                                                      | 102  |

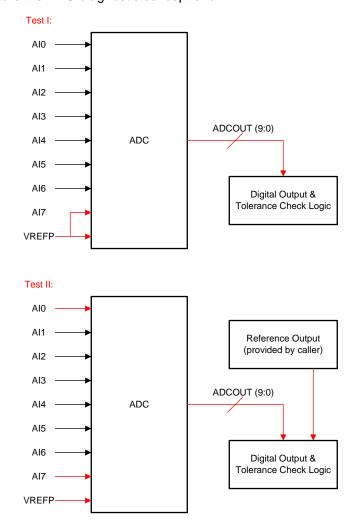

|   | 4.3   | ADC Tests                                                                     | 103  |

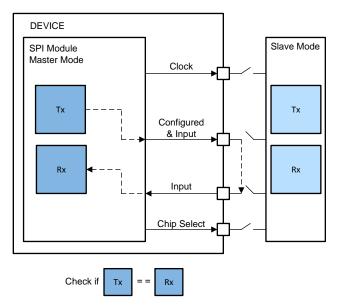

|   | 4.4   | SPI API                                                                       | 103  |

|   | 4.5   | CRC API                                                                       | 104  |

|   | 4.6   | DCC API                                                                       | 104  |

|   | 4.7   | ESM API                                                                       | 106  |

|   | 4.8   | DCAN Loopback API                                                             | 107  |

|   | 4.9   | QSPI (SPI for Boot in 4-Bit Data Mode)                                        | 107  |

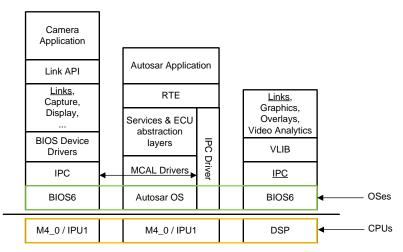

|   | 4.10  | TI AutoSAR TDA3x MCAL Architecture                                            | 108  |

|   | 4.11  | Vision SDK AutoSAR Integration Proposal on TDA3x                              | 108  |

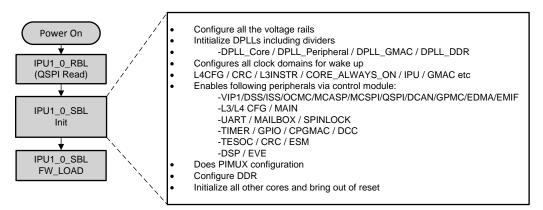

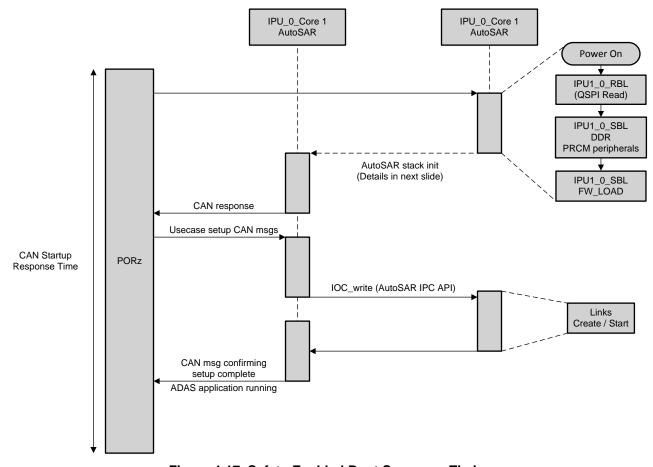

|   | 4.12  | Vision SDK SBL Concept                                                        | 109  |

|   | 4.13  | Vision SDK AutoSAR Boot Sequence                                              | 109  |

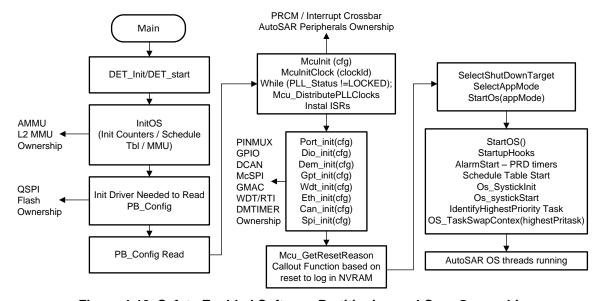

|   | 4.14  | Vision SDK AutoSAR Stack Initialization With Validation of Resource Conflicts | 110  |

|   | 4.15  | IPC Concept Between AutoSAR OS and SYS/BIOS                                   | 111  |

|   | 4.16  | SYS/BIOS Data Integrity Check Concept                                         | 111  |

|   | 4.17  | Freedom From Interference and Isolation for Software Components               | 112  |

|   |       | 4.17.1 Memory Isolation High-Level Concept                                    | 112  |

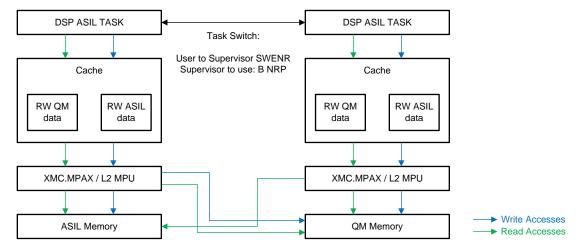

|   |       | 4.17.2 Memory Isolation on DSP                                                | 114  |

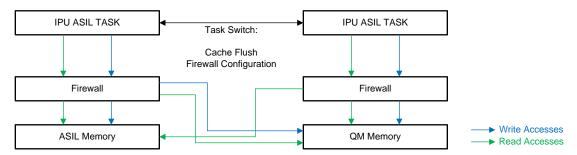

|   |       | 4.17.3 Memory Isolation on Cortex-M4                                          | 115  |

|   |       | 4.17.4 Memory Isolation on EVE                                                | 116  |

| 5 | Depe  | ndent Fail Analysis Information                                               | 118  |

| Α | -     | lopment Interface Agreement                                                   |      |

|   | A.1   | Appointment of Safety Managers                                                |      |

|   | A.2   | Tailoring the Safety Lifecycle                                                |      |

|   | A.3   | Activities Performed by TI                                                    |      |

|   | A.4   | Information to Exchange                                                       |      |

|   | A.5   | Parties Responsible for Safety Activities                                     |      |

|   | A.6   | Supporting Processes and Tools                                                |      |

|   | A.7   | Supplier Hazard and Risk Assessment                                           |      |

|   | A.8   | Creation of Functional Safety Concept                                         |      |

|   | ,     | 5.54.5 5 45.5 54.6.J. 56.60pt 111111111111111111111111111111111111            |      |

## **List of Figures**

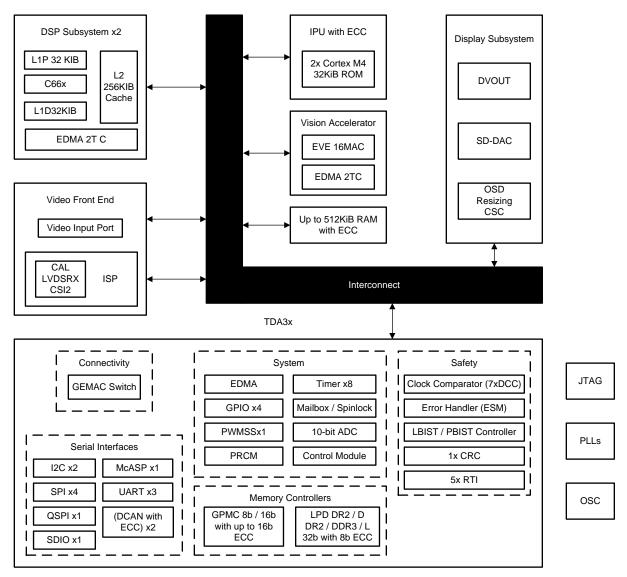

| 1-1.  | High-Level Device Diagram                                                       | 9   |

|-------|---------------------------------------------------------------------------------|-----|

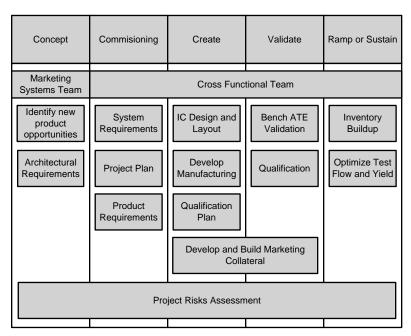

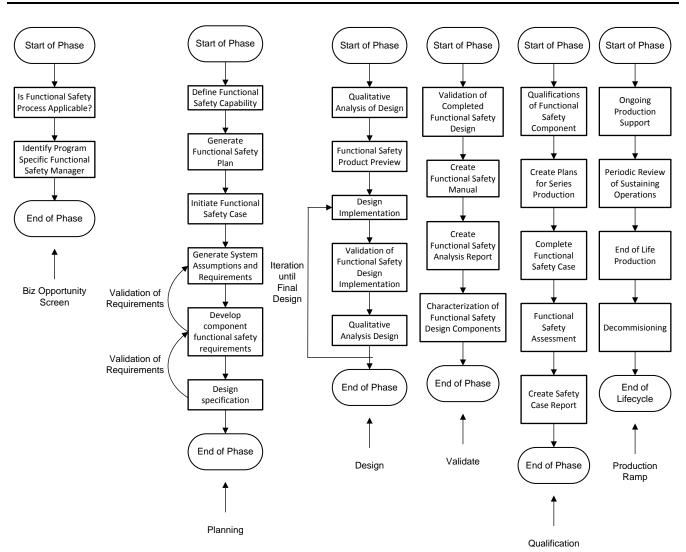

| 2-1.  | TI Standard DSP QM Development Process and ISO 26262 Compliant Process (1 of 2) | 11  |

| 2-2.  | TI Standard DSP QM Development Process and ISO 26262 Compliant Process (2 of 2) | 12  |

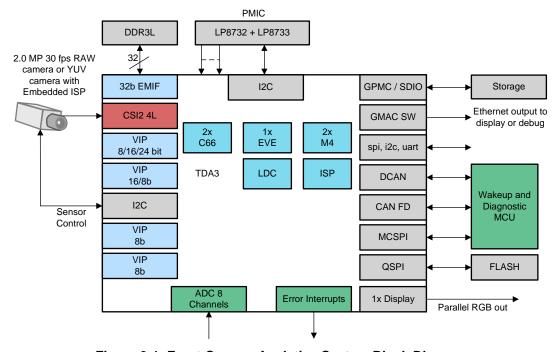

| 3-1.  | Front Camera Analytics System Block Diagram                                     | 14  |

| 3-2.  | Driver Monitoring System Block Diagram                                          | 15  |

| 3-3.  | Surround View and Camera Mirror System Conceptual Block Diagram                 | 15  |

| 3-4.  | Radar and Camera Fusion Block Diagram                                           | 16  |

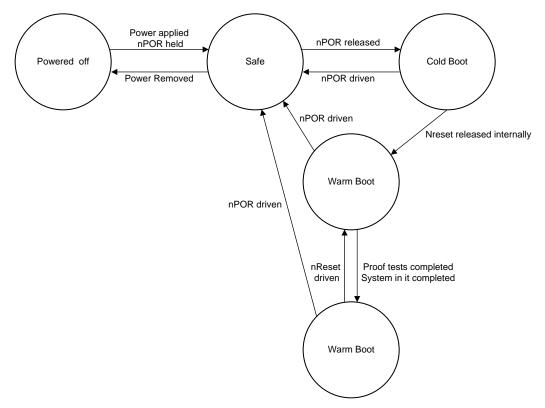

| 3-5.  | Operating States                                                                | 83  |

| 4-1.  | Diagnostics Library High-Level Architecture                                     | 102 |

| 4-2.  | Testing ECC Logic                                                               | 103 |

| 4-3.  | Using On-Chip ADC for System Monitoring                                         | 103 |

| 4-4.  | SPI Loopback Test Mechanism                                                     | 104 |

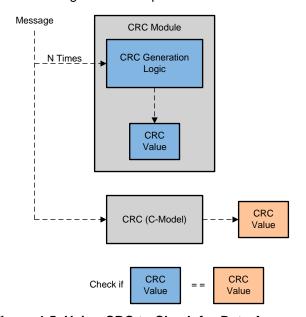

| 4-5.  | Using CRC to Check for Data Accuracy                                            | 104 |

| 4-6.  | Using DCC for Clock Monitoring (1 of 3)                                         | 105 |

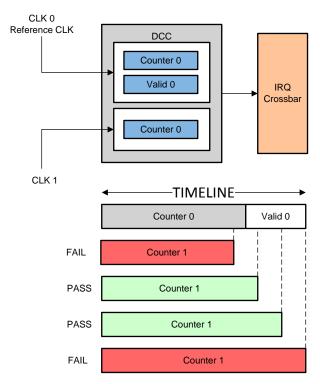

| 4-7.  | Using DCC for Clock Monitoring (2 of 3)                                         | 105 |

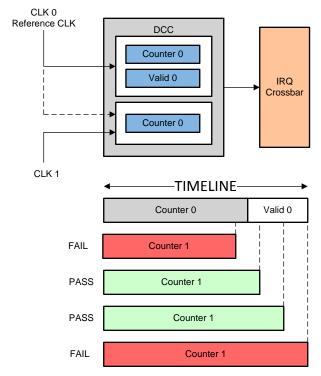

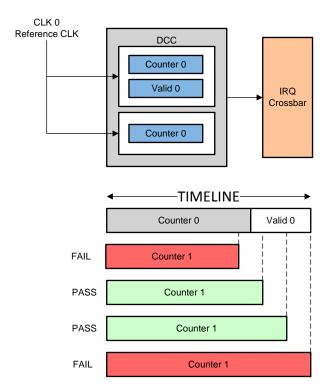

| 4-8.  | Using DCC for Clock Monitoring (3 of 3)                                         |     |

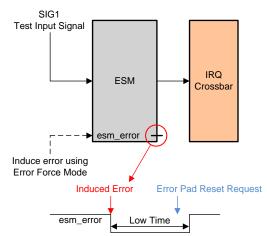

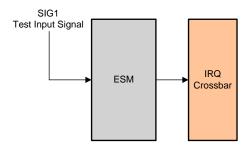

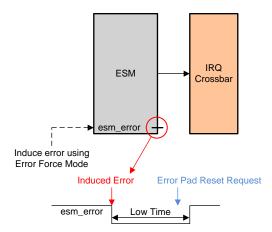

| 4-9.  | Error Interrupts for System Monitoring in ESM (1 of 3)                          | 106 |

| 4-10. | Error Interrupts for System Monitoring in ESM (2 of 3)                          | 107 |

| 4-11. | Error Interrupts for System Monitoring in ESM (3 of 3)                          | 107 |

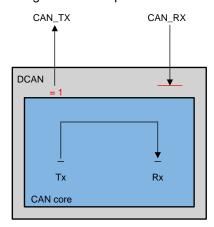

| 4-12. | Loopback Mechanism for Testing DCAN IP                                          | 107 |

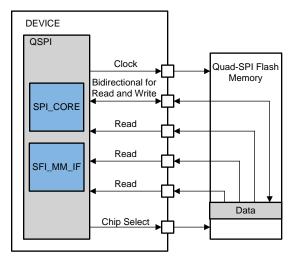

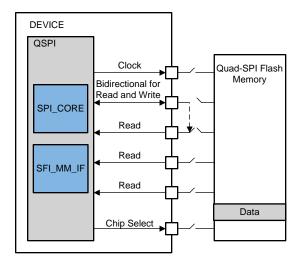

| 4-13. | Confirming Correctness of Boot Over QSPI (1 of 2)                               |     |

| 4-14. | Confirming Correctness of Boot Over QSPI (2 of 2)                               | 108 |

| 4-15. | High-Level AutoSAR Integration                                                  |     |

| 4-16. | Safety-Enabled Boot Sequence                                                    |     |

| 4-17. | Safety-Enabled Boot Sequence Timing                                             |     |

| 4-18. | Safety-Enabled Software Partitioning and Core Ownership                         |     |

| 4-19. | Safety-Enabled Interprocessor Communication (IPC)                               | 111 |

| 4-20. | Ensuring Critical Safety Data Integrity in SYSBIOS                              |     |

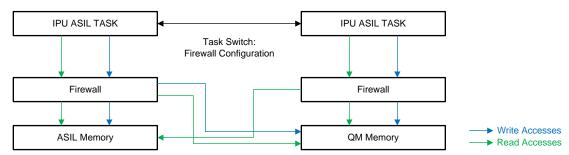

| 4-21. | Ensuring Isolation Between an ASIL and QM Task on DSP (1 of 2)                  |     |

| 4-22. | Ensuring Isolation Between an ASIL and QM Task on DSP (2 of 2)                  |     |

| 4-23. | Ensuring Isolation Between an ASIL and QM Task on M4                            | 116 |

| 1-21  | Ensuring Isolation Retween an ASII, and OM Task on EVE                          | 116 |

#### www.ti.com

## **List of Tables**

| 3-1.  | FCA Analytics                                        | . 17 |

|-------|------------------------------------------------------|------|

| 3-2.  | Front Camera Safety-Critical Components              | . 17 |

| 3-3.  | RVC Analytics                                        | . 21 |

| 3-4.  | Rear Camera Safety-Critical Components               | . 22 |

| 3-5.  | SRV Analytics                                        |      |

| 3-6.  | SRV Safety-Critical Components                       |      |

| 3-7.  | RAD Analytics                                        |      |

| 3-8.  | RAD Safety-Critical Components                       |      |

| 3-9.  | CMS Analytics                                        |      |

| 3-10. | CMS Safety-Critical Component                        |      |

| 3-11. | System Diagnostics                                   |      |

| 3-12. | Spinlock States                                      |      |

| 4-1.  | Implementing FFI for Processor Cores                 |      |

| A-1.  | Activities Performed by TI and Performed by Customer | 119  |

| A-2.  | Product Safety Documentation                         |      |

| A-3.  | Product Safety Documentation Tools and Data Formats  |      |

#### Scope

This safety manual for the TDA3x device product family specifies the responsibilities of the user for installation and operation to maintain the desired safety level.

This document contains the following:

- Product scope

- Purpose of product

- Intended application sectors

- Product safety constraints

- Information for each safety-related subsystem

- Functions, interfaces, and parameters of each safety-related subsystem

- Safety application overview

- Lifetime, environment, and application limits

- Application limits of each safety-related subsystem

- Built-in device safety logic

- User operation requirements to maintain the desired ASIL level, including a set of proof tests, diagnostic tests, and test intervals

- Summary of responsibilities of the user to integrate TDA3x device family products into safety system

- Safety-related characteristics

- Terms and definitions

- Document revision status

The following information is documented in the Safety Analysis Report Summary for the TDA3x Device (part of the FMEDA xls sheet), and is not repeated in this document:

- · Failure rate summary of the SoC estimated at the chip level

- Failure rates and diagnostic coverage for each subsystem

- Assumptions of use in calculation of safety metrics

- Fault model used to estimate device failure rates suitable to enable calculation of customized failure rates

- Quantitative FMEA (also known as FMEDA: Failure Modes, Effects, and Diagnostics Analysis) with detail to the sub-module level of the device, suitable to enable calculation based on customized application of diagnostics

Users should have a general understanding of the TDA3x device product family by reading the TDA3x Data Manual and the TDA3x Technical Reference Manual. This document is intended to be used in conjunction with the pertinent data sheets, technical reference manuals, and other documentation for the products under development.

For more information regarding the Safety Report, contact your TI sales representative.

#### **Trademarks**

C66x, Embedded Vision Engine, OMAP are trademarks of Texas Instruments.

Cortex is a registered trademark of ARM Limited.

network-on-chip is a registered trademark of Arteris, Inc.

MIPI is a registered trademark of MIPI Alliance, Inc.

Microsoft is a registered trademark of Microsoft Corporation.

## Introduction

#### 1.1 Overview

You, as a system and equipment manufacturer or designer, must ensure that your systems (and any TI hardware or software components incorporated in your systems) meet all applicable safety, regulatory, and system-level performance requirements. All application and safety-related information in this document (including application descriptions, suggested safety measures, suggested TI products, and other materials) is provided for reference only. You understand and agree that your use of TI components in safety-critical applications is entirely at your risk, and that you (as the buyer) agree to defend, indemnify, and hold harmless TI from any and all damages, claims, suits, or expense resulting from such use.

This safety manual provides information needed by system developers to assist in creating a safety-critical system using a TDA3x device. TI does not claim any compliance to any industry safety standard or Automotive Safety Integrity Level at the system level (ASIL). The devices of this family are targeted to support systems which are QM, ASIL A, and ASIL B. The safety manual specifies the responsibilities of the user for installation and operation to maintain the desired safety level.

For more information regarding the product documentation, contact your TI sales representative.

#### 1.2 Product Scope

#### 1.2.1 Purpose of the Product and Safety Constraints

The purpose of the TDA3x device is to function as a digital signal processor (DSP) in embedded automotive applications in the driver assistance space. Some of these applications may be safety critical.

Multiple safety applications were analyzed during the concept and design phase for this product, to support Safety Element Out of Context (SEOoC) development according to ISO 26262-10:2011. The product was developed per ISO 26262 standard processes. You, as the system and equipment manufacturer or designer, must ensure that your systems (and any TI hardware or software components incorporated in your systems) meet all applicable safety, regulatory, and system-level performance requirements.

TI provides safety manuals, safety analysis reports (part of FMEDA), configurable FMEDAs, and certificates of compliance to enable customers to perform item (system) level safety analysis. No assumptions have been made in the FMEDA for whether a particular item uses a block of TDA3x. This document includes the failure rates for all the blocks, without making any assumptions on the use of that particular block for a given system. The customer must use the reports provided in context of their own usage and system requirements. This safety manual highlights five use cases that customers can use as a starting point for their safety concept. These use cases should be treated as examples only, for TI customers when they use the FMEDA tool and other collateral to measure metrics and perform their own due diligence for item-level ASIL assessment.

The TDA3x device was developed according to ISO 26262 safety standards, to ease customer adoption of the product for safety applications; however, no compliance to these standards is claimed.

MidTDA3x silicon is targeted for a variety of safety applications, thus there is no fixed FTTI that TI as a supplier could propose. It is the responsibility of the customer to use the methods and safety features outlined in the safety manual and the device TRM to meet their own identified FTTI requirements.

#### 1.2.2 Application Sectors

The TDA3x device is intended to be used in automotive Advanced Driver Assistance Systems (ADAS). Specific, targeted-application segments include, but are not limited to the following:

Product Scope www.ti.com

- Front camera

- Lane departure warning

- Traffic sign recognition

- High beam assist

- Collision mitigation

- · Backup camera

- Obstacle detection

- Park assist

- Surround View Systems

- Ethernet surround view

- LVDS surround view

- Radar

- Long-range radar

- Short-range radar

- Mirror replacement

TI has designed the TDA3x device and corresponding safety documentation to be applicable to applications beyond those mentioned above. In these cases, special attention is required when following the requirements specified in this document, to ensure the correct use of this safety information.

#### 1.2.3 Product Overview

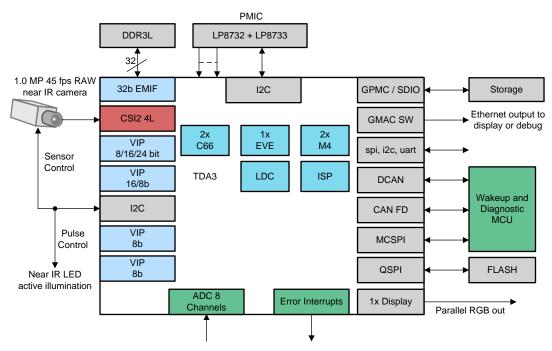

Figure 1-1 provides a high-level overview of the TDA3x device.

www.ti.com Product Scope

Consult the individual TRM of the device you use to identify the correct configuration for the module in the block diagram.

Figure 1-1. High-Level Device Diagram

The device is composed of the following main subsystems:

- Up to DSP C66x<sup>™</sup> subsystems

- Embedded Vision Engine™ (EVE) accelerator subsystem

- Dual Cortex®-M4 microprocessor unit subsystem

- Video input capture port (VIP)

- Display subsystem (DSS)

- Imaging subsystem (ISS) with imaging signal processor (ISP)

- Debug subsystem

The device provides a rich set of connectivity peripherals, including the following among others:

- Camera parallel interface (CPI)

- Camera serial interface (MIPI® CSI-2)

- Display parallel 24-bit output (for MIPI DPI 2.0 or BT.656/BT.1120 support), and one NTSC/PAL standard definition digital-to-audio converter (DAC) (for composite video support)

Product Scope www.ti.com

- Gigabit Ethernet (GEMAC) subsystem

- Two DCAN subsystems

- SDIO controller

- QSPI module

- McASP module

- PWMSS module

The device also integrates the following features:

- On-chip memory

- External memory interfaces

- · Memory management

- Level 3 (L3) and level 4 (L4) interconnects

- System and serial control peripherals

- · Phase-locked loop (PLL) for internal clock generation

The device includes comprehensive support for the following functional safety system requirements:

- Dual-core ECC-protected M4

- ECC-protected 32-bit DDR interface

- · Error detection and correction:

- Parity bit per byte on C66x DSP level 1 (L1) program cache and single-error correction dual-error detection (SECDED) on level 2 (L2) memories

- SECDED on large L3 on-chip RAM

- Dedicated memory management units per CPU (Cortex-M4 MCU, C66x DSP, and EDMA) to implement freedom from interference

- Memory protection units inside Cortex-M4 MCU subsystem allow freedom from interference

- Memory protection units internal to DSP cache controller allow freedom from interference

- · Firewalls to enable isolation and inadvertent access

- Real-time interrupt (RTI) module supports a windowed watchdog feature

- Dedicated hardware accelerated CRC block

- Embedded CRC handles MIPI pixel data on CSI-2 interface

- Two C66x DSP subsystems for redundant calculations

- MISR test schemes for EVE

- Parity-protected EVE internal memories on minimum access size granularity

- LBIST controller for testing device processors and PBIST controller for all on-chip memories

- ESM module to enable error monitoring off-chip

- DCC module for on-line clock monitoring

- Temperature monitoring sensors

- Embedded 8-channel analog-to-digital converter (ADC) for system monitoring

The ADAS TDA3x device is a high-performance, automotive, vision application device, based on enhanced OMAP™ architecture integrated on a 28-nm technology.

## TI Standard DSP Development Process

#### 2.1 Overview

TI has been developing products for the automotive applications for more than twenty years. Automotive markets have strong requirements on quality management and high-reliability of products. Though not explicitly developed for compliance to a functional safety standard, the TI standard DSP development process already features many elements necessary to manage systematic faults. This development process can be considered to be quality managed (QM), but it does not achieve an IEC 61058 Safety Integrity Level (SIL) or ISO 26262 Automotive Safety Integrity Level (ASIL).

The standard process breaks development into the following phases:

- Concept

- Commissioning

- Create

- Validation

- Ramp

In addition to following the standard development process, TDA3x has also followed a functional safety certified development process based on ISO 26262. TI engaged with an external assessor (Exida) for evaluating whether the practices followed during the development processes meet the requirements of ISO 26262. Summary phases for both of the development processes followed are illustrated in Figure 2-1 and Figure 2-2.

Figure 2-1. TI Standard DSP QM Development Process and ISO 26262 Compliant Process (1 of 2)

Overview www.ti.com

Figure 2-2. TI Standard DSP QM Development Process and ISO 26262 Compliant Process (2 of 2)

## Product Safety Architecture and User Requirements

#### 3.1 Safety Function Overview

Assume a useful lifetime, based on experience. The failure rate stated in the FMEDA only applies within the useful lifetime of the component. Beyond the useful lifetime, the result of the probabilistic calculation method is therefore meaningless, because the probability of failure significantly increases with time. The useful lifetime is highly dependent on the subsystem and its operating conditions.

This assumption of a constant failure rate is based on the bathtub curve.

The TDA3x does not have any significant factors that are known to limit the useful lifetime. A 10-year useful lifetime can be assumed as a conservative measure. The manufacturer of a safety product using the TDA3x device must determine any useful lifetime limitations of other components used in the product design and disclose them in their product specific FMEDA and user manual.

When experience indicates a shorter useful lifetime than indicated in this section, use the number based on actual experience.

#### 3.2 Electrical Specifications and Environment Limits

The Recommended Operating Conditions section in the TDA3x Data Manual and the PRCM Subsystem Environment section in the TDA3x TRM specify the environmental conditions.

The user must ensure these constraints are kept. Only the Q version device should be considered in the Automobile industry.

#### 3.3 Mechanical Environment Constraints

The constraints on mechanics, humidity, and temperature in the reflow oven are stated in AEC-Q100 Rev G. The user must ensure these constraints are kept.

#### 3.4 Operating Frequency Limits

The Operating Performance Points section in the TDA3x Data Manual specifies the operating performance point for processor clocks and device core clocks. The user must ensure these constraints are kept.

#### 3.5 Other Foreseeable Environment Disturbances

#### Radiation

All the soft error rate (SER) calculations in the FMEDA are based on the NYC sea-level cosmic particles and ultra-low alpha emission package. The soft error caused by the cosmic particles must be reevaluated if this product applies to a higher altitude. If necessary for your product safety analysis, contact your TI sales representative for more details on failure rates at higher altitudes. This product is not allowed to be used in outer space safety applications. Failures due to protons and other heavy nuclei must be considered in outer space. All TI failure rates driven by alpha particles are based upon the use of an ultra-low alpha mold compound in packaging (<0.002 alpha / (cm2hr)).

#### EM immunity

The ESD tolerance of this product is documented in the Absolute Maximum Ratings section of the TDA3x Data Manual. Any ESD event higher than this limit may cause permanent damage to the IC. The user must implement measures to prevent ESD events higher than the ESD tolerance limit. This product should not be exposed under any high frequency (<1 MHz) electric field larger than 400 V/m or any magnetic field larger than 1.07 A/m. Exposure to such a field may cause communication interrupt, soft error, hard error (can be recovered by a power cycle), or permanent damage to the IC. The user

must implement shielding, grounding, filtering, or other methods to ensure the electromagnetic field strength is under the limits previously mentioned.

#### 3.6 Safety Application Overview

The TDA3x device is intended for use in a number of safety-critical automotive applications, such as:

- Front camera analytics system

- Rear view camera analytics system

- Surround view system

- Radar system

- Radar and camera fusion processing system

- · Driver monitoring system

- · Camera mirror replacement system

- And more

The purpose of this overview is to help you as a customer use the diagnostic features available in TDA3x silicon and supporting software, and achieve the required system-level ASIL performance rating. The figures below illustrate how the available sensors and varied integrations of supporting logic can result in multiple device interfaces, which must be considered safety critical to comprehend all common system implementations.

Figure 3-1 shows how a front camera analytics system can be realized using the TDA3x device.

Figure 3-1. Front Camera Analytics System Block Diagram

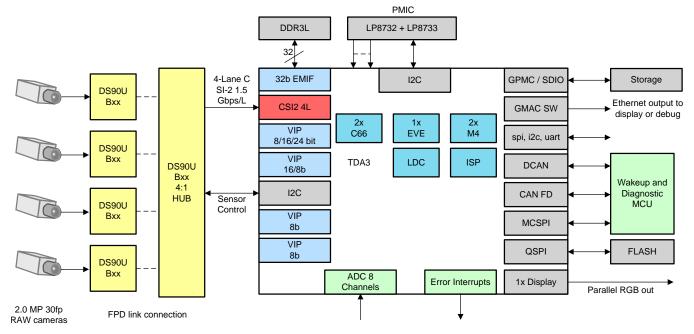

Figure 3-2 shows how a driver monitoring system could be realized using the TDA3x device.

Figure 3-2. Driver Monitoring System Block Diagram

Figure 3-3 shows how a surround view system or CMS (Camera Mirror System) could be realized using the TDA3x device. A camera mirror system typically does not use fisheye lenses, and may require higher frame rates of video. The CMS system also typically uses 1 or 2 cameras, unlike the surround view system that requires 4.

Figure 3-3. Surround View and Camera Mirror System Conceptual Block Diagram

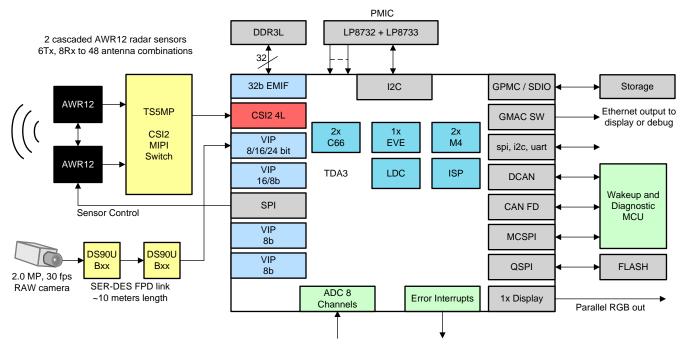

Figure 3-4 shows how a radar and camera fusion processing system can be realized using the TDA3x device. If all the radar (AWR1x) and camera devices except one AWR1x are removed from Figure 3-4, then it is a simple example of an MRR or LRR radar processing system.

Figure 3-4. Radar and Camera Fusion Block Diagram

#### 3.7 Derivation of Technical Safety Concept Based on Identified Safety Goals

System integrators are responsible for the safety analysis at the item level for all systems. This analysis includes identification of the safety goals through formal HARA (HAzard and Risk Analysis) methods. Using severity, exposure, and controllability factors, hazardous events can be assigned ASIL levels and safety goals can be derived. When safety goals are identified, fail modes that can potentially violate the safety goals must be identified. This typically creates a functional safety concept where software- or hardware-based detection mechanisms must be designed and assigned to detect violation of the safety goals, as a result of the variety of fail modes that have been identified.

This analysis does not lay any claim toward thoroughness or comprehensive detailing of failure types that may be systematic or otherwise. As a customer and system designer, you must ensure thorough safety analysis, development of the required safety concept, and assessment of applicability of any recommendations in the safety manual, FMEDA, or any other TI document, to achieve a robustness and high ASIL rating for your part.

#### 3.7.1 Front Camera Analytics System (FCA)

Such analysis may lead to identification of some of the following sample safety goals and fail modes for FCA system. Table 3-1 lists the ways in which a typical technical safety concept may lead to identification of certain modules on the processor as safety critical.

Table 3-1. FCA Analytics

| Sample Safety Goal / Identified ASIL Level                              | Potential Transient Fail Modes That<br>May Violate the Safety Goal   | Technical Safety Concept Derivation to Detect Safety Goal Violation                                                                          |

|-------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                         | Obstructed camera lens                                               | Monitor mechanical obstructions                                                                                                              |

|                                                                         | Power supply failure, Temperature beyond allowed limits, clock drift | Monitor voltage, clock, temperature                                                                                                          |

| Lane detection works properly to identify                               | Processor computation failure                                        | Monitor software execution of the algorithms                                                                                                 |

| lanes                                                                   | Processor lockout                                                    | Implement time-out mechanisms                                                                                                                |

|                                                                         | Message corruption for lane detect                                   | Wrap critical messages with signatures                                                                                                       |

|                                                                         | Audio warning system fails                                           | Feedback to the system based on speakers/mic that is synchronized with the lane detection system                                             |

|                                                                         | Obstructed camera lens                                               | Monitor mechanical obstructions                                                                                                              |

|                                                                         | Power supply failure, temperature beyond allowed limits, clock drift | Monitor voltage, clock, temperature                                                                                                          |

| Automatic emergency braking system does not work in case of an imminent | Processor computation failure                                        | Monitor software execution of the algorithms                                                                                                 |

| pedestrian collision / ASIL xx                                          | Processor lockout                                                    | Implement time-out mechanisms                                                                                                                |

| The system does not activate false alarms.                              | Message corruption for lane detect                                   | Wrap critical messages with signatures                                                                                                       |

|                                                                         | Audio warning system fails                                           | Feedback to the system based on<br>speakers/mic that is synchronized with the<br>lane detection system (in case of a<br>warning-only system) |

Based on such an analysis, in general the following components in Table 3-2 may be considered safety critical in this safety analysis for the front camera analytics system for the TDA3x device. The user must perform a detailed analysis based on the actual system implementation, device TRM, and FMEDA.

**Table 3-2. Front Camera Safety-Critical Components**

| Hierarchical Part Level | Safety-Related Element |  |

|-------------------------|------------------------|--|

| Mission - Digital SRAM  |                        |  |

| ADCSS                   | Yes                    |  |

| DCAN1                   | Yes                    |  |

| DEBUGSS_hp              | No                     |  |

| DEBUGSS_hd              | No                     |  |

| MMC                     | No                     |  |

| TESOC                   | No                     |  |

| BENELLI unicache_data   | Yes                    |  |

| BENELLI unicache_tag    | Yes                    |  |

| BENELLI L2              | Yes                    |  |

| MCAN                    | Yes                    |  |

| OCMC                    | Yes                    |  |

| OCP_WP_NOC              | No                     |  |

| GMAC_hp                 | No                     |  |

| GMAC_hd                 | No                     |  |

| UART1                   | No                     |  |

| UART2                   | No                     |  |

| UART3                   | No                     |  |

| DSS                     | No                     |  |

| ISS_hp                  | Yes                    |  |

| ISS_hd                  | Yes                    |  |

| EDMA tpcc               | Yes                    |  |

Table 3-2. Front Camera Safety-Critical Components (continued)

| Hierarchical Part Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Safety-Related Element                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| EDMA tptc1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Yes                                     |

| EDMA tptc2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Yes                                     |

| VIP_hp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                      |

| VIP_hd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                      |

| EVE dmem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Yes                                     |

| EVE ibuf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Yes                                     |

| EVE wbuf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Yes                                     |

| EVE pcache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Yes                                     |

| EVE pacahe_tag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Yes                                     |

| EVE edma tpcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Yes                                     |

| EVE edma tptc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Yes                                     |

| TURING1 edma tpcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Yes                                     |

| TURING1 edma tptc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Yes                                     |

| TURING1 L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Yes                                     |

| TURING1 L1D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Yes                                     |

| TURING1 L1P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Yes                                     |

| TURING1 umc/pmc/dmc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Yes                                     |

| TURING2 edma tpcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Yes                                     |

| TURING2 edma tptc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Yes                                     |

| TURING2 L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Yes                                     |

| TURING2 L1D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Yes                                     |

| TURING2 L1P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Yes                                     |

| TURING2 umc/pmc/dmc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Yes                                     |

| Mission - Digital Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |

| i_adas_io_pad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Yes                                     |

| u_vd_core_logic.ADCSS_inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Yes                                     |

| and and large ATD AOVAIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |

| u_vd_core_logic.ATB_ASYNC_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No                                      |

| u_vd_core_logic.ATB_ASYNC_<br>u_vd_core_logic.CAMERARX_inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No<br>Yes                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |

| u_vd_core_logic.CAMERARX_inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Yes                                     |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Yes<br>Yes                              |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Yes<br>Yes<br>Yes                       |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Yes Yes Yes Yes                         |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Yes Yes Yes Yes Yes Yes                 |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst                                                                                                                                                                                                                                                                                                                                                                                                                                      | Yes Yes Yes Yes Yes Yes Yes             |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst                                                                                                                                                                                                                                                                                                                                                                                                      | Yes Yes Yes Yes Yes Yes Yes Yes Yes     |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst u_vd_core_logic.DAC_inst                                                                                                                                                                                                                                                                                                                                                                             | Yes Yes Yes Yes Yes Yes Yes Yes Yes No  |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst u_vd_core_logic.DAC_inst u_vd_core_logic.DCAN1_inst                                                                                                                                                                                                                                                                                                                                                  | Yes Yes Yes Yes Yes Yes Yes Yes No Yes  |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst u_vd_core_logic.DAC_inst u_vd_core_logic.DCAN1_inst u_vd_core_logic.DCC1_inst                                                                                                                                                                                                                                                                                                                        | Yes |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst u_vd_core_logic.DAC_inst u_vd_core_logic.DCAN1_inst u_vd_core_logic.DCC1_inst u_vd_core_logic.DCC2_inst                                                                                                                                                                                                                                                                                              | Yes |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst u_vd_core_logic.DAC_inst u_vd_core_logic.DCAN1_inst u_vd_core_logic.DCC1_inst u_vd_core_logic.DCC2_inst u_vd_core_logic.DCC3_inst                                                                                                                                                                                                                                                                    | Yes |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst u_vd_core_logic.DAC_inst u_vd_core_logic.DCC1_inst u_vd_core_logic.DCC2_inst u_vd_core_logic.DCC3_inst u_vd_core_logic.DCC3_inst u_vd_core_logic.DCC4_inst                                                                                                                                                                                                                                           | Yes |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst u_vd_core_logic.DAC_inst u_vd_core_logic.DCC1_inst u_vd_core_logic.DCC2_inst u_vd_core_logic.DCC3_inst u_vd_core_logic.DCC4_inst u_vd_core_logic.DCC4_inst u_vd_core_logic.DCC4_inst u_vd_core_logic.DCC5_inst                                                                                                                                                                                       | Yes |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst u_vd_core_logic.DAC_inst u_vd_core_logic.DCAN1_inst u_vd_core_logic.DCC1_inst u_vd_core_logic.DCC2_inst u_vd_core_logic.DCC3_inst u_vd_core_logic.DCC4_inst u_vd_core_logic.DCC5_inst u_vd_core_logic.DCC5_inst u_vd_core_logic.DCC5_inst u_vd_core_logic.DCC6_inst                                                                                                                                  | Yes |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst u_vd_core_logic.DAC_inst u_vd_core_logic.DCAN1_inst u_vd_core_logic.DCC1_inst u_vd_core_logic.DCC2_inst u_vd_core_logic.DCC3_inst u_vd_core_logic.DCC3_inst u_vd_core_logic.DCC4_inst u_vd_core_logic.DCC5_inst u_vd_core_logic.DCC5_inst u_vd_core_logic.DCC6_inst u_vd_core_logic.DCC6_inst u_vd_core_logic.DCC7_inst u_vd_core_logic.DESUGSS_ATCLK_mdp_inst u_vd_core_logic.DEBUGSS_ICLK_mdp_inst | Yes |

| u_vd_core_logic.CAMERARX_inst u_vd_core_logic.CM_CORE_AON_inst u_vd_core_logic.CM_CORE_inst u_vd_core_logic.COUNTER_32K_inst u_vd_core_logic.CTRL_MODULE_CORE_inst u_vd_core_logic.CTRL_MODULE_WKUP_inst u_vd_core_logic.CUST_EFUSE_inst u_vd_core_logic.DAC_inst u_vd_core_logic.DCC1_inst u_vd_core_logic.DCC1_inst u_vd_core_logic.DCC2_inst u_vd_core_logic.DCC3_inst u_vd_core_logic.DCC4_inst u_vd_core_logic.DCC5_inst u_vd_core_logic.DCC5_inst u_vd_core_logic.DCC6_inst u_vd_core_logic.DCC6_inst u_vd_core_logic.DCC6_inst u_vd_core_logic.DCC7_inst u_vd_core_logic.DCC7_inst u_vd_core_logic.DCC7_inst                           | Yes |

Table 3-2. Front Camera Safety-Critical Components (continued)

| Hierarchical Part Level                          | Safety-Related Element |

|--------------------------------------------------|------------------------|

| u_vd_core_logic.DPLL_CORE_inst                   | Yes                    |

| u_vd_core_logic.DPLL_DDR_inst                    | Yes                    |

| u_vd_core_logic.DPLL_DSP_inst                    | Yes                    |

| u_vd_core_logic.DPLL_GMAC_inst                   | Yes                    |

| u_vd_core_logic.DPLL_PER_inst                    | Yes                    |

| u_vd_core_logic.EMIF1_inst                       | Yes                    |

| u_vd_core_logic.ESM_inst                         | Yes                    |

| u_vd_core_logic.GPIO1_inst                       | Yes                    |

| u_vd_core_logic.GPIO2_inst                       | Yes                    |

| u_vd_core_logic.GPIO3_inst                       | Yes                    |

| u_vd_core_logic.GPIO4_inst                       | Yes                    |

| u_vd_core_logic.HSDIVIDER_                       | Yes                    |

| u_vd_core_logic.l2ASYNC_                         | Yes                    |

| u_vd_core_logic.l2C1_inst                        | Yes                    |

| u_vd_core_logic.l2C2_inst                        | Yes                    |

| u_vd_core_logic.ICEMELTER_inst                   | No                     |

| u_vd_core_logic.IEEE1500_2_OCP_inst              | No                     |

| u_vd_core_logic.INTELLIPHY_EMIF1_inst            | Yes                    |

| u_vd_core_logic.ISS_ATB_async_bridge_m_inst      | No                     |

| u_vd_core_logic.L4_WKUP_inst                     | Yes                    |

| u_vd_core_logic.MCASP1_inst                      | Yes                    |

| u_vd_core_logic.MCSPI1_inst                      | Yes                    |

| u_vd_core_logic.MCSPI2_inst                      | Yes                    |

| u_vd_core_logic.MCSPI3_inst                      | Yes                    |

| u_vd_core_logic.MCSPI4_inst                      | Yes                    |

| u_vd_core_logic.MMC_inst                         | No                     |

| u_vd_core_logic.MMC_mdp_inst                     | No                     |

| u_vd_core_logic.PRM_inst                         | Yes                    |

| u_vd_core_logic.RTI1_inst                        | Yes                    |

| u_vd_core_logic.RTI2_inst                        | Yes                    |

| u_vd_core_logic.RTI3_inst                        | Yes                    |

| u_vd_core_logic.RTI4_inst                        | Yes                    |

| u_vd_core_logic.RTI5_inst                        | Yes                    |

| u_vd_core_logic.SC_PWR_CLK_DIV_IO_SC_pd_         | Yes                    |

| u_vd_core_logic.SMARTREFLEX_CORE_inst            | Yes                    |

| u_vd_core_logic.SMARTREFLEX_DSPEVE_inst          | Yes                    |

| u_vd_core_logic.T2ASYNC_CM_CORE_                 | Yes                    |

| u_vd_core_logic.T2ASYNC_L3_                      | Yes                    |

| u_vd_core_logic.T2ASYNC_L4_                      | Yes                    |

| u_vd_core_logic.T2ASYNC_OCP_L4_                  | Yes                    |

| u_vd_core_logic.T2ASYNC_PRM_TO_L3_               | Yes                    |

| u_vd_core_logic.TESOC_                           | Yes                    |

| u_vd_core_logic.TIMER1_inst                      | Yes                    |

| u_vd_core_logic.TOP_SSYNC_PBIST_                 | No                     |

| u_vd_core_logic.TOP_SYNC_PBIST_                  | No                     |

| u_vd_core_logic.adas_ddr_bscan_inst              | No                     |

| u_vd_core_logic.adas_efuse_autoload_handler_inst | No                     |

Table 3-2. Front Camera Safety-Critical Components (continued)

| Hierarchical Part Level                  | Safety-Related Element |

|------------------------------------------|------------------------|

| u_vd_core_logic.dftss_adas_low_inst      | No                     |

| u_vd_core_logic.dma_xbar_inst            | Yes                    |

| u_vd_core_logic.i_adas_io_bsr            | Yes                    |

| u_vd_core_logic.intelliphy_              | Yes                    |

| u_vd_core_logic.ipu_core_reset_          | Yes                    |

| u_vd_core_logic.tesoc_inst               | Yes                    |

| u_vd_core_logic.test_glue_adas_inst      | Yes                    |

| u_vd_core_logic.testcm_adas_wrap_inst    | Yes                    |

| u_vd_core_logic.top_cdr_dcdr_inst        | No                     |

| u_vd_core_logic.u_sc_L3                  | Yes                    |

| u_vd_core_logic.u_top_et_                | No                     |

| u_sc_common.DCAN2_                       | Yes                    |

| u_sc_common.DFT_                         | No                     |

| u_sc_common.ELM_inst                     | No                     |

| u_sc_common.GPMC_inst                    | No                     |

| u_sc_common.HEAD_POS_FOR_ASYNC_BRIDGE_   | Yes                    |

| u_sc_common.l2ASYNC_                     | Yes                    |

| u_sc_common.L4_CFG_inst                  | Yes                    |

| u_sc_common.L4_PER2_inst                 | Yes                    |

| u_sc_common.L4_PER3_inst                 | Yes                    |

| u_sc_common.L4_PER_inst                  | Yes                    |

| u_sc_common.MAILBOX1_inst                | Yes                    |

| u_sc_common.MAILBOX2_inst                | Yes                    |

| u_sc_common.OCMC_DMLED_                  | No                     |

| u_sc_common.OCMC_RAM1_                   | Yes                    |

| u_sc_common.OCP_WP_NOC_                  | No                     |

| u_sc_common.PWMSS1_inst                  | Yes                    |

| u_sc_common.QSPI_inst                    | Yes                    |

| u_sc_common.SC_COMMON_PBIST_             | No                     |

| u_sc_common.SC_PWR_CLK_DIV_SC_COMMON_pd_ | Yes                    |

| u_sc_common.SPINLOCK_inst.SPINLOCK_      | Yes                    |

| u_sc_common.TIMER2_inst                  | Yes                    |

| u_sc_common.TIMER3_inst                  | Yes                    |

| u_sc_common.TIMER4_inst                  | Yes                    |

| u_sc_common.TIMER5_inst                  | Yes                    |

| u_sc_common.TIMER6_inst                  | Yes                    |

| u_sc_common.TIMER7_inst                  | Yes                    |

| u_sc_common.TIMER8_inst                  | Yes                    |

| u_sc_common.UART1_                       | No                     |

| u_sc_common.UART2_                       | No                     |

| u_sc_common.UART3_                       | No                     |

| u_sc_common.sc_common_cdr_dcdr_inst      | No                     |

| u_sc_common.u_GMAC.GMAC_                 | Yes                    |

| u_sc_common.u_sc_common_et_              | No                     |

| u_sc_common.ATL_inst                     | No                     |