# **KeyStone Architecture Security Accelerator (SA)**

# **User Guide**

Literature Number: SPRUGY6B January 2013

# **Release History**

| Release  | Date         | Description/Comments                                                                                                                                           |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPRUGY6B | January 2013 | • Added addition engine IDs within Appendix. (Page A-3)                                                                                                        |

|          |              | • Added Keystone II note to SA function block diagram figure in Intro. (Page 1-6)                                                                              |

|          |              | • Added aditional bits for second authentication and encryption modules in CMD_STATUS. (Page 4-3)                                                              |

|          |              | • Added features not supported in intruduction. (Page 1-4)                                                                                                     |

|          |              | • Added Tru Random Number generator KeyStone II details in features. (Page 1-4)                                                                                |

|          |              | • Added KeyStone II SCCTL Register structure in Appendix. (Page A-8)                                                                                           |

|          |              | • Added details for in SRTP KeyStone II Devices (Page 3-8)                                                                                                     |

|          |              | Added KeyStone II details to SA Engine Processing (Page 2-8)                                                                                                   |

|          |              | • Added KeyStone II specifics to SRTP examples (Page 3-8)                                                                                                      |

|          |              | • Added mention of KeyStone II engine to Protocol Descriptions. (Page 2-5)                                                                                     |

|          |              | • Added Specifics for IPsec in KeyStone II devices at IPsec Examples. (Page 3-3)                                                                               |

|          |              | • Included SRTP KeyStone II Updates (Page 2-21)                                                                                                                |

|          |              | • Put KeyStone II specification in IPSEC Use (Page 2-11)                                                                                                       |

| SPRUGY6A | July 2012    | • Added AES XCBC authentication mode support to IPsec ESP. (Page 2-15)                                                                                         |

|          |              | • Added AES XCBC support for data mode. (Page 2-9)                                                                                                             |

|          |              | • Added AES XCBC support for IPsec AH. (Page 2-12)                                                                                                             |

|          |              | • Added DES CBC cipher support for the encryption and decryption engine. (Page 1-4)                                                                            |

|          |              | • Added DES CBC support data mode. (Page 2-8)                                                                                                                  |

|          |              | • Added DES CBC support for the IPsec ESP protocol. (Page 2-15)                                                                                                |

|          |              | • Added information to PHP2 to state that it is used with the Air Cipher Engine for 3GPP operations. (Page 1-5)                                                |

|          |              | • Added note to reference the SA LLD documentation for the full list of channel interface APIs. (Page 2-3)                                                     |

|          |              | • Added note to reference the SA LLD documentation for the full list of common interface APIs. (Page 2-3)                                                      |

|          |              | • Added support for AES XCBC authentication. (Page 1-4)                                                                                                        |

|          |              | • Updated 3GPP Air Cipher Channel SA LLD APIs table to remove information that is duplicated in the global Channel API table. (Page 2-6)                       |

|          |              | • Updated Data Mode Channel SA LLD APIs table to remove information that is duplicated in the global Channel API table. (Page 2-10)                            |

|          |              | • Updated IPsec AH Channel SA LLD APIs table to remove information that is duplicated in the global Channel API table. (Page 2-12)                             |

|          |              | • Updated IPsec ESP Channel SA LLD APIs table to remove information that is duplicated in the global Channel API table. (Page 2-16)                            |

|          |              | • Updated SRTCP Channel SA LLD APIs table to remove information that is duplicated in the global Channel API table. (Page 2-19)                                |

|          |              | • Fixed typo in data-mode authentication section. Previously, it erroneously listed the authentication modes as being under the IPsec ESP protocol. (Page 2-9) |

|          |              | • Removed FIPS 140-1 compliance statement from Industry Standard(s) Compliance Statement section (Page 1-6)                                                    |

|          |              | • Removed FIPS 140-1 compliance statement from the True Random number generator in the Features section (Page 1-4)                                             |

|          |              | • Removed note that AES CMAC authentication is not supported. This functionality has been added to the SA LLD. (Page 2-6)                                      |

|          |              | • Changed PS_FLAGS to error flags (Page 2-30)                                                                                                                  |

| SPRUGY6  | May 2011     | Initial Release                                                                                                                                                |

www.ti.com Contents

# **Contents**

|           | Release History. ø-ii List of Tables ø-vii List of Figures ø-ix List of Procedures ø-xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | PrefaceØ-xiiiAbout This Manual.ø-xiiiNotational Conventions.ø-xiiiRelated Documentation from Texas Instruments.ø-xivTrademarks.ø-xiv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter 1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | Introduction 1-1 1.1 Purpose of the Peripheral1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | 1.2 Terminology Used in This Document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Chapter 2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | Architecture       2-1         2.1 Clock Control       2-2         2.2 Memory Map       2-2         2.3 Security Accelerator Programming with the Low-Level Driver       2-2         2.3.1 SA LLD Common Interface APIs       2-2         2.3.2 SA LLD Channel Interface APIs       2-3         2.4 Protocol Descriptions       2-5         2.4.1 3GPP Air Cipher       2-5         2.4.1.1 SA Hardware Engine Utilization       2-5         2.4.1.2 Supported Cipher Modes       2-5         2.4.1.3 Supported Authentication Modes       2-6         2.4.1.4 Protocol-Specific SA LLD Channel APIs       2-6         2.4.1.5 Descriptor Protocol-Specific Information Section       2-7                                                                                                                                                                                                                                                                                     |

|           | 2.4.2 Data-Mode       2-7         2.4.2.1 SA Data Processing Engine Utilization       2-7         2.4.2.2 Supported Cipher Modes       2-8         2.4.2.3 Supported Authentication Modes       2-9         2.4.2.4 Protocol-Specific SA LLD Channel APIs       2-10         2.4.2.5 Descriptor Protocol-Specific Information Section       2-10         2.4.3 IPsec AH       2-11         2.4.3.1 SA Hardware Engine Utilization       2-11         2.4.3.2 Supported Cipher Modes       2-12         2.4.3.3 Supported Authentication Modes       2-12         2.4.3.4 Protocol-Specific SA LLD Channel APIs       2-13         2.4.3 Descriptor Protocol-Specific Information Section       2-13         2.4.4 IPsec ESP       2-15         2.4.4.1 SA Hardware Engine Utilization       2-15         2.4.4.2 Supported Cipher Modes       2-15         2.4.4.3 Supported Authentication Modes       2-15         2.4.4.4 Protocol-Specific SA LLD Channel APIs       2-16 |

www.ti.com

| 2.4.4.5 Descriptor Protocol-Specific Information Section                       |       |

|--------------------------------------------------------------------------------|-------|

| 2.4.5 SRTCP                                                                    |       |

| 2.4.5.1 SA Hardware Engine Utilization      2.4.5.2 Supported Cipher Modes     |       |

| 2.4.5.3 Supported Ciprier Modes                                                |       |

| 2.4.5.4 Protocol-Specific SA LLD Channel APIs                                  |       |

| 2.4.6 SRTP                                                                     |       |

| 2.4.6.1 SA Hardware Engine Utilization                                         | 2-20  |

| 2.4.6.2 Supported Cipher Modes                                                 |       |

| 2.4.6.3 Supported Authentication Modes                                         |       |

| 2.4.6.4 Protocol-Specific SA LLD Channel APIs                                  |       |

| 2.4.6.5 Descriptor Protocol-Specific Information Section                       |       |

| 2.6 Descriptor Software Information Words                                      |       |

| 2.7 Security Contexts                                                          |       |

| 2.7.1 Generating Security Contexts.                                            |       |

| 2.7.2 Security Context Memory Allocation                                       |       |

| 2.8 Security Context Cache                                                     |       |

| 2.8.1 Security Context Fetch                                                   |       |

| 2.8.2 Security Context Tiers                                                   |       |

| 2.8.3 Security Context Identification and Security Context Pointers            |       |

| 2.8.4 Security Context Cache Control Flags                                     |       |

| 2.8.5 Context Cache Algorithm                                                  |       |

| 2.9 Packet Header Processor Modules                                            |       |

| 2.9.1 Command Label Generation.         2.9.2 Authentication Tag Verification. |       |

| 2.9.3 Authentication Tag Insertion                                             |       |

| 2.9.4 Packet Replay Protection                                                 |       |

| 2.9.5 PHP1                                                                     |       |

| 2.9.5.1 Processing IPsec AH packets with PHP1                                  | 2-30  |

| 2.9.5.2 Processing IPsec ESP Packets with PHP1                                 | 2-30  |

| 2.9.6 PHP2                                                                     |       |

| 2.9.6.1 Processing SRTP Packets with PHP2                                      |       |

| 2.9.6.2 Processing Air Cipher packets with PHP2                                |       |

| 2.9.7 Procedure for Downloading Firmware onto the PHP PDSPs                    |       |

| 2.10 Encryption and Decryption Engine                                          |       |

| 2.12 Air Cipher Engine                                                         |       |

| 2.13 Public Key Accelerator                                                    |       |

| 2.13.1 Programming Considerations                                              |       |

| 2.13.2 Functional Description PKA Components                                   |       |

| 2.13.3 Configuration and Status Registers                                      |       |

| 2.13.3.1 PKA_APTR, PKA_BPTR, PKA_CPTR, PKA_DPTR Registers                      | 2-36  |

| 2.13.3.2 PKA_ALENGTH and PKA_BLENGTH Registers                                 |       |

| 2.13.3.3 PKA_SHIFT Register                                                    |       |

| 2.13.3.4 PKA_FUNCTION Register.                                                |       |

| 2.13.3.5 PKA_COMPARE Register                                                  |       |

| 2.13.3.7 PKA_DIVMSW Register                                                   |       |

| 2.13.4 Vector RAM.                                                             |       |

| 2.13.4.1 RAM Size Requirements                                                 |       |

| 2.13.5 PKA Input Requirements                                                  | 2-39  |

| 2.13.6 Result Vector RAM Allocation.                                           |       |

| 2.14 True Random Number Generator                                              |       |

| 2.14.1 Programming Considerations                                              |       |

| 2.14.2 Initial Latency after Reset.                                            |       |

| 2.14.3 Random Number Generation                                                | 2-41  |

|                                                                                | / -41 |

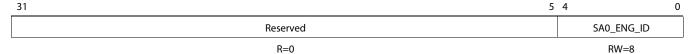

Contents www.ti.com 2.15 Initializing the SA Using the SA LLD ......2-42 2.16 SA LLD Channel Initialization and Configuration ......2-42 2.17 Sending Packets to the SA for Processing......2-43 Chapter 3 Data Flow Examples 3-1 Chapter 4 4-1 Registers 4.1 Security Accelerator System Register Region.......4-2 4.1.1 Peripheral and Version Identification Register (PID)........4-2 4.1.2 Command Status Register (CMD\_STATUS) .......4-3 4.1.6 SA0 Next Engine Identification Register (SA0\_ENG\_ID) .......4-6 4.2 Context Cache Register Region ......4-7 4.2.1 Context Cache Control Register (CTXCACH\_CTRL) .......4-7 4.2.2 Context Cache Security Context Pointer Register (CTXCACH\_SC\_PTR).......4-8 4.2.3 Context Cache Security Context Identification Register (CTXCACH\_SC\_ID) .......4-8 4.3 PHP PDSP Control and Status Registers .......4-11

|            |                                                                                    | www.ti.com |

|------------|------------------------------------------------------------------------------------|------------|

|            | 4.3.8 PDSP Constant Table Programmable Pointer Register 1 (PDSP_POINTER1)          | 4-15       |

|            | 4.4 Public Key Accelerator Register Region                                         | 4-16       |

|            | 4.4.1 Operand A Pointer Register (PKA_APTR)                                        | 4-16       |

|            | 4.4.2 Operand B Pointer Register (PKA_BPTR)                                        |            |

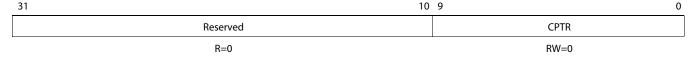

|            | 4.4.3 Operand C Pointer Register (PKA_CPTR)                                        |            |

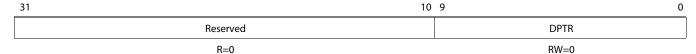

|            | 4.4.4 Operand D Pointer Register (PKA_DPTR)                                        | 4-18       |

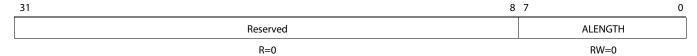

|            | 4.4.5 Operand A Length Register (PKA_ALENGTH)                                      | 4-18       |

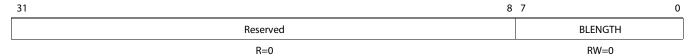

|            | 4.4.6 Operand B Length Register (PKA_BLENGTH)                                      | 4-19       |

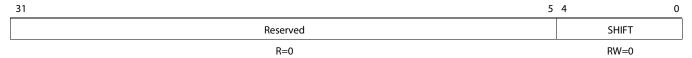

|            | 4.4.7 Shift Operation Register (PKA_SHIFT)                                         |            |

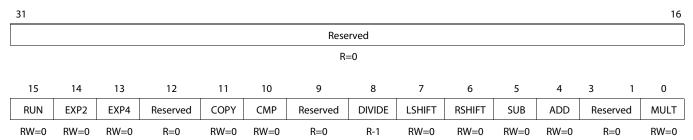

|            | 4.4.8 Function Select Register (PKA_FUNCTION)                                      |            |

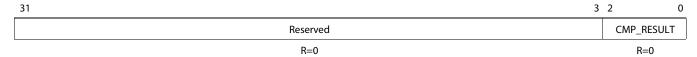

|            | 4.4.9 Compare Results Register (PKA_COMPARE)                                       |            |

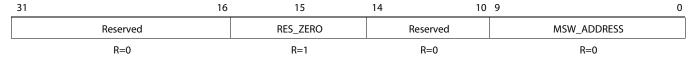

|            | 4.4.10 Result Most Significant Word Address Register (PKA_MSW)                     |            |

|            | 4.4.11 Division Remainder Most Significant Word Address Register (PKA_MSWDIV)      | 4-22       |

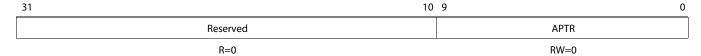

|            | 4.5 True Random Number Generator Register Region                                   |            |

|            | 4.5.1 Data Output Least Significant Word Register (TRNG_OUTPUT_L)                  |            |

|            | 4.5.2 Data Output MSW Register (TRNG_OUTPUT_H)                                     |            |

|            | 4.5.3 Status Register (TRNG_STATUS)                                                |            |

|            | 4.5.4 Interrupt Acknowledge Register (TRNG_INTACK)                                 |            |

|            | 4.5.5 Control Register (TRNG_CONTROL)                                              |            |

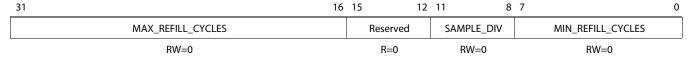

|            | 4.5.6 Configuration Register (TRNG_CONFIG)                                         | 4-26       |

|            |                                                                                    |            |

| Appendix A |                                                                                    |            |

|            | Additional Security Accelerator Details                                            | A-1        |

|            | A.1 Descriptor Software Information Word Configuration                             |            |

|            | A.1.1 Descriptor Software Information Word Configuration                           |            |

|            | A.1.1 Descriptor Software Information Word 0                                       |            |

|            | A.1.3 Descriptor Software Information Word 2.                                      |            |

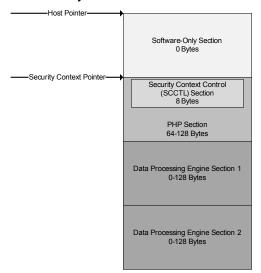

|            | A.2 Security Context Structure in Host Memory                                      |            |

|            | A.2.1 Security Context Structure in Host Memory                                    |            |

|            | A.2.2 Security Context PHP                                                         |            |

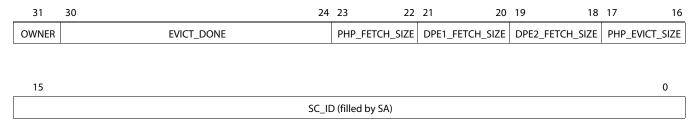

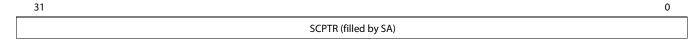

|            | A.2.2 Security Context FFIF  A.2.2.1 KeyStone   Security Context Control Structure |            |

|            | A.2.2.1 ReyStone I Security Context Control Structure                              |            |

|            | A.2.3 Security Context Data Processing Engine                                      |            |

|            | A.3 Security Context Control Flags                                                 |            |

|            |                                                                                    |            |

|            | A.3.1 Evict Flag                                                                   |            |

|            | A.3.2 Tear-Down Flag.                                                              |            |

|            | A.3.3 No Payload Flag                                                              | A-11       |

|            |                                                                                    |            |

|            | Index                                                                              | IX-1       |

www.ti.com List of Tables

# **List of Tables**

| Table 2-1  | Security Accelerator Memory Map                                              |       |

|------------|------------------------------------------------------------------------------|-------|

| Table 2-2  | SA LLD Channel Specific API Overview                                         |       |

| Table 2-3  | 3GPP Air Cipher Channel SA LLD APIs                                          |       |

| Table 2-4  | Cipher Mode to SA Data Processing Engine Mapping                             |       |

| Table 2-5  | Authentication Mode to SA Data Processing Engine Mapping                     |       |

| Table 2-6  | SA LLD Data-mode Channel APIs                                                |       |

| Table 2-7  | SA LLD IPsec AH Channel APIs                                                 |       |

| Table 2-8  | SA LLD IPsec ESP Channel APIs                                                |       |

| Table 2-9  | SA LLD SRTCP Channel APIs                                                    |       |

| Table 2-10 | SA LLD SRTP Channel APIs                                                     |       |

| Table 2-11 | PKA Status and Control Registers                                             |       |

| Table 2-12 | Functional Roles of PKA_APTR, PKA_BPTR, PKA_CPTR, and PKA_DPTR Registers     |       |

| Table 2-13 | Vector RAM Requirement for ACT Operations                                    |       |

| Table 2-14 | Supported ACTs vs. Modulus Length for 8 Kbyte Vector RAM                     |       |

| Table 2-15 | PKA Input Requirements                                                       |       |

| Table 2-16 | Minimum Memory Allocation for Result Vector                                  |       |

| Table 4-1  | Security Accelerator Register Regions                                        |       |

| Table 4-2  | Security Accelerator System Register Region                                  |       |

| Table 4-3  | Peripheral and Version Identification Register Field Descriptions            |       |

| Table 4-4  | Command Status Register Field Descriptions                                   |       |

| Table 4-5  | SA1 Port Flow Identification Register Field Descriptions                     |       |

| Table 4-6  | SA0 Port Flow Identification Register Field Descriptions                     | 4-6   |

| Table 4-7  | SA1 Next Engine Identification Register Field Descriptions                   |       |

| Table 4-8  | SA0 Next Engine Identification Register Field Descriptions                   | 4-6   |

| Table 4-9  | Context Cache Register Region                                                | 4-7   |

| Table 4-10 | Context Cache Control Register Field Descriptions.                           | 4-7   |

| Table 4-11 | Context Cache Security Context Pointer Register Field Descriptions           | 4-8   |

| Table 4-12 | Context Cache Security Context Identification Register Field Descriptions    | 4-9   |

| Table 4-13 | Register Field Descriptions                                                  | .4-10 |

| Table 4-14 | PDSP Control/Status Register Region.                                         | .4-11 |

| Table 4-15 | PDSP Control Register Field Descriptions                                     | .4-11 |

| Table 4-16 | PDSP Status Register Field Descriptions                                      | .4-12 |

| Table 4-17 | PDSP Cycle Count Register Field Descriptions                                 | .4-13 |

| Table 4-18 | PDSP Stall Count Register Field Descriptions                                 | .4-13 |

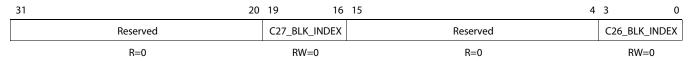

| Table 4-19 | PDSP Constant Table Block Index 0 Register Field Descriptions                |       |

| Table 4-20 | PDSP Constant Table Block Index Register 1 Field Descriptions                |       |

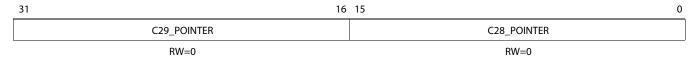

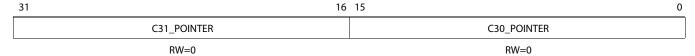

| Table 4-21 | PDSP Constant Table Programmable Pointer Register 0 Field Descriptions       | .4-15 |

| Table 4-22 | PDSP Constant Table Programmable Pointer Register 1 Field Descriptions       | .4-15 |

| Table 4-23 | Public Key Accelerator Register Region                                       | .4-16 |

| Table 4-24 | Operand A Pointer Register Field Descriptions                                | .4-16 |

| Table 4-25 | Operand B Pointer Register Field Descriptions                                | .4-17 |

| Table 4-26 | Operand C Pointer Register Field Descriptions                                | .4-17 |

| Table 4-27 | Operand D Pointer Register Field Descriptions                                | .4-18 |

| Table 4-28 | Operand D Pointer Register Field Descriptions                                | .4-18 |

| Table 4-29 | Operand D Pointer Register Field Descriptions                                | .4-19 |

| Table 4-30 | Shift Operation Register Field Descriptions                                  | .4-19 |

| Table 4-31 | Function Select Register Field Descriptions                                  |       |

| Table 4-32 | Compare Results Register Field Descriptions                                  | .4-21 |

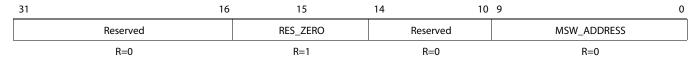

| Table 4-33 | Result Most Significant Word Address Register Field Descriptions             | .4-21 |

| Table 4-34 | Division Remainder Most Significant Word Address Register Field Descriptions | .4-22 |

| Table 4-35 | Public Key Accelerator Register Region                                       | .4-23 |

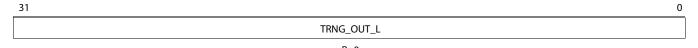

| Table 4-36 | Data Output Least Significant Word Register Field Descriptions               | .4-23 |

| Tables                                                                 | www.ti.com |

|------------------------------------------------------------------------|------------|

| ole 4-37 Data Output Most Significant Word Register Field Descriptions | 4-24       |

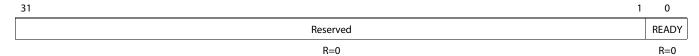

| ole 4-38 Status Register Field Descriptions                            | 4-24       |

| ole 4-39 Interrupt Acknowledge Register Field Descriptions             | 4-25       |

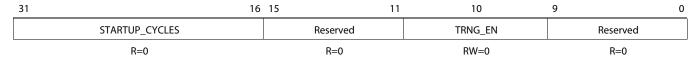

| ole 4-40 Control Register Field Descriptions                           | 4-25       |

| ole 4-41 Configuration Register Field Descriptions                     | 4-26       |

| ole A-1 Descriptor Software Info 0 Field Descriptions                  | A-2        |

| sle A-2 KeyStone I Engine ID Mapping                                   |            |

| ole A-3 KeyStone II Engine ID Mapping                                  |            |

| ole A-4 Descriptor Software Info 1 Field Descriptions                  |            |

| ole A-5 Descriptor Software Info 2 Field Descriptions                  | A-5        |

| ole A-6 Keystone I Security Context Control (SCCTL) Structure          | A-7        |

| ole A-7 Keystone II Security Context Control (SCCTL) Structure         |            |

# **List of Figures**

www.ti.com

| Figure 1-1  | Keystone I Security Accelerator Functional Block Diagram         | 1-6   |

|-------------|------------------------------------------------------------------|-------|

| Figure 2-1  | 3GPP Air Cipher Descriptor Protocol-Specific Information Diagram |       |

| Figure 2-2  | Data-Mode Descriptor Protocol-Specific Information Diagram       |       |

| Figure 2-3  | IPsec AH Descriptor Protocol-Specific Information Diagram        |       |

| Figure 2-4  | IPsec ESP Descriptor Protocol-Specific Information Diagram       |       |

| Figure 2-5  | SRTP Descriptor Protocol-Specific Information Diagram            |       |

| Figure 3-1  | 3GPP Air Cipher Encryption Example                               |       |

| Figure 3-2  | 3GPP Air Cipher Decryption Example                               |       |

| Figure 3-3  | IPsec AH Authentication Tag Generation Example                   |       |

| Figure 3-4  | IPsec AH Authentication Verification Example                     |       |

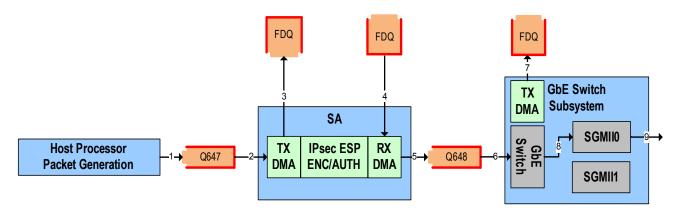

| Figure 3-5  | IPsec ESP Encryption Example                                     |       |

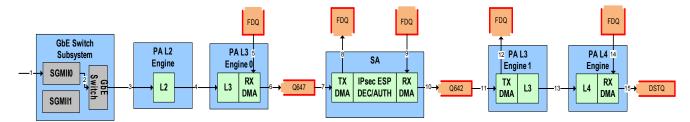

| Figure 3-6  | IPsec ESP Decryption Example                                     |       |

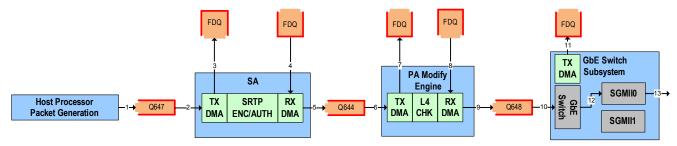

| Figure 3-7  | SRTP Encryption Example                                          |       |

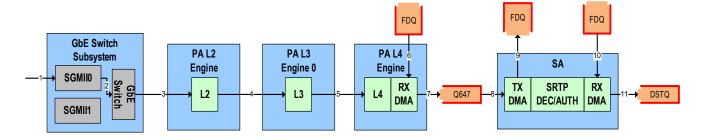

| Figure 3-8  | SRTP Decryption Example                                          |       |

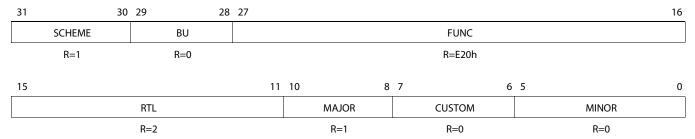

| Figure 4-1  | Peripheral and Version Identification Register                   |       |

| Figure 4-2  | Command Status Register                                          |       |

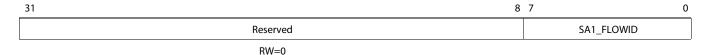

| Figure 4-3  | SA1 Port Flow Identification Register                            |       |

| Figure 4-4  | SA0 Port Flow Identification Register                            |       |

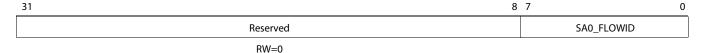

| Figure 4-5  | SA1 Next Engine Identification Register                          |       |

| Figure 4-6  | SAO Next Engine Identification Register                          |       |

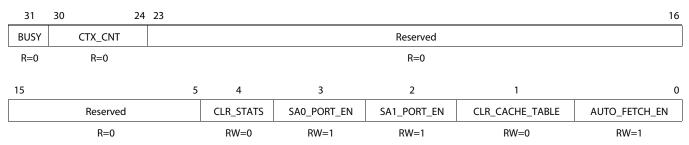

| Figure 4-7  | Context Cache Control Register                                   |       |

| Figure 4-8  | Context Cache Security Context Pointer Register                  |       |

| Figure 4-9  | Context Cache Security Context Identification Register           |       |

| Figure 4-10 | Context Cache Security Context Identification Register           |       |

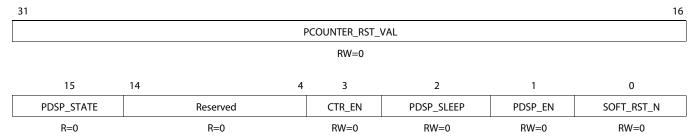

| Figure 4-11 | PDSP Control Register                                            |       |

| Figure 4-12 | PDSP Status Register                                             |       |

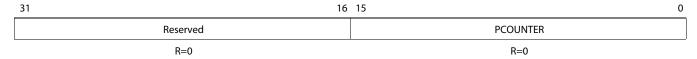

| Figure 4-13 | PDSP Cycle Count Register                                        |       |

| Figure 4-14 | PDSP Stall Count Register                                        |       |

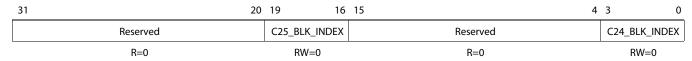

| Figure 4-15 | PDSP Constant Table Block Index 0 Register                       |       |

| Figure 4-16 | PDSP Constant Table Block Index 1 Register                       |       |

| Figure 4-17 | PDSP Constant Table Programmable Pointer 0 Register              |       |

| Figure 4-18 | PDSP Constant Table Programmable Pointer 1 Register              |       |

| Figure 4-19 | Operand A Pointer Register                                       |       |

| Figure 4-20 | Operand B Pointer Register                                       |       |

| Figure 4-21 | Operand C Pointer Register                                       |       |

| Figure 4-22 | Operand D Pointer Register                                       |       |

| Figure 4-23 | Operand A Length Register                                        |       |

| Figure 4-24 | Operand B Length Register                                        |       |

| Figure 4-25 | Shift Operation Register                                         |       |

| Figure 4-26 | Function Select Register                                         |       |

| Figure 4-27 | Compare Results Register                                         |       |

| Figure 4-28 | Result Most Significant Word Address Register                    | .4-21 |

| Figure 4-29 | Division Remainder Most Significant Word Address Register        | .4-22 |

| Figure 4-30 | Data Output Least Significant Word Register                      | .4-23 |

| Figure 4-31 | Data Output Most Significant Word Register                       | .4-24 |

| Figure 4-32 | Status Register                                                  | .4-24 |

| Figure 4-33 | Interrupt Acknowledge Register                                   | .4-25 |

| Figure 4-34 | Control Register                                                 |       |

| Figure 4-35 | Configuration Register                                           | .4-26 |

| Figure A-1  | Descriptor Software Info 0                                       | A-2   |

| Figure A-2  | Descriptor Software Info 1                                       | A-4   |

| Figure A-3  | Descriptor Software Info 2                                       | A-5   |

|             |                                                                  |       |

| List of Figures |                                           | www.ti.com |

|-----------------|-------------------------------------------|------------|

| Figure A-4      | Security Context Structure                |            |

| Figure A-5      | Security Context Control Structure Word 0 |            |

| Figure A-6      | Security Context Control Structure Word 1 | A-7        |

| Figure A-7      | Security Context Control Structure Word 0 | A-8        |

| Figure A-8      | Security Context Control Structure Word 1 | A-8        |

www.ti.com List of Procedures

# **List of Procedures**

| Procedure 2-1 | Performing an Authentication Tag Blind Patch using the PA |      |

|---------------|-----------------------------------------------------------|------|

| Procedure 2-2 |                                                           |      |

| Procedure 2-3 | Procedure for Downloading Firmware on the PHP PDSPs       |      |

| Procedure 2-4 | TRNG Example Configuration                                |      |

| Procedure 2-5 | -                                                         |      |

| Procedure 2-6 | SA LLD Channel Initialization and Configuration           | 2-42 |

| Procedure 2-7 | Sending Packets to the SA for Processing                  |      |

List of Procedures www.ti.com

# **Preface**

#### **About This Manual**

The Security Accelerator (SA) provides hardware engines to perform encryption, decryption, and authentication operations on packets for commonly supported protocols, including IPsec ESP and AH, SRTP, and Air Cipher. The SA also provides the hardware modules to assist the host in generating public keys and random numbers.

#### **Notational Conventions**

This document uses the following conventions:

- Commands and keywords are in **boldface** font.

- Arguments for which you supply values are in *italic* font.

- Terminal sessions and information the system displays are in screen font.

- Information you must enter is in **boldface screen font**.

- Elements in square brackets ([]) are optional.

Notes use the following conventions:

**Note**—Means reader take note. Notes contain helpful suggestions or references to material not covered in the publication.

The information in a caution or a warning is provided for your protection. Please read each caution and warning carefully.

**CAUTION**—Indicates the possibility of service interruption if precautions are not taken.

**WARNING**—Indicates the possibility of damage to equipment if precautions are not taken.

Preface www.ti.com

## **Related Documentation from Texas Instruments**

Multicore Navigator for KeyStone Devices User GuideSPRUGR9Network Coprocessor (NETCP) for KeyStone Devices User GuideSPRUGZ6

#### **Trademarks**

C66x is a trademark of Texas Instruments Incorporated.

All other brand names and trademarks mentioned in this document are the property of Texas Instruments Incorporated or their respective owners, as applicable.

# **Chapter 1**

# Introduction

**IMPORTANT NOTE**—The information in this document should be used in conjunction with information in the device-specific Keystone Architecture data manual that applies to the part number of your device.

- 1.1 "Purpose of the Peripheral" on page 1-2

- 1.2 "Terminology Used in This Document" on page 1-2

- 1.3 "Features" on page 1-3

- 1.4 "Functional Block Diagram" on page 1-5

- 1.5 "Industry Standard(s) Compliance Statement" on page 1-6

# 1.1 Purpose of the Peripheral

The Security Accelerator (SA) is one of the main components of the Network Coprocessor (NETCP) peripheral. The SA works together with the Packet Accelerator (PA) and the Gigabit Ethernet (GbE) switch subsystem to form a network processing solution. The purpose of the SA is to assist the host by performing security related tasks. The SA provides hardware engines to perform encryption, decryption, and authentication operations on packets for commonly supported protocols, including IPsec ESP and AH, SRTP, and Air Cipher. The SA also provides the hardware modules to assist the host in generating public keys and random numbers.

# 1.2 Terminology Used in This Document

This section defines terminology and acronyms that are used throughout this document.

| Term  | Definition                                     |

|-------|------------------------------------------------|

| 3GPP  | 3rd Generation Partnership Project             |

| AES   | Advanced Encryption Standard                   |

| СВС   | Cipher Block Chaining                          |

| ССМ   | Counter with CBC MAC                           |

| CMAC  | Cipher-based Message Authentication Code       |

| CTR   | Counter                                        |

| DES   | Data Encryption Standard                       |

| FIPS  | Federal Information Processing System          |

| GCM   | Galois Counter Mode                            |

| GMAC  | Galois Message Authentication Code             |

| НМАС  | Hashed Mac Authentication Code                 |

| IETF  | Internet Engineering Task Force                |

| IPsec | Internet Protocol security                     |

| MD5   | Message Digest 5                               |

| NIST  | National Institute of Standards and Technology |

| PDSP  | Packet data structure processor                |

| PHP   | Packet header processor                        |

| PKA   | Public key accelerator                         |

| PS    | Protocol specific                              |

| RFC   | Request for comment                            |

| RISC  | Reduced instruction set controller             |

| RTP   | Real-Time Transport Protocol                   |

| sc    | Security Context                               |

| SHA   | Secure Hash Algorithm                          |

| SRTP  | Secure Real-time Transport Protocol            |

| SSL   | Secure Socket Layer                            |

| TRNG  | True random number generator                   |

| TSL   | Transport Layer Security                       |

#### 1.3 Features

This section gives an overview of the features provided by the security accelerator.

- Protocol stack features provided:

- Provides IPsec protocol stack

- > Support transport mode for both AH and ESP processing

- > Support tunnel mode for both AH and ESP processing

- > Full header parsing and padding checks

- > Constructs initialization vector from header

- > Supports anti-replay

- > Supports true 64K bytes packet processing

- Provides SRTP protocol stack

- > Supports F8 mode of processing

- > Supports replay protection

- > Supports true 64K bytes packet processing

- Provides 3GPP protocol stack, Wireless Air cipher standard

- > AES counter

- > ECSD A5/3 key generation

- > GEA3 (GPRA) key generation

- > GSM A5/3 key generation

- > Kasumi F8

- > Snow3G

- Features provided by respective hardware modules:

- Encryption and Decryption Engine

- > 3DES CBC cipher

- AES CTR cipher

- AES CBC cipher

- AES F8 cipher

- AES XCBC authentication

- CCM cipher

- > DES CBC cipher

- GCM cipher

- Authentication Engine provides hardware modules to support keyed (HMAC) and non-keyed hash calculations:

- CMAC authentication

- > GMAC authentication

- > HMAC MD5 authentication

- > HMAC SHA1 authentication

- > HMAC SHA2 224 authentication

- > HMAC SHA2 256 authentication

- Air Cipher Engine

- AES CTR cipher

- AES CMAC authentication

- > Kasumi F8 cipher

- > Snow3G F8 cipher

- Kasumi F9 authentication

- Programmable Header Parsing module

- PDSP based header processing engine for packet parsing, algorithm control and decode

- > Carry out protocol related packet header and trailer processing

- Support null cipher and null authentication for debugging

- True Random number generator

- True (not pseudo) random number generator

- FIPS 140-1 Compliant (if KeyStone II)

- Non-deterministic noise source for generating keys, IV, etc.

- Public Key accelerator

- High performance public key engine for large vector math operation

- Supports modulus size up to 4096 bits

- Extremely useful for public key computations

- Context cache module to automatically fetch security context

#### 1.3.1 Features Not Supported

- SHA2 beyond 256

- RC4 stream cipher

- Snow3G F9 Authentication

## 1.4 Functional Block Diagram

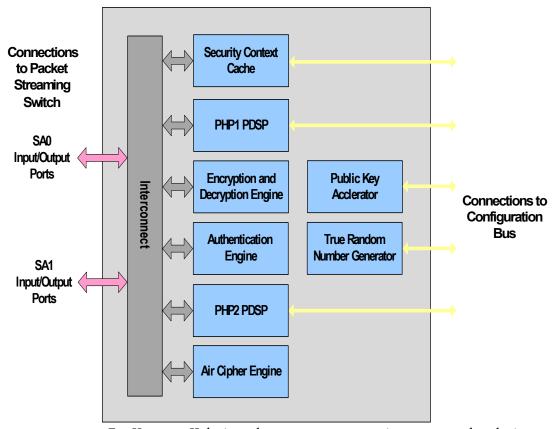

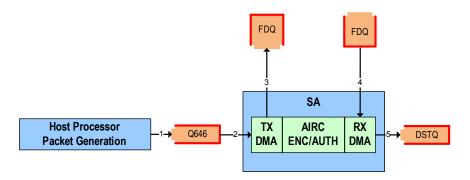

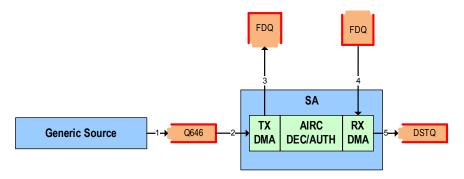

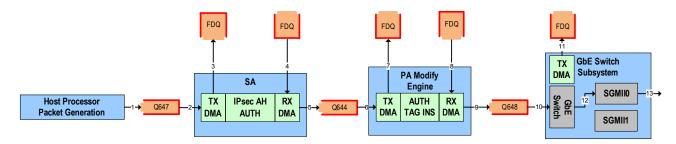

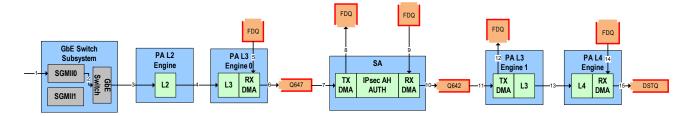

Figure 1-1 shows the Security Accelerator (SA) functional block diagram. The SA provides two ports to interface to the packet streaming switch in the Network Coprocessor (NETCP). All data packets entering and exiting the SA must use one of these two ports. The SA0 port is used for packets entering the SA from queue 647. The SA1 port is used for packets entering the SA from queue 646.

To encrypt, decrypt, and authenticate data packets, the SA provides the following modules:

- **Security Context Cache**: fetches and caches the security contexts that are used by the SA hardware modules to encrypt, decrypt, and authenticate data packets.

- Packet Header Processor 1 (PHP1) PDSP: primarily used with the encryption and decryption engine and the authentication engine to perform IPsec operations.

- Encryption and Decryption Engine: used with PHP1 and PHP2 to perform encryption and decryption operations. PHP1 uses this engine for IPsec operations, while PHP2 uses this engine for SRTP operations. This module can also be used with data-mode packets without engaging the PHPs.

- **Authentication Engine**: used with PHP1 and PHP2 to perform authentication operations. PHP1 uses this engine for IPsec operations, while PHP2 uses this engine for SRTP operations. This module can also be used with data-mode packets without engaging the PHPs.

- **PHP2 PDSP**: primarily used with the encryption and decryption engine and the authentication engine to perform SRTP operations, or the Air Cipher engine to perform 3GPP operations.

- Air Cipher Engine: used with PHP2 to perform Air Cipher encryption and decryption operations. This module can also be used with data-mode packets without engaging the PHP2.

In addition to the modules provided for packet processing, the SA also provides the following two modules to assist the host in security related operations:

- **Public Key Accelerator (PKA)**: used primarily for large vector math, as typically used in public key operations.

- True Random Number Generator (TRNG): used primarily for generating random numbers.

Figure 1-1 Keystone I Security Accelerator Functional Block Diagram

For Keystone II devices, there are two extra engines connected to the interconnect for authentication and encryption/decryption operations.

**Note**—The encryption and decryption engine, the authenticating engine, and the air cipher engine do not have connections to the configuration bus. Since these engines are not connected to the configuration bus, these modules do not contain memory-mapped registers and cannot be accessed through register reads and writes. All configuration for these modules is taken care of automatically by the PHP firmware.

# 1.5 Industry Standard(s) Compliance Statement

The SA is compliant with the following standards:

- RFC 1321 The MD5 Message-Digest Algorithm

- RFC 2104 HMAC: Keyed-Hashing for Message Authentication

- RFC 2246 Transport Layer Security Protocol

- RFC 3711 The Secure Real-time Transport Protocol (SRTP)

- RFC 4301 Security Architecture for IP

- RFC 4302 IP Authentication Header

- RFC 4303 IP Encapsulating Security Payload (ESP)

- RFC 4305 Cryptographic Algorithm Implementation Requirements for Encapsulating Security Payload (ESP) and Authentication Header

- Secure socket layer protocol

# **Architecture**

This chapter describes the Security Accelerator architecture.

- 2.1 "Clock Control" on page 2-2

- 2.2 "Memory Map" on page 2-2

- 2.3 "Security Accelerator Programming with the Low-Level Driver" on page 2-2

- 2.4 "Protocol Descriptions" on page 2-5

- 2.5 "Command Labels" on page 2-24

- 2.6 "Descriptor Software Information Words" on page 2-25

- 2.7 "Security Contexts" on page 2-25

- 2.8 "Security Context Cache" on page 2-26

- 2.9 "Packet Header Processor Modules" on page 2-28

- 2.10 "Encryption and Decryption Engine" on page 2-32

- 2.11 "Authentication Engine" on page 2-33

- 2.12 "Air Cipher Engine" on page 2-34

- 2.13 "Public Key Accelerator" on page 2-34

- 2.14 "True Random Number Generator" on page 2-40

- 2.15 "Initializing the SA Using the SA LLD" on page 2-42

- 2.16 "SA LLD Channel Initialization and Configuration" on page 2-42

- 2.17 "Sending Packets to the SA for Processing" on page 2-43

- 2.18 "SA Transmit Queues" on page 2-43

- 2.19 "Interrupt Support" on page 2-44

- 2.20 "DMA Event Support" on page 2-44

- 2.21 "Power Management" on page 2-44

#### 2.1 Clock Control

The Security Accelerator (SA) has one clock, which it receives from the Network Coprocessor (NETCP). This clock is used to operate all of the SA logic. To reduce power consumption, this clock is disabled by default; therefore, this clock must be enabled before using the SA. For more information about this clock, including the operating frequency, see the *Network Coprocessor (NETCP) for KeyStone Devices User Guide*, and the device-specific data manual. For more information about power management for the SA, see Section 2.21 "Power Management" on page 2-44.

## 2.2 Memory Map

The memory map of the Security Accelerator (SA) is shown in Table 2-1.

Table 2-1 Security Accelerator Memory Map<sup>1</sup>

| Memory Region                       | Address Offset |

|-------------------------------------|----------------|

| Security Accelerator System         | 00000h         |

| Context Cache Module                | 00100h         |

| PHP1 PDSP Module                    | 01000h         |

| PHP2 PDSP Module                    | 01100h         |

| PHP1 PDSP Program Memory            | 04000h         |

| PHP2 PDSP Program Memory            | 08000h         |

| Public Key Accelerator Module       | 20000h         |

| Public Key Accelerator Vector RAM   | 22000h         |

| True Random Number Generator Module | 24000h         |

| End of Table 2-1                    |                |

The address offsets are relative to the base address of the SA module. See the NETCP user guide to determine the base address

of the SA module relative to the NETCP.

# 2.3 Security Accelerator Programming with the Low-Level Driver

To ease the task of programming the Security Accelerator (SA) by abstracting many of the hardware details, a low-level driver (LLD) software package has been generated for use with the SA. Included with the SA LLD are firmware images that must be loaded onto the PHP PDSPs before using the SA to encrypt, decrypt, and authenticate packets. Due to interdependencies between the PHP firmware and the SA LLD, all users must use the SA LLD to generate the security contexts for the SA. Failure to use the SA LLD to generate security contexts will result in undefined behavior.

The SA LLD provides a set of APIs that can be called to configure and control the SA. The APIs provided by the SA LLD can be divided into two main categories: common interface APIs and channel interface APIs. These APIs are described in detail in the following sections.

#### 2.3.1 SA LLD Common Interface APIs

The common interface APIs are provided primarily to abstract the SA hardware from the user, and eliminates the need for the user to directly program the SA memory mapped registers. These APIs handle all the SA register reads and writes that are required to initialize and use the SA hardware. The common interface APIs provide the ability to enable, initialize, and use the hardware modules in the SA. The common interface provides APIs for configuring the following modules:

- SA System Configuration

- Security Context Cache

- Packet header processor 1 (PHP1)

- Packet header processor 2 (PHP2)

- Public key accelerator (PKA)

- True random number generator (TRNG)

Using the common interface APIs, the following list shows some of the tasks that can be performed:

- Reset, download, and update the PDSP firmware images on the SA PHP hardware modules

- Generate a 64-bit true random number from the TRNG hardware module

- Perform large integer arithmetic through the PKA hardware module

- Query SA states and statistics

- Monitor and report SA system errors

**Note**—For the full list of common interface APIs provided by the SA LLD, see the SA LLD documentation.

#### 2.3.2 SA LLD Channel Interface APIs

The channel interface APIs are provided to assist the SA with protocol-specific operations for the protocols listed in Section 2.4. For each of these protocols, the SA LLD channel interface allows the user to create channels allowing the SA to perform encryption, decryption, and authentication operations. Each channel is differentiated through a separate channel identification value, which is specified by the user. For each channel, the channel interface APIs perform the following tasks:

- Convert channel configuration information into security contexts for use by the SA encryption and decryption, authentication, and PHP hardware modules

- Perform protocol-specific packet operations such as insertion of the ESP header, padding, and ESP tail

- Decrypt and authenticate received SRTP packets when the SA hardware is not able to perform the operations due to key validation failure

- Generate SA operation control command labels when operating in data mode

- Maintain protocol-specific channel statistics

For details about the protocol-specific operations that will be completed by each protocol, see Section 2.4.

**Note**—A subset of the channel-specific APIs is provided in Table 2-2. For the full list of channel interface APIs provided by the SA LLD, see the SA LLD documentation.

Table 2-2 SA LLD Channel Specific API Overview

| API                 | Description                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sa_chanGetBufferReq | Get SA channel memory requirements.                                                                                                                                                                                                                                                                                                                                         |

|                     | This API is responsible for determining the SA LLD channel memory requirements for the protocol that will be used.                                                                                                                                                                                                                                                          |

| Sa_chanCreate       | Create the SA LLD channel.                                                                                                                                                                                                                                                                                                                                                  |

|                     | This API is responsible for instantiating the SA channel for the desired protocol. This API only instantiates the channels, and does not configure that channel. The Sa_chanControl API must be used to configure the channel.                                                                                                                                              |

| Sa_chanClose        | Close the SA LLD channel.                                                                                                                                                                                                                                                                                                                                                   |

|                     | This API is responsible for closing the SA channel. It will free the memory associated with the channel, tear down the security context, return the security context ownership to the Host, and remove the security context from the SA security context cache.                                                                                                             |

|                     | If the channel was setup for both TX and RX, then the above actions are completed for both the TX and RX portions of the channel.                                                                                                                                                                                                                                           |

| Sa_chanControl      | Configure the SA LLD channel.                                                                                                                                                                                                                                                                                                                                               |

|                     | This API is responsible for configuring the SA LLD channel. This API should be called multiple times to configure a channel and for re-key operations.                                                                                                                                                                                                                      |

|                     | <ol> <li>The first call to this function will set up the general settings such as the cipher mode, authentication mode, and other configuration parameters.</li> <li>For IPsec ESP, this is where things like the block size, MAC size, and SPI are specified.</li> <li>For Air Cipher, this is where things like the count-C, fresh, and IV size are specified.</li> </ol> |

|                     | 2. The second call to this function will set up the protocol specific key information used for the channel.                                                                                                                                                                                                                                                                 |

|                     | 3. Subsequent calls to this API are used to generate the TX and RX security contexts for the channel.                                                                                                                                                                                                                                                                       |

| Sa_chanSendData     | Prepare packet and descriptor for transmission to the SA.                                                                                                                                                                                                                                                                                                                   |

|                     | This API is responsible for completing protocol-specific operations to prepare the packet for transmission to the SA.                                                                                                                                                                                                                                                       |

|                     | This API is also responsible for generating the information required for the descriptor so that the SA will have the information required to process the packet. These operations include generating the descriptor software info words, and providing the updated packet and buffer lengths after making the protocol-specific updates to the packet.                      |

| Sa_chanReceiveData  | Post process a packet after receiving it from the SA.                                                                                                                                                                                                                                                                                                                       |

|                     | This API is responsible for doing the post-SA protocol-specific operations on the decrypted and/or integrity verified receive packet.                                                                                                                                                                                                                                       |

| Sa_chanGetStats     | Get the statistics for the channel.                                                                                                                                                                                                                                                                                                                                         |

|                     | This API is responsible for getting the SA LLD channel protocol-specific statistics.                                                                                                                                                                                                                                                                                        |

| Sa_chanGetID        | Get the channel ID.                                                                                                                                                                                                                                                                                                                                                         |

|                     | This API is responsible for getting the ID associated with the channel.                                                                                                                                                                                                                                                                                                     |

| End of Table 2-2    |                                                                                                                                                                                                                                                                                                                                                                             |

**Note**—The channel-level interface APIs do not communicate directly with the SA hardware.

## 2.4 Protocol Descriptions

This section describes the high-level protocols supported by the SA and the SA LLD. The types of cipher modes and the authentication modes supported by each protocol are discussed in detail.

The following protocols are supported by the SA and the SA LLD. See the protocol-specific section listed below for more details.

- 3GPP Air Cipher

- Data-Mode

- IPsec AH

- IPsec ESP

- SRTCP

- SRTP

For KeyStone II devices, the SA has two IPSEC/SRTP engines, versus only one in KeyStone I devices.

#### 2.4.1 3GPP Air Cipher

This section describes how to use the 3GPP air cipher protocol with the SA and the SA LLD and provides details about the SA hardware engines used to perform air cipher encryption, decryption, and authentication. This section also provides details about which cipher modes and authentication modes are supported when using the 3GPP air cipher protocol.

**Note**—The information in this section is accurate for SA LLD version 1.0.4.1. See the documentation provided with the version of the SA LLD that you are using for the most up-to-date information.

#### 2.4.1.1 SA Hardware Engine Utilization

Packets using the 3GPP air cipher protocol require the use of the following hardware engines:

- PHP2

- Air cipher engine

When sending a packet to the SA, the SA transmit queue selected must adhere to the requirements in Section 2.18. When it is in the appropriate queue, the NETCP packet DMA transfers the packet to the SA for encryption and authentication operations. There is no additional configuration needed to direct packets between the PHP2 and the air cipher engine. All transmission between modules inside the SA is taken care of by the packet command label, which is generated by PHP2 for the 3GPP air cipher protocol. For more information on command labels, see Section 2.5. For more information about sending packets to the SA, see Procedure 2-7.

#### 2.4.1.2 Supported Cipher Modes

The SA supports the following cipher modes for the 3GPP air cipher protocol:

- Null (no cipher)

- AES Counter

- ECSD A5/3 key generation

- GEA3 (GPRA) key generation

- GSM A5/3 key generation

- Kasumi F8

- Snow3G F8

The desired cipher mode can be selected when creating and configuring a channel using the SA LLD. The cipher used can be selected on a per-channel basis, meaning that only one cipher can be used per channel; however, different ciphers can be used by creating multiple channels and selecting a different cipher for each channel. The same cipher also can be used for multiple channels. For more information on creating and configuring channels see Procedure 2-6.

#### 2.4.1.3 Supported Authentication Modes

The SA supports the following authentication modes for the 3GPP air cipher protocol:

- Null (no authentication)

- AES CMAC

- Kasumi F9

The desired authentication mode can be selected when creating and configuring a channel using the SA LLD. The authentication mode that is used can be selected on a per-channel basis, meaning that only one authentication mode can be used per channel; however, different authentication modes can be used by creating multiple channels and selecting a different authentication mode for each channel. The same authentication mode also can be used for multiple channels. For more information on creating and configuring channels see Procedure 2-6.

#### 2.4.1.4 Protocol-Specific SA LLD Channel APIs

Table 2-3 lists the protocol-specific operations performed by the SA LLD channel specific APIs when using the 3GPP air cipher protocol.

Table 2-3 3GPP Air Cipher Channel SA LLD APIs

| API                | 3GPP Air Cipher Channel Operations                                                                                                                                                                                                                                                        |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sa_chanSendData    | Prepare a 3GPP air cipher From-Air packet for transmission to the SA.                                                                                                                                                                                                                     |

|                    | This API is mainly responsible for generating the SA-specific software information, which is required for every packet that is sent to the SA. This API only modifies the descriptor information and does not make any modifications to the packet data for the 3GPP air cipher protocol. |

| Sa_chanReceiveData | Prepare a 3GPP air cipher To-Air packet for transmission to the SA.                                                                                                                                                                                                                       |

|                    | This API is mainly responsible for generating the SA-specific software information, which is required for every packet that is sent to the SA. This API only modifies the descriptor information and does not make any modifications to the packet data for the 3GPP air cipher protocol. |

**Note**—Table 2-3 only provides information specific to the 3GPP air cipher protocol. For an overview of the functionality provided for all protocols by the SA LLD channel specific APIs, see Table 2-2.

#### 2.4.1.5 Descriptor Protocol-Specific Information Section

This section describes the descriptor protocol-specific information (PS info) section of the 3GPP air cipher protocol. The content stored in descriptor PS info section will be discussed for both transmit and receive packets.

#### 2.4.1.5.1 Transmit Packet Descriptor Protocol-Specific Information

This section describes the transmit configuration required for the descriptor PS info section of 3GPP air cipher packets. In this case, a transmit packet refers to a packet that is generated by the Host, and will be sent to the SA for encryption and/or authentication operations.

For transmit operations, the PASAHO\_SINFO\_FORMAT\_CMD macro should be used to create a command with the offset to the encryption payload, and the length of the encryption payload in bytes. This information must be placed in the PS info section of the descriptor so that the SA knows what section of the packet needs to be processed.

For 3GPP air cipher packets requiring authentication, the SA automatically inserts the authentication tag into the packet before the packet exits the SA. The PS info section does not require any additional configuration for 3GPP air cipher packets. A diagram of the PS info section of a 3GPP air cipher transmit packet is shown in Figure 2-1.

Figure 2-1 3GPP Air Cipher Descriptor Protocol-Specific Information Diagram

#### 2.4.1.5.2 Receive Packet Descriptor Protocol-Specific Information

This section describes the information in the PS info section of receive packets. 3GPP air cipher packets received by the SA and PA contain the PA/SA/Host long info structure in the PS info section. This structure is shared by both the PA and the SA. From this structure, the offset to the 3GPP air cipher header as well as additional information about the headers contained in the packet can be determined. For more information about the PA/SA/Host long info structure, see the *Network Coprocessor (NETCP) for KeyStone Devices User Guide*.

#### 2.4.2 Data-Mode

This section describes how to use the data-mode configuration with the SA and the SA LLD. This section provides details about the SA data processing engines used to perform encryption and authentication. This section also provides details about which cipher modes and authentication modes are supported when using data-mode.

The data-mode protocol is used when using the PHPs is not desired, or when using the other protocols is not desired.

#### 2.4.2.1 SA Data Processing Engine Utilization

The packets using data-mode can use of the following data processing engines:

- Encryption and decryption engine

- Authentication engine

- Air cipher engine

Unlike other protocols, data-mode does not use SA PHP modules. Since the PHPs are not used, they cannot generate the command label for the packet, so the command label must be generated by the Host processor and inserted into the PS info section of the packet before sending it to the SA for processing. Data-mode command labels are discussed in more detail in Table 2-6 and Section 2.4.2.5.

For data-mode, the exact data processing engine that will be used is not as clearly defined as it is for the other protocols, and depends on the cipher mode and authentication mode that is used for the packet. A mapping between the cipher mode and data processing engine used is provided in Table 2-4. Similarly, a mapping between the authentication mode and the data processing engine used is provided in Table 2-5.

Due to the fact that the SA data processing engines used to process a packet are not as clear as for the other protocols, extra care must be taken to adhere to the requirements mentioned in Section 2.18 to make sure that the correct transmit queue for the SA is used, so a deadlock condition can be avoided. Once the packet is placed into the appropriate transmit queue, the NETCP packet DMA will transfer the packet to the SA for encryption and authentication operations.

There is no additional configuration needed to direct the packet between the SA data processing engines. All communication between the modules inside the SA will be taken care of by the packet command label. For more information on command labels, see Section 2.5.

Note, that for KeyStone II devices, when using IPSEC or SRTP protocols, the SA will use two engines instead of one (as used in KeyStone1 devices) to authenticate and encrypt or decrypt payloads.

The information in this section is accurate for SA LLD version 1.0.4.1. See the documentation provided with the version of the SA LLD that you are using for the most up-to-date information.

## 2.4.2.2 Supported Cipher Modes

The SA supports the following cipher modes for the data-mode protocol:

- Null (no cipher)

- 3DES CBC

- AES CTR

- AES CBC

- AES F8

- CCM

- DES CBC

- GCM

- Kusami F8

- Snow3G F8

The desired cipher mode can be selected when creating and configuring a channel using the SA LLD. The cipher that is used can be selected on a per-channel basis, meaning that only one cipher can be used per channel; however, different ciphers can be used by creating multiple channels and selecting a different cipher for each channel. The same cipher also can be used for multiple channels. For more information on creating and configuring channels see Procedure 2-6.

Table 2-4 maps each of the cipher modes available in data-mode to the data processing engine in the SA that will take care of encrypting and decrypting the packet.

Table 2-4 Cipher Mode to SA Data Processing Engine Mapping

| Cipher Mode                | SA Data processing Engine Used                                            |

|----------------------------|---------------------------------------------------------------------------|

| Null                       | No data processing engines will be used to encrypt or decrypt the packet. |

| 3DES CBC                   | Encryption and Decryption Engine                                          |