# TMS320C5515/14/05/04 DSP Universal Serial Bus 2.0 (USB) Controller

# **User's Guide**

Literature Number: SPRUGH9A June 2010-Revised May 2014

# **Contents**

| Pret | ace     |                                                                                   | 12         |

|------|---------|-----------------------------------------------------------------------------------|------------|

| 1    | Univers | al Serial Bus (USB) Controller                                                    | 15         |

| 1    | Introdu | ction                                                                             | 16         |

|      | 1.1     | Purpose of the Peripheral                                                         | 16         |

|      | 1.2     | Features                                                                          | 16         |

|      | 1.3     | Functional Block Diagram                                                          |            |

|      | 1.4     | Industry Standard(s) Compliance Statement                                         | 17         |

| 2    | Archite | cture                                                                             | 17         |

|      | 2.1     | Clock Control                                                                     | 17         |

|      | 2.2     | Signal Descriptions                                                               | 18         |

|      | 2.3     | Memory Map                                                                        | 18         |

|      | 2.4     | USB_DP/USB_DM Polarity Inversion                                                  | 19         |

|      | 2.5     | Indexed and Non-Indexed Registers                                                 | 20         |

|      | 2.6     | USB PHY Initialization                                                            | 20         |

|      | 2.7     | Dynamic FIFO Sizing                                                               | 22         |

|      | 2.8     | USB Controller Peripheral Mode Operation                                          | 22         |

|      | 2.9     | Communications Port Programming Interface (CPPI) 4.1 DMA Overview for TMS320C5515 | 42         |

|      | 2.10    | BYTEMODE Bits of the USB System Control Register                                  | 66         |

|      | 2.11    | Reset Considerations                                                              | 67         |

|      | 2.12    | Interrupt Support                                                                 | 67         |

|      | 2.13    | DMA Event Support                                                                 | 67         |

|      | 2.14    | Power Management                                                                  | 67         |

| 3    | Registe | rs                                                                                | 69         |

|      | 3.1     | USB Controller Register Summary                                                   | 69         |

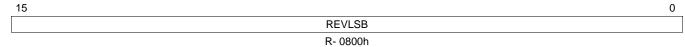

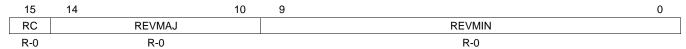

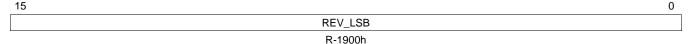

|      | 3.2     | Revision Identification Registers (REVID1 and REVID2)                             | 77         |

|      | 3.3     | Control Register (CTRLR)                                                          | 78         |

|      | 3.4     | Emulation Register (EMUR)                                                         | <b>7</b> 9 |

|      | 3.5     | Mode Registers (MODE1 and MODE2)                                                  | 80         |

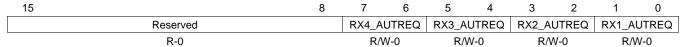

|      | 3.6     | Auto Request Register (AUTOREQ)                                                   | 82         |

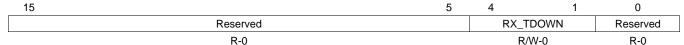

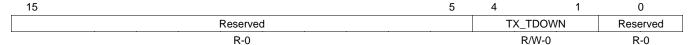

|      | 3.7     | Teardown Registers (TEARDOWN1 and TEARDOWN2)                                      | 83         |

|      | 3.8     | USB Interrupt Source Registers (INTSRCR1 and INTSRCR2)                            |            |

|      | 3.9     | USB Interrupt Source Set Registers (INTSETR1 and INTSETR2)                        |            |

|      | 3.10    | USB Interrupt Source Clear Registers (INTCLRR1 and INTCLRR2)                      | 86         |

|      | 3.11    | USB Interrupt Mask Registers (INTMSKR1 and INTMSKR2)                              |            |

|      | 3.12    | USB Interrupt Mask Set Registers (INTMSKSETR1 and INTMSKSETR2)                    |            |

|      | 3.13    | USB Interrupt Mask Clear Registers (INTMSKCLRR1 and INTMSKCLRR2)                  |            |

|      | 3.14    | USB Interrupt Source Masked Registers (INTMASKEDR1 and INTMASKEDR2)               |            |

|      | 3.15    | USB End of Interrupt Register (EOIR)                                              |            |

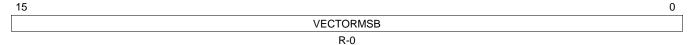

|      | 3.16    | USB Interrupt Vector Registers (INTVECTR1 and INTVECTR2)                          |            |

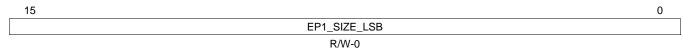

|      | 3.17    | Generic RNDIS EP1 Size Registers (GREP1SZR1 and GREP1SZR2)                        |            |

|      | 3.18    | Generic RNDIS EP2 Size Registers (GREP2SZR1 and GREP2SZR2)                        | 93         |

|      |         |                                                                                   |            |

### www.ti.com

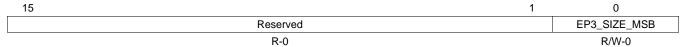

| 3.19 | Generic RNDIS EP3 Size Registers (GREP3SZR1 and GREP3SZR2)                                 |      |  |

|------|--------------------------------------------------------------------------------------------|------|--|

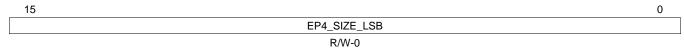

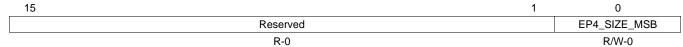

| 3.20 | Generic RNDIS EP4 Size Registers (GREP4SZR1 and GREP4SZR2)                                 |      |  |

| 3.21 | Function Address Register (FADDR)                                                          |      |  |

| 3.22 | Power Management Register (POWER)9                                                         |      |  |

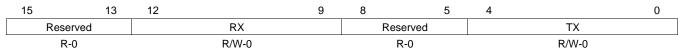

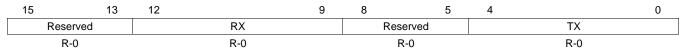

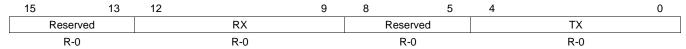

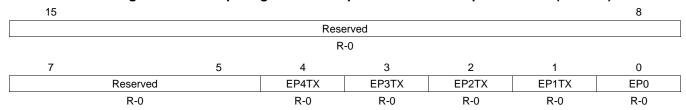

| 3.23 | Interrupt Register for Endpoint 0 Plus Transmit Endpoints 1 to 4 (INTRTX)                  | . 97 |  |

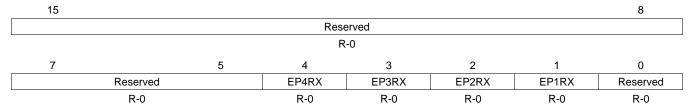

| 3.24 | Interrupt Register for Receive Endpoints 1 to 4 (INTRRX)                                   | . 97 |  |

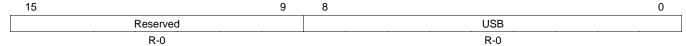

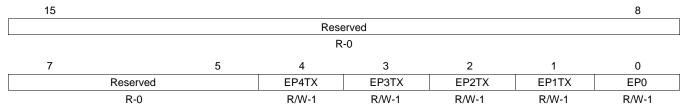

| 3.25 | Interrupt Enable Register for INTRTX (INTRTXE)                                             | . 98 |  |

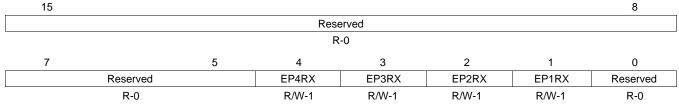

| 3.26 | Interrupt Enable Register for INTRRX (INTRRXE)                                             | . 98 |  |

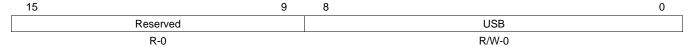

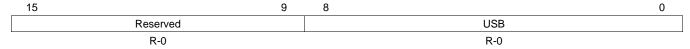

| 3.27 | Interrupt Register for Common USB Interrupts (INTRUSB)                                     | . 99 |  |

| 3.28 | Interrupt Enable Register for INTRUSB (INTRUSBE)                                           | 100  |  |

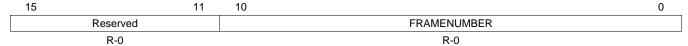

| 3.29 | Frame Number Register (FRAME)                                                              | 100  |  |

| 3.30 | Index Register for Selecting the Endpoint Status and Control Registers (INDEX)             | 101  |  |

| 3.31 | Register to Enable the USB 2.0 Test Modes (TESTMODE)                                       | 101  |  |

| 3.32 | Maximum Packet Size for Peripheral/Host Transmit Endpoint (TXMAXP)                         | 102  |  |

| 3.33 | Control Status Register for Peripheral Endpoint 0 (PERI_CSR0)                              |      |  |

| 3.34 | Control Status Register for Peripheral Transmit Endpoint (PERI_TXCSR)                      |      |  |

| 3.35 | Maximum Packet Size for Peripheral Receive Endpoint (RXMAXP)                               |      |  |

| 3.36 | Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR)                       |      |  |

| 3.37 | Count 0 Register (COUNT0)                                                                  |      |  |

| 3.38 | Receive Count Register (RXCOUNT)                                                           |      |  |

| 3.39 | Configuration Data Register (CONFIGDATA)                                                   |      |  |

| 3.40 | Transmit and Receive FIFO Registers for Endpoint 0 (FIFO0R1 and FIFO0R2)                   |      |  |

| 3.41 | Transmit and Receive FIFO Registers for Endpoint 1 (FIFO1R1 and FIFO1R2)                   |      |  |

| 3.42 | Transmit and Receive FIFO Registers for Endpoint 2 (FIFO2R1 and FIFO2R2)                   |      |  |

| 3.43 | Transmit and Receive FIFO Registers for Endpoint 3 (FIFO3R1 and FIFO3R2)                   |      |  |

| 3.44 | Transmit and Receive FIFO Registers for Endpoint 4 (FIFO4R1 and FIFO4R2)                   |      |  |

| 3.45 | Device Control Register (DEVCTL)                                                           |      |  |

| 3.46 | Transmit Endpoint FIFO Size (TXFIFOSZ)                                                     |      |  |

| 3.47 | Receive Endpoint FIFO Size (RXFIFOSZ)                                                      |      |  |

| 3.48 | Transmit Endpoint FIFO Address (TXFIFOADDR)                                                |      |  |

| 3.49 | Hardware Version Register (HWVERS)                                                         |      |  |

| 3.50 | Receive Endpoint FIFO Address (RXFIFOADDR)                                                 |      |  |

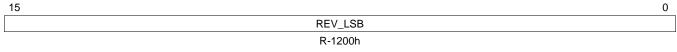

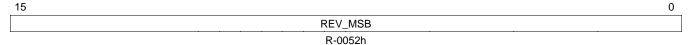

| 3.51 | CDMA Revision Identification Registers (DMAREVID1 and DMAREVID2)                           |      |  |

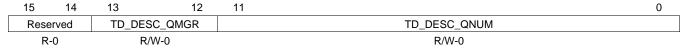

| 3.52 | CDMA Teardown Free Descriptor Queue Control Register (TDFDQ)                               |      |  |

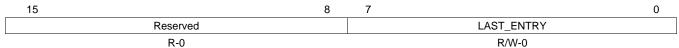

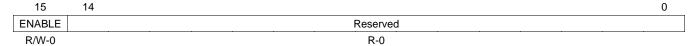

| 3.53 | CDMA Emulation Control Register (DMAEMU)                                                   |      |  |

| 3.54 | CDMA Transmit Channel n Global Configuration Registers (TXGCR1[n] and TXGCR2[n])           |      |  |

| 3.55 | CDMA Receive Channel n Global Configuration Registers (RXGCR1[n] and RXGCR2[n])            |      |  |

| 3.56 | CDMA Receive Channel n Host Packet Configuration Registers A (RXHPCR1A[n] and RXHPCR2A[n]) | 122  |  |

| 3.57 | CDMA Receive Channel n Host Packet Configuration Registers B (RXHPCR1B[n] and RXHPCR2B[n]) | 123  |  |

| 3.58 | CDMA Scheduler Control Register (DMA_SCHED_CTRL1 and DMA_SCHED_CTRL2)                      | 124  |  |

| 3.59 | CDMA Scheduler Table Word n Registers (ENTRYLSW[n]-ENTRYMSW[n])                            | 125  |  |

| 3.60 | Queue Manager Revision Identification Registers (QMGRREVID1 and QMGRREVID2)                |      |  |

| 3.61 | Queue Manager Queue Diversion Registers (DIVERSION1 and DIVERSION2)                        |      |  |

| 3.62 | Queue Manager Free Descriptor/Buffer Starvation Count Register 0 (FDBSC0)                  |      |  |

| 3.63 | Queue Manager Free Descriptor/Buffer Starvation Count Register 1 (FDBSC1)                  |      |  |

| 3.64 | Queue Manager Free Descriptor/Buffer Starvation Count Register 2 (FDBSC2)                  |      |  |

| 3.65 | Queue Manager Free Descriptor/Buffer Starvation Count Register 3 (FDBSC3)                  |      |  |

| 3.66 | Queue Manager Free Descriptor/Buffer Starvation Count Register 4 (FDBSC4)                  |      |  |

| 3.67 | Queue Manager Free Descriptor/Buffer Starvation Count Register 5 (FDBSC5)                  |      |  |

|      |                                                                                            |      |  |

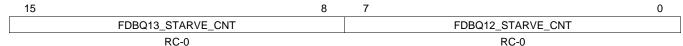

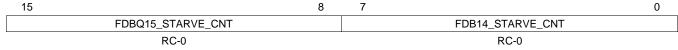

|          | 3.68    | Queue Manager Free Descriptor/Buffer Starvation Count Register 6 (FDBSC6)               | 131 |

|----------|---------|-----------------------------------------------------------------------------------------|-----|

|          | 3.69    | Queue Manager Free Descriptor/Buffer Starvation Count Register 7 (FDBSC7)               | 131 |

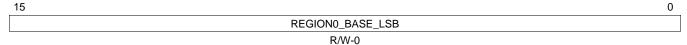

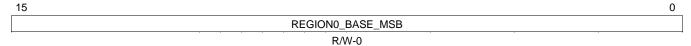

|          | 3.70    | Queue Manager Linking RAM Region 0 Base Address Registers (LRAM0BASE1 and LRAM0BASE2) . | 132 |

|          | 3.71    | Queue Manager Linking RAM Region 0 Size Register (LRAM0SIZE)                            | 133 |

|          | 3.72    | Queue Manager Linking RAM Region 1 Base Address Registers (LRAM1BASE1 and LRAM1BASE2) . | 134 |

|          | 3.73    | Queue Manager Queue Pending Register 0 (PEND0)                                          | 135 |

|          | 3.74    | Queue Manager Queue Pending Register 1 (PEND1)                                          | 135 |

|          | 3.75    | Queue Manager Queue Pending Register 2 (PEND2)                                          | 136 |

|          | 3.76    | Queue Manager Queue Pending Register 3 (PEND3)                                          | 136 |

|          | 3.77    | Queue Manager Queue Pending Register 4 (PEND4)                                          | 137 |

|          | 3.78    | Queue Manager Queue Pending Register 5 (PEND5)                                          | 137 |

|          | 3.79    | Queue Manager Memory Region R Base Address Registers (QMEMRBASE1[R] and QMEMRBASE2[R])  | 138 |

|          | 3.80    | Queue Manager Memory Region R Control Registers (QMEMRCTRL1[R] and QMEMRCTRL2[R])       | 139 |

|          | 3.81    | Queue Manager Queue N Control Register D (CTRL1D[N] and CTRL2D[N])                      | 140 |

|          | 3.82    | Queue Manager Queue N Status Register A (QSTATA[N])                                     | 141 |

|          | 3.83    | Queue Manager Queue N Status Registers B (QSTAT1B[N] and QSTAT2B[N])                    | 141 |

|          | 3.84    | Queue Manager Queue N Status Register C (QSTATC[N])                                     | 142 |

| Revision | n Histo | ory                                                                                     | 143 |

## **List of Figures**

| 1  | Functional Block Diagram                              | 17 |

|----|-------------------------------------------------------|----|

| 2  | USB Clocking Diagram                                  | 17 |

| 3  | USB System Control Register (USBSCR) [1C32h]          | 21 |

| 4  | Interrupt Service Routine Flow Chart                  | 23 |

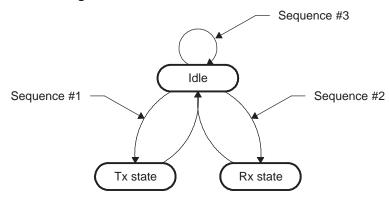

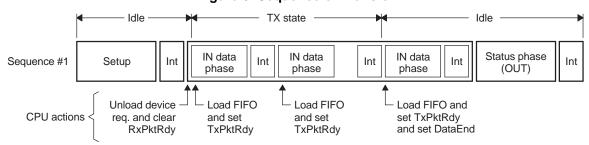

| 5  | CPU Actions at Transfer Phases                        | 28 |

| 6  | Sequence of Transfer                                  | 28 |

| 7  | Service Endpoint 0 Flow Chart                         | 30 |

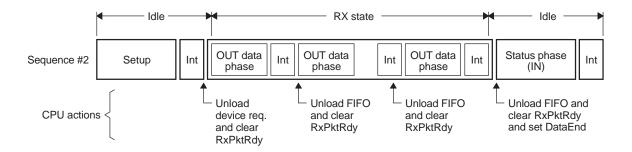

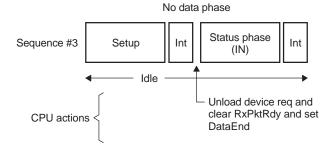

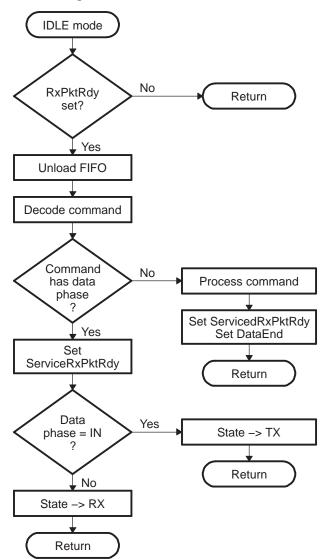

| 8  | IDLE Mode Flow Chart                                  | 31 |

| 9  | TX Mode Flow Chart                                    | 32 |

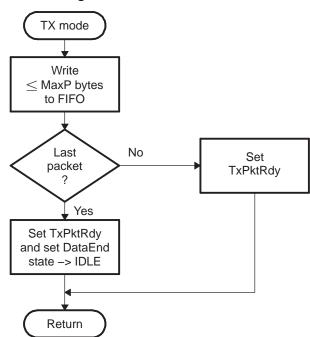

| 10 | RX Mode Flow Chart                                    | 33 |

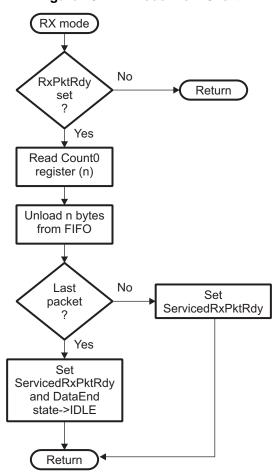

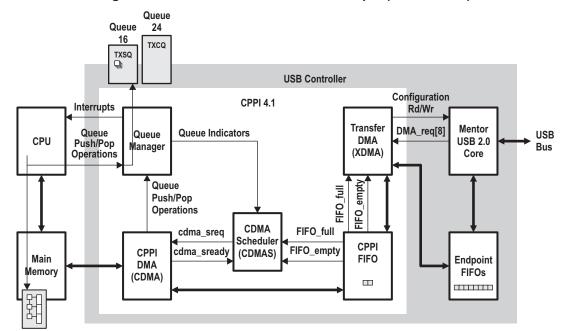

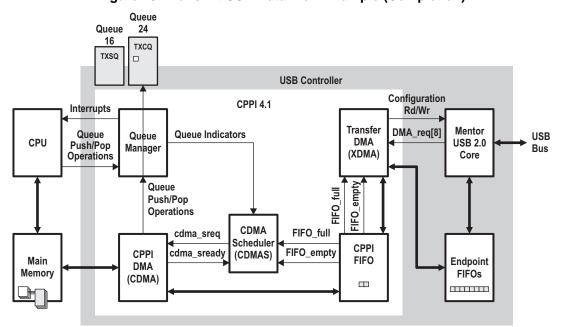

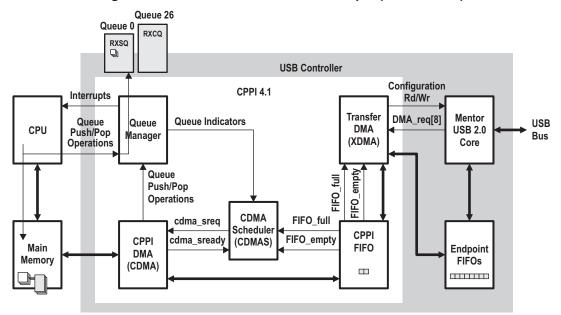

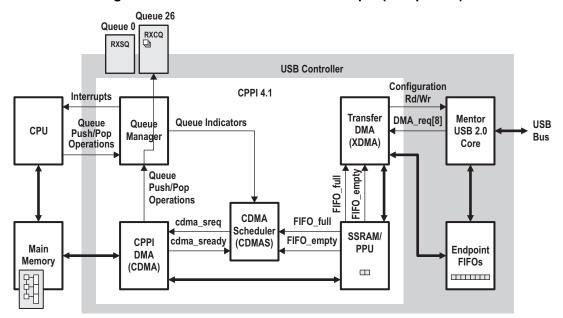

| 11 | USB Controller Block Diagram                          | 42 |

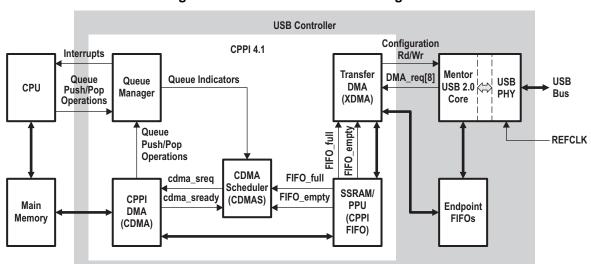

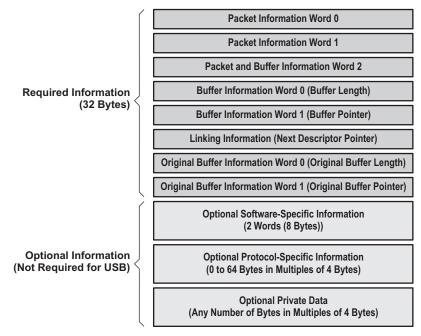

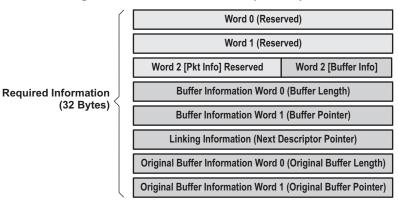

| 12 | Host Packet Descriptor Layout                         |    |

| 13 | Host Buffer Descriptor Layout                         |    |

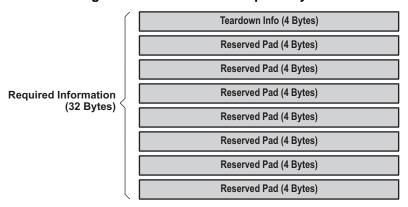

| 14 | Teardown Descriptor Layout                            |    |

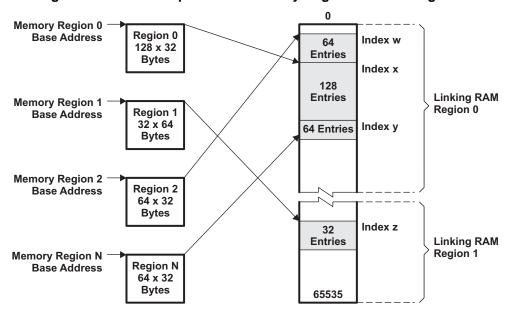

| 15 | Relationship Between Memory Regions and Linking RAM   |    |

| 16 | High-Level Transmit and Receive Data Transfer Example |    |

| 17 | Transmit Descriptors and Queue Status Configuration   |    |

| 18 | Transmit USB Data Flow Example (Initialization)       | 61 |

| 19 | Transmit USB Data Flow Example (Completion)           |    |

| 20 | Receive Descriptors and Queue Status Configuration    |    |

| 21 | Receive USB Data Flow Example (Initialization)        |    |

| 22 | Receive USB Data Flow Example (Completion)            |    |

| 23 | Revision Identification Register 1 (REVID1)           |    |

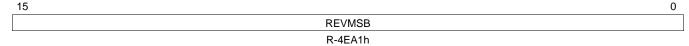

| 24 | Revision Identification Register 2 (REVID2)           |    |

| 25 | Control Register (CTRLR)                              |    |

| 26 | Emulation Register (EMUR)                             |    |

| 27 | Mode Register 1 (MODE1)                               |    |

| 28 | Mode Register 2 (MODE2)                               |    |

| 29 | Auto Request Register (AUTOREQ)                       | 82 |

| 30 | Teardown Register 1 (TEARDOWN1)                       |    |

| 31 | Teardown Register 2 (TEARDOWN2)                       | 83 |

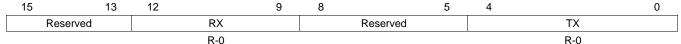

| 32 | USB Interrupt Source Register 1 (INTSRCR1)            | 84 |

| 33 | USB Interrupt Source Register 2 (INTSRCR2)            | 84 |

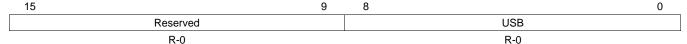

| 34 | USB Interrupt Source Set Register 1 (INTSETR1)        | 85 |

| 35 | USB Interrupt Source Set Register 2 (INTSETR2)        | 85 |

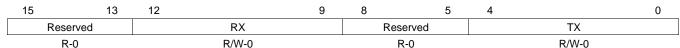

| 36 | USB Interrupt Source Clear Register 1 (INTCLRR1)      | 86 |

| 37 | USB Interrupt Source Clear Register 2 (INTCLRR2)      | 86 |

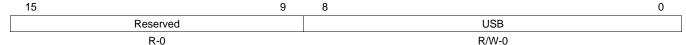

| 38 | USB Interrupt Mask Register 1 (INTMSKR1)              | 87 |

| 39 | USB Interrupt Mask Register 2 (INTMSKR2)              | 87 |

| 40 | USB Interrupt Mask Set Register 1 (INTMSKSETR1)       | 88 |

| 41 | USB Interrupt Mask Set Register 2 (INTMSKSETR2)       | 88 |

| 42 | USB Interrupt Mask Clear Register 1 (INTMSKCLRR1)     | 89 |

| 43 | USB Interrupt Mask Clear Register 2 (INTMSKCLRR2)     |    |

| 44 | USB Interrupt Source Masked Register 1 (INTMASKEDR1)  |    |

| 45 | USB Interrupt Source Masked Register 2 (INTMASKEDR2)  |    |

| 46 | USB End of Interrupt Register (EOIR)                  | 91 |

| 47 | USB Interrupt Vector Register 1 (INTVECTR1)           | 91 |

|    |                                                       |    |

| 48 | USB Interrupt Vector Register 2 (INTVECTR2)                                         | . 91 |

|----|-------------------------------------------------------------------------------------|------|

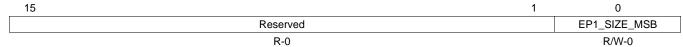

| 49 | Generic RNDIS EP1 Size Register 1 (GREP1SZR1)                                       | . 92 |

| 50 | Generic RNDIS EP1 Size Register 2 (GREP1SZR2)                                       | . 92 |

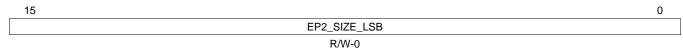

| 51 | Generic RNDIS EP2 Size Register 1 (GREP2SZR1)                                       | . 93 |

| 52 | Generic RNDIS EP2 Size Register 2 (GREP2SZR2)                                       | . 93 |

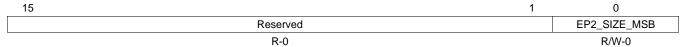

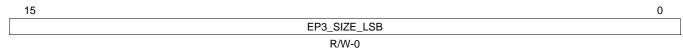

| 53 | Generic RNDIS EP3 Size Register 1 (GREP3SZR1)                                       | . 94 |

| 54 | Generic RNDIS EP3 Size Register 2 (GREP3SZR2)                                       | . 94 |

| 55 | Generic RNDIS EP4 Size Register 1 (GREP4SZR1)                                       | . 95 |

| 56 | Generic RNDIS EP4 Size Register 2 (GREP4SZR2)                                       | . 95 |

| 57 | Function Address Register (FADDR)                                                   | . 96 |

| 58 | Power Management Register (POWER)                                                   | . 96 |

| 59 | Interrupt Register for Endpoint 0 Plus Tx Endpoints 1 to 4 (INTRTX)                 | . 97 |

| 60 | Interrupt Register for Receive Endpoints 1 to 4 (INTRRX)                            | . 97 |

| 61 | Interrupt Enable Register for INTRTX (INTRTXE)                                      | . 98 |

| 62 | Interrupt Enable Register for INTRRX (INTRRXE)                                      | . 98 |

| 63 | Interrupt Register for Common USB Interrupts (INTRUSB)                              | . 99 |

| 64 | Interrupt Enable Register for INTRUSB (INTRUSBE)                                    | 100  |

| 65 | Frame Number Register (FRAME)                                                       | 100  |

| 66 | Index Register for Selecting the Endpoint Status and Control Registers (INDEX)      | 101  |

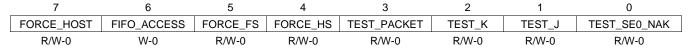

| 67 | Register to Enable the USB 2.0 Test Modes (TESTMODE)                                | 101  |

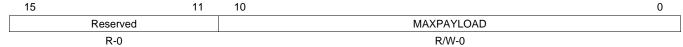

| 68 | Maximum Packet Size for Peripheral/Host Transmit Endpoint (TXMAXP)                  | 102  |

| 69 | Control Status Register for Peripheral Endpoint 0 (PERI_CSR0)                       | 103  |

| 70 | Control Status Register for Peripheral Transmit Endpoint (PERI_TXCSR)               | 104  |

| 71 | Maximum Packet Size for Peripheral Receive Endpoint (RXMAXP)                        | 105  |

| 72 | Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR)                | 106  |

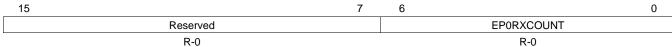

| 73 | Count 0 Register (COUNT0)                                                           | 107  |

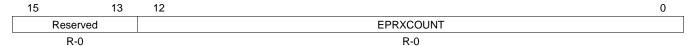

| 74 | Receive Count Register (RXCOUNT)                                                    | 107  |

| 75 | Configuration Data Register (CONFIGDATA)                                            | 108  |

| 76 | Transmit and Receive FIFO Register 1 for Endpoint 0 (FIFO0R1)                       | 109  |

| 77 | Transmit and Receive FIFO Register 2 for Endpoint 0 (FIFO0R2)                       | 109  |

| 78 | Transmit and Receive FIFO Register 1 for Endpoint 1 (FIFO1R1)                       | 110  |

| 79 | Transmit and Receive FIFO Register 2 for Endpoint 1 (FIFO1R2)                       | 110  |

| 80 | Transmit and Receive FIFO Register 1 for Endpoint 2 (FIFO2R1)                       | 111  |

| 81 | Transmit and Receive FIFO Register 2 for Endpoint 2 (FIFO2R2)                       | 111  |

| 82 | Transmit and Receive FIFO Register 1 for Endpoint 3 (FIFO3R1)                       | 112  |

| 83 | Transmit and Receive FIFO Register 2 for Endpoint 3 (FIFO3R2)                       | 112  |

| 84 | Transmit and Receive FIFO Register 1 for Endpoint 4 (FIFO4R1)                       | 113  |

| 85 | Transmit and Receive FIFO Register 2 for Endpoint 4 (FIFO4R2)                       | 113  |

| 86 | Device Control Register (DEVCTL)                                                    |      |

| 87 | Transmit Endpoint FIFO Size (TXFIFOSZ)                                              | 115  |

| 88 | Receive Endpoint FIFO Size (RXFIFOSZ)                                               | 115  |

| 89 | Transmit Endpoint FIFO Address (TXFIFOADDR)                                         | 116  |

| 90 | Hardware Version Register (HWVERS)                                                  | 116  |

| 91 | Receive Endpoint FIFO Address (RXFIFOADDR)                                          |      |

| 92 | CDMA Revision Identification Register 1 (DMAREVID1)                                 |      |

| 93 | CDMA Revision Identification Register 2 (DMAREVID2)                                 |      |

| 94 | CDMA Teardown Free Descriptor Queue Control Register (TDFDQ)                        | 118  |

| 95 | CDMA Emulation Control Register (DMAEMU)                                            | 118  |

| 96 | CDMA Transmit Channel <i>n</i> Global Configuration Register 1 (TXGCR1[ <i>n</i> ]) | 119  |

### www.ti.com

| 97  | CDMA Transmit Channel <i>n</i> Global Configuration Register 2 (TXGCR2[ <i>n</i> ])    | 119 |

|-----|----------------------------------------------------------------------------------------|-----|

| 98  | CDMA Receive Channel <i>n</i> Global Configuration Register 1 (RXGCR1[ <i>n</i> ])     | 120 |

| 99  | CDMA Receive Channel <i>n</i> Global Configuration Register 2 (RXGCR2[ <i>n</i> ])     | 120 |

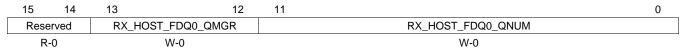

| 100 | Receive Channel n Host Packet Configuration Register 1 A (RXHPCR1A[n])                 | 122 |

| 101 | Receive Channel n Host Packet Configuration Register 2 A (RXHPCR2A[n])                 | 122 |

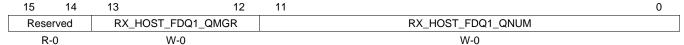

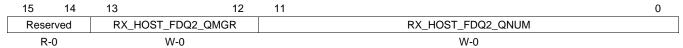

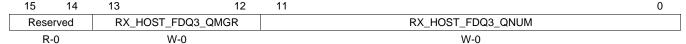

| 102 | Receive Channel <i>n</i> Host Packet Configuration Register 1 B (RXHPCR1B[ <i>n</i> ]) | 123 |

| 103 | Receive Channel <i>n</i> Host Packet Configuration Register 2 B (RXHPCR2B[ <i>n</i> ]) | 123 |

| 104 | CDMA Scheduler Control Register 1 (DMA_SCHED_CTRL1)                                    | 124 |

| 105 | CDMA Scheduler Control Register 2 (DMA_SCHED_CTRL2)                                    | 124 |

| 106 | CDMA Scheduler Table Word <i>n</i> Registers (ENTRYLSW[ <i>n</i> ])                    | 125 |

| 107 | CDMA Scheduler Table Word <i>n</i> Registers (ENTRYMSW[ <i>n</i> ])                    | 125 |

| 108 | Queue Manager Revision Identification Register 1 (QMGRREVID1)                          | 126 |

| 109 | Queue Manager Revision Identification Register 2 (QMGRREVID2)                          | 126 |

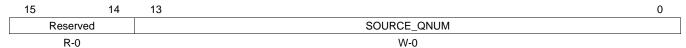

| 110 | Queue Manager Queue Diversion Register 1 (DIVERSION1)                                  | 127 |

| 111 | Queue Manager Queue Diversion Register 2 (DIVERSION2)                                  | 127 |

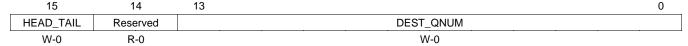

| 112 | Queue Manager Free Descriptor/Buffer Starvation Count Register 0 (FDBSC0)              | 128 |

| 113 | Queue Manager Free Descriptor/Buffer Starvation Count Register 1 (FDBSC1)              | 128 |

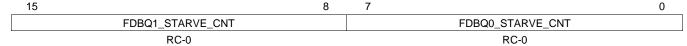

| 114 | Queue Manager Free Descriptor/Buffer Starvation Count Register 2 (FDBSC2)              | 129 |

| 115 | Queue Manager Free Descriptor/Buffer Starvation Count Register 3 (FDBSC3)              | 129 |

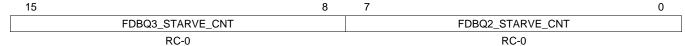

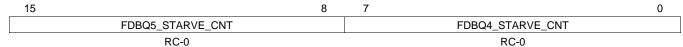

| 116 | Queue Manager Free Descriptor/Buffer Starvation Count Register 4 (FDBSC4)              | 130 |

| 117 | Queue Manager Free Descriptor/Buffer Starvation Count Register 5 (FDBSC5)              | 130 |

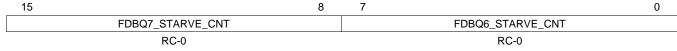

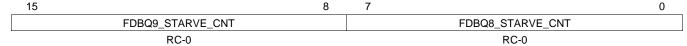

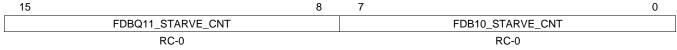

| 118 | Queue Manager Free Descriptor/Buffer Starvation Count Register 6 (FDBSC6)              | 131 |

| 119 | Queue Manager Free Descriptor/Buffer Starvation Count Register 7 (FDBSC7)              | 131 |

| 120 | Queue Manager Linking RAM Region 0 Base Address Register 1 (LRAM0BASE1)                | 132 |

| 121 | Queue Manager Linking RAM Region 0 Base Address Register 2 (LRAM0BASE2)                | 132 |

| 122 | Queue Manager Linking RAM Region 0 Size Register (LRAM0SIZE)                           | 133 |

| 123 | Queue Manager Linking RAM Region 1 Base Address Register 1 (LRAM1BASE1)                | 134 |

| 124 | Queue Manager Linking RAM Region 1 Base Address Register 2 (LRAM1BASE2)                | 134 |

| 125 | Queue Manager Queue Pending Register 0 (PEND0)                                         | 135 |

| 126 | Queue Manager Queue Pending Register 1 (PEND1)                                         | 135 |

| 127 | Queue Manager Queue Pending Register 2 (PEND2)                                         | 136 |

| 128 | Queue Manager Queue Pending Register 3 (PEND3)                                         | 136 |

| 129 | Queue Manager Queue Pending Register 4 (PEND4)                                         | 137 |

| 130 | Queue Manager Queue Pending Register 5 (PEND5)                                         | 137 |

| 131 | Queue Manager Memory Region R Base Address Register 1 (QMEMRBASE1[R])                  | 138 |

| 132 | Queue Manager Memory Region R Base Address Register 2 (QMEMRBASE2[R])                  | 138 |

| 133 | Queue Manager Memory Region R Control Register 1 (QMEMRCTRL1[R])                       | 139 |

| 134 | Queue Manager Memory Region R Control Register 2 (QMEMRCTRL2[R])                       | 139 |

| 135 | Queue Manager Queue N Control Register 1 D (CTRL1D[N])                                 | 140 |

| 136 | Queue Manager Queue N Control Register 2 D (CTRL2D[N])                                 | 140 |

| 137 | Queue Manager Queue N Status Register A (QSTATA[N])                                    | 141 |

| 138 | Queue Manager Queue N Status Register 1 B (QSTAT1B[N])                                 | 141 |

| 139 | Queue Manager Queue N Status Register 2 B (QSTAT2B[N])                                 | 141 |

| 140 | Queue Manager Queue N Status Register C (QSTATC[N])                                    | 142 |

## **List of Tables**

| 1  | USB Terminal Functions                                                     | 18 |

|----|----------------------------------------------------------------------------|----|

| 2  | USB Controller Memory Map                                                  | 18 |

| 3  | USB System Control Register (USBSCR) Field Descriptions                    | 21 |

| 4  | PERI_TXCSR Register Bit Configuration for Bulk IN Transactions             |    |

| 5  | PERI_RXCSR Register Bit Configuration for Bulk OUT Transactions            |    |

| 6  | PERI_TXCSR Register Bit Configuration for Isochronous IN Transactions      |    |

| 7  | PERI_RXCSR Register Bit Configuration for Isochronous OUT Transactions     |    |

| 8  | Host Packet Descriptor Word 0 (HPD Word 0)                                 |    |

| 9  | Host Packet Descriptor Word 1 (HPD Word 1)                                 |    |

| 10 | Host Packet Descriptor Word 2 (HPD Word 2)                                 |    |

| 11 | Host Packet Descriptor Word 3 (HPD Word 3)                                 |    |

| 12 | Host Packet Descriptor Word 4 (HPD Word 4)                                 |    |

| 13 | Host Packet Descriptor Word 5 (HPD Word 5)                                 |    |

| 14 | Host Packet Descriptor Word 6 (HPD Word 6)                                 |    |

| 15 | Host Packet Descriptor Word 7 (HPD Word 7)                                 |    |

| 16 | Host Buffer Descriptor Word 0 (HBD Word 0)                                 |    |

| 17 | Host Buffer Descriptor Word 1 (HBD Word 1)                                 |    |

| 18 | Host Buffer Descriptor Word 2 (HBD Word 2)                                 |    |

| 19 | Host Buffer Descriptor Word 3 (HBD Word 3)                                 |    |

| 20 | Host Buffer Descriptor Word 4 (HBD Word 4)                                 |    |

| 21 | Host Buffer Descriptor Word 5 (HBD Word 5)                                 |    |

| 22 | Host Buffer Descriptor Word 6 (HBD Word 6)                                 | 49 |

| 23 | Host Buffer Descriptor Word 7 (HBD Word 7)                                 |    |

| 24 | Teardown Descriptor Word 0                                                 |    |

| 25 | Teardown Descriptor Words 1-7                                              |    |

| 26 | Allocation of Queues                                                       |    |

| 27 | Interrupts Generated by the USB Controller                                 |    |

| 28 | USB Interrupt Conditions                                                   |    |

| 29 | Effect of USBSCR BYTEMODE Bits on USB Access                               | 67 |

| 30 | LDO Pin Connections                                                        | 68 |

| 31 | Universal Serial Bus (USB) Registers                                       | 69 |

| 32 | Common USB Register Layout                                                 |    |

| 33 | Common USB Registers                                                       |    |

| 34 | USB Indexed Register Layout when Index Register Set to Select Endpoint 0   | 71 |

| 35 | USB Indexed Register Layout when Index Register Set to Select Endpoint 1-4 |    |

| 36 | USB Indexed Registers                                                      |    |

| 37 | USB FIFO Registers                                                         | 72 |

| 38 | Dynamic FIFO Control Register Layout                                       | 72 |

| 39 | Dynamic FIFO Control Registers                                             |    |

| 40 | Control and Status Registers for Endpoints 0-4                             | 73 |

| 41 | CPPI DMA (CMDA) Registers                                                  | 74 |

| 42 | Queue Manager (QMGR) Registers                                             |    |

| 43 | Revision Identification Register 1 (REVID1) Field Descriptions             |    |

| 44 | Revision Identification Register 2 (REVID2) Field Descriptions             |    |

| 45 | Control Register (CTRLR) Field Descriptions                                |    |

| 46 | Emulation Register (EMUR) Field Descriptions                               |    |

| 47 | Mode Register 1 (MODE1) Field Descriptions                                 |    |

|    |                                                                            |    |

| www. | ŤΙ | ഹ | m |

|------|----|---|---|

|      |    |   |   |

| 48 | Mode Register 2 (MODE2) Field Descriptions                                                        | 80  |

|----|---------------------------------------------------------------------------------------------------|-----|

| 49 | Auto Request Register (AUTOREQ) Field Descriptions                                                | 82  |

| 50 | Teardown Register 1 (TEARDOWN1) Field Descriptions                                                | 83  |

| 51 | Teardown Register 2 (TEARDOWN2) Field Descriptions                                                | 83  |

| 52 | USB Interrupt Source Register 1 (INTSRCR1) Field Descriptions                                     | 84  |

| 53 | USB Interrupt Source Register 2 (INTSRCR2) Field Descriptions                                     | 84  |

| 54 | USB Interrupt Source Set Register 1 (INTSETR1) Field Descriptions                                 | 85  |

| 55 | USB Interrupt Source Set Register 2 (INTSETR2) Field Descriptions                                 | 85  |

| 56 | USB Interrupt Source Clear Register 1 (INTCLRR1) Field Descriptions                               | 86  |

| 57 | USB Interrupt Source Clear Register 2 (INTCLRR2) Field Descriptions                               | 86  |

| 58 | USB Interrupt Mask Register 1 (INTMSKR1) Field Descriptions                                       | 87  |

| 59 | USB Interrupt Mask Register 2 (INTMSKR2) Field Descriptions                                       | 87  |

| 60 | USB Interrupt Mask Set Register 1 (INTMSKSETR1) Field Descriptions                                | 88  |

| 61 | USB Interrupt Mask Set Register 2 (INTMSKSETR2) Field Descriptions                                | 88  |

| 62 | USB Interrupt Mask Clear Register 1 (INTMSKCLRR1) Field Descriptions                              | 89  |

| 63 | USB Interrupt Mask Clear Register 2 (INTMSKCLRR2) Field Descriptions                              | 89  |

| 64 | USB Interrupt Source Masked Register 1 (INTMASKEDR1) Field Descriptions                           | 90  |

| 65 | USB Interrupt Source Masked Register 2 (INTMASKEDR2) Field Descriptions                           | 90  |

| 66 | USB End of Interrupt Register (EOIR) Field Descriptions                                           | 91  |

| 67 | USB Interrupt Vector Register 1 (INTVECTR1) Field Descriptions                                    | 91  |

| 68 | USB Interrupt Vector Register 2 (INTVECTR2) Field Descriptions                                    | 91  |

| 69 | Generic RNDIS EP1 Size Register 1 (GREP1SZR1) Field Descriptions                                  | 92  |

| 70 | Generic RNDIS EP1 Size Register 2 (GREP1SZR2) Field Descriptions                                  | 92  |

| 71 | Generic RNDIS EP2 Size Register 1 (GREP2SZR1) Field Descriptions                                  | 93  |

| 72 | Generic RNDIS EP2 Size Register 2 (GREP2SZR2) Field Descriptions                                  | 93  |

| 73 | Generic RNDIS EP3 Size Register 1 (GREP3SZR1) Field Descriptions                                  | 94  |

| 74 | Generic RNDIS EP3 Size Register 2 (GREP3SZR2) Field Descriptions                                  | 94  |

| 75 | Generic RNDIS EP4 Size Register 1 (GREP4SZR1) Field Descriptions                                  | 95  |

| 76 | Generic RNDIS EP4 Size Register 2 (GREP4SZR2) Field Descriptions                                  | 95  |

| 77 | Function Address Register (FADDR) Field Descriptions                                              | 96  |

| 78 | Power Management Register (POWER) Field Descriptions                                              | 96  |

| 79 | Interrupt Register for Endpoint 0 Plus Transmit Endpoints 1 to 4 (INTRTX) Field Descriptions      | 97  |

| 80 | Interrupt Register for Receive Endpoints 1 to 4 (INTRRX) Field Descriptions                       | 97  |

| 81 | Interrupt Enable Register for INTRTX (INTRTXE) Field Descriptions                                 | 98  |

| 82 | Interrupt Enable Register for INTRRX (INTRRXE) Field Descriptions                                 | 98  |

| 83 | Interrupt Register for Common USB Interrupts (INTRUSB) Field Descriptions                         | 99  |

| 84 | Interrupt Enable Register for INTRUSB (INTRUSBE) Field Descriptions                               | 100 |

| 85 | Frame Number Register (FRAME) Field Descriptions                                                  | 100 |

| 86 | Index Register for Selecting the Endpoint Status and Control Registers (INDEX) Field Descriptions | 101 |

| 87 | Register to Enable the USB 2.0 Test Modes (TESTMODE) Field Descriptions                           | 101 |

| 88 | Maximum Packet Size for Peripheral/Host Transmit Endpoint (TXMAXP) Field Descriptions             | 102 |

| 89 | Control Status Register for Peripheral Endpoint 0 (PERI_CSR0) Field Descriptions                  | 103 |

| 90 | Control Status Register for Peripheral Transmit Endpoint (PERI_TXCSR) Field Descriptions          | 104 |

| 91 | Maximum Packet Size for Peripheral Receive Endpoint (RXMAXP) Field Descriptions                   | 105 |

| 92 | Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR) Field Descriptions           | 106 |

| 93 | Count 0 Register (COUNT0) Field Descriptions                                                      |     |

| 94 | Receive Count Register (RXCOUNT) Field Descriptions                                               |     |

| 95 | Configuration Data Register (CONFIGDATA) Field Descriptions                                       | 108 |

| 96 | Transmit and Receive FIFO Register 1 for Endpoint 0 (FIFO0R1) Field Descriptions                  | 109 |

|    |                                                                                                   |     |

| 97  | Transmit and Receive FIFO Register 2 for Endpoint 0 (FIFO0R2) Field Descriptions                          |     |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

| 98  | Transmit and Receive FIFO Register 1 for Endpoint 1 (FIFO1R1) Field Descriptions                          |     |

| 99  | Transmit and Receive FIFO Register 2 for Endpoint 1 (FIFO1R2) Field Descriptions                          |     |

| 100 | Transmit and Receive FIFO Register 1 for Endpoint 2 (FIFO2R1) Field Descriptions                          |     |

| 101 | Transmit and Receive FIFO Register 2 for Endpoint 2 (FIFO2R2) Field Descriptions                          |     |

| 102 | Transmit and Receive FIFO Register 1 for Endpoint 3 (FIFO3R1) Field Descriptions                          |     |

| 103 | Transmit and Receive FIFO Register 2 for Endpoint 3 (FIFO3R2) Field Descriptions                          |     |

| 104 | Transmit and Receive FIFO Register 1 for Endpoint 4 (FIFO4R1) Field Descriptions                          |     |

| 105 | Transmit and Receive FIFO Register 2 for Endpoint 4 (FIFO4R2) Field Descriptions                          |     |

| 106 | Device Control Register (DEVCTL) Field Descriptions                                                       |     |

| 107 | Transmit Endpoint FIFO Size (TXFIFOSZ) Field Descriptions                                                 |     |

| 108 | Receive Endpoint FIFO Size (RXFIFOSZ) Field Descriptions                                                  |     |

| 109 | Transmit Endpoint FIFO Address (TXFIFOADDR) Field Descriptions                                            | 116 |

| 110 | Hardware Version Register (HWVERS) Field Descriptions                                                     | 116 |

| 111 | Receive Endpoint FIFO Address (RXFIFOADDR) Field Descriptions                                             | 117 |

| 112 | CDMA Revision Identification Register 1 (DMAREVID1) Field Descriptions                                    | 117 |

| 113 | CDMA Revision Identification Register 2 (DMAREVID2) Field Descriptions                                    | 117 |

| 114 | CDMA Teardown Free Descriptor Queue Control Register (TDFDQ) Field Descriptions                           | 118 |

| 115 | CDMA Emulation Control Register (DMAEMU) Field Descriptions                                               | 118 |

| 116 | CDMA Transmit Channel <i>n</i> Global Configuration Register 1 (TXGCR1[ <i>n</i> ]) Field Descriptions    | 119 |

| 117 | CDMA Transmit Channel <i>n</i> Global Configuration Register 2 (TXGCR2[ <i>n</i> ]) Field Descriptions    | 119 |

| 118 | CDMA Receive Channel <i>n</i> Global Configuration Register 1 (RXGCR1[ <i>n</i> ]) Field Descriptions     | 120 |

| 119 | CDMA Receive Channel <i>n</i> Global Configuration Register 2 (RXGCR2[ <i>n</i> ]) Field Descriptions     | 120 |

| 120 | Receive Channel <i>n</i> Host Packet Configuration Register 1 A (RXHPCR1A[ <i>n</i> ]) Field Descriptions | 122 |

| 121 | Receive Channel <i>n</i> Host Packet Configuration Register 2 A (RXHPCR2A[ <i>n</i> ]) Field Descriptions | 122 |

| 122 | Receive Channel <i>n</i> Host Packet Configuration Register 1 B (RXHPCR1B[ <i>n</i> ]) Field Descriptions | 123 |

| 123 | Receive Channel <i>n</i> Host Packet Configuration Register 2 B (RXHPCR2B[ <i>n</i> ]) Field Descriptions | 123 |

| 124 | CDMA Scheduler Control Register 1 (DMA_SCHED_CTRL1) Field Descriptions                                    | 124 |

| 125 | CDMA Scheduler Control Register 2 (DMA_SCHED_CTRL2) Field Descriptions                                    | 124 |

| 126 | CDMA Scheduler Table Word <i>n</i> Registers (ENTRYLSW[ <i>n</i> ]) Field Descriptions                    | 125 |

| 127 | CDMA Scheduler Table Word <i>n</i> Registers (ENTRYMSW[ <i>n</i> ]) Field Descriptions                    | 125 |

| 128 | Queue Manager Revision Identification Register 1 (QMGRREVID1) Field Descriptions                          | 126 |

| 129 | Queue Manager Revision Identification Register 2 (QMGRREVID2) Field Descriptions                          | 126 |

| 130 | Queue Manager Queue Diversion Register 1 (DIVERSION1) Field Descriptions                                  | 127 |

| 131 | Queue Manager Queue Diversion Register 2 (DIVERSION2 Field Descriptions                                   | 127 |

| 132 | Queue Manager Free Descriptor/Buffer Starvation Count Register 0 (FDBSC0) Field Descriptions              | 128 |

| 133 | Queue Manager Free Descriptor/Buffer Starvation Count Register 1 (FDBSC1) Field Descriptions              | 128 |

| 134 | Queue Manager Free Descriptor/Buffer Starvation Count Register 2 (FDBSC2) Field Descriptions              | 129 |

| 135 | Queue Manager Free Descriptor/Buffer Starvation Count Register 3 (FDBSC3) Field Descriptions              | 129 |

| 136 | Queue Manager Free Descriptor/Buffer Starvation Count Register 4 (FDBSC4) Field Descriptions              | 130 |

| 137 | Queue Manager Free Descriptor/Buffer Starvation Count Register 5 (FDBSC5) Field Descriptions              | 130 |

| 138 | Queue Manager Free Descriptor/Buffer Starvation Count Register 6 (FDBSC6) Field Descriptions              | 131 |

| 139 | Queue Manager Free Descriptor/Buffer Starvation Count Register 7 (FDBSC7) Field Descriptions              | 131 |

| 140 | Queue Manager Linking RAM Region 0 Base Address Register 1 (LRAM0BASE1) Field Descriptions                | 132 |

| 141 | Queue Manager Linking RAM Region 0 Base Address Register 2 (LRAM0BASE2) Field Descriptions                | 132 |

| 142 | Queue Manager Linking RAM Region 0 Size Register (LRAM0SIZE) Field Descriptions                           | 133 |

| 143 | Queue Manager Linking RAM Region 1 Base Address Register 1 (LRAM1BASE1) Field Descriptions                | 134 |

| 144 | Queue Manager Linking RAM Region 1 Base Address Register (LRAM1BASE2) Field Descriptions                  |     |

| 145 | Queue Manager Queue Pending Register 0 (PEND0) Field Descriptions                                         | 135 |

### www.ti.com

| 146 | Queue Manager Queue Pending Register 1 (PEND1) Field Descriptions                        | 135 |

|-----|------------------------------------------------------------------------------------------|-----|

| 147 | Queue Manager Queue Pending Register 2 (PEND2) Field Descriptions                        | 136 |

| 148 | Queue Manager Queue Pending Register 3 (PEND3) Field Descriptions                        | 136 |

| 149 | Queue Manager Queue Pending Register 4 (PEND4) Field Descriptions                        | 137 |

| 150 | Queue Manager Queue Pending Register 5 (PEND5) Field Descriptions                        | 137 |

| 151 | Queue Manager Memory Region R Base Address Register 1 (QMEMRBASE1[R]) Field Descriptions | 138 |

| 152 | Queue Manager Memory Region R Base Address Register 2 (QMEMRBASE2[R]) Field Descriptions | 138 |

| 153 | Queue Manager Memory Region R Control Register 1 (QMEMRCTRL1[R]) Field Descriptions      | 139 |

| 154 | Queue Manager Memory Region R Control Register 2 (QMEMRCTRL2[R]) Field Descriptions      | 140 |

| 155 | Queue Manager Queue N Control Register 1 D (CTRL1D[N]) Field Descriptions                | 140 |

| 156 | Queue Manager Queue N Control Register 2 D (CTRL2D[N]) Field Descriptions                | 140 |

| 157 | Queue Manager Queue N Status Register A (QSTATA[N]) Field Descriptions                   | 141 |

| 158 | Queue Manager Queue N Status Register 1 B (QSTAT1B[N]) Field Descriptions                | 141 |

| 159 | Queue Manager Queue N Status Register 2 B (QSTAT2B[N]) Field Descriptions                | 141 |

| 160 | Queue Manager Queue N Status Register C (QSTATCIM) Field Descriptions                    | 142 |

## Read This First

### **About This Manual**

This document describes the universal serial bus (USB) controller on the TMS320C5515/14/05/04 digital signal processor (DSP).

### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

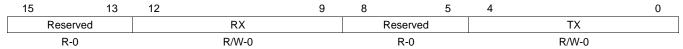

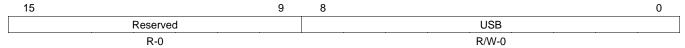

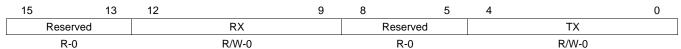

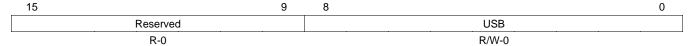

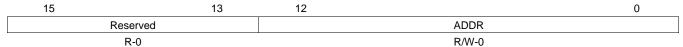

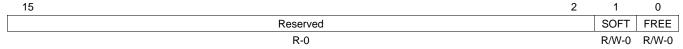

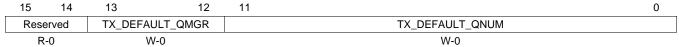

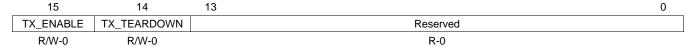

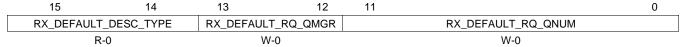

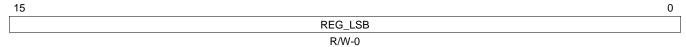

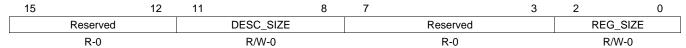

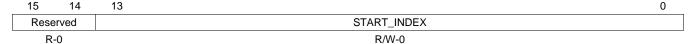

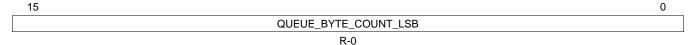

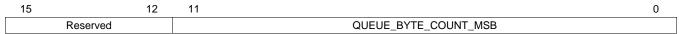

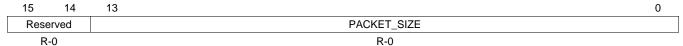

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

### **Related Documentation From Texas Instruments**

The following documents describe the TMS320C5515/14/05/04 digital signal processor (DSP). Copies of these documents are available on the internet at <a href="http://www.ti.com">http://www.ti.com</a>.

- <u>SWPU073</u> TMS320C55x 3.0 CPU Reference Guide. This manual describes the architecture, registers, and operation of the fixed-point TMS320C55x digital signal processor (DSP) CPU.

- <u>SPRU652</u> TMS320C55x DSP CPU Programmer's Reference Supplement. This document describes functional exceptions to the CPU behavior.

- SPRUFO1A TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Inter-Integrated Circuit (I2C) Peripheral User's Guide. This document describes the inter-integrated circuit (I2C) peripheral in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The I2C peripheral provides an interface between the device and other devices compliant with Phillips Semiconductors Inter-IC bus (I2C-bus) specification version 2.1 and connected by way of an I2C-bus. This document assumes the reader is familiar with the I2C-bus specification.

- SPRUFO2 TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Timer/Watchdog Timer User's Guide. This document provides an overview of the three 32-bit timers in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The 32-bit timers of the device are software programmable timers that can be configured as general-purpose (GP) timers. Timer 2 can be configured as a GP, a Watchdog (WD), or both simultaneously.

- SPRUFO3 TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Serial Peripheral Interface (SPI) User's Guide. This document describes the serial peripheral interface (SPI) in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The SPI is a high-speed synchronous serial input/output port that allows a serial bit stream of programmed length (1 to 32 bits) to be shifted into and out of the device at a programmed bit-transfer rate. The SPI supports multi-chip operation of up to four SPI slave devices. The SPI can operate as a master device only.

- SPRUFO4 TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) General-Purpose Input/Output (GPIO) User's Guide. This document describes the general-purpose input/output (GPIO) on the TMS320C5515/14/05/04/VC05/VC04 digital signal processor (DSP) devices. The GPIO peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an input, you can detect the state of an internal register. When configured as an output you can write to an internal register to control the state driven on the output pin.

- SPRUFO5 TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) Universal Asynchronous Receiver/Transmitter (UART) User's Guide. This document describes the universal asynchronous receiver/transmitter (UART) peripheral in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The UART performs serial-to-parallel conversions on data received from a peripheral device and parallel-to-serial conversion on data received from the CPU.

- SPRUFP1 TMS320C5515/05/VC05 Digital Signal Processor (DSP) Successive Approximation (SAR) Analog to Digital Converter (ADC) User's Guide. This document provides an overview of the Successive Approximation (SAR) Analog to Digital Converter (ADC) on the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The SAR is a 10-bit ADC using a switched capacitor architecture which converts an analog input signal to a digital value.

- SPRUFP3 TMS320C5515/05/VC05 Digital Signal Processor (DSP) Liquid Crystal Display Controller (LCDC) User's Guide. This document describes the liquid crystal display controller (LCDC) in the TMS320C5515/14/05/04/VC05/VC04 Digital Signal Processor (DSP) devices. The LCD controller includes a LCD Interface Display Driver (LIDD) controller.

- SPRUFT2— TMS320C5515/14/05/04 DSP Direct Memory Access (DMA) Controller User's Guide This document describes the features and operation of the DMA controller that is available on the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. The DMA controller is used to move data among internal memory, external memory, and peripherals without intervention from the CPU and in the background of CPU operation.

- SPRUGU6— TMS320C5515/14/05/04 DSP External Memory Interface (EMIF) User's Guide. This document describes the operation of the external memory interface (EMIF) in the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. The purpose of the EMIF is to provide a means to connect to a variety of external devices.

- SPRUFO6— TMS320C5515/14/05/04/VC05/VC04 DSP Multimedia Card (MMC)/Secure Digital (SD)

Card Controller This document describes the Multimedia Card (MMC)/Secure Digital (SD) Card

Controller on the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. The multimedia

card (MMC)/secure digital (SD) card is used in a number of applications to provide removable data

storage. The MMC/SD card controller provides an interface to external MMC and SD cards.

- SPRUFX2— TMS320C5515/14/05/04 Digital Signal Processor (DSP) Real-Time Clock (RTC) User's Guide. This document describes the operation of the Real-Time Clock (RTC) module in the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. The RTC also has the capability to wake-up the power management and apply power to the rest of the device through an alarm, periodic interrupt, or external WAKEUP signal.

- SPRUFX4— TMS320C5515/14/05/04 Digital Signal Processor (DSP) Inter-IC Sound (I2S) Bus User's Guide. This document describes the features and operation of Inter-IC Sound (I2S) Bus in the TMS320C5515/14/05/04 Digital Signal Processor (DSP) devices. This peripheral allows serial transfer of full duplex streaming data, usually streaming audio, between DSP and an external I2S peripheral device such as an audio codec.

- SPRUFX5— TMS320C5515 DSP System User's Guide. This document describes various aspects of the TMS320C5515 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

- SPRUGH5— TMS320C5505 DSP System User's Guide. This document describes various aspects of the TMS320C5505 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

- SPRUFX6— TMS320C5514 DSP System User's Guide. This document describes various aspects of the TMS320C5514 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

- SPRUGH6— TMS320C5504 DSP System User's Guide. This document describes various aspects of the TMS320C5504 digital signal processor (DSP) including: system memory, device clocking options and operation of the DSP clock generator, power management features, interrupts, and system control.

- SPRUGH9— TMS320C5515 DSP Universal Serial Bus 2.0 (USB) Controller User's Guide This document describes the universal serial bus 2.0 (USB) in the TMS320C5515 Digital Signal Processor (DSP) devices. The USB controller supports data throughput rates up to 480 Mbps. It provides a mechanism for data transfer between USB devices.

- SPRABB6— FFT Implementation on the TMS320VC5505, TMS320C5505, and TMS320C5515 DSPs

This document describes FFT computation on the TMS320VC5505 and TMS320C5505/15 DSPs devices.

# Universal Serial Bus (USB) Controller

| Торіс | Page |

|-------|------|

|       |      |

Introduction www.ti.com

### 1 Introduction

This document describes the universal serial bus (USB) controller. The controller complies with the USB 2.0 standard high-speed and full-speed functions. In addition, the four test modes for high-speed operation described in the USB 2.0 specification are supported. It also allows options that allow the USB controller to be forced into full-speed mode and high-speed mode that may be used for debug purposes.

### 1.1 Purpose of the Peripheral

The USB controller provides a low-cost connectivity solution for consumer portable devices by providing a mechanism for data transfer between USB devices up to 480 Mbps. With the USB controller, you can use the DSP to create a high-speed USB slave device that is complaint with the Universal Serial Bus Specification version 2.0.

### 1.2 Features

The USB has the following features:

- Operating as a peripheral, it complies with the USB 2.0 standard for high-speed (480 Mbps) and full-speed (12 Mbps) operation with a host

- Supports 4 simultaneous RX and TX endpoints, in addition to control endpoint, more devices can be supported by dynamically switching endpoints states

- Each endpoint (other than endpoint 0) can support all transfer types (control, bulk, interrupt, and isochronous)

- Includes a 4K endpoint FIFO RAM, and supports programmable FIFO sizes

- Includes a DMA controller that supports 4 TX and 4 RX DMA channels

- Includes four types of Communications Port Programming Interface (CPPI) 4.1 DMA compliant transfer modes, Transparent, Generic RNDIS, RNDIS, and Linux CDC mode of DMA for accelerating RNDIS type protocols using short packet termination over USB

- DMA supports single data transfer size up to 4Mbytes

www.ti.com Introduction

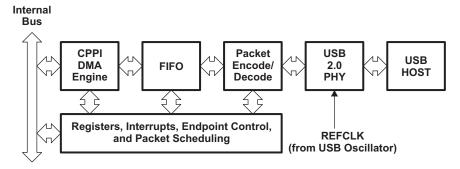

### 1.3 Functional Block Diagram

The USB functional block diagram is shown in Figure 1.

Figure 1. Functional Block Diagram

### 1.4 Industry Standard(s) Compliance Statement

This device conforms to USB 2.0 Specification.

### 2 Architecture

### 2.1 Clock Control

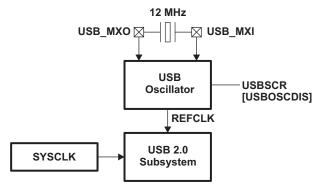

Figure 2 shows the clock connections for the USB2.0 module. Note that there is a built-in oscillator that generates a 12 MHz reference clock for the internal PLL of the USB 2.0 subsystem. The USB2.0 subsystem peripheral bus clock is sourced from the system clock (SYSCLK).

**NOTE:** The device system clock (SYSCLK) must be at least 30 MHz for proper USB operation.

Figure 2. USB Clocking Diagram

### 2.2 Signal Descriptions

The USB controller provides the I/O signals listed in Table 1.

**Table 1. USB Terminal Functions**

| Name         | I/O <sup>(1)</sup> | Description                                                               |

|--------------|--------------------|---------------------------------------------------------------------------|

| USB_DP       | A I/O/Z            | USB D+ (differential signal pair)                                         |

| USB_DM       | A I/O/Z            | USB D- (differential signal pair)                                         |

| USB_VBUS     | ΑI                 | Five volt input that signifies that VBUS is connected.                    |

| USB_REXT     | A I/O/Z            | External resistor connect.                                                |

| USB_MXI      | 1                  | 12 MHz crystal oscillator input.                                          |

| USB_MXO      | 0                  | 12 MHz crystal oscillator output.                                         |

| USB_LDOO     | PWR                | USB module LDO output. This output is regulated to 1.3V.                  |

| USB_LDOI     | PWR                | USB module LDO input. This input handles a voltage range of 1.8V to 3.6V. |

| VSS_USBOSC   | PWR                | 3.3V USB oscillator power supply.                                         |

| VDD_USBPLL   | PWR                | 3.3V USB PLL power supply.                                                |

| VDDA_USBXCVR | PWR                | 3.3V USB transceiver power supply.                                        |

| VDDA_USB     | PWR                | 1.3V USB analog power supply.                                             |

| VDD_USB      | PWR                | 1.3V USB PLL and oscillator digital power supply.                         |

| VSS_USBOSC   | GND                | USB oscillator ground.                                                    |

| VSS_USBPLL   | GND                | USB PLL ground.                                                           |

| VSSA_USBXCVR | GND                | USB transceiver ground.                                                   |

| VSS_USBXCVR  | GND                | USB ground for reference circuits.                                        |

| VSSA_USB     | GND                | USB analog ground.                                                        |

| VSS_USB      | GND                | USB PLL and oscillator digital ground.                                    |

<sup>(1)</sup> I = Input, O = Output, Z = High impedance, GND = Ground, A = Analog signal, PWR = Power supply pin.

### 2.3 Memory Map

The USB controller can access internal single-access RAM (SARAM) and external memory. It cannot access dual-access RAM (DARAM). The starting address for SARAM and external memory is different from the point-of-view of the CPU and USB controller. The memory map, as seen by the USB controller and the CPU, is shown in Table 2.

**Table 2. USB Controller Memory Map**

| USB Start Byte Address    | CPU Start Word Address  | CPU Memory Map | USB Controller Memory Map |

|---------------------------|-------------------------|----------------|---------------------------|

| 0001 0000h <sup>(1)</sup> | 00 0000h <sup>(1)</sup> | DARAM          | Reserved                  |

| 0009 0000h                | 00 8000h                | SARAM          | SARAM                     |

| 0100 0000h                | 02 8000h                | EMIF CS0       | EMIF CS0                  |

| 0200 0000h                | 40 0000h                | EMIF CS2       | EMIF CS2                  |

| 0300 0000h                | 60 0000h                | EMIF CS3       | EMIF CS3                  |

| 0400 0000h                | 70 0000h                | EMIF CS4       | EMIF CS4                  |

| 0500 0000h                | 78 0000h                | EMIF CS5       | EMIF CS5                  |

<sup>(1)</sup> CPU word addresses 00 0000h - 00 005Fh (which correspond to byte addresses 00 0000h - 00 00BFh) are reserved for the memory-mapped registers (MMRs) of the DSP CPU.

### 2.4 USB\_DP/USB\_DM Polarity Inversion

The polarity of the USB data pins (USB\_DP and USB\_DM) can be inverted through the USBDATPOL bit of the USB system control register (USBSCR). Since USB\_DP is equal to the inverse of USB\_DM (they form a differential pair), inverting these pins allows you to effectively swap their function. This allows flexibility in board design by allowing different USB connector configurations. In particular, this allows for mounting the connector on either side of the board and for arranging the data pins so they do not physically cross each other.

### 2.5 Indexed and Non-Indexed Registers

The USB controller provides two mechanisms of accessing the endpoint control and status registers:

- Indexed Endpoint Control/Status Registers: These registers are located at I/O address 8410h to 841Fh. The endpoint is selected by programming the INDEX register of the controller.

- Non-indexed Endpoint Control/Status Registers: These registers are located at I/O address 8500h to 854Fh. Registers at address 8500h to 850Fh map to Endpoint 0; at address 8510h to 851Fh map to Endpoint 1, and so on.

For detailed information about the USB controller registers, see Section 3.

### 2.6 USB PHY Initialization

The general procedure for USB PHY initialization consists of enabling the USB on-chip oscillator, configuring PHY parameters, and finally resetting the PHY. The detailed USB PHY initialization sequence is as follows:

- 1. The bits USBOSCBIASDIS and USBOSCDIS in the USB system control register (USBSCR) should be cleared to 0 to enable the on-chip USB oscillatory if not enabled already.

- Wait cycles for the on-chip oscillator to stabilize. Refer to the device-specific data manual for oscillator stabilization time.

- 3. To configure the PHY for normal operation, the bits USBPWDN, USBSESSEND, and USBPLLEN in USBSCR should be cleared to 0, the USBVBUSDET bit should be set to 1, and the USBDATPOL bit should be set according to the system requirements (set to 1 for normal operation).

- 4. Enable the USB clock by clearing USBCG to 0 in the peripheral clock gating configuration register 2 (PCGCR2) register.

- 5. Set the USBCLKSTPREQ bit.

- 6. Set COUNT = 20h in the peripheral software reset counter register (PSRCR).

- 7. Reset the USB controller by setting USB\_RST to 1 in the peripheral reset control register (PRCR). This bit will self-clear once the reset has been completed.

For more information on the PCGCR2, CLKSTOP, PSRCR, and PRCR, see the *TMS320C5505 System User's Guide* (SPRUGH5).

During the normal operation, the USB PHY PLL should run at 60 MHz. This clock can be probed on the device. One can monitor different clocks of the device by probing the CLKOUT pin for debugging purposes. Different clocks can be routed to this pin by setting both register CCSSR (1C24h at IO space) and CPU register ST3 55.

To monitor the USB PHY PLL, the setting of register CCSSR should be as follows:

When CCSSR = 0x000F; USB PHY clock (60 MHz) is routed to the CLKOUT pin

The setting of bit-2 (CLKOFF) of register ST3\_55:

- When CLKOFF = 0, the CLKOUT pin is enabled

- When CLKOFF = 1, the CLKOUT pin is disabled

After these settings, the 60 MHz clock can be probed on CLKOUT pin.

### 2.6.1 USB System Control Register (USBSCR)

The USB system control register is used to disable the USB on-chip oscillator and to power-down the USB.

The USB system control register (USBSCR) is shown in Figure 3 and described in Table 3.

### Figure 3. USB System Control Register (USBSCR) [1C32h]

| 15       | 14         | 13         | 12       | 11            |           |       | 8    |

|----------|------------|------------|----------|---------------|-----------|-------|------|

| USBPWDN  | USBSESSEND | USBVBUSDET | USBPLLEN |               | Rese      | erved |      |

| R/W-1    | R/W-0      | R/W-1      | R/W-0    |               | R         | -0    |      |

| 7        | 6          | 5          | 4        | 3             | 2         | 1     | 0    |

| Reserved | USBDATPOL  | Reserved   |          | USBOSCBIASDIS | USBOSCDIS | BYTE  | MODE |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 3. USB System Control Register (USBSCR) Field Descriptions

| Bit  | Field         | Value | Description                                                                    |  |  |

|------|---------------|-------|--------------------------------------------------------------------------------|--|--|

| 15   | USBPWDN       |       | USB module power.                                                              |  |  |

|      |               | 0     | USB module is powered.                                                         |  |  |

|      |               | 1     | USB module is powered-down.                                                    |  |  |

| 14   | USBSESSEND    |       | USB VBUS session end comparator enable.                                        |  |  |

|      |               | 0     | USB VBUS session end comparator is disabled.                                   |  |  |

|      |               | 1     | USB VBUS session end comparator is enabled.                                    |  |  |

| 13   | USBVBUSDET    |       | USB VBUS detect enable.                                                        |  |  |

|      |               | 0     | USB VBUS detect comparator is disabled.                                        |  |  |

|      |               | 1     | USB VBUS detect comparator is enabled.                                         |  |  |

| 12   | USBPLLEN      |       | USB PLL enable.                                                                |  |  |

|      |               | 0     | Normal USB operation.                                                          |  |  |

|      |               | 1     | Override USB suspend end behavior and force release of PLL from suspend state. |  |  |

| 11-7 | Reserved      | 0     | Reserved. Always write 0 to these bits.                                        |  |  |

| 6    | USBDATPOL     |       | USB data polarity bit.                                                         |  |  |

|      |               | 0     | Reverse polarity on DP and DM signals.                                         |  |  |

|      |               | 1     | Normal polarity.                                                               |  |  |

| 5-4  | Reserved      | 0     | Reserved.                                                                      |  |  |

| 3    | USBOSCBIASDIS |       | USB internal oscillator bias resistor disable.                                 |  |  |

|      |               | 0     | Internal oscillator bias resistor enabled (normal operating mode).             |  |  |

|      |               | 1     | Internal oscillator bias resistor disabled.                                    |  |  |

| 2    | USBOSCDIS     |       | USB oscillator disable bit.                                                    |  |  |

|      |               | 0     | USB internal oscillator enable.                                                |  |  |

|      |               | 1     | USB internal oscillator disabled.                                              |  |  |

| 1-0  | BYTEMODE      |       | USB byte mode select bits.                                                     |  |  |

|      |               | 0     | Word accesses by the CPU are allowed.                                          |  |  |

|      |               | 1h    | Byte accesses by the CPU are allowed (high byte is selected).                  |  |  |

|      |               | 2h    | Byte accesses by the CPU are allowed (low byte is selected).                   |  |  |

|      |               | 3h    | Reserved.                                                                      |  |  |

#### 2.7 Dynamic FIFO Sizing

The USB controller supports a total of 4K RAM to dynamically allocate FIFO to all endpoints. The allocation of FIFO space to the different endpoints requires the specification for each Tx and Rx endpoint

- The start address of the FIFO within the RAM block

- The maximum size of packet to be supported

- Whether double-buffering is required.

These details are specified through four registers, which are added to the indexed area of the memory map. That is, the registers for the desired endpoint are accessed after programming the INDEX register with the desired endpoint value. Section 3.46, Section 3.47, Section 3.48, and Section 3.50 provide details of these registers.

NOTE: The option of setting FIFO sizes dynamically only applies to Endpoints 1 to 4. Endpoint 0 FIFO has a fixed size (64 bytes) and a fixed location (start address 0).

It is the responsibility of the firmware to ensure that all the Tx and Rx endpoints that are active in the current USB configuration have a block of RAM assigned exclusively to that endpoint that is at least as large as the maximum packet size set for that endpoint.

#### 2.8 **USB Controller Peripheral Mode Operation**

The USB controller can be used as a high-speed or a full-speed USB peripheral device attached to a conventional USB host (such as a PC).

The USB2.0 controller will transition to session when it sees power (must be greater or equal to 4.01V) on the USB0\_VBUS pin, assuming that the firmware has set the SOFTCONN bit in the POWER register and has enabled the data lines and there is an external host sourcing power on the USB0\_VBUS line. The USB 2.0 controller will then set the SESSION bit upon detecting the power on the USB0 VBUS line and it will connect its 1.5Kohm pull-up resistor so it signifies to the external host out it is a Full-Speed device. Note that even when operating as a High-Speed; it has to first come up as Full-Speed. The USB2.0 controller will then wait for a reset signal from the host.

#### 2.8.1 **USB Interrupts**

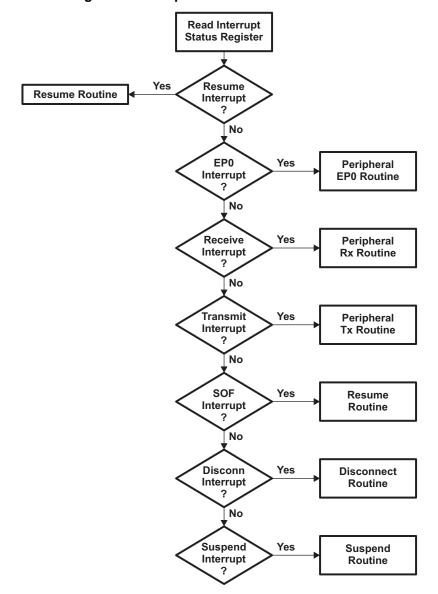

The USB controller interrupts the CPU on completion of the data transfer on any of the endpoints or on detecting reset, resume, suspend, connect, disconnect, or start-of-frame (SOF) on the bus.

When the CPU is interrupted with a USB interrupt, it needs to read the interrupt status register to determine the endpoints that have caused the interrupt and jump to the appropriate routine. If multiple endpoints have caused the interrupt, endpoint 0 should be serviced first followed by the other endpoints. The suspend interrupt should be serviced last.

The flowchart in Figure 4 describes the interrupt service routine for the USB module.

The following sections describe the programming of USB controller in peripheral mode.

Figure 4. Interrupt Service Routine Flow Chart

### 2.8.2 Connect, Suspend Mode, and Reset Signaling

The following sections describe the operation of the USB controller during connect, suspend mode, and USB reset.

### 2.8.2.1 Soft Connect

After a reset, the SOFTCONN bit in the POWER register is cleared to 0. The controller will therefore appear disconnected until the software has set the SOFTCONN bit to 1. The application software can then choose when to set the PHY into its normal mode. Systems with a lengthy initialization procedure may use this to ensure that initialization is complete and the system is ready to perform enumeration before connecting to the USB.

Once the SOFTCONN bit of the POWER register has been set, the software can also simulate a disconnect by clearing this bit to 0.

### 2.8.2.2 Suspend Mode

The controller monitors activity on the bus and when no activity has occurred for 3 ms, it goes into Suspend mode. If the Suspend interrupt has been enabled, an interrupt will be generated.

At this point, the controller can be left active (and hence able to detect when Resume signaling occurs on the USB), or the application may arrange to disable the controller by stopping its clock. However, the controller will not then be able to detect Resume signaling on the USB. As a result, some external hardware will be needed to detect Resume signaling (by monitoring the DM and DP signals) so that the clock to the controller can be restarted.

When Resume signaling occurs on the bus, first the clock to the controller must be restarted if necessary. Then the controller will automatically exit Suspend mode. If the Resume interrupt is enabled, an interrupt will be generated.

If the software wants to initiate a remote wake-up while the controller is in Suspend mode, it should write to the POWER register to set the RESUME bit to 1. The software should then leave this bit set for approximately 10 ms (minimum of 2 ms, a maximum of 15 ms) before resetting it to 0.

NOTE: No resume interrupt will be generated when the software initiates a remote wake-up.

### 2.8.2.3 Reset Signaling

If the HSENA bit in the POWER register was set, the controller also tries to negotiate for high-speed operation.

Whether high-speed operation is selected is indicated by the HSMODE bit of the POWER register.

When the application software receives a reset interrupt, it should close any open pipes and wait for bus enumeration to begin.

#### 2.8.3 **Control Transactions**

Endpoint 0 is the main control endpoint of the core. The software is required to handle all the standard device requests that may be sent or received via endpoint 0. These are described in Universal Serial Bus Specification, Revision 2.0, Chapter 9. The protocol for these device requests involves different numbers and types of transactions per transfer. To accommodate this, the software needs to take a state machine approach to command decoding and handling.

The Standard Device Requests received by a USB peripheral device can be divided into three categories: Zero Data Requests (in which all the information is included in the command). Write Requests (in which the command will be followed by additional data), and Read Requests (in which the device is required to send data back to the host).

This section looks at the sequence of actions that the software must perform to process these different types of device request.

NOTE: The Setup packet associated with any standard device request should include an 8-byte command. Any setup packet containing a command field of anything other than 8 bytes will be automatically rejected by the controller.

#### 2.8.3.1 Zero Data Requests

Zero data requests have all their information included in the 8-byte command and require no additional data to be transferred. Examples of Zero Data standard device requests are:

- SET\_FEATURE

- CLEAR FEATURE

- SET\_ADDRESS

- SET CONFIGURATION

- SET INTERFACE

The sequence of events will begin, as with all requests, when the software receives an endpoint 0 interrupt. The RXPKTRDY bit of the PERI CSR0 register will also have been set. The 8-byte command should then be read from the endpoint 0 FIFO, decoded, and the appropriate action taken.

For example, if the command is SET ADDRESS, the 7-bit address value contained in the command should be written to the FADDR register. The PERI\_CSR0 register should then be written to set the SERV RXPKTRDY bit (indicating that the command has been read from the FIFO) and to set the DATAEND bit (indicating that no further data is expected for this request). The interval between setting the SERV\_RXPKTRDY bit and setting the DATAEND bit should be very small to avoid getting a SetupEnd error condition.

When the host moves to the status stage of the request, a second endpoint 0 interrupt will be generated to indicate that the request has completed. No further action is required from the software. The second interrupt is just a confirmation that the request completed successfully. For SET ADDRESS command, the address should be set in the FADDR register only after the status stage interrupt is received.

If the command is an unrecognized command, or for some other reason cannot be executed, then when it has been decoded, the PERI CSR0 register should be written to set the SERV RXPKTRDY bit and to set the SENDSTALL bit. When the host moves to the status stage of the request, the controller will send a STALL to tell the host that the request was not executed. A second endpoint 0 interrupt will be generated and the SENTSTALL bit in the PERI CSR0 register will be set.

If the host sends more data after the DATAEND bit has been set, then the controller will send a STALL. An endpoint 0 interrupt will be generated and the SENTSTALL bit in the PERI\_CSR0 register will be set.

NOTE: DMA is not supported for endpoint 0, so the command should be read by accessing the endpoint 0 FIFO register.

### 2.8.3.2 Write Requests

Write requests involve an additional packet (or packets) of data being sent from the host after the 8-byte command. An example of a Write standard device request is: SET DESCRIPTOR.