# TMS320DM647/DM648 DSP 3 Port Switch (3PSW) Ethernet Subsystem

# **User's Guide**

Literature Number: SPRUF57B July 2009

# **Contents**

| Pref | ace     |                                                                                     | 13         |

|------|---------|-------------------------------------------------------------------------------------|------------|

| 1    | Introdu | ction                                                                               | 16         |

|      | 1.1     | Features                                                                            | 16         |

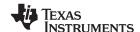

|      | 1.2     | Block Diagram                                                                       | 17         |

|      | 1.3     | Signal Summary                                                                      | 18         |

|      | 1.4     | Clocks                                                                              | 18         |

| 2    | Compo   | nents                                                                               | 20         |

|      | 2.1     | Communication Processor Gigabit Ethernet Switch (3pGSw)                             | 20         |

|      | 2.2     | Serial Gigabit Media Independent Interface (SGMII)                                  | 21         |

|      | 2.3     | MDIO                                                                                | 21         |

|      | 2.4     | Serializer/Deserializer Module (SerDes)                                             | 22         |

|      | 2.5     | Interrupts                                                                          | 22         |

| 3    | Softwa  | re Operation                                                                        | 25         |

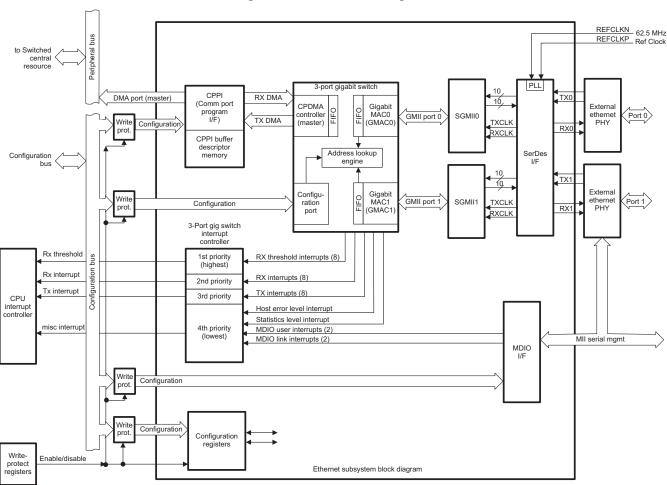

|      | 3.1     | Buffer Descriptors                                                                  | 25         |

|      | 3.2     | Transmit Operation                                                                  | 32         |

|      | 3.3     | Receive Operation                                                                   | 34         |

|      | 3.4     | Initialization and Configuration of 3-Port Gigabit Switch Subsystem                 | 36         |

|      | 3.5     | Address Lookup Engine (ALE)                                                         | 38         |

|      | 3.6     | MDIO Module Operation                                                               | 46         |

| 4    | Chip Lo | evel Configuration Registers                                                        | <b>47</b>  |

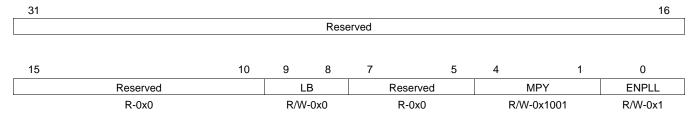

|      | 4.1     | PLL Configuration Register (CFGPLL)                                                 | 47         |

|      | 4.2     | Receiver Configuration Register (CFGRX0/1)                                          | 48         |

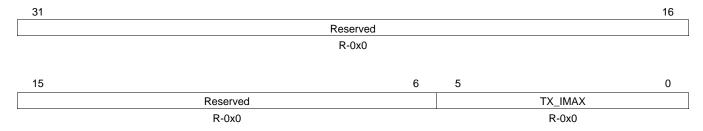

|      | 4.3     | Transmitter Configuration Register (CFGTX0/1)                                       | 51         |

| 5    | 3-Port  | Gigabit Switch (CPSW) Registers                                                     | <b>53</b>  |

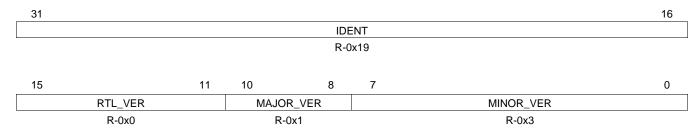

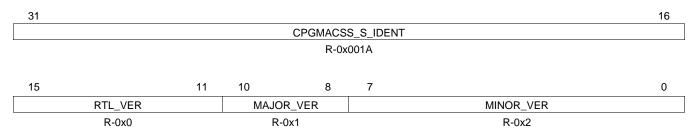

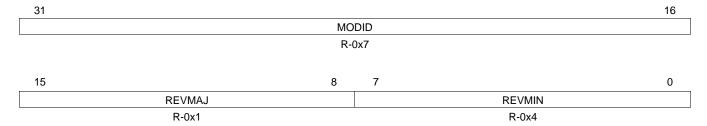

|      | 5.1     | 3pGSw ID Version Register (CPSW_ID_VER)                                             | 58         |

|      | 5.2     | 3pGSw Switch Control Register (CPSW_CONTROL)                                        | 59         |

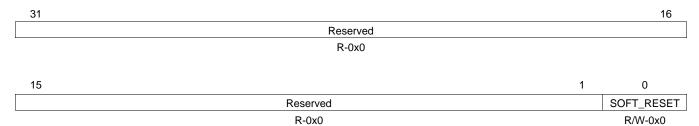

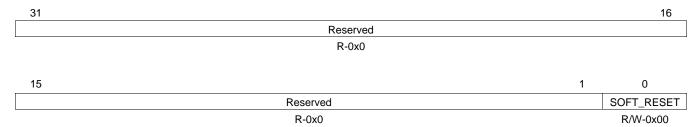

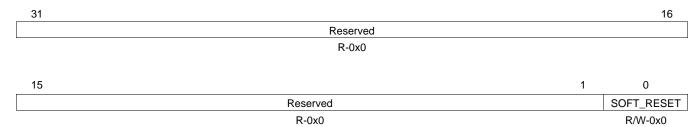

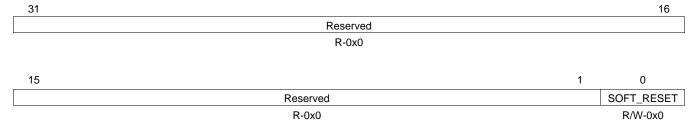

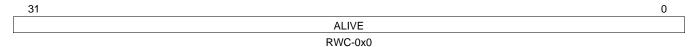

|      | 5.3     | 3pGSw Soft Reset Register (CPSW_SOFT_RESET)                                         | 61         |

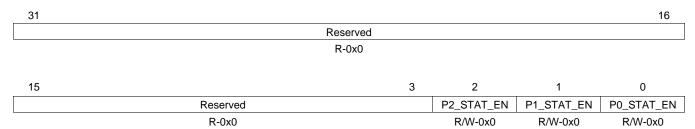

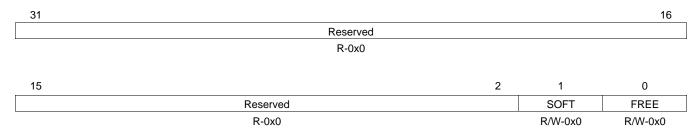

|      | 5.4     | 3pGSw Statistics Port Enable Register (CPSW_STAT_PORT_EN)                           | 62         |

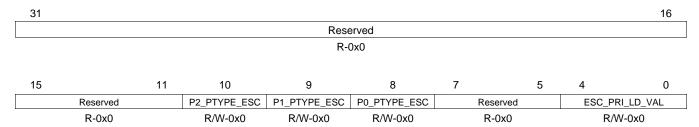

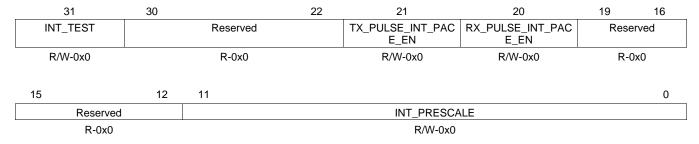

|      | 5.5     | 3pGSw Transmit Priority Type Register (CPSW_PTYPE)                                  | 63         |

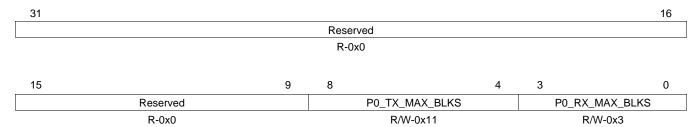

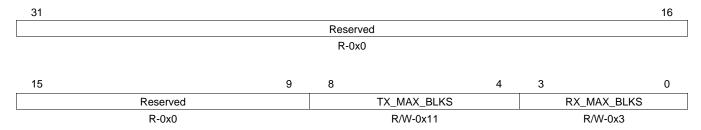

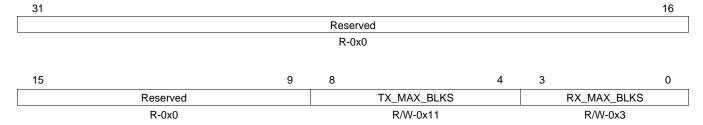

|      | 5.6     | 3pGSw Port 0 Maximum FIFO Blocks Register (P0_MAX_BLKS)                             | 64         |

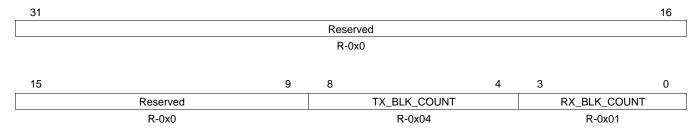

|      | 5.7     | 3pGSw Port 0 FIFO Block Usage Count Register (Read Only) (P0_BLK_CNT)               | 65         |

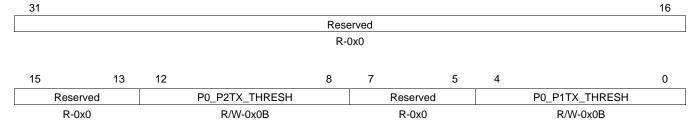

|      | 5.8     | 3pGSw Port 0 Flow Control Threshold Register (P0_FLOW_THRESH)                       | 65         |

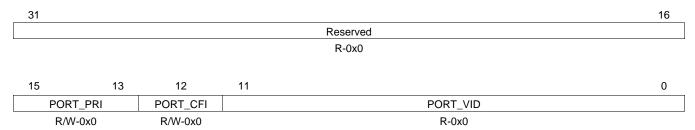

|      | 5.9     | 3pGSw Port 0 VLAN Register (P0_PORT_VLAN)                                           | 66         |

|      | 5.10    | 3pGSw Port 0 TX Header Priority to Switch Priority Mapping Register (P0_TX_PRI_MAP) | 67         |

|      | 5.11    | 3pGSw GMAC0 Short Gap Threshold Register (GMAC0_GAP_THRESH)                         | 68         |

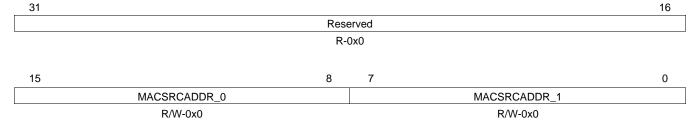

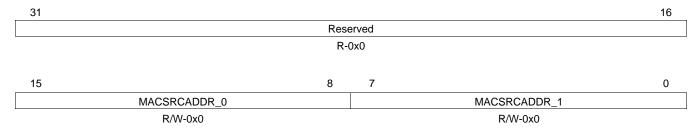

|      | 5.12    | 3pGSw GMAC0 Source Address Low Register (GMAC0_SA_LO)                               | 68         |

|      | 5.13    | 3pGSw GMAC0 Source Address High Register (GMAC0_SA_HI)                              | 69         |

|      | 5.14    | 3pGSw Port 1 Maximum FIFO Blocks Register (DM648 only) (P1_MAX_BLKS)                | <b>7</b> 0 |

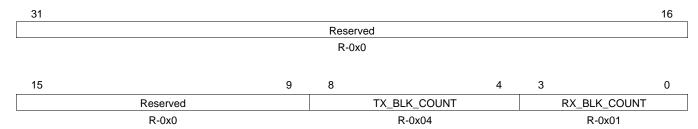

|      | 5.15    | 3pGSw Port 1 FIFO Block Usage Count Register (Read Only) (DM648 only) (P1_BLK_CNT)  | 71         |

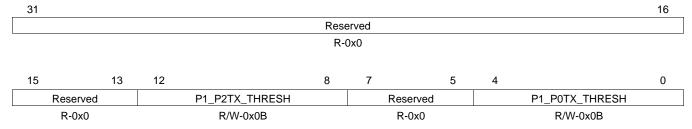

|      | 5.16    | 3pGSw Port 1 Flow Control Threshold Register (DM648 only) (P1_FLOW_THRESH)          |            |

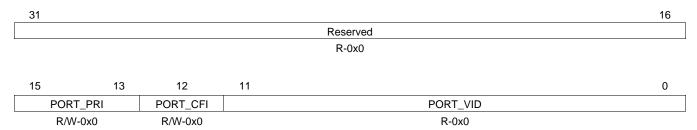

|      | 5.17    | 3pGSw Port 1 VLAN Register (DM648 only) (P1_PORT_VLAN)                              | 72         |

|      |         |                                                                                     |            |

| 5.18 | 3pGSw Port 1 TX Header Priority to Switch Priority Mapping Register (DM648 only) (P1_TX_PRI_MAP)  | 73         |

|------|---------------------------------------------------------------------------------------------------|------------|

| 5.19 | 3pGSw GMAC1 Short Gap Threshold Register (DM648 only) (GMAC1_GAP_THRESH)                          |            |

| 5.20 | 3pGSw GMAC1 Source Address Low Register (DM648 only) (GMAC1_SA_LO)                                |            |

| 5.21 | 3pGSw GMAC1 Source Address High Register (DM648 only) (GMAC1_SA_HI)                               |            |

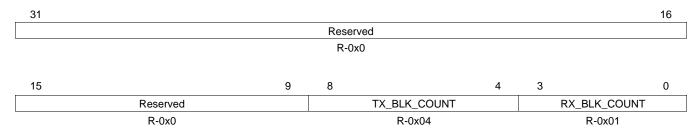

| 5.22 | 3pGSw Port 2 Maximum FIFO Blocks Register (P2_MAX_BLKS)                                           |            |

| 5.23 | 3pGSw Port 2 FIFO Block Usage Count Register (Read Only) (P2_BLK_CNT)                             |            |

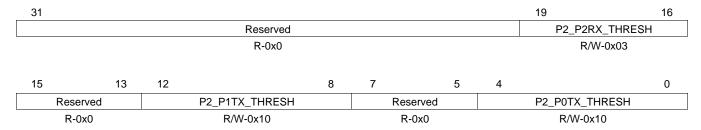

| 5.24 | 3pGSw Port 2 Flow Control Threshold Register (P2_FLOW_THRESH)                                     |            |

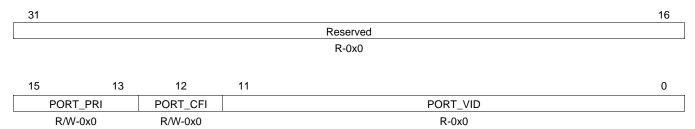

| 5.25 | 3pGSw Port 2 VLAN Register (P2_PORT_VLAN)                                                         |            |

| 5.26 | 3pGSw Port 2 TX (CPDMA RX) Header Priority to Switch Priority Mapping Register                    |            |

| 0.20 | (P2_TX_PRI_MAP)                                                                                   | <b>7</b> 9 |

| 5.27 | 3pGSw CPDMA TX (Port 2 Rx) Packet Priority to Header Priority Mapping Register (CPDMA_TX_PRI_MAP) | 80         |

| 5.28 | 3pGSw CPDMA RX (Port 2 TX) Switch Priority to DMA Channel Mapping Register (CPDMA_RX_CH_MAP)      |            |

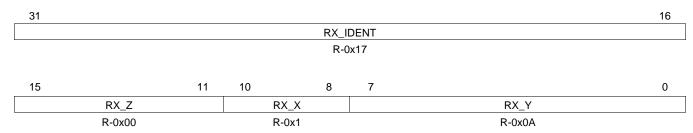

| 5.29 | GMAC0 ID/Version Register (GMAC0_IDVER)                                                           | 82         |

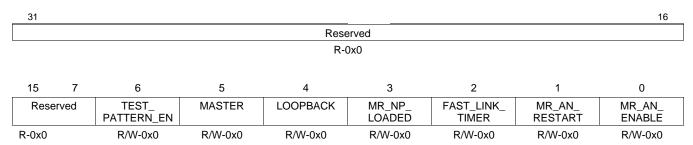

| 5.30 | GMAC0 MAC Control Register (GMAC0_MACCONTROL)                                                     |            |

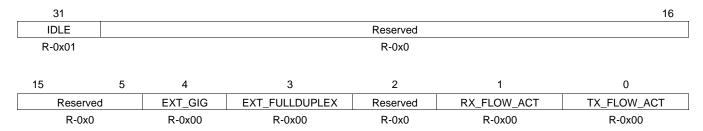

| 5.31 | GMAC0 MAC Status Register (GMAC0_MACSTATUS)                                                       |            |

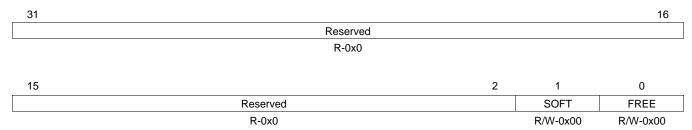

| 5.32 | GMAC0 Soft Reset Register (GMAC0_SOFT_RESET)                                                      |            |

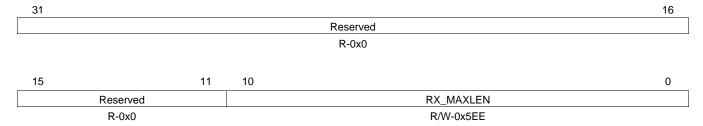

| 5.33 | GMAC0 RX Maximum Length Register (GMAC0_RX_MAXLEN)                                                |            |

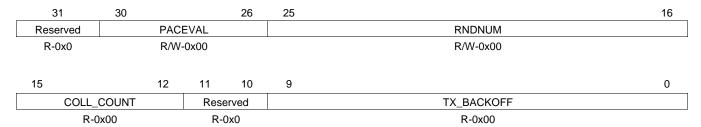

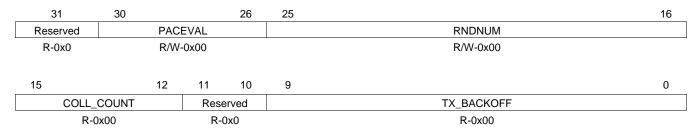

| 5.34 | GMAC0 Backoff Test Register (GMAC0_BOFFTEST)                                                      |            |

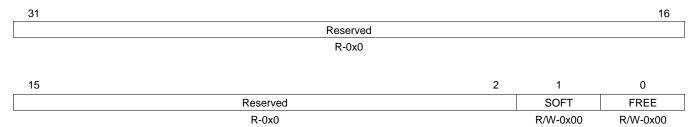

| 5.35 | GMAC0 Emulation Control Register (GMAC0_EMCONTROL)                                                |            |

| 5.36 | GMAC0 Rx Packet Priority to Header Priority Mapping Register (GMAC0_RX_PRI_MAP)                   |            |

| 5.37 | GMAC1 ID/Version Register (DM648 only) (GMAC1_IDVER)                                              |            |

| 5.38 | GMAC1 MAC Control Register (DM648 only) (GMAC1_MACCONTROL)                                        |            |

| 5.39 | GMAC1 MAC Status Register (DM648 only) (GMAC1_MACSTATUS)                                          |            |

| 5.40 | GMAC1 Soft Reset Register (DM648 only) (GMAC1_SOFT_RESET)                                         |            |

| 5.41 | GMAC1 RX Maximum Length Register (DM648 only) (GMAC1_RX_MAXLEN)                                   |            |

| 5.42 | GMAC1 Backoff Test Register (DM648 only) (GMAC1_BOFFTEST)                                         |            |

| 5.43 | GMAC1 Emulation Control Register (DM648 only) (GMAC1_EMCONTROL)                                   |            |

| 5.44 | GMAC1 Rx Packet Priority to Header Priority Mapping Register (DM648 only) (GMAC1_RX_PRI_MAP)      |            |

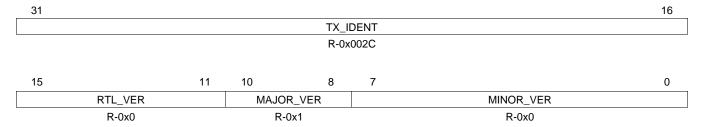

| 5.45 | CPDMA_REGS TX Identification and Version Register (TX_IDVER)                                      |            |

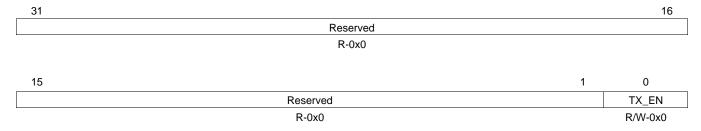

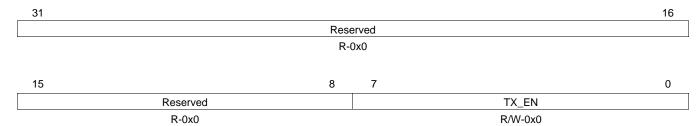

| 5.46 | CPDMA_REGS TX Control Register (TX_CONTROL).                                                      |            |

| 5.47 | CPDMA_REGS TX Teardown Register (TX_TEARDOWN)                                                     |            |

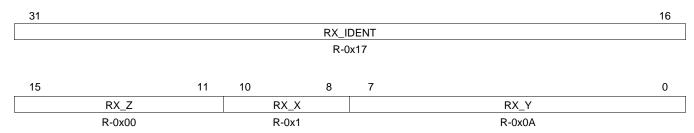

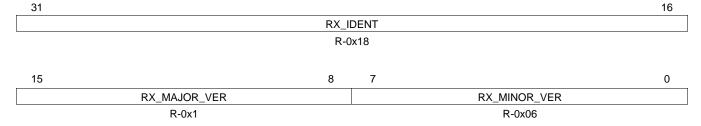

| 5.48 | CPDMA_REGS RX Identification and Version Register (RX_IDVER)                                      |            |

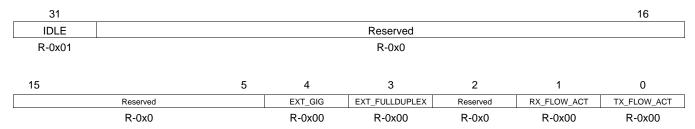

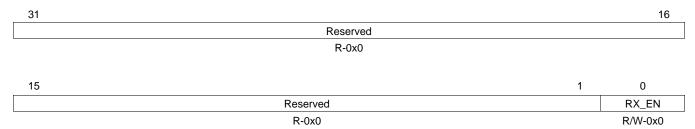

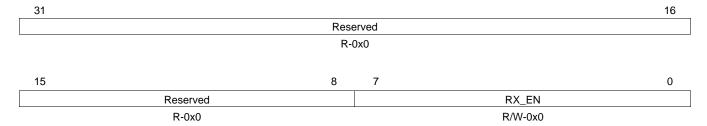

| 5.49 | CPDMA_REGS RX Control Register (RX_CONTROL)                                                       |            |

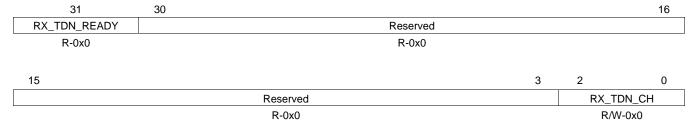

| 5.50 | CPDMA_REGS RX Teardown Register (RX_TEARDOWN)                                                     |            |

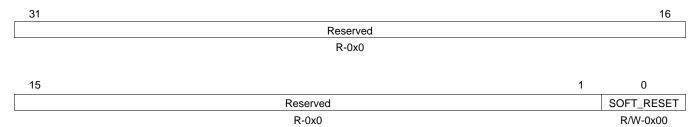

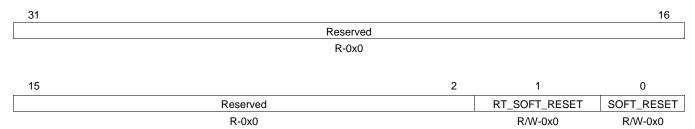

| 5.51 | CPDMA_REGS Soft Reset Register (SOFT_RESET)                                                       |            |

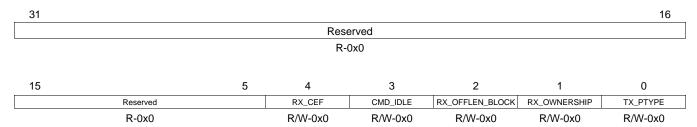

| 5.52 | CPDMA_REGS CPDMA Control Register (DMACONTROL)                                                    |            |

| 5.53 | CPDMA_REGS CPDMA Status Register (DMASTATUS)                                                      |            |

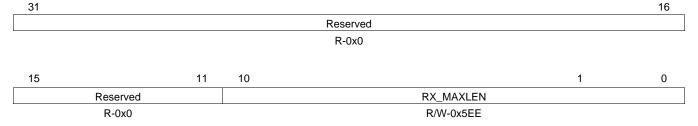

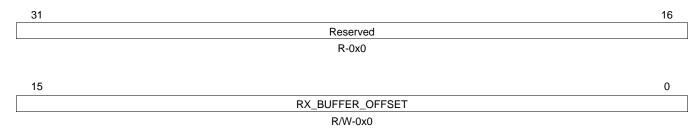

| 5.54 | CPDMA_REGS Receive Buffer Offset Register (RX_BUFFER_OFFSET)                                      |            |

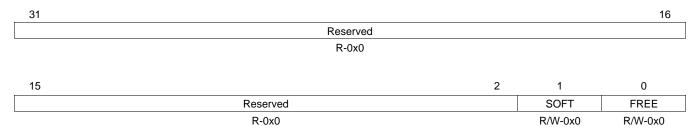

| 5.55 | CPDMA_REGS Emulation Control Register (EMCONTROL)                                                 |            |

| 5.56 | CPDMA_INT TX Interrupt Status Register (Raw Value) (TX_INTSTAT_RAW)                               |            |

| 5.57 | CPDMA_INT TX Interrupt Status Register (Masked Value) (TX_INTSTAT_MASKED)                         |            |

| 5.58 | CPDMA_INT TX Interrupt Mask Set Register (TX_INTMASK_SET)                                         |            |

| 5.59 | CPDMA_INT TX Interrupt Mask Clear Register (TX_INTMASK_CLEAR)                                     |            |

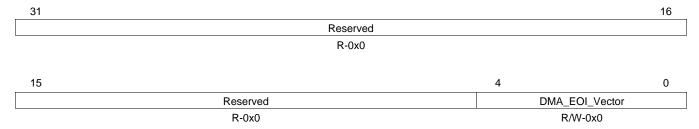

| 5.60 | CPDMA_INT Input Vector Register (Read Only) (CPDMA_IN_VECTOR)                                     |            |

| 5.61 | CPDMA_INT End Of Interrupt Vector Register (CPDMA_EOI_VECTOR)                                     |            |

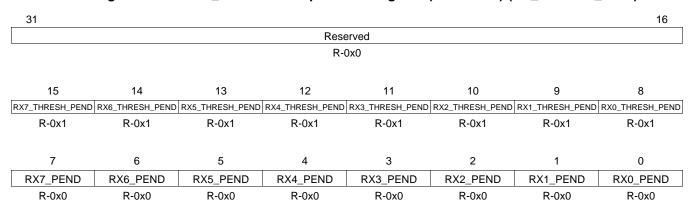

| 5.62 | CPDMA_INT_RX Interrupt_Status_Register_(Raw_Value)_(RX_INTSTAT_RAW)                               |            |

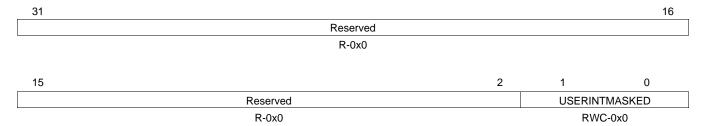

| 5.63                                                                                       | CPDMA_INT RX Interrupt Status Register (Masked Value) (RX_INTSTAT_MASKED)                                                                                                                                                                                                                                                                                                                                                             | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

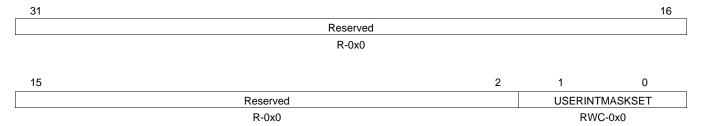

| 5.64                                                                                       | CPDMA_INT RX Interrupt Mask Set Register (RX_INTMASK_SET)                                                                                                                                                                                                                                                                                                                                                                             | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

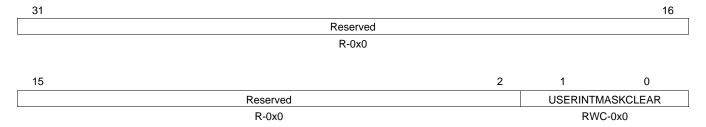

| 5.65                                                                                       | CPDMA_INT RX Interrupt Mask Clear Register (RX_INTMASK_CLEAR)                                                                                                                                                                                                                                                                                                                                                                         | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

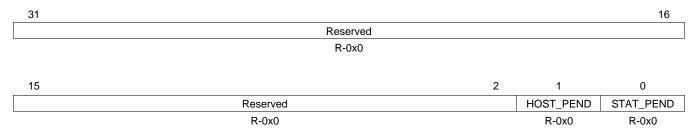

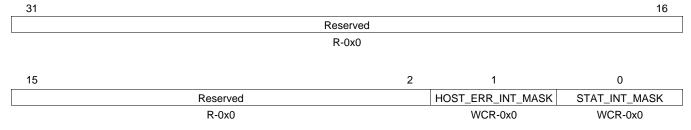

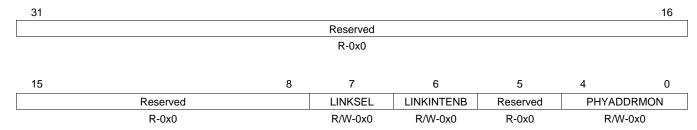

| 5.66                                                                                       | CPDMA_INT DMA Interrupt Status Register (Raw Value) (DMA_INTSTAT_RAW)                                                                                                                                                                                                                                                                                                                                                                 | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.67                                                                                       | CPDMA_INT DMA Interrupt Status Register (Masked Value) (DMA_INTSTAT_MASKED)                                                                                                                                                                                                                                                                                                                                                           | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

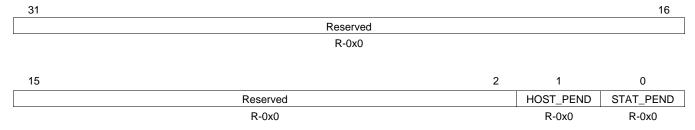

| 5.68                                                                                       | CPDMA_INT DMA Interrupt Mask Set Register (DMA_INTMASK_SET)                                                                                                                                                                                                                                                                                                                                                                           | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.69                                                                                       | CPDMA_INT DMA Interrupt Mask Clear Register (DMA_INTMASK_CLEAR)                                                                                                                                                                                                                                                                                                                                                                       | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

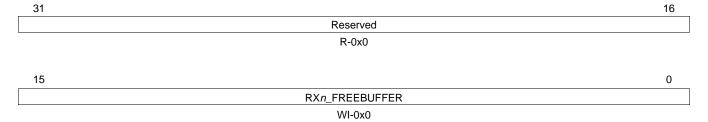

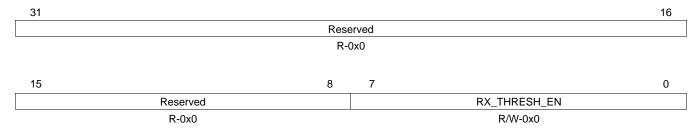

| 5.70                                                                                       | CPDMA_INT Receive Threshold Pending Register Channels 0-7 (RXn_PENDTHRESH)                                                                                                                                                                                                                                                                                                                                                            | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

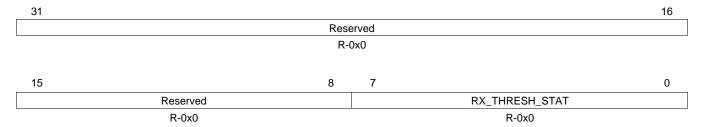

| 5.71                                                                                       | CPDMA_INT Receive Free Buffer Register Channels 0-7 (RXn_FREEBUFFER)                                                                                                                                                                                                                                                                                                                                                                  | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

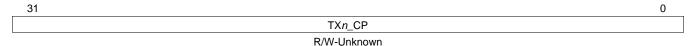

| 5.72                                                                                       | CPDMA_STATERAM TX Channels 0-7 Head Descriptor Pointer Register (TXn_HDP)                                                                                                                                                                                                                                                                                                                                                             | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

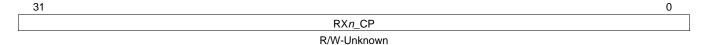

| 5.73                                                                                       | CPDMA_STATERAM RX Channels 0-7 Head Descriptor Pointer Register (RXn_HDP)                                                                                                                                                                                                                                                                                                                                                             | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.74                                                                                       | CPDMA_STATERAM TX Channels 0-7 Completion Pointer Register (TXn_CP)                                                                                                                                                                                                                                                                                                                                                                   | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.75                                                                                       | CPDMA_STATERAM RX Channels 0-7 Completion Pointer Register (RXn_CP)                                                                                                                                                                                                                                                                                                                                                                   | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.76                                                                                       | Statistics Interface Registers                                                                                                                                                                                                                                                                                                                                                                                                        | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

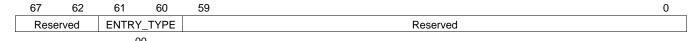

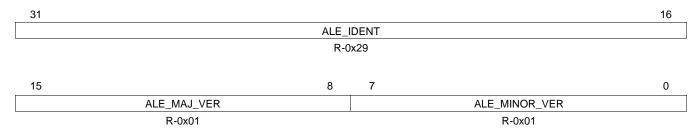

| 5.77                                                                                       | Address Lookup Engine ID/Version Register (DM648 only) (ALE_IDVER)                                                                                                                                                                                                                                                                                                                                                                    | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.78                                                                                       | Address Lookup Engine Control Register (DM648 only) (ALE_CONTROL)                                                                                                                                                                                                                                                                                                                                                                     | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.79                                                                                       | Address Lookup Engine Prescale Register (DM648 only) (ALE_PRESCALE)                                                                                                                                                                                                                                                                                                                                                                   | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.80                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

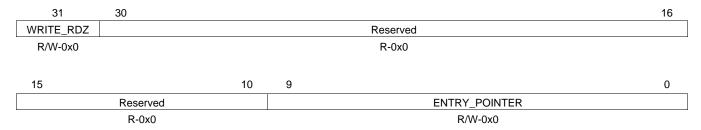

| 5.81                                                                                       | Address Lookup Engine Table Control Register (DM648 only) (ALE_TBLCTL)                                                                                                                                                                                                                                                                                                                                                                | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

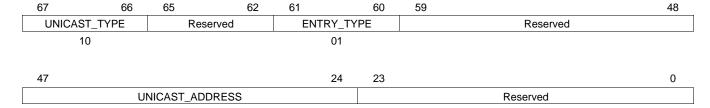

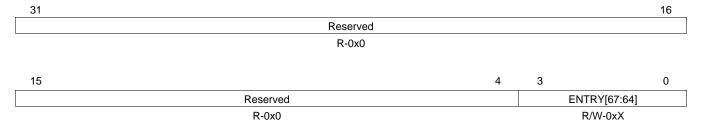

| 5.82                                                                                       | Address Lookup Engine Table Word 2 Register (DM648 only) (ALE_TBLW2)                                                                                                                                                                                                                                                                                                                                                                  | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.83                                                                                       | Address Lookup Engine Table Word 1 Register (DM648 only) (ALE_TBLW1)                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

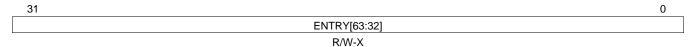

| 5.84                                                                                       | Address Lookup Engine Table Word 0 Register (DM648 only) (ALE_TBLW0)                                                                                                                                                                                                                                                                                                                                                                  | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

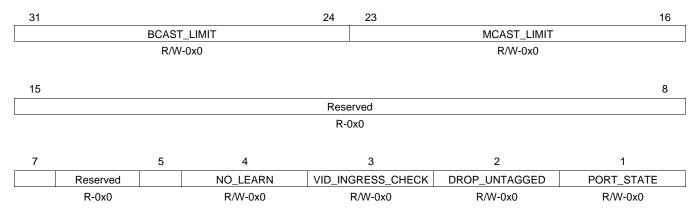

| 5.85                                                                                       | Address Lookup Engine Port 0 Control Register (DM648 only) (ALE_PORTCTL0)                                                                                                                                                                                                                                                                                                                                                             | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

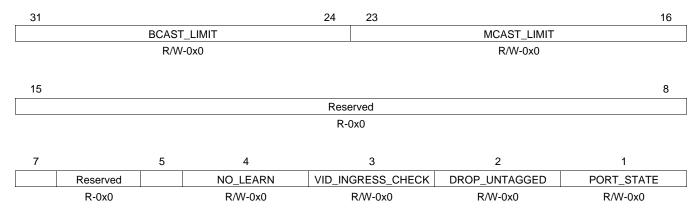

| 5.86                                                                                       | Address Lookup Engine Port 1 Control Register (DM648 only) (ALE_PORTCTL1)                                                                                                                                                                                                                                                                                                                                                             | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

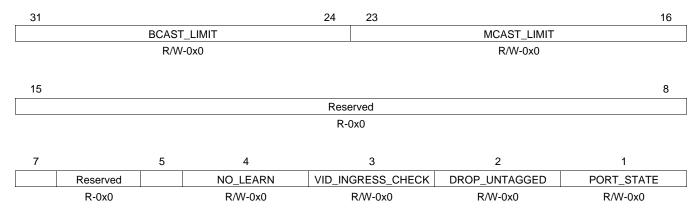

| 5.87                                                                                       | Address Lookup Engine Port 2 Control Register (DM648 only) (ALE_PORTCTL2)                                                                                                                                                                                                                                                                                                                                                             | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |