# TMS320C672x DSP Dual Data Movement Accelerator (dMAX)

# Reference Guide

Literature Number: SPRU795D November 2005-Revised October 2007

## **Contents**

| Pref | face  |           |                                                                | 11 |

|------|-------|-----------|----------------------------------------------------------------|----|

| 1    | Intro | duction   | n/Feature Overview                                             | 13 |

|      | 1.1   | Overvi    | ew                                                             | 14 |

|      | 1.2   | dMAX      | Terminology                                                    | 18 |

|      | 1.3   | Initiatir | ng dMAX Transfers                                              | 20 |

|      | 1.4   | FIFO I    | mplementation                                                  | 20 |

|      |       | 1.4.1     | FIFO Watermarks                                                | 22 |

|      |       | 1.4.2     | FIFO Error Field                                               | 22 |

|      | 1.5   | Types     | of dMAX Transfers                                              | 23 |

|      |       | 1.5.1     | One-Dimensional Transfers                                      | 24 |

|      |       | 1.5.2     | Two-Dimensional Transfers                                      | 25 |

|      |       | 1.5.3     | Three-Dimensional Transfers                                    | 27 |

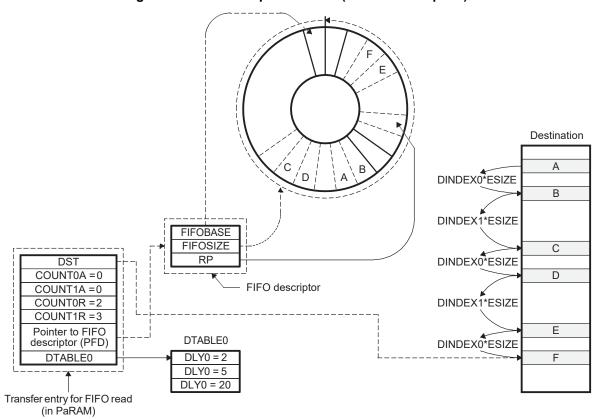

|      |       | 1.5.4     | FIFO Transfers                                                 | 29 |

|      |       | 1.5.5     | One-Dimensional Burst (1DN) Transfers                          | 42 |

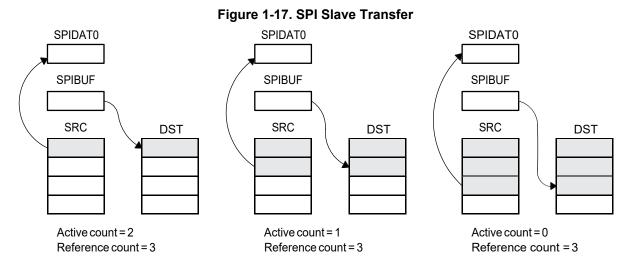

|      |       | 1.5.6     | SPI Slave Transfer                                             | 43 |

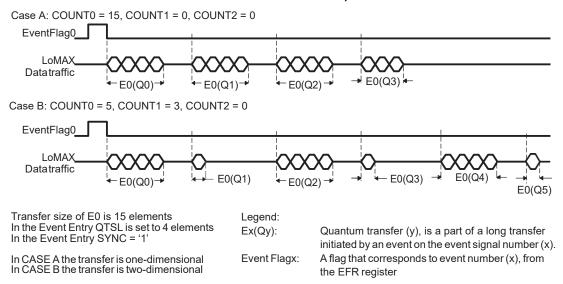

|      | 1.6   | Quantı    | um Transfers                                                   | 44 |

|      | 1.7   | Eleme     | nt Size and Alignment                                          | 45 |

|      | 1.8   | Source    | e/Destination Address Updates                                  | 45 |

|      | 1.9   | Reload    | ding dMAX Transfers                                            | 45 |

|      | 1.10  | dMAX      | Interrupt Generation                                           | 45 |

|      |       | 1.10.1    | Using an Event to Initiate a CPU Interrupt                     | 46 |

|      |       | 1.10.2    | End of Transfer Notification Interrupt to the CPU              | 46 |

|      |       | 1.10.3    | FIFO Status Notification Interrupt                             | 47 |

|      |       | 1.10.4    | dMAX NMI Interrupt                                             | 47 |

|      | 1.11  | Emulat    | tion Operation                                                 | 47 |

|      | 1.12  | Event l   | Encoder                                                        | 48 |

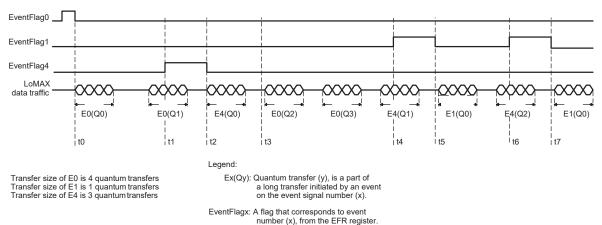

|      |       | 1.12.1    | Synchronization of dMAX Events                                 | 48 |

|      |       | 1.12.2    | Event Priority Processing Within the Same Event Priority Group | 50 |

| 2    | Regi  | ster and  | d Memory Description                                           | 53 |

|      | 2.1   | Param     | neter RAM (PaRAM)                                              | 54 |

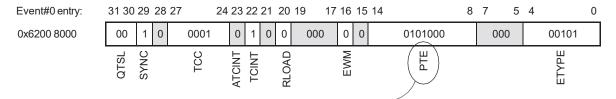

|      |       | 2.1.1     | Event Entry Table                                              | 56 |

|      |       | 2.1.2     | Transfer Entry Table                                           | 63 |

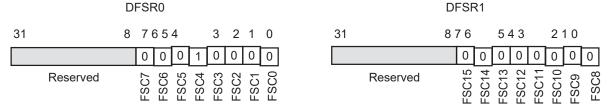

|      | 2.2   | FIFO D    | Descriptor                                                     | 71 |

|      | 2.3   |           | Control Registers                                              | 73 |

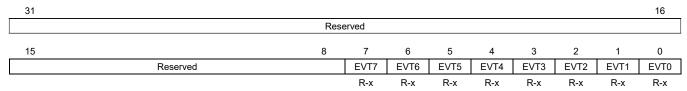

|      |       | 2.3.1     | dMAX Event Register 0 (DER0)                                   | 74 |

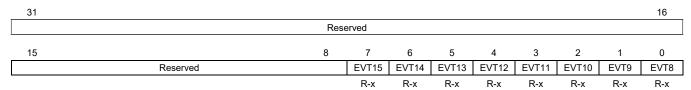

|      |       | 2.3.2     | dMAX Event Register 1 (DER1)                                   | 74 |

|      |       | 2.3.3     | dMAX Event Register 2 (DER2)                                   | 75 |

|      |       | 2.3.4     | dMAX Event Flag Register (DEFR)                                | 76 |

|      |       | 2.3.5     | dMAX Event Enable Register (DEER)                              | 77 |

|      |       | 2.3.6     | dMAX Event Disable Register (DEDR)                             |    |

|      |       | 2.3.7     | dMAX Event Polarity (DEPR)                                     |    |

|      |       | 2.3.8     | dMAX Event High Priority (DEHPR)                               |    |

|      |       | 2.3.9     | dMAX Event Low Priority (DELPR)                                | 80 |

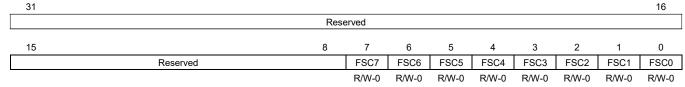

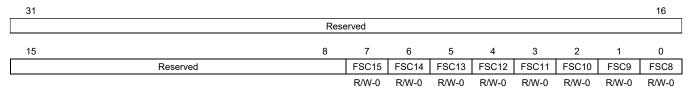

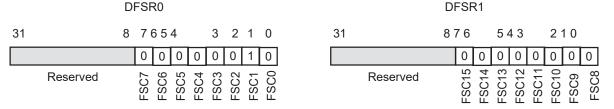

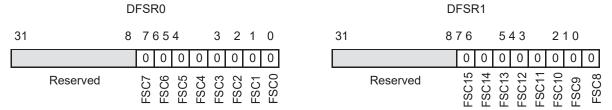

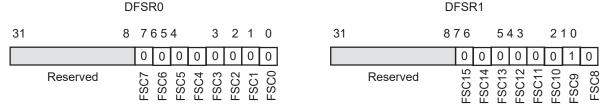

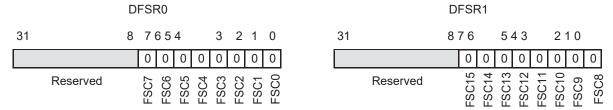

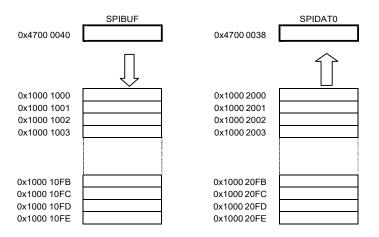

|      |       | 2.3.10    | dMAX FIFO Status Register 0 (DFSR0)                            | 80 |

|      |       |           |                                                                |    |

|   |      | 2.3.11         | dMAX FIFO Status Register 1 (DFSR1)                        | 81  |

|---|------|----------------|------------------------------------------------------------|-----|

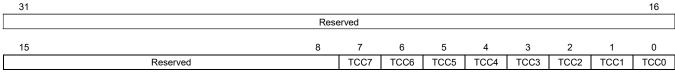

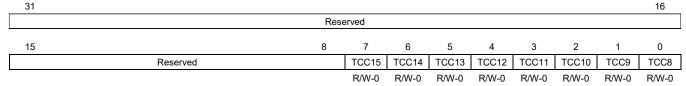

|   |      | 2.3.12         | dMAX Transfer Completion Register 0 (DTCR0)                | 82  |

|   |      | 2.3.13         | dMAX Transfer Completion Register 1 (DTCR1)                | 82  |

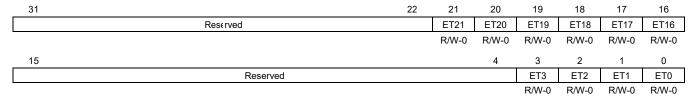

|   |      | 2.3.14         | dMAX Event Trigger Register (DETR)                         | 83  |

|   |      | 2.3.15         | dMAX Event Status Register (DESR)                          | 85  |

| 3 | Tran | sfer Ex        | camples                                                    | 87  |

|   | 3.1  |                | fer Synchronization                                        |     |

|   | 3.2  | Gener          | ral Purpose Transfer Examples                              | 88  |

|   |      | 3.2.1          | Steps Required to Set Up a General Purpose Transfer        |     |

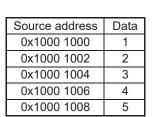

|   |      | 3.2.2          | EXAMPLE: 1D Block Move Transfer                            | 89  |

|   |      | 3.2.3          | EXAMPLE: Element- Synchronized 1D Transfer                 | 90  |

|   |      | 3.2.4          | EXAMPLE: Sub-frame Extraction                              | 93  |

|   |      | 3.2.5          | EXAMPLE: Three Dimensional (3D) Data De-Interleaving       | 95  |

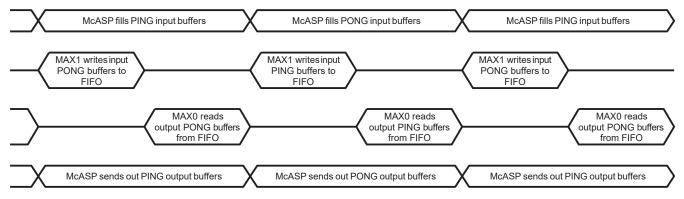

|   |      | 3.2.6          | EXAMPLE: Ping-Pong Data Buffering Example                  | 96  |

|   | 3.3  | FIFO           | Transfer Examples                                          | 102 |

|   |      | 3.3.1          | Steps Required to Set Up a FIFO Transfer                   | 102 |

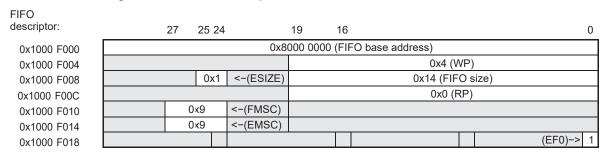

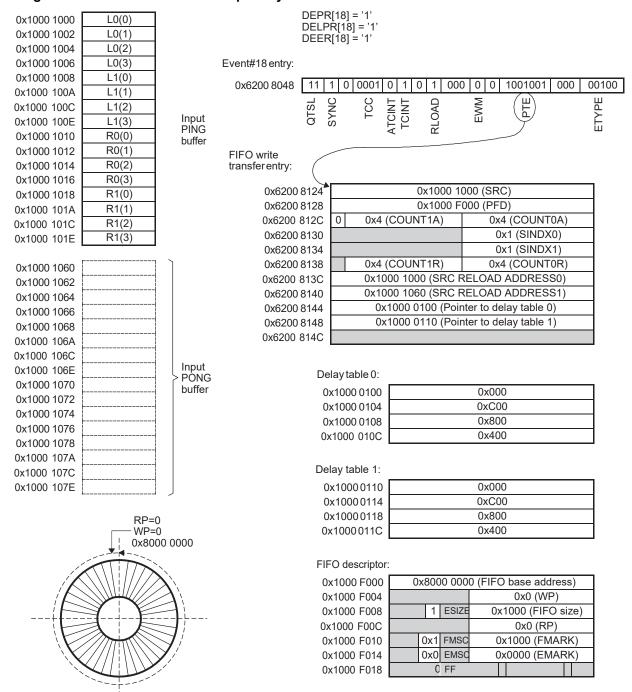

|   |      | 3.3.2          | EXAMPLE: 1D FIFO Write Transfer                            |     |

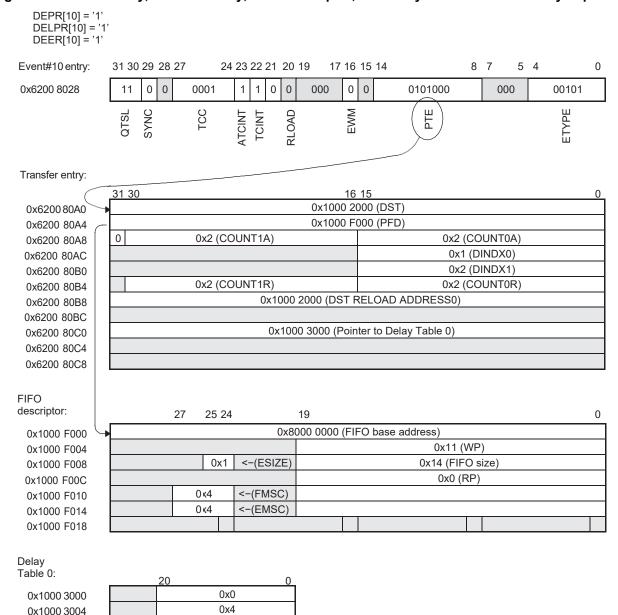

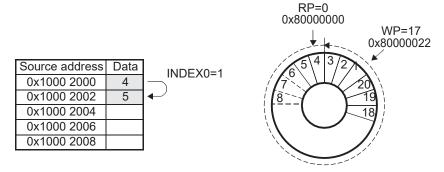

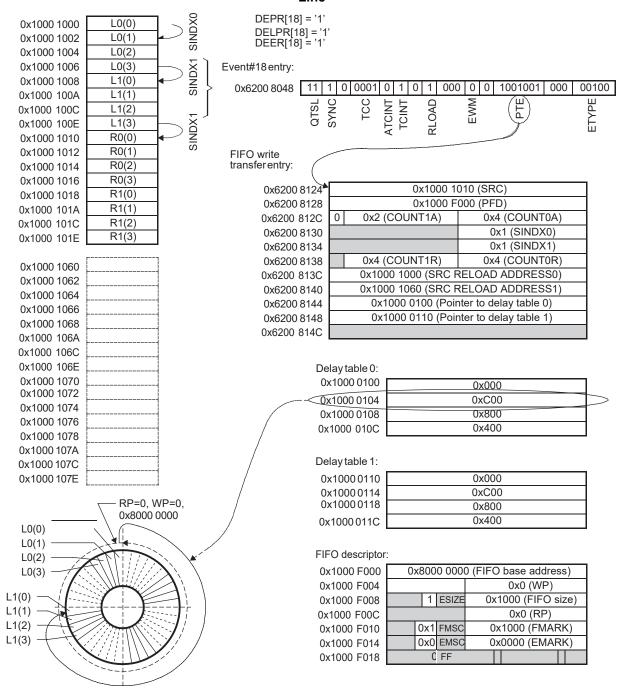

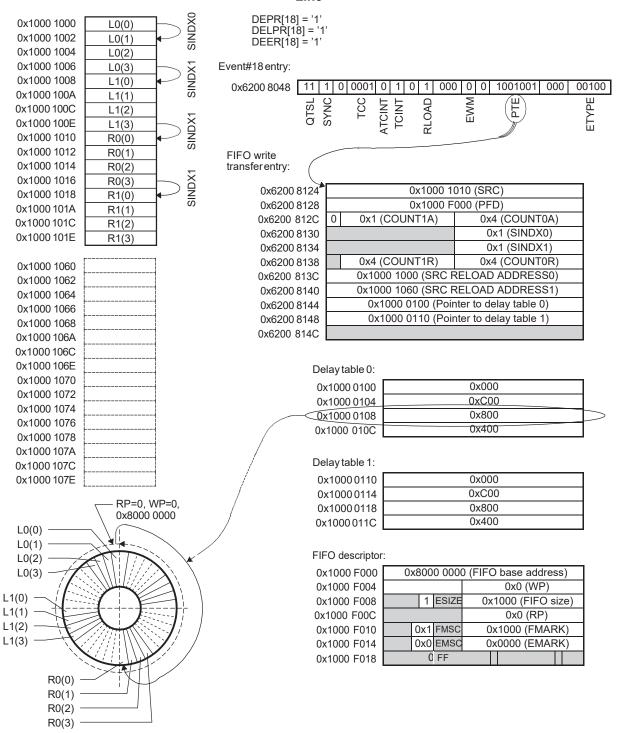

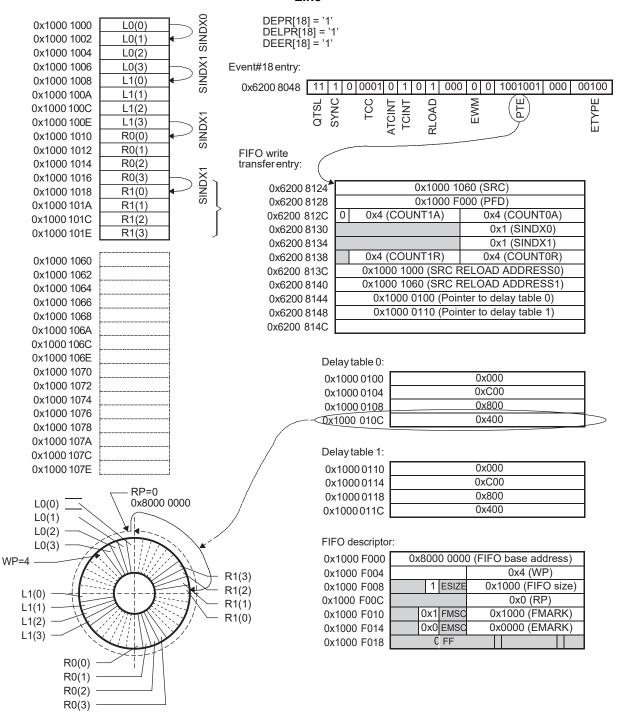

|   |      | 3.3.3          | EXAMPLE: 2D FIFO Write Transfer with Reload                |     |

|   |      | 3.3.4          | EXAMPLE: 1D FIFO Read Transfer                             |     |

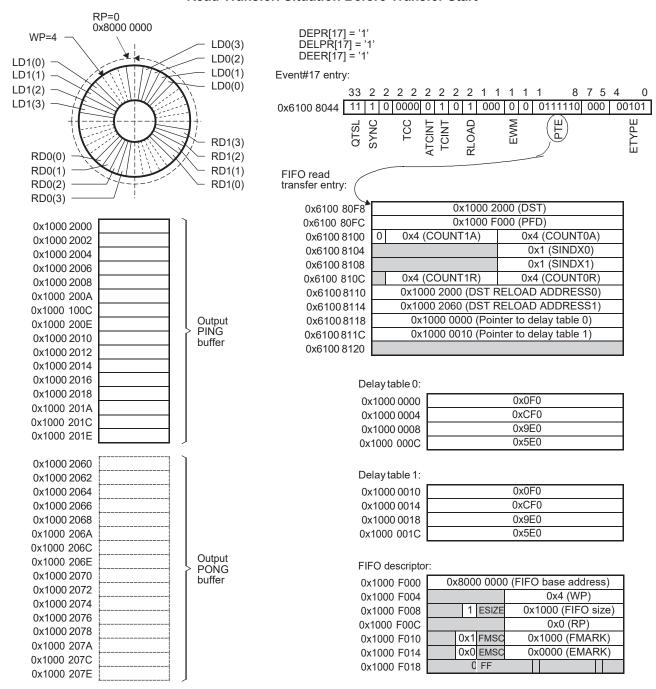

|   |      | 3.3.5          | EXAMPLE: 2D FIFO Read Transfer with Reload                 |     |

|   |      | 3.3.6          | EXAMPLE: FIFO Overflow Error                               |     |

|   |      | 3.3.7          | EXAMPLE: FIFO Underflow Error                              |     |

|   |      | 3.3.8          | EXAMPLE: FIFO Delay-Tap Error                              |     |

|   | 3.4  | One-D          | Dimensional Burst Transfers                                |     |

|   |      | 3.4.1          | Steps Required to Set Up a One-Dimensional Burst Transfer  |     |

|   |      | 3.4.2          | Example: One-Dimensional Burst Transfer                    |     |

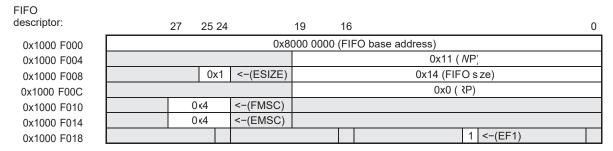

|   | 3.5  |                | lave Transfer                                              |     |

|   |      | 3.5.1          | Steps Required to Set Up a SPI Slave Transfer              |     |

|   |      | 3.5.2          | Example: SPI Slave Transfer                                |     |

|   | 3.6  |                | ples of Servicing Peripherals                              |     |

|   |      | 3.6.1          | EXAMPLE: Servicing McASP Peripheral                        |     |

|   |      | 3.6.2          | EXAMPLE: Servicing I2C Peripherals (FIFO FMARK Watermark)  |     |

|   | 0.7  | 3.6.3          | (                                                          |     |

|   | 3.7  |                | ple of Using dMAX Events to Generate a CPU Interrupt       |     |

|   | 2.0  | 3.7.1          | Using External Signals to Trigger a CPU Interrupt          |     |

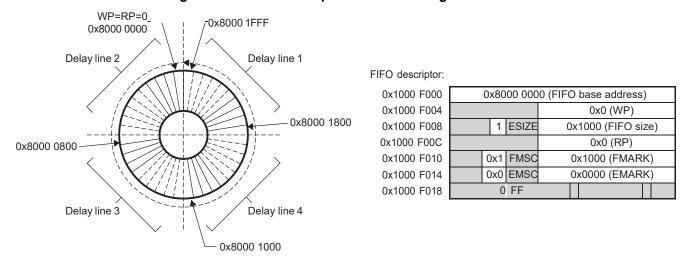

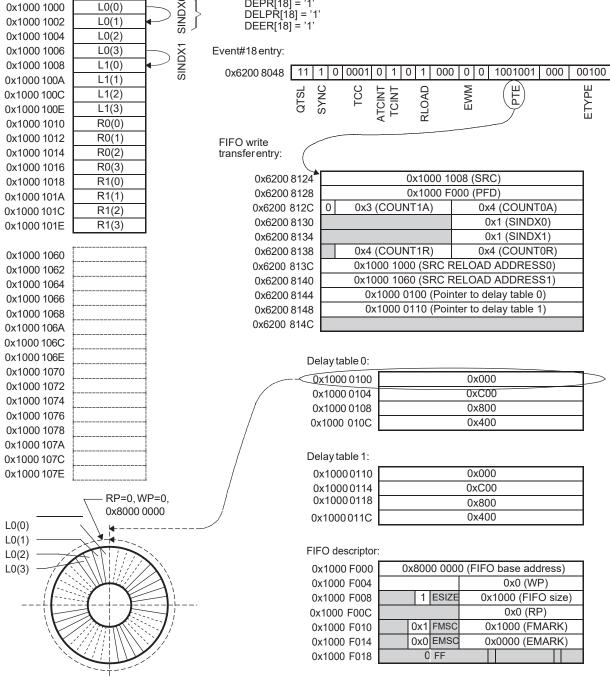

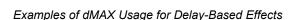

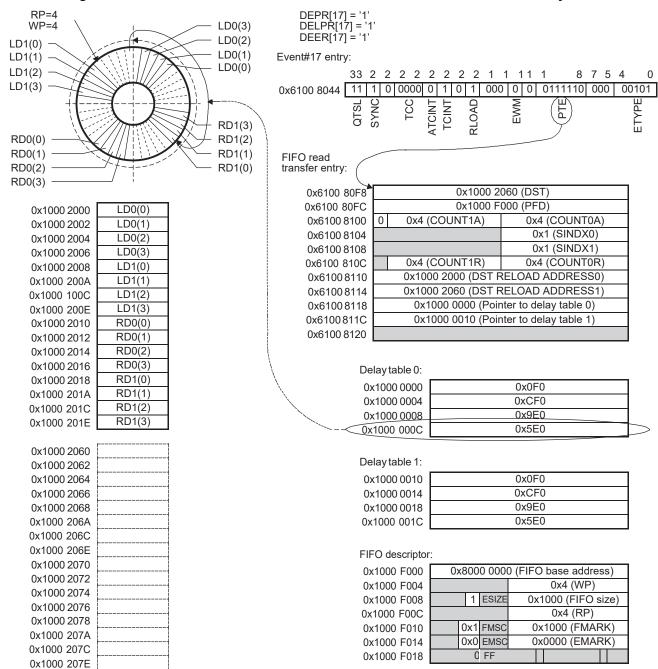

|   | 3.8  |                | ples of dMAX Usage for Delay-Based Effects                 |     |

|   |      | 3.8.1<br>3.8.2 | Writing a Block of Fresh Samples to Each FIFO Quadrant     |     |

|   |      |                | Reading a Block of Delayed Samples from Each FIFO Quadrant |     |

| 4 |      |                | troller Performance                                        |     |

|   | 4.1  |                | riew                                                       |     |

|   | 4.2  |                | elines for Getting the Best dMAX Performance               |     |

|   |      |                | 1 General Purpose Transfer: Best Performance Tips          |     |

|   |      |                | 2 FIFO Transfer: Best Performance Tips                     |     |

|   | 4.0  |                | .3 One-Dimensional Burst Transfer: Best Performance Tips   |     |

|   | 4.3  |                | ral Performance Transfer Performance                       |     |

|   | 4.4  |                | fer Duration and Latency                                   |     |

|   | 4.5  |                | ral Purpose Transfer Latency                               |     |

|   | 4.6  | ı rans         | fers within the Internal Memory                            | 1/0 |

Submit Documentation Feedback

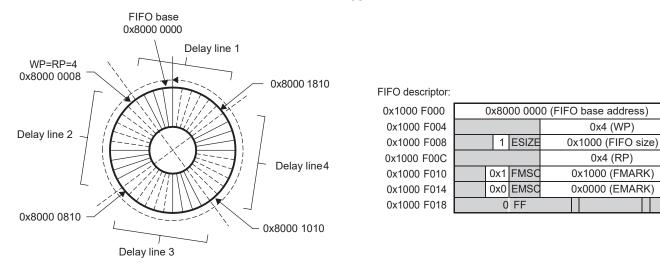

|   |       | 4.6.1 Copy of Sequential Data (SINDX0=1 and DINDX0=1)                               | 170 |

|---|-------|-------------------------------------------------------------------------------------|-----|

|   |       | 4.6.2 Sorting of Sequential Data (SINDX0≠1 and DINDX0=1, or SINDX0=1 and DINDX0≠1)  | 172 |

|   |       | 4.6.3 Sorting of Non-Sequential Data (SINDX0≠1 and DINDX0≠1)                        | 174 |

|   | 4.7   | Transfers Between the Internal Memory and McASP                                     | 176 |

|   |       | 4.7.1 Copy of Sequential Data (SINDX0=1 and DINDX0=1)                               | 177 |

|   |       | 4.7.2 Sorting of Sequential Data (SINDX0=1 and DINDX0≠1 or SINDX0≠1 and DINDX0=1)   | 178 |

|   | 4.8   | Transfers Between Internal Memory and EMIF SDRAM                                    | 179 |

|   |       | 4.8.1 Copy of Sequential Data (SINDX0=1 and DINDX0=1)                               | 179 |

|   |       | 4.8.2 Sorting of Sequential Data (SINDX0≠1 and DINDX0=1 or SINDX0 = 1 and DINDX0≠1) | 184 |

|   | 4.9   | One-Dimensional Burst Transfer Performance                                          | 188 |

|   | 4.10  | SPI Slave Transfer Performance                                                      | 195 |

|   | 4.11  | FIFO Transfer Performance                                                           | 196 |

|   | 4.12  | Transfer Duration and Latency                                                       | 197 |

|   | 4.13  | FIFO Read                                                                           | 198 |

|   |       | 4.13.1 FIFO Read Transfers Within Internal Memory                                   | 198 |

|   |       | 4.13.2 FIFO Read Transfers Between Internal Memory and EMIF SDRAM                   | 199 |

|   | 4.14  | FIFO Write Transfer                                                                 | 200 |

|   |       | 4.14.1 FIFO Write Transfers Within the Internal Memory                              | 200 |

|   |       | 4.14.2 FIFO Write Transfers Between Internal Memory and EMIF SDRAM                  | 201 |

| 1 | Revis | sion History                                                                        | 203 |

## List of Figures

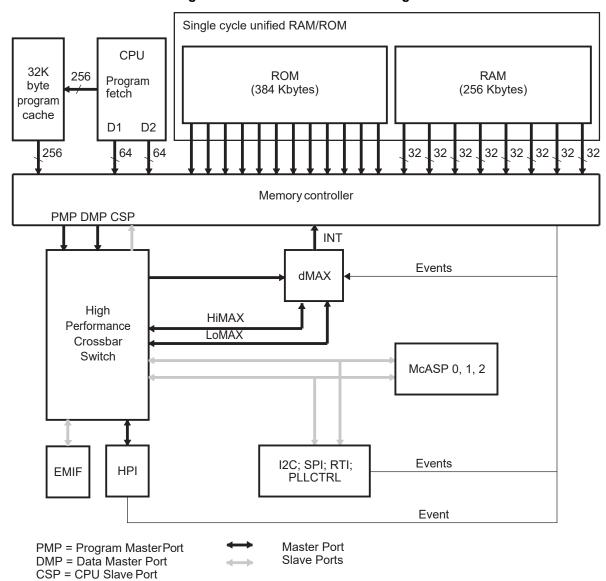

| 1-1  | TMS320C672x Block Diagram                                                                                                   | 14 |

|------|-----------------------------------------------------------------------------------------------------------------------------|----|

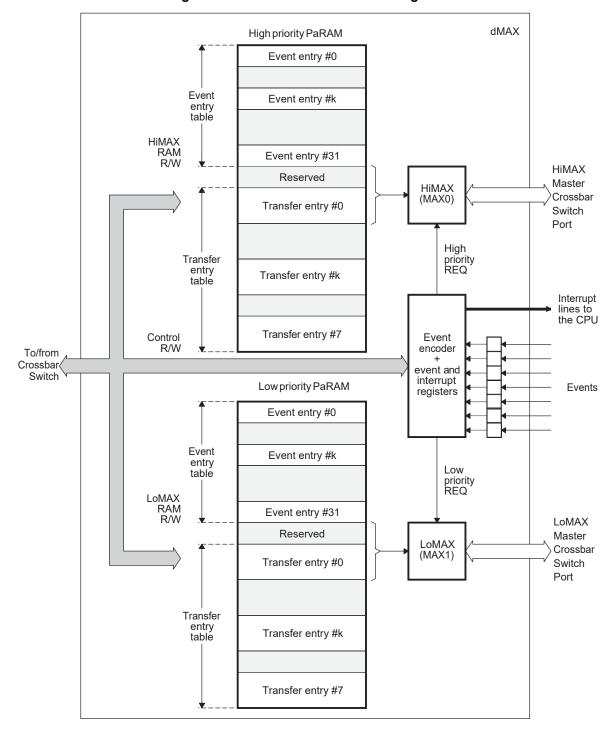

| 1-2  | dMAX Controller Block Diagram                                                                                               | 16 |

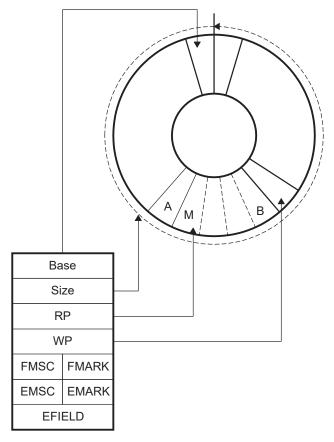

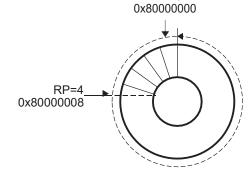

| 1-3  | Parameters Defining a FIFO: Read Pointer, Write Pointer, FIFO Base Address, FIFO Size, EMARK, FMARK, FMSC, EMSC, and EFIELD | 21 |

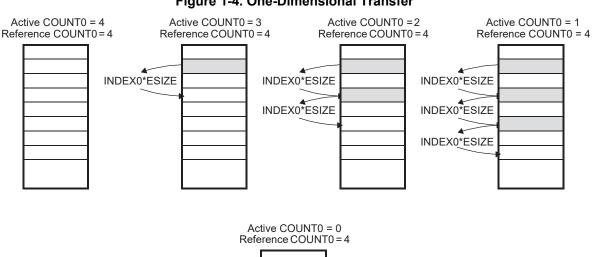

| 1-4  | One-Dimensional Transfer                                                                                                    |    |

| 1-5  | A Two-Dimensional Transfer                                                                                                  | 26 |

| 1-6  | A Three-Dimensional Transfer                                                                                                |    |

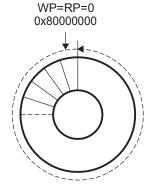

| 1-7  | Three-Frame FIFO Write Transfer (Prior to Transfer Start)                                                                   |    |

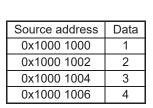

| 1-8  | Three-Frame FIFO Write Transfer (After Transfer of the First Frame)                                                         |    |

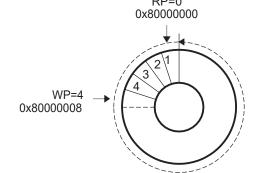

| 1-9  | Three-Frame FIFO Write Transfer (After Transfer of the Second Frame)                                                        |    |

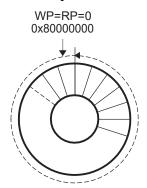

| 1-10 | Three-Frame FIFO Write Transfer (Immediately After Transfer of the Third Frame)                                             |    |

| 1-11 | Three-Frame FIFO Write Transfer (Transfer Complete)                                                                         |    |

| 1-12 | Three-Frame FIFO Read (Prior to Transfer Start)                                                                             |    |

| 1-13 | Three-Frame FIFO Read (After Reading the First Tap)                                                                         |    |

| 1-14 | Three-Tap FIFO Read (After Reading the Second Tap)                                                                          |    |

| 1-15 | Three-Tap FIFO Read (Immediately After Reading the Third Tap)                                                               |    |

| 1-16 | Three-Tap FIFO Read (Transfer Complete)                                                                                     |    |

| 1-17 | SPI Slave Transfer                                                                                                          |    |

| 1-18 | An Example of a Long Transfer (Transfer Size is Equal to 15 Elements and Quantum Transfer Limit Size is Set to 4)           |    |

| 1-19 | A Data Traffic Example: All Events Arrive from Three Event Signals Sorted to the Lower Priority Event Group                 |    |

| 1-20 | A Data Traffic Example: A New Event Arrives During a Long Transfer                                                          |    |

| 2-1  | PaRAM Memory Map                                                                                                            |    |

| 2-2  | PaRAM Memory Organization Block Diagram                                                                                     |    |

| 2-3  | Event Entry for General Purpose Data Transfer                                                                               |    |

| 2-4  | Event Entry for FIFO Transfer                                                                                               |    |

| 2-5  | Event Entry for Interrupt from dMAX Controller to the CPU                                                                   |    |

| 2-6  | Event Entry for One-Dimensional Burst Transfer                                                                              |    |

| 2-7  | Event Entry for SPI Slave Transfers                                                                                         |    |

| 2-8  | Transfer Entry for General Purpose Data Transfer for CC=01 or CC=11                                                         |    |

| 2-9  | Transfer Entry for General Purpose Data Transfer for CC=10                                                                  |    |

| 2-10 | Transfer Entry for General Purpose Data Transfer for CC=00                                                                  |    |

| 2-11 | Transfer Entry for FIFO Write                                                                                               |    |

| 2-12 | Transfer Entry for FIFO Read                                                                                                |    |

| 2-13 | Transfer Entry for One-Dimensional Burst Transfer                                                                           |    |

| 2-14 | Transfer Entry for SPI Slave Transfer                                                                                       |    |

| 2-15 | FIFO Descriptor                                                                                                             |    |

| 2-16 | dMAX Event Register 0 (DER0)                                                                                                |    |

| 2-17 | dMAX Event Register 1 (DER1)                                                                                                |    |

| 2-18 | dMAX Event Register 2 (DER2)                                                                                                |    |

| 2-19 | dMAX Event Flag Register (DEFR)                                                                                             |    |

| 2-20 | dMAX Event Enable Register (DEER)                                                                                           |    |

| 2-21 | dMAX Event Disable Register (DEDR)                                                                                          |    |

| 2-22 | dMAX Event Polarity (DEPR)                                                                                                  |    |

| 2-23 | dMAX Event High Priority (DEHPR)                                                                                            |    |

| 2-24 | dMAX Event Low Priority (DELPR)                                                                                             |    |

| 2-25 | dMAX FIFO Status Register 0 (DFSR0)                                                                                         |    |

| 2-26 | dMAX FIFO Status Register 1 (DFSR1)                                                                                         |    |

| 2-27 | dMAX Transfer Completion Register 0 (DTCR0)                                                                                 |    |

| 2-28 | dMAX Transfer Completion Register 1 (DTCR1)                                                                                 |    |

| 2-29 | dMAX Event Trigger Register (DETR)                                                                                          |    |

|      |                                                                                                                             | 55 |

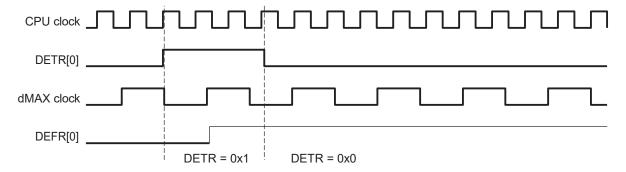

| 2-30         | CPU Triggers Event by Writing to the DETR (when DEPR[0]=1) Timing Diagram                   | 84              |

|--------------|---------------------------------------------------------------------------------------------|-----------------|

| 2-31         | dMAX Event Status (DES) Register                                                            | 85              |

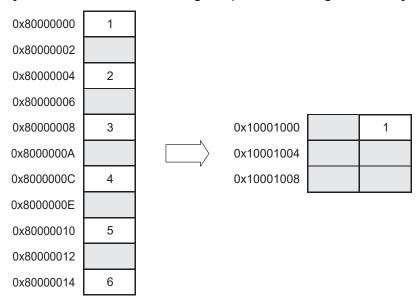

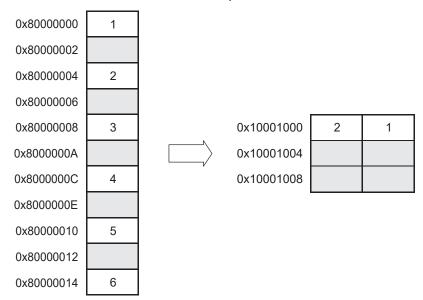

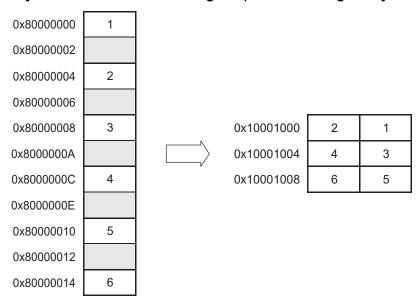

| 3-1          | Block Move Diagram                                                                          | 89              |

| 3-2          | Event Entry and Transfer Entry for 1D Block Transfer                                        | 90              |

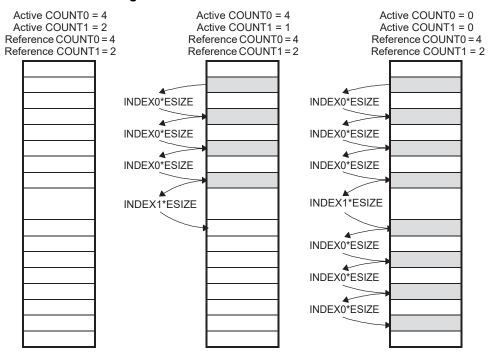

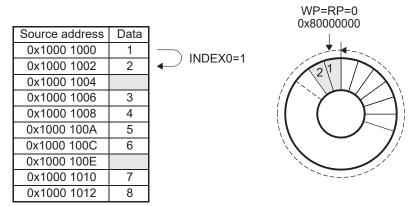

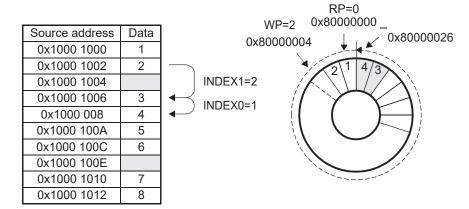

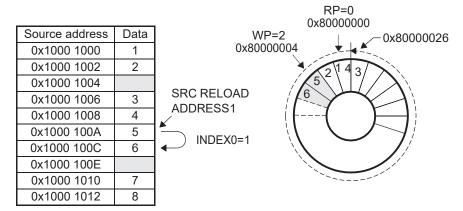

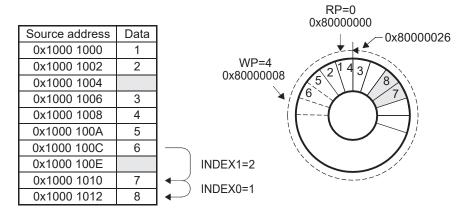

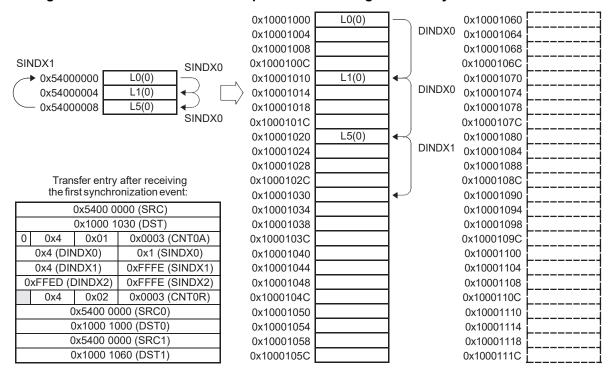

| 3-3          | Element-Synchronized 1D Transfer Diagram (After Receiving the First Synchronization Event)  | 91              |

| 3-4          | Element-Synchronized 1D Transfer Diagram (After Receiving the Second Synchronization Event) | 91              |

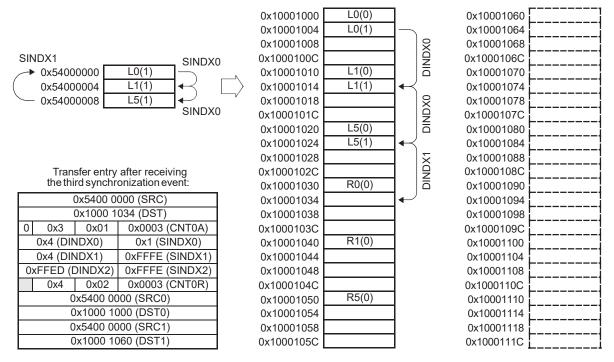

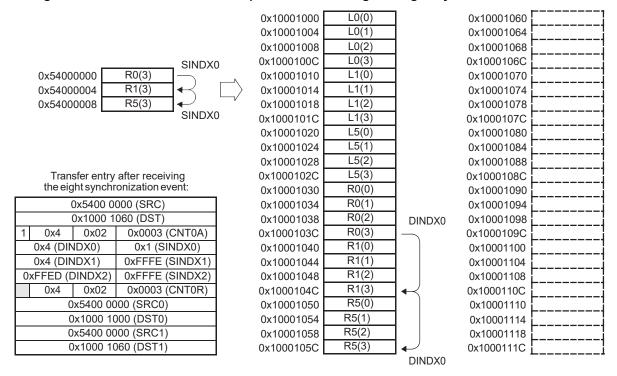

| 3-5          | Element-Synchronized 1D Transfer Diagram (After Receiving Six Synchronization Events)       | <mark>92</mark> |

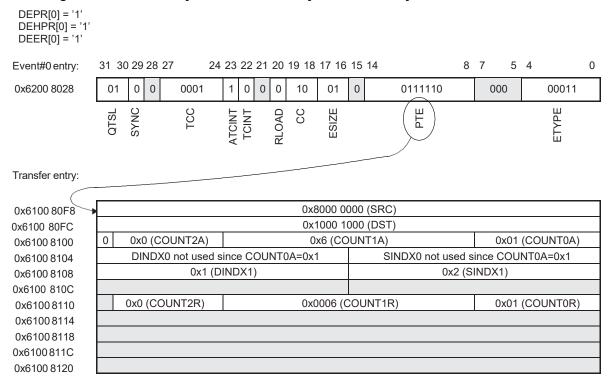

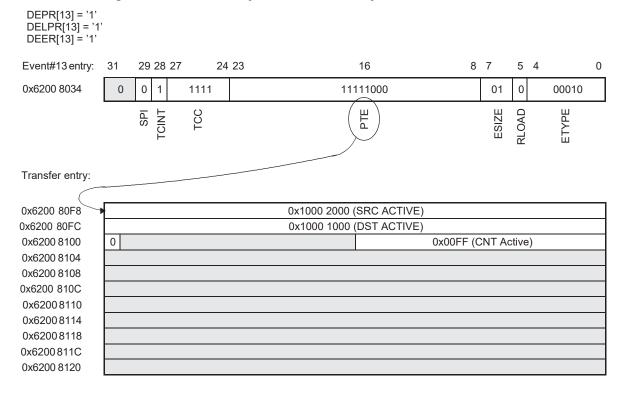

| 3-6          | Event Entry and Transfer Entry for Element-Synchronized 1D Transfer                         |                 |

| 3-7          | Sub-Frame Extraction                                                                        |                 |

| 3-8          | Event Entry and Transfer Entry for Sub-Frame Extraction Transfer                            |                 |

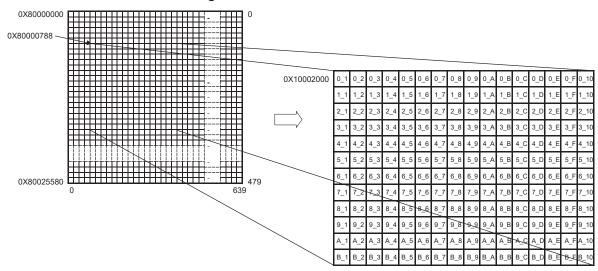

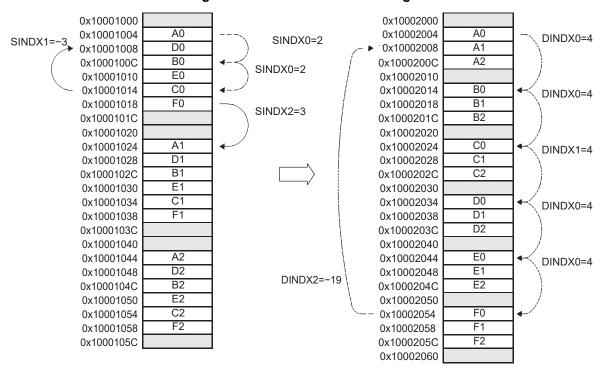

| 3-9          | 3D Data De-Interleaving                                                                     |                 |

| 3-10         | Event Entry and Transfer Entry for 3D Data De-Interleaving                                  |                 |

| 3-11         | Event Entry and Transfer Entry for Ping-Pong Data Buffering                                 |                 |

| 3-12         | Ping-Pong Data Buffering After Receiving the First Synchronization Event                    |                 |

| 3-13         | Ping-Pong Data Buffering After Receiving the Second Synchronization Event                   |                 |

| 3-14         | Ping-Pong Data Buffering After Receiving the Fourth Synchronization Event                   |                 |

| 3-15         | Ping-Pong Data Buffering After Receiving the Fifth Synchronization Event                    |                 |

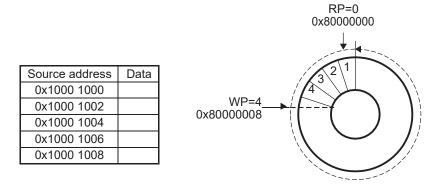

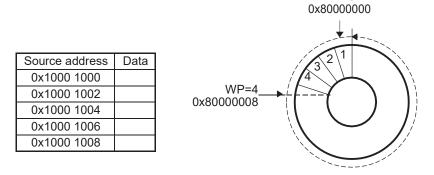

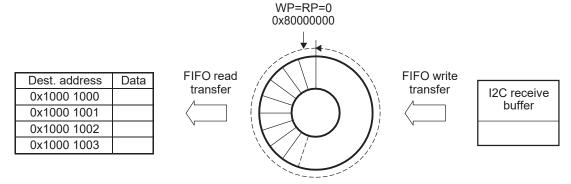

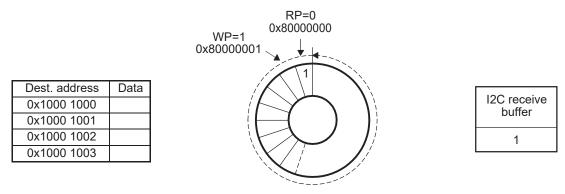

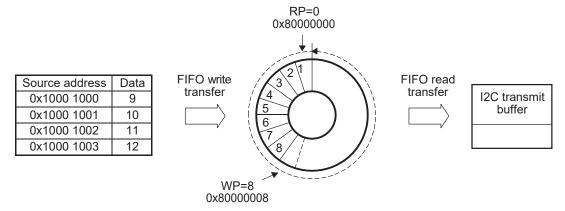

| 3-16         | 1D FIFO Write Diagram (Before Transfer)                                                     |                 |

| 3-17         | 1D FIFO Write Diagram (After Transfer)                                                      |                 |

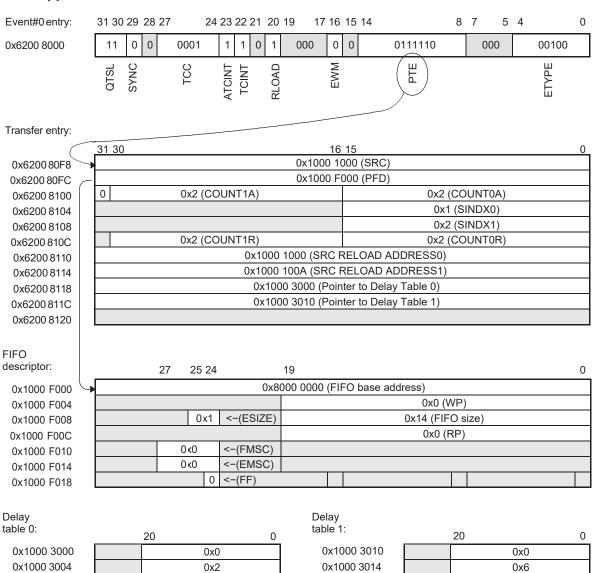

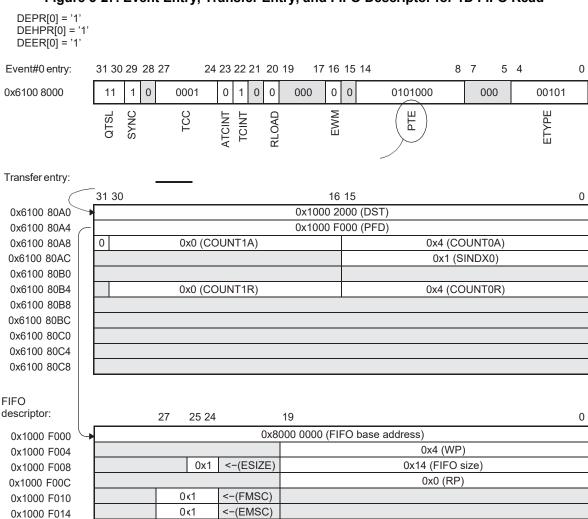

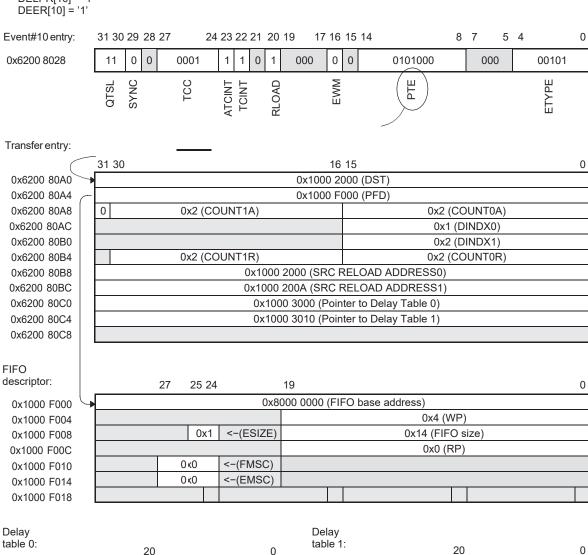

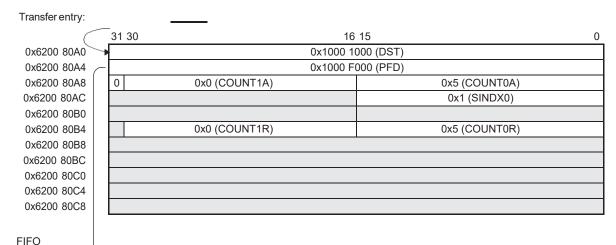

| 3-18         | Event Entry, Transfer Entry, and FIFO Descriptor for 1D FIFO Write                          |                 |

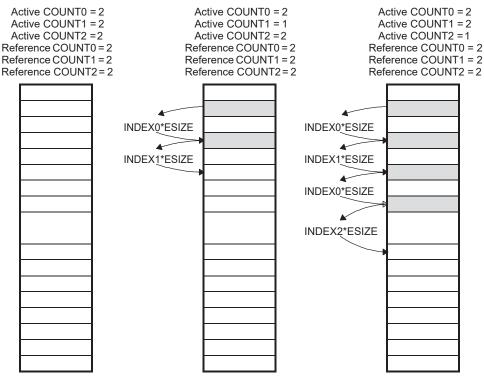

| 3-19         | 2D FIFO Write Transfer Diagram (Before First Synchronization Event)                         |                 |

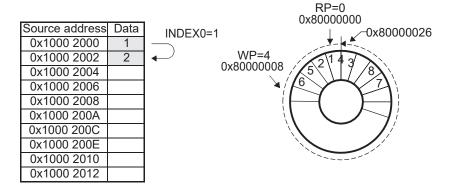

| 3-20         | 2D FIFO Write Transfer Diagram (After Receiving the First Synchronization Event)            |                 |

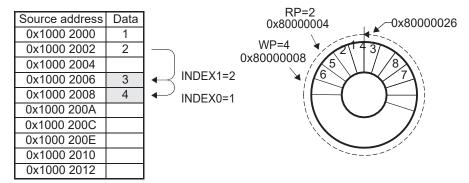

| 3-21         | 2D FIFO Write Transfer Diagram (After Receiving the Second Synchronization Event)           |                 |

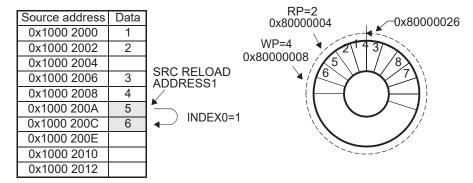

| 3-22         | 2D FIFO Write Transfer Diagram (After Receiving Three Synchronization Events)               |                 |

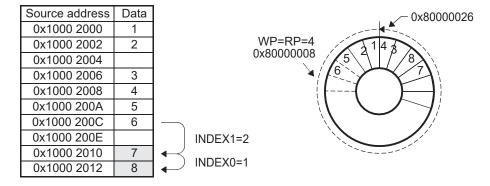

| 3-23         | 2D FIFO Write Transfer Diagram (After Receiving All Synchronization Events)                 |                 |

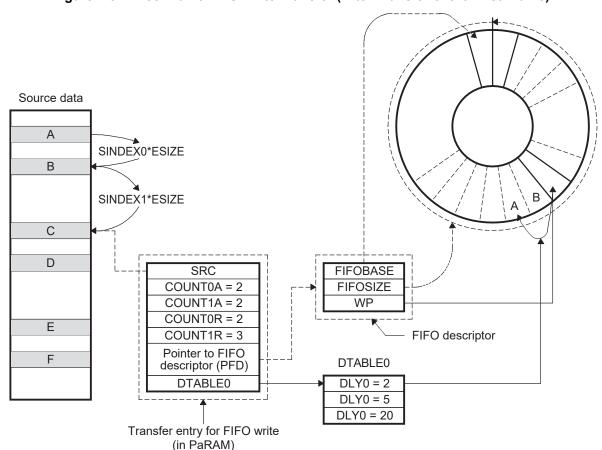

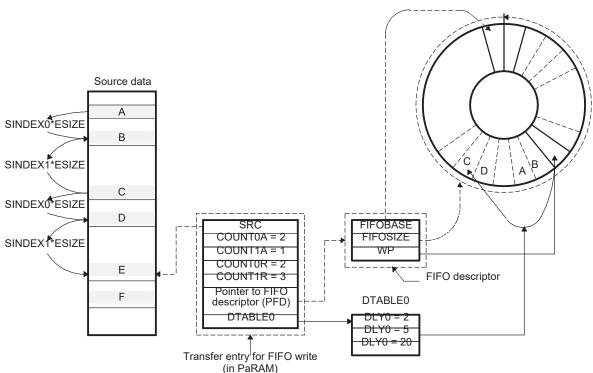

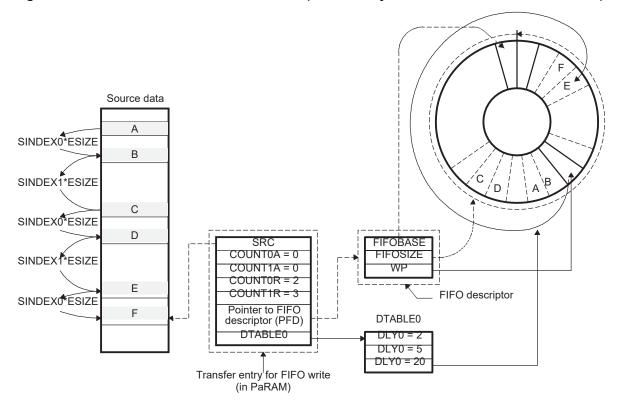

| 3-24         | Event Entry, Transfer Entry, FIFO Descriptor, and Delay Tables for 2D FIFO Write Transfer   |                 |

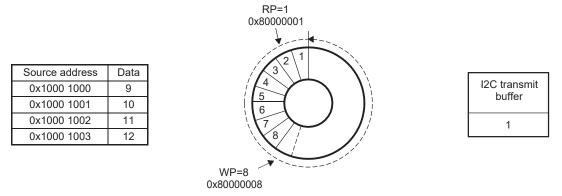

| 3-25         | 1D FIFO Read Diagram (Before Transfer)                                                      |                 |

| 3-26         | 1D FIFO Read Diagram (After Transfer)                                                       |                 |

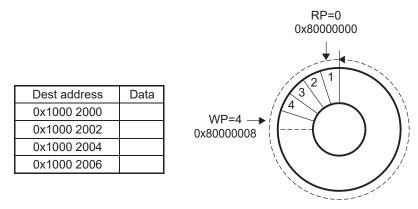

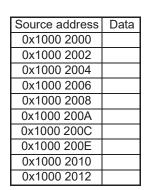

| 3-27         | Event Entry, Transfer Entry, and FIFO Descriptor for 1D FIFO Read                           |                 |

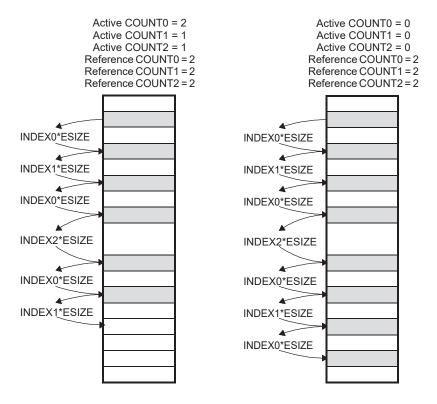

| 3-28<br>3-29 | 2D FIFO Read Transfer Diagram (After Receiving the First Synchronization Event)             |                 |

| 3-30         | 2D FIFO Read Transfer Diagram (After Receiving the First Synchronization Event)             |                 |

| 3-31         | 2D FIFO Read Transfer Diagram (After Receiving Three Synchronization Events)                |                 |

| 3-32         | 2D FIFO Read Transfer Diagram (After Receiving All Synchronization Events)                  |                 |

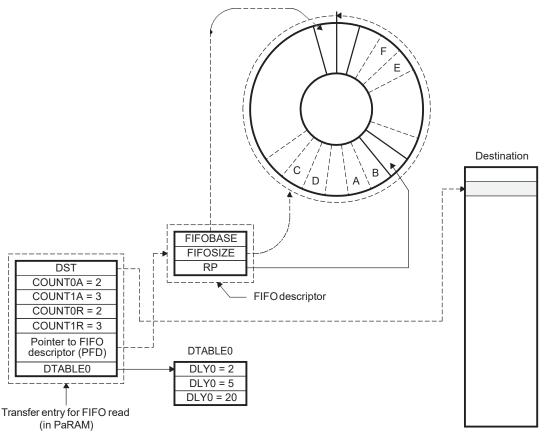

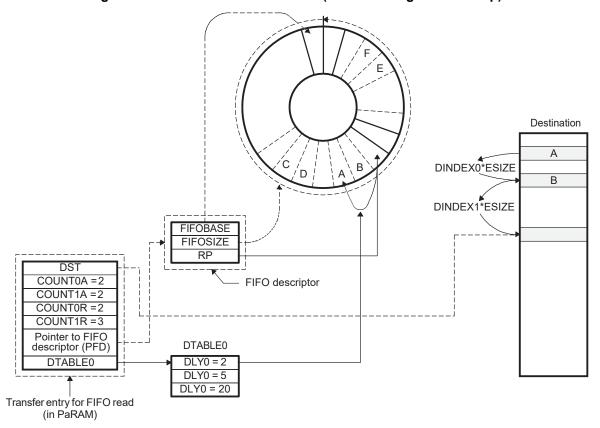

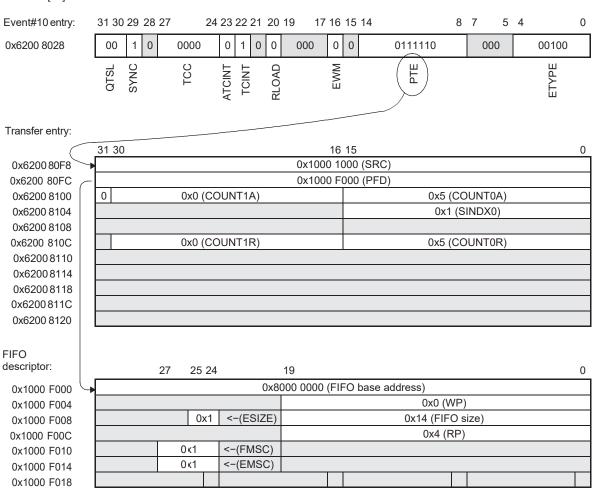

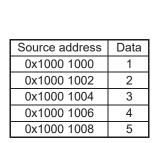

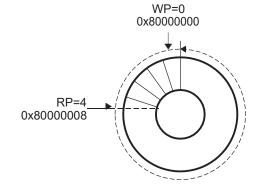

| 3-33         | Event Entry, Transfer Entry, FIFO Descriptor, and Delay Tables for 2D FIFO Read Transfer    |                 |

| 3-34         | Event Entry, Transfer Entry, and FIFO Descriptor for FIFO Overflow Error                    |                 |

| 3-35         | FIFO Overflow Error Diagram (Before Receiving Synchronization Event)                        |                 |

| 3-36         | FIFO Overflow Error Diagram (After Receiving Synchronization Event)                         |                 |

| 3-37         | dMAX FIFO Status Registers Before FIFO Overflow Error Occurs                                |                 |

| 3-38         | dMAX FIFO Status Registers After FIFO Overflow Error Occurs                                 |                 |

| 3-39         | FIFO Descriptor After FIFO Overflow Error Occurs                                            |                 |

| 3-40         | Event Entry, Transfer Entry, and FIFO Descriptor for FIFO Underflow Error                   |                 |

| 3-41         | FIFO Underflow Error Diagram (Before Receiving Synchronization Event)                       |                 |

| 3-42         | FIFO Underflow Error Diagram (After Receiving Synchronization Event)                        |                 |

| 3-43         | dMAX FIFO Status Registers Before FIFO Underflow Error Occurs                               |                 |

| 3-44         | dMAX FIFO Status Registers After FIFO Underflow Error Occurs                                |                 |

| 3-45         | FIFO Descriptor After FIFO Overflow Error Occurs                                            |                 |

| 3-46         | Event Entry, Transfer Entry, FIFO Descriptor, and Delay Tables for FIFO Delay-Tap Error     |                 |

| 3-47         | FIFO Delay-tap Error Diagram (Before First Synchronization Event)                           |                 |

| 3-48         | FIFO Delay-Tap Error Diagram (After Receiving the First Synchronization Event)              |                 |

| 3-49         | FIFO Delay-Tap Error Diagram (After Receiving the Second Synchronization Event)             |                 |

| 3-50         | dMAX FIFO Status Registers Before FIFO Delay-Tap Error Occurs                               | 125             |

| 3-51         | dMAX FIFO Status Registers After FIFO Delay-Tap Error Occurs                                | 125             |

| 3-52         | FIFO Descriptor After FIFO Delay-Tap Error Occurs                                                                                               |       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3-53         | 1DN Block Move Diagram                                                                                                                          |       |

| 3-54         | Event Entry and Transfer Entry for 1DN Transfer                                                                                                 |       |

| 3-55         | SPI Slave Transfer Diagram                                                                                                                      |       |

| 3-56         | Event Entry and Transfer Entry for SPI Slave Transfer                                                                                           |       |

| 3-57         | Event Entry and Transfer Entry for McASP Transfer                                                                                               |       |

| 3-58         | McASP Receive Example After Receiving the First Synchronization Event                                                                           | 133   |

| 3-59         | McASP Receive Example After Receiving the Second Synchronization Event                                                                          |       |

| 3-60         | McASP Receive Example After Receiving the Third Synchronization Event                                                                           | 135   |

| 3-61         | McASP Receive Example After Receiving the Eight Synchronization Events                                                                          |       |

| 3-62         | McASP Receive Example After Receiving the Nine Synchronization Event                                                                            |       |

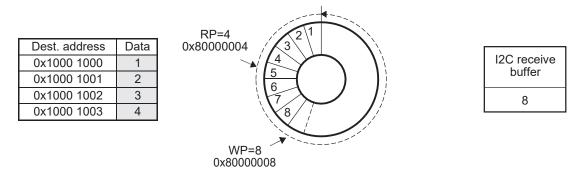

| 3-63         | FIFO FMARK Example Diagram (Before First I2C Event)                                                                                             |       |

| 3-64         | FIFO FMARK Example Diagram (After First Synchronization Event from the I2C)                                                                     |       |

| 3-65         | FIFO FMARK Example (After the Eighth Element Has Been Transferred)                                                                              |       |

| 3-66         | dMAX FIFO Status Registers Before FIFO FMARK is Reached                                                                                         |       |

| 3-67         | dMAX FIFO Status Registers After FIFO FMARK is Reached                                                                                          | . 138 |

| 3-68         | FIFO FMARK Example (After FIFO Read Transfer)                                                                                                   |       |

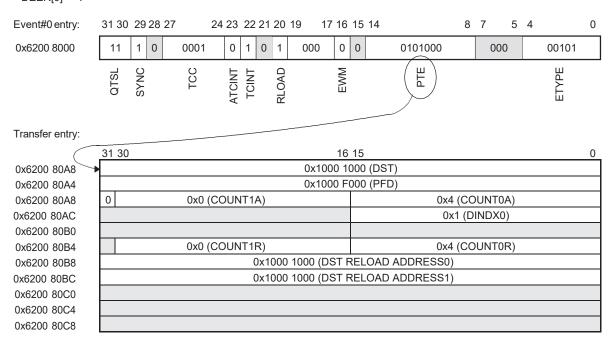

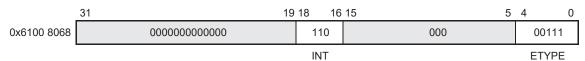

| 3-69         | Event Entry and Transfer Entry for FIFO FMARK Example (FIFO Write Transfer)                                                                     | . 139 |

| 3-70         | Event Entry and Transfer Entry for FIFO FMARK Example (FIFO Read Transfer)                                                                      | . 139 |

| 3-71         | FIFO Descriptor for FIFO FMARK Example                                                                                                          |       |

| 3-72         | FIFO EMARK Example Diagram (Before First I2C Event)                                                                                             | 141   |

| 3-73         | FIFO EMARK Example Diagram (After First Synchronization Event from the I2C)                                                                     |       |

| 3-74         | FIFO EMARK Example (After the Fourth Element has been Transferred)                                                                              | 141   |

| 3-75         | dMAX FIFO Status Registers Before FIFO EMARK is Reached                                                                                         | 142   |

| 3-76         | dMAX FIFO Status Registers After FIFO EMARK is Reached                                                                                          | 142   |

| 3-77         | FIFO EMARK Example (After FIFO Write Transfer)                                                                                                  | 142   |

| 3-78         | Event Entry and Transfer Entry for FIFO EMARK Example (FIFO Read Transfer)                                                                      | 143   |

| 3-79         | Event Entry and Transfer Entry for FIFO EMARK Example (FIFO Write Transfer)                                                                     | 144   |

| 3-80         | FIFO Descriptor for FIFO FMARK Example                                                                                                          |       |

| 3-81         | Event Used to Trigger CPU Interrupt INT13 Example                                                                                               | . 145 |

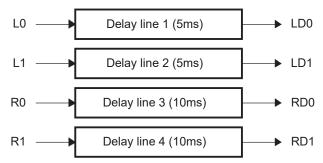

| 3-82         | Block Diagram of the Delay Effect on Four Input Channels                                                                                        | .146  |

| 3-83         | Sequence of Events for Processing                                                                                                               | 146   |

| 3-84         | FIFO Descriptor and Block Diagram of FIFO                                                                                                       |       |

| 3-85         | Table-Guided Multi-tap Delay FIFO Write Transfer. Situation Before Transfer Start                                                               | . 149 |

| 3-86         | Condition After Fresh Block of Data from the First Channel Moved to the First Delay Line                                                        | . 150 |

| 3-87         | Condition After Fresh Block of Data From the Second Channel Moved to the Second Delay Line                                                      | . 151 |

| 3-88         | Condition After Fresh Block of Data From the Third Channel is Moved to the Third Delay Line                                                     | . 152 |

| 3-89<br>3-90 | Condition After a Fresh Block of Data From the Fourth Channel is Moved to the Fourth Delay Line                                                 |       |

| 0.04         | Transfer. Situation Before Transfer Start                                                                                                       |       |

| 3-91         | Condition After Delayed Block of Data is Retrieved From the First Delay Line                                                                    |       |

| 3-92         | Condition After Delayed block of Data is Retrieved From the Second Delay Line                                                                   |       |

| 3-93         | Condition After Delayed Block of Data is Retrieved From the Third Delay Line                                                                    |       |

| 3-94         | condition After a Block of Data is Retrieved From the Fourth Delay Line                                                                         |       |

| 3-95         | FIFO Descriptor and Block Diagram of FIFO After Moving Four Delay TAPS to Four Delay Lines                                                      |       |

| 4-1          | Three Transfer Types Used to Collect Performance Data                                                                                           |       |

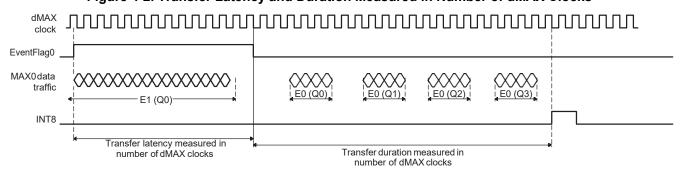

| 4-2<br>4-3   | Transfer Latency and Duration Measured in Number of dMAX Clocks                                                                                 |       |

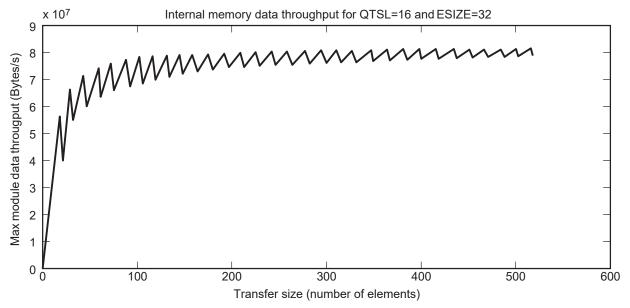

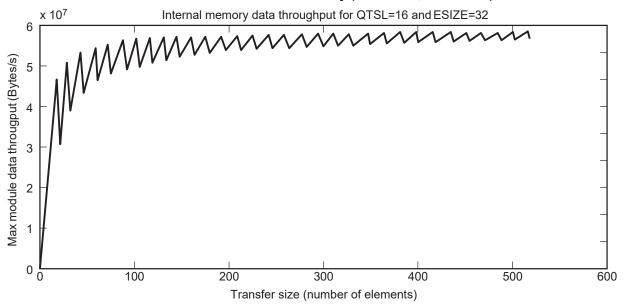

| 4-4          | MAX Module Data Throughput for Sorting of Sequential Block of Data when both Source and Destination are in Internal Memory (SINDX0≠1, DINDX0=1) |       |

| 4-5          | Table-Guided Multi-tap Delay FIFO Transfer                                                                                                      |       |

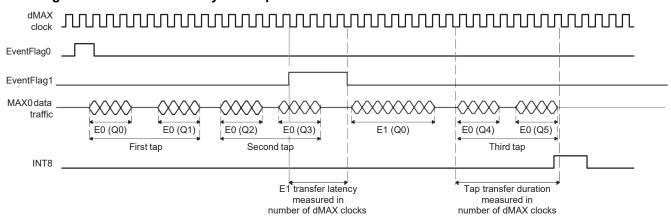

| 4-6          | Transfer Latency and Tap Transfer Duration Measured in Number of dMAX Clocks                                                                    |       |

| . •          |                                                                                                                                                 |       |

## **List of Tables**

| 1-1          | Differences Between the C621x/C671x EDMA and C672x dMAX                                                                                                   | 17  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1-2          | dMAX Channel Synchronization Events                                                                                                                       | 49  |

| 2-1          | Event Entry for General Purpose Data Transfer Field Descriptions                                                                                          | 57  |

| 2-2          | Event Entry for FIFO Transfer Field Descriptions                                                                                                          | 59  |

| 2-3          | Event Entry for Interrupt from dMAX Controller to the CPU Field Descriptions                                                                              | 60  |

| 2-4          | Table Describing Bit Fields of Event Entry for One-Dimensional Burst Transfer                                                                             |     |

| 2-5          | Table Describing Bit Fields of Event Entry for SPI Slave Transfer                                                                                         |     |

| 2-6          | Transfer Entry for General Purpose Data Field Descriptions                                                                                                |     |

| 2-7          | Transfer Entry for FIFO Write Field Descriptions                                                                                                          |     |

| 2-8          | Transfer Entry for FIFO READ Field Descriptions                                                                                                           |     |

| 2-9          | Transfer Entry for One-Dimensional Burst Transfer Description                                                                                             |     |

| 2-10         | Transfer Entry for SPI Slave Transfer Description                                                                                                         |     |

| 2-11         | FIFO Descriptor Field Descriptions                                                                                                                        |     |

| 2-11         | dMAX Control Registers                                                                                                                                    |     |

| 2-12<br>2-13 | dMAX Event Register 0 (DER0) Field Descriptions                                                                                                           |     |

| 2-13<br>2-14 | dMAX Event Register 1 (DER1) Field Descriptions                                                                                                           |     |

|              | · · · · · · · · · · · · · · · · · · ·                                                                                                                     |     |

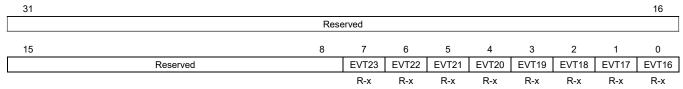

| 2-15         | dMAX Event Register 2 (DER2) Field Descriptions                                                                                                           |     |

| 2-16         | dMAX Event Register 3 (DER3) Field Descriptions                                                                                                           |     |

| 2-17         | dMAX Event Flag Register (DEFR) Field Descriptions                                                                                                        |     |

| 2-18         | dMAX Event Enable Register (DEER) FIELD Descriptions                                                                                                      |     |

| 2-19         | dMAX Event Disable Register (DEDR) Field Descriptions                                                                                                     |     |

| 2-20         | dMAX Event Polarity Register (DEPR) Field Descriptions                                                                                                    |     |

| 2-21         | dMAX Event High Priority Register (DEHPR) Field Descriptions                                                                                              |     |

| 2-22         | dMAX Event Low Priority Register (DELPR) Field Descriptions                                                                                               |     |

| 2-23         | dMAX FIFO Status Register 0 (DFSR0) Field Descriptions                                                                                                    |     |

| 2-24         | dMAX FIFO Status Register 1 (DFSR1) Field Descriptions                                                                                                    |     |

| 2-25         | dMAX Transfer Completion Register 0 (DTCR0) Field Descriptions                                                                                            | 82  |

| 2-26         | dMAX Transfer Completion Register 1 (DTCR1) Field Descriptions                                                                                            | 82  |

| 2-27         | dMAX Event Trigger (DET) Register Field Descriptions                                                                                                      | 83  |

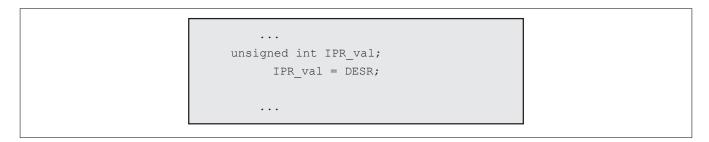

| 2-28         | dMAX Event Status Register (DESR) Field Descriptions                                                                                                      | 85  |

| 4-1          | MAX Module Performance for Copy of a Block of Sequential Elements when both Source and                                                                    |     |

|              | Destination are in Internal Memory                                                                                                                        | 171 |

| 4-2          | MAX Module Performance for Sorting of Sequential Elements when both Source and Destination are in Internal Memory                                         | 173 |

| 4-3          | MAX Module Performance for Sorting of Non-Sequential Elements when both Source and Destination                                                            |     |

|              | are in Internal Memory                                                                                                                                    | 175 |

| 4-4          | MAX Module Performance for Copy of Block of Sequential Elements from McASP DMA Port Source to Destination in Internal Memory                              | 177 |

| 4-5          | MAX Module Performance for Copy of a Block of Sequential Elements from Source in the Internal                                                             |     |

|              | Memory to McASP DMA Port Destination                                                                                                                      | 177 |

| 4-6          | MAX Module Performance for Sorting of Sequential Elements from McASP DMA Port Source to                                                                   |     |

|              | Non-Sequential Destination in Internal Memory                                                                                                             | 178 |

| 4-7          | MAX Module Performance for Sorting of Non-Sequential Data from Source in the Internal Memory to                                                           |     |

| 4.0          | McASP DMA Port Destination                                                                                                                                | 178 |

| 4-8          | MAX Module Performance for Copy of a Block of Sequential Elements when Source is in Internal Memory and Destination is in the SDRAM (EMIF is 32-bit wide) | 190 |

| 4-9          | MAX Module Performance for Copy of a Block of Sequential Elements when Source is in SDRAM and                                                             | 100 |

| 4-9          | Destination is in Internal Memory (EMIF is 32-bit wide)                                                                                                   | 181 |

| 4-10         | MAX Module Performance for Copy of a Block of Sequential Elements when Source is in Internal                                                              |     |

|              | Memory and Destination is in the SDRAM (EMIF is 16-bit wide)                                                                                              | 182 |

| 4-11         | MAX Module Performance for Copy of a Block of Sequential Elements when Source is in SDRAM and                                                             |     |

|              | Destination is in Internal Memory (EMIF is 16-bit wide)                                                                                                   | 183 |

| 4-12 | MAX Module Performance for Sorting Block of Non-Sequential Elements from Source in Internal Memory to Sequential Locations at Destination in SDRAM (EMIF is 32-bit wide)       | 185   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4-13 | MAX Module Performance for Sorting of Block of Sequential Locations from Source in SDRAM to Non-Sequential Destination Locations in Internal Memory (EMIF is 32-bit wide)      |       |

| 4-14 | MAX Module Performance for Sorting Block of Non-Sequential Elements from Source in Internal Memory to Sequential Locations at Destination in SDRAM (EMIF is 16-bit wide)       |       |

| 4-15 | MAX Module Performance for Sorting of Block of Sequential Locations from Source in the SDRAM to  Non-Sequential Destination Locations in Internal Memory (EMIF is 16-bit wide) |       |

| 4-16 | MAX Module Performance for Moving Sequential Data - Both Source and Destination are in Internal Memory                                                                         |       |

| 4-17 | MAX Module Performance for Moving Sequential Data - Source is in Internal Memory and Destination is in External Memory (EMIF is 32 bits Wide)                                  | .190  |

| 4-18 | MAX Module Performance for Moving Sequential Data - Source is in Internal Memory and Destination is in External Memory (EMIF is 16 bits Wide)                                  | .191  |

| 4-19 | MAX Module Performance for Moving sequential Data - Source is in External Memory and Destination is in Internal Memory (EMIF is 32 bits Wide)                                  | . 192 |

| 4-20 | MAX Module Performance for Moving Sequential Data - Source is in External Memory and Destination is in Internal Memory (EMIF is 16-bit wide)                                   | . 193 |

| 4-21 | MAX Module Performance for Moving Sequential Data - Source is in External Memory and Destination is in External memory (EMIF is 32-bit Wide)                                   | .194  |

| 4-22 | MAX Module Performance for Moving Sequential Data - Source is in External Memory and Destination is in External Memory (EMIF is 16-bit Wide)                                   | . 195 |

| 4-23 | MAX Module Performance for Handling One SPI Event                                                                                                                              | .195  |

| 4-24 | FIFO Read MAX Module Performance for Moving Various Tap Sizes When Both Source FIFO and Destination Locations are in Internal Memory                                           | . 198 |

| 4-25 | FIFO Read MAX Module Performance for Moving Various Tap Sizes When Source FIFO is in SDRAM and Destination is in Internal Memory (EMIF is 32-bit wide)                         | . 199 |

| 4-26 | FIFO Read MAX Module Performance for Moving Various Tap Sizes when Source FIFO Is In the SDRAM and Destination is in Internal Memory (EMIF is 16-bit wide)                     | . 199 |

| 4-27 | FIFO Write MAX Module Performance for Various Tap Sizes when Source Data and Destination FIFO are in Internal Memory                                                           | .200  |

| 4-28 | FIFO Write MAX Module Performance for Various Tap Sizes when Source is in Internal Memory and Destination FIFO is in SDRAM (EMIF is 32-bit wide)                               |       |

| 4-29 | FIFO Write MAX Module Performance for Various Tap Sizes when Source is in Internal Memory and Destination FIFO is in SDRAM (EMIF is 16-bit wide)                               |       |

| A-1  | Changes in this Revision                                                                                                                                                       |       |

### Read This First

#### **About This Manual**

This document provides an overview and describes the common operation of the data movement accelerator controller (referred to as dMAX throughout this document) in the digital signal processors (DSPs) of the TMS320C672x<sup>™</sup> DSP family. This document also describes operations and registers unique to dMAX. The following chapters are included:

- Chapter 1 provides an overview of dMAX.

- Chapter 2 provides a list of registers and register descriptions that are used in dMAX.

- Chapter 3 presents transfer examples for dMAX.

- Chapter 4 provides performance and throughput data along with guidelines on how to obtain the best performance.

Project collateral discussed in this reference guide can be downloaded from <a href="http://www.ti.com/lit/zip/SPRU795">http://www.ti.com/lit/zip/SPRU795</a>.

#### **Notational Conventions**

This document uses the following conventions:

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in chapter and described in tables

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the C6000™ devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at <a href="https://www.ti.com">www.ti.com</a>.

TMS320C672x DSP Peripherals Overview Reference Guide (literature number <u>SPRU723</u>) describes peripherals available on the TMS320C672x™ DSPs.

*TMS320C6000 Technical Brief* (literature number <u>SPRU197</u>) gives an introduction to the TMS320C62x<sup>™</sup> and TMS320C67x<sup>™</sup> DSPs, development tools, and third-party support.

TMS320c672x DSP CPU and Instruction Set Reference Guide (literature number <u>SPRU733</u>) describes the TMS320C672x<sup>™</sup> CPU architecture, instruction set, pipeline, and interrupts for these digital signal processors.

*TMS320C6000 Code Composer Studio Tutorial* (literature number <u>SPRU301</u>) introduces the Code Composer Studio ™ integrated development environment and software tools.

*TMS320C6000 Programmer's Guide* (literature number <u>SPRU198</u>) describes ways to optimize C and assembly code for the TMS320C6000 DSPs and includes application program examples.

Code Composer Studio Application Programming Interface Reference Guide (literature number SPRU321) describes the Code Composer Studio™ application programming interface (API), which allows you to program custom plug-ins for Code Composer.

#### **Trademarks**

TMS320C672x, C6000, TMS320C62x, TMS320C67x, Code Composer Studio are trademarks of Texas Instruments.

## Introduction/Feature Overview

This chapter provides an overview of the data movement acceleration controller (dMAX) and its features.

| lopic |                                    | Page |

|-------|------------------------------------|------|

|       |                                    |      |

| 1.1   | Overview                           | 14   |

| 1.2   | dMAX Terminology                   | 18   |

| 1.3   | Initiating dMAX Transfers          | 20   |

| 1.4   | FIFO Implementation                | 20   |

| 1.5   | Types of dMAX Transfers            | 23   |

| 1.6   | Quantum Transfers                  | 44   |

| 1.7   | Element Size and Alignment         | 45   |

| 1.8   | Source/Destination Address Updates | 45   |

| 1.9   | Reloading dMAX Transfers           | 45   |

| 1.10  | dMAX Interrupt Generation          | 45   |

| 1.11  | Emulation Operation                | 47   |

| 1.12  | Event Encoder                      |      |

|       |                                    |      |

#### 1.1 Overview

The dMAX controller handles user-programmed data transfers between the internal data memory controller and the device peripherals on the C672x DSP, as shown in Figure 1-1. dMAX also allows movement of data to/from any addressable memory space, including internal memory, peripherals, and external memory. Additionally, it has a different architecture from the previous EDMA controller in the C621x/C671x devices.

Figure 1-1. TMS320C672x Block Diagram

The dMAX controller includes the capability to:

- Perform three-dimensional data transfers for advanced data sorting

- Manage a section of the memory as a circular buffer/FIFO with delay tap based reading and writing data

- Concurrently process two transfer requests (provided that they are to/from different source/destinations)

Figure 1-2 shows a block diagram of dMAX which includes:

- Event and interrupt processing registers

- Event encoder

- High priority event parameter RAM (PaRAM)

- Low priority event parameter RAM (PaRAM)

- Address generation hardware for high-priority events MAX0 (HiMAX)

- Address generation hardware for low-priority events MAX1 (LoMAX)

The TMS320C672x peripheral bus structure can be described logically as a high-performance crossbar switch with five master ports and five slave ports (shown in Figure 1-1). When accessing the slave ports, the MAX0 (HiMAX) module is always given the highest priority, followed by the MAX1 (LoMAX) module. If, for example, several masters, including MAX0 and MAX1, attempt concurrently to access the same slave port, the MAX0 module will be given the highest priority, followed by the MAX1 module.

Event signals are connected to bits of the dMAX Event Register (DER), and the bits in the DER reflect the current state of the event signals. An event is defined as a transition of the event signal. The dMAX Event Flag Register (DEFR) can be programmed individually for each event signal, to capture either low-to-high or high-to-low transitions of the bits in the DER (event polarity is individually programmable). Event polarity is programmable in the dMAX Event Polarity Register (DEPR).

An event is also a synchronization signal that can be used: 1) to trigger dMAX to start a transfer, or 2) to generate an interrupt to the CPU. All the events are sorted into two groups: a low-priority event group (the LoMAX module serves these requests) and a high-priority event group (the HiMAX module serves these requests).

Simultaneous occurrences of events are prioritized by the event encoder, which sorts them out and chooses the two highest priority events - one from each priority group. The event encoder then passes the events to the address-generation hardware. The priority of simultaneous events within a group is resolved according to the event number (an event with the lower number has higher priority within its group). dMAX can simultaneously process the two highest priority requests from each priority group.

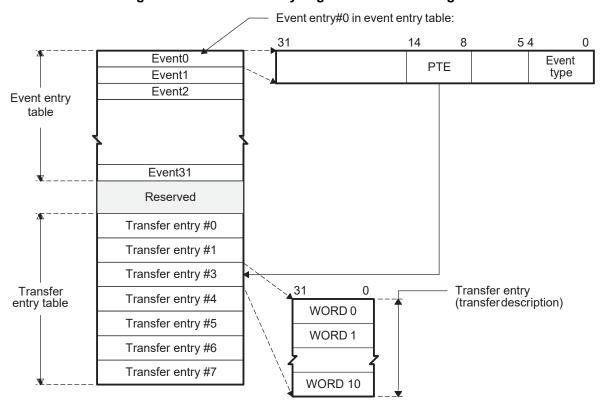

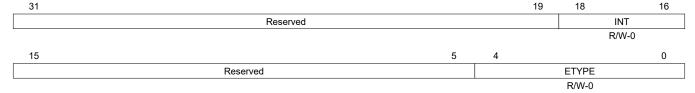

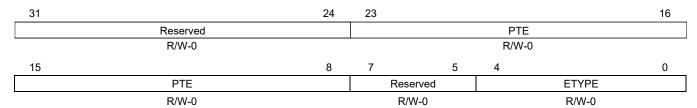

Each PaRAM contains an event entry table section and a transfer entry table section. An event entry describes an event type and associates the event to either one of the transfer types or to an interrupt. If an event entry associates the event to one of the transfer types, the event entry will contain a pointer to the specific transfer entry in the transfer entry table. The transfer entry table may contain up to eight transfer entries. A transfer entry specifies details required by dMAX to perform the transfer. If an event entry associates the event to an interrupt, the event entry specifies which interrupt should be generated to the CPU when the event arrives.

Prior to enabling events and triggering a transfer, the event entry and transfer entry must be configured. The event entry must specify type of transfer, transfer details (type of synchronization, reload, element size, etc.), and should include a pointer to the transfer entry. The transfer entry must specify source, destination, counts, and indexes. If an event is sorted in the high-priority event group, the event entry and transfer entry must be specified in the high-priority parameter RAM. If an event is sorted in the low-priority event group, the event entry and transfer entry must be specified in the low-priority parameter RAM.

When an event is used to trigger a CPU interrupt, the event entry specifies which interrupt line should be used, and a transfer entry is not required. When an event is used to trigger a data transfer, the event entry specifies the type of transfer, transfer options, and points to the transfer entry. The transfer entry is stored in the parameter RAM, and is passed to the address generation hardware (MAX modules), which addresses the external memory interface (EMIF) and/or peripherals to perform the necessary read and write transactions.

Figure 1-2. dMAX Controller Block Diagram

Table 1-1 summarizes the difference between dMAX and the C6000 EDMAs.

Table 1-1. Differences Between the C621x/C671x EDMA and C672x dMAX

| Features                                                                                   | C621x/671x EDMA                                           | dMAX                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum number of channels                                                                 | 16                                                        | 16                                                                                                                                                                                                                          |

| Parameter RAM size                                                                         | 2048 bytes                                                | 1024 bytes (512b HiMAX + 512b LoMAX)                                                                                                                                                                                        |

| Alternate transfer complete interrupt                                                      | No                                                        | Yes                                                                                                                                                                                                                         |

| Transfer chaining                                                                          | Only channels 8 to 11                                     | No                                                                                                                                                                                                                          |

| Linking transfers                                                                          | Yes                                                       | No (Values used for transfer reload are built inside a transfer entry)                                                                                                                                                      |

| Clock rate                                                                                 | EDMA clock rate equals CPU clock rate                     | dMAX clock rate equals of the CPU clock rate                                                                                                                                                                                |

| Parameter storage for an event                                                             | 6 words                                                   | 11 words                                                                                                                                                                                                                    |

| Number of words in parameter RAM required to specify a data transfer with reload           | 18 words                                                  | 11 words                                                                                                                                                                                                                    |

| CIER Register                                                                              | Yes                                                       | No                                                                                                                                                                                                                          |

| CIPR Register Flag Clear                                                                   | Write 1 to clear                                          | dMAX Transfer Completion (DTCR) Register has similar functionality. Write 1 to clear.                                                                                                                                       |

| Event Select Register                                                                      | Yes                                                       | No (Event Entry Table used for similar purpose)                                                                                                                                                                             |

| Priority Queue Status Register                                                             | Yes                                                       | No                                                                                                                                                                                                                          |

| Interrupt events to the CPU                                                                | 1                                                         | 8 dMAX handles CPU interrupts along with transfer<br>events. One interrupt line (INT8) is dedicated for end of<br>transfer notification. One interrupt line (INT7) is<br>dedicated for FIFO status and error notifications. |

| Event Set Register                                                                         | Yes                                                       | No. The CPU can initiate transfers by using dMAX Event Trigger (DETR) Register.                                                                                                                                             |

| Event Clear Register                                                                       | Yes                                                       | No.                                                                                                                                                                                                                         |

| Event Enable Register                                                                      | Yes                                                       | Yes. Used only to enable events. Write 0 has no effect.                                                                                                                                                                     |

| Event Disable Register                                                                     | No                                                        | Yes. Write 1 to disable an event                                                                                                                                                                                            |

| QDMA transfers                                                                             | Yes                                                       | No                                                                                                                                                                                                                          |

| Event polarity selection                                                                   | No                                                        | Yes                                                                                                                                                                                                                         |

| Event Register (reflects current state of event signals)                                   | No                                                        | Yes                                                                                                                                                                                                                         |

| Event Flag Register (Captures transitions on event signals captured in the Event Register) | Yes. (On 621x/671x, called ER)                            | Yes                                                                                                                                                                                                                         |

| 3D transfer support                                                                        | No                                                        | Yes                                                                                                                                                                                                                         |

| Independent index fields for source and destination for all transfer dimensions.           | No                                                        | Yes                                                                                                                                                                                                                         |

| Size of index field for the first transfer dimension                                       | 16                                                        | 16                                                                                                                                                                                                                          |

| Size of index field for the second transfer dimension                                      | 16                                                        | 16                                                                                                                                                                                                                          |

| Internal Read/Write Path Width                                                             | 64 bits                                                   | Each of two MAX modules has 32-bit wide path                                                                                                                                                                                |

| Size of index field for the third transfer dimension                                       | N/A                                                       | 16                                                                                                                                                                                                                          |

| Frame index usage to derive the next frame start address                                   | Frame index added to the start element address in a frame | Frame index added to the address of a last element in a frame                                                                                                                                                               |

| Priority levels for events                                                                 | Yes. Set in the PRI bit field in the OPT parameter        | Yes. If set, bits in DEHPR put events into the high-priority group. If set, bits in DELPR put events into the low-priority group.                                                                                           |

| Error notification to the CPU in case of FIFO overflow or underflow                        | No                                                        | Yes                                                                                                                                                                                                                         |

| Transfer indexes expressed in no. of elements                                              | No                                                        | Yes                                                                                                                                                                                                                         |

| Circular buffer support                                                                    | No                                                        | Yes                                                                                                                                                                                                                         |

| Table based multi-tap delay transfers                                                      | No                                                        | Yes                                                                                                                                                                                                                         |

#### 1.2 dMAX Terminology

The following definitions help to understand some of the terms used in this document:

- **dMAX:** Dual data movement accelerator. dMAX is composed of two equivalent modules, MAX0 and MAX1. The MAX modules can operate in parallel.

- **Element transfer:** An element transfer is the transfer of a single data element (8-,16-, or 32-bit) from source to destination. Each element can be transferred based on a synchronization event, if required. Element transfer is used in context with (1D) transfer.

- **Frame:** A group of elements comprise a frame. A frame can have staggered or contiguous elements. A frame can be transferred with or without a synchronizing event. Frame is used in context with one-dimensional (1D) transfer.

- **Event:** An event is a transition on an event signal latched in the dMAX Event Flag Register (DEFR). For example, data received by the McASP can trigger an event.

- **Event Entry:** If an event is used to trigger a data transfer, the event entry should be set to specify the type of transfer, the transfer options, and should include a pointer to a transfer entry. If the event is used to trigger an interrupt, the event entry only specifies which interrupt line should be used.

- The event entry uses only one word of memory space in the dMAX parameter RAM, within which is a one-to-one correspondence between the events and the event entries. A unique event entry is assigned to an event in each PaRAM (an event has one event entry in the high-priority PaRAM, and one event entry in the low-priority PaRAM). The event priority group decides which event entry will be passed to the HiMAX/LoMAX once an event arrives.

- All the events are sorted into low- or high-priority groups. The event encoder prioritizes all received events, and sorts the event with the highest priority from each group. The two highest priority events (one from each group) can be processed at the same time (HiMAX will process the highest priority request from the high priority event group, and LoMAX will process the highest priority request from the low priority event group). An event entry is programmable and defines how the corresponding event is going to be processed when it arrives.

- Event Entry Table: The event entry table contains all the event entries and occupies 32 words; it is located at the very beginning of the parameter RAM. There are two event entry tables, one for high priority events and the other for low priority events. If an event belongs to a high priority event group, then its event entry is located in the high-priority event entry table. If an event belongs to a low priority event group, then its event entry is located in the low-priority event entry table.

- Event Priority Group: dMAX events can be configured as either high-priority or low-priority. This splits events into two priority groups; high-priority or low-priority. The high-priority event group is serviced by the MAX0 module. The low-priority event group is serviced by the MAX1 module.

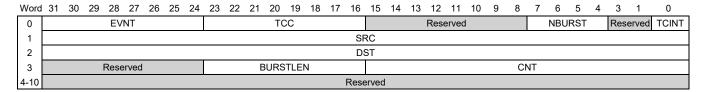

- **Transfer Entry:** The transfer entry table includes an 11-word long entry that defines transfer parameters such as source, destination, count, and indexes. There is enough space in each parameter RAM to keep transfer entries for eight different transfers (16 transfer entries total).

- Quantum Transfer: To improve system latency, long data transfers are divided into a number of smaller transfers (quantum transfers). The dMAX controller is always moving data in small sub-transfers called quantum transfers. If an event arrives while dMAX is performing a quantum transfer, the event will be serviced after the current quantum has been transferred.

- Quantum Transfer Size Limit (QTSL): The maximum size of a quantum transfer is programmable

within the event entry for a given channel. It can be programmed to be 1, 4, 8, or 16 elements. The

actual size of a quantum transfer is the smaller of the QTSL and the number of elements still to be

transferred. Decreasing the QTSL will decrease the overall dMAX latency; increasing it will increase

the dMAX data throughput.

- Pending Event: A pending event is an event latched in the DEFR that has not been processed by the dMAX controller.

- Long Data Transfer: A long data transfer occurs when the number of elements to be transferred after each synchronization event is larger than the QTSL.

- One-Dimensional (1D) Transfer: A group of elements makes up a 1D block. The number of elements in this block can be specified as well as the spacing between them. The spacing can be specified independently for both the source and the destination and can range from -32768 to +32767 elements).

- Two-Dimensional (2D) Transfers: A group of frames comprise a 2D block. The first dimension is the number of elements in a frame, and the second dimension is the number of frames. The number of frames in a 2D block can range from 1 to 65535. Either frames or the entire 2D block can be transferred at a time. Spacing between frames can be specified independently for source and destination (valid values for frame index: -32768 to 32767 elements).

- Three-Dimensional (3D) Transfers: A group of 2D blocks comprise a 3D block. The first dimension is the number of elements in a frame, and the second dimension is the number of such frames, and the third dimension is number of 2D blocks. The number of 2D blocks can range from 1 to 32767. Either a frame or the entire 3D block can be transferred at a time. Spacing between 2D blocks can be specified independently for source and destination (valid values for spacing between 2D blocks are: -32768 to 32767 elements).

- One-Dimensional Burst (1DN) Transfer: One-dimensional burst transfer is optimized for moving sequential data from one memory location to the other. This transfer does not support non-sequential source or destination.

- **SPI Slave Transfer:** SPI peripheral servicing requires that for a given SPI event, one element be read from the SPI input register and an element be written to the SPI output shift register. The SPI slave transfer provides this functionality.

- **FIFO (Circular Buffer):** A FIFO is defined by its base address, size, two watermarks and two pointers (read pointer and write pointer). The two pointers are continuously chasing each other as data is being written to and read from the buffer. Reads and writes to the buffer are asynchronous to each other. When the FIFO is filled with data, the pointers wrap around and new samples overwrite the old data. The FIFO size is specified in number of elements; it does not have to be a power of two.

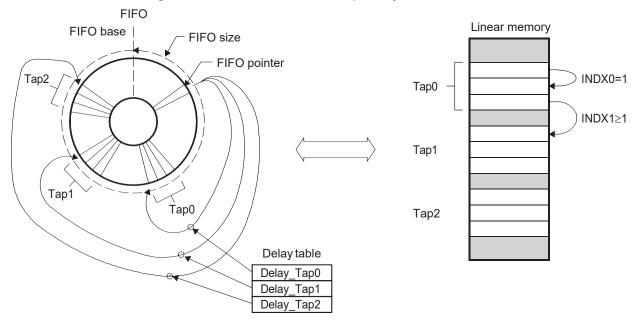

- Table-based Multi-tap Delay Transfer: Many audio algorithms access large delay buffers in a non-sequential fashion. A table-based, multi-tap delay transfer reads/writes elements to/from a FIFO according to table of pre-defined delay tap offsets.

- Table based, multi-tap delay memory access patterns have arbitrary spacing between consecutive taps (defined by the delay tables), and have predictable contiguous spacing within a tap (the delay samples within a tap are contiguous).

- dMAX Channel: An event signal associated with the event entry and transfer entry used to transfer data.

- Reference (Reload) Registers in Transfer Entry: Values from the reference set of registers are used

to load the active set of registers at the end of a transfer if reload is enabled. This facilitates the

ping-pong buffering scheme.