# **Emulation and Trace Headers**

# **Technical Reference Manual**

Literature Number: SPRU655I February 2003–Revised August 2012

# **Contents**

| Prefac | се      |                                                           | . 5        |

|--------|---------|-----------------------------------------------------------|------------|

| 1      | Introd  | uction                                                    | . <b>7</b> |

| 2      | Adapt   | ers                                                       | . 9        |

| 3      | Funda   | mental Information                                        | . 9        |

| 4      | Altern  | ate Target Impedance Configurations                       | . 9        |

| 5      | Heade   | er Information                                            | 10         |

| 6      | Heade   | er Footprint Comparisons                                  | 10         |

| 7      | Targe   | t Mating Caution                                          | 12         |

| 8      | Heade   | er Pin Assignment                                         | 12         |

| 9      | Electr  | ical Requirements                                         | <b>21</b>  |

| 10     | Single  | -Processor Termination                                    | 23         |

| 11     | Buffer  | ing                                                       | 24         |

| 12     | Gener   | al Specifications                                         | 24         |

| 13     | Accep   | otable Signal Qualifications                              | 25         |

| 14     | Conne   | ecting Alternate Headers                                  | 26         |

|        | 14.1    | TI 14-Pin and 60-Pin Headers in Parallel                  | 26         |

| 15     | Layou   | t and Routing Requirements                                | <b>27</b>  |

|        | 15.1    | Maximum Recommended Distances                             | 27         |

| 16     | Advar   | nced Emulation - Layout and Route Distance Deviations     |            |

|        | 16.1    | - 3 3                                                     |            |

|        | 16.2    | 3 - 3 -                                                   |            |

| 17     |         | ional JTAG Emulation Layout and Route Distance Deviations |            |

|        | 17.1    | .,                                                        |            |

| 18     |         | Function Trace Pins                                       |            |

| 19     | •       | le Device Considerations                                  |            |

|        | 19.1    |                                                           |            |

|        |         | Alternate Target Impedance Configurations                 |            |

|        |         | Buffering - Methods, Techniques and Terminations          |            |

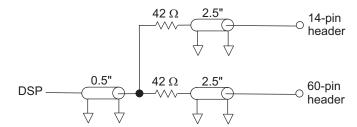

| • •    |         | TI 14-Pin and 60-Pin Headers in Parallel                  |            |

| Apper  |         | Layout and Routing Requirements                           |            |

|        | D.1     | Layout and Route Deviations [Advanced Emulation]          |            |

|        |         | XDS560T Spice Model                                       |            |

|        |         | XDS560 v2 System Trace Modeling                           |            |

|        |         | XDS Pro Trace Modeling                                    |            |

|        |         | Finding a Buffer's Output Impedance                       |            |

| Apper  | ndix I  | Variable Board Impedance                                  | 63         |

| Revis  | ion His | story                                                     | 64         |

2

# **List of Figures**

| 1  | TI 60-Pin Emulation Header                                                                  | 10 |

|----|---------------------------------------------------------------------------------------------|----|

| 2  | MIPI 60-Pin Header                                                                          | 11 |

| 3  | TI 20-Pin CTI Header                                                                        | 11 |

| 4  | TI 14-Pin Traditional Through-Hole Emulation Interface                                      | 11 |

| 5  | TI 14-Pin Traditional SMT Emulation Interface Header                                        | 11 |

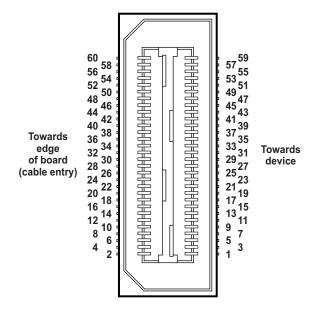

| 6  | 60-Pin Header Orientation                                                                   | 18 |

| 7  | Emulator Cable Connector Superimposed Over 60-Pin Header                                    | 19 |

| 8  | MIPI 60-Pin Header Pin Location                                                             |    |

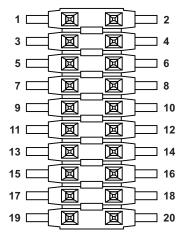

| 9  | TI 20-Pin CTI Header Pin Location                                                           |    |

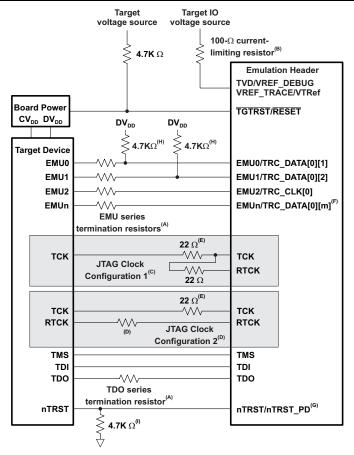

| 10 | Target Connection for Unbuffered JTAG and EMU Signals                                       | 22 |

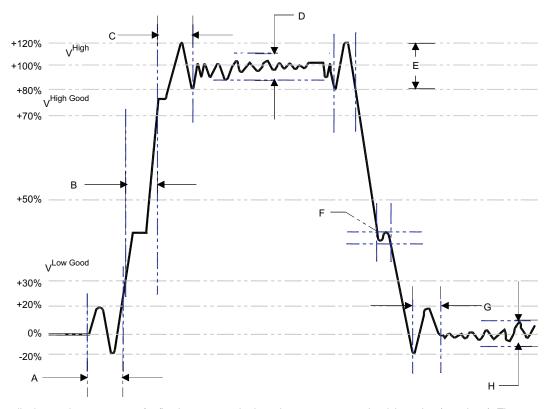

| 11 | Acceptable Wave Form Criteria                                                               |    |

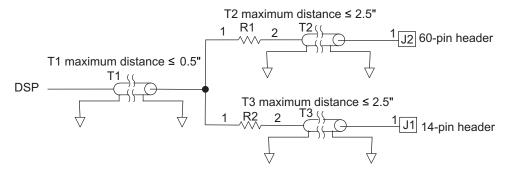

| 12 | Multi-Header EMU0, EMU1, TDO Termination                                                    |    |

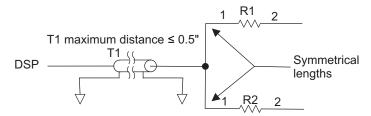

| 13 | Symmetrical Nets                                                                            |    |

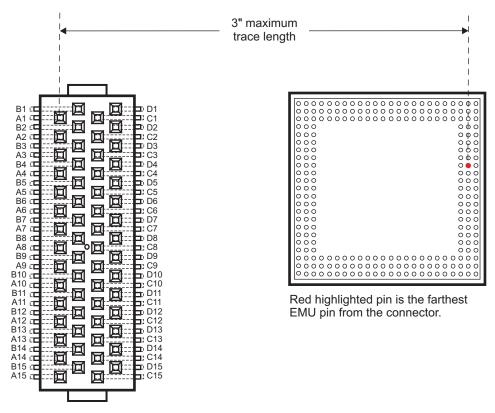

| 14 | TI 60-Pin Connector Maximum Trace Length                                                    |    |

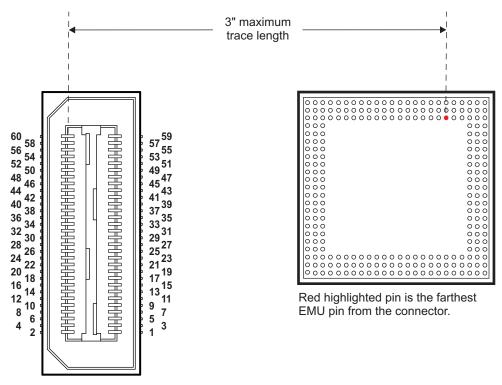

| 15 | MIPI 60-Pin Connector Maximum Trace Length                                                  |    |

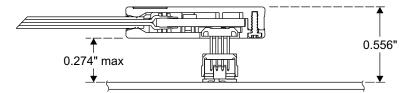

| 16 | XDS560T TI 60-Pin Target Cable Connector Minimum Clearance - Height                         |    |

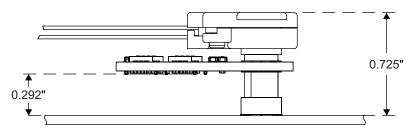

| 17 | XDS560 v2 System Trace MIPI 60-Pin Target Cable Connector Minimum Clearance - Height        |    |

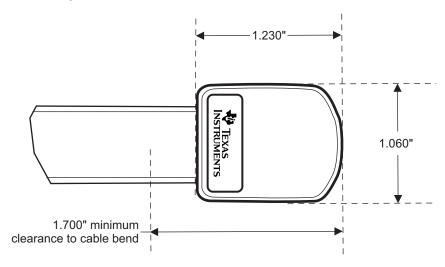

| 18 | XDS560T TI 60-Pin Target Cable Header Dimensions                                            |    |

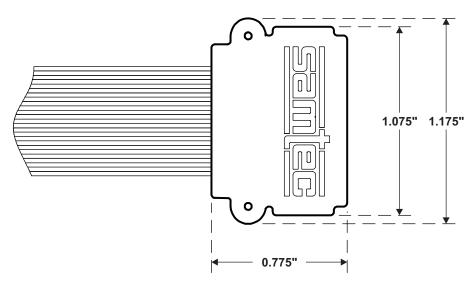

| 19 | XDS560 v2 System Trace MIPI 60-Pin Target Cable Header Dimensions                           |    |

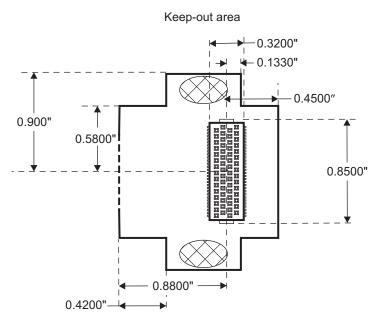

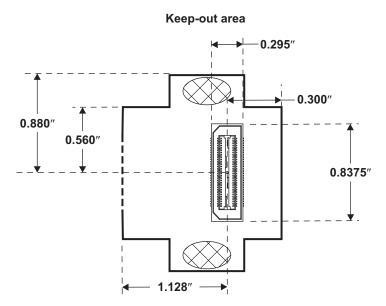

| 20 | XDS560T TI 60-Pin Target Cable Board Keep-Out Area                                          |    |

| 21 | XDS560 v2 System Trace MIPI 60-Pin Target Cable Board Keep-Out Area                         |    |

| 22 | Multi-Function Trace                                                                        |    |

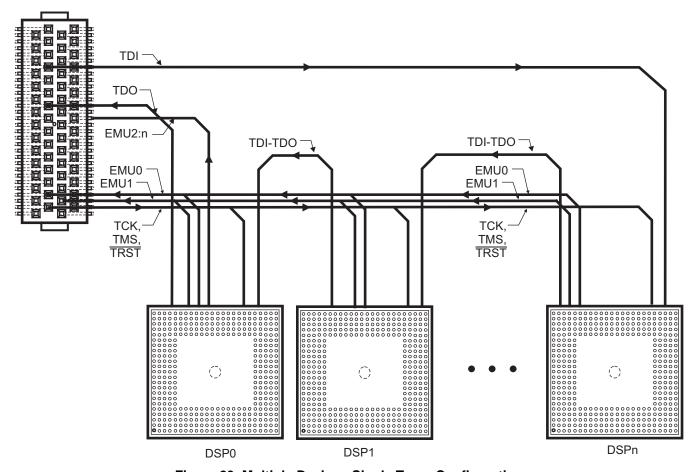

| 23 | Multiple Device - Single Trace Configuration                                                |    |

| 24 | Multiple Device - Parallel Trace Configuration                                              |    |

| 25 | Device-Independent Trace Configuration                                                      |    |

| 26 | Parallel Termination                                                                        |    |

| 27 | Recommended TCK Buffered Configuration                                                      |    |

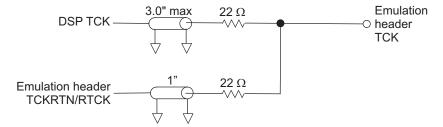

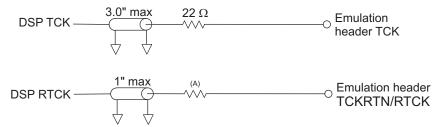

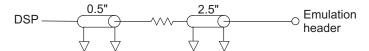

| 28 | Recommended TCK Unbuffered Configuration                                                    |    |

| 29 | Recommended RTCK Configuration                                                              |    |

| 30 | Recommended EMU Output Configuration                                                        |    |

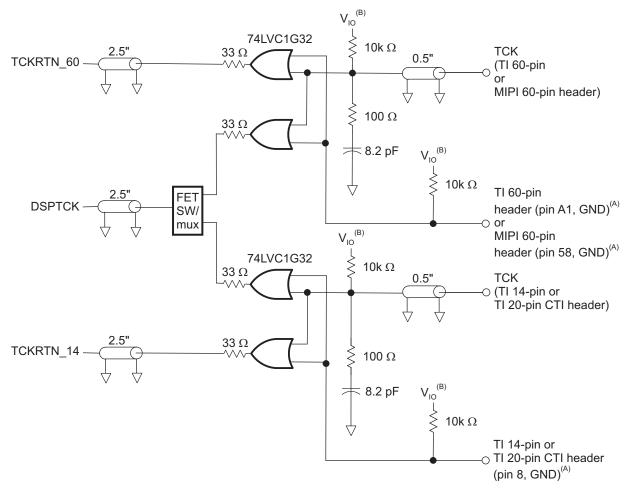

| 31 | TCK, Multiple Header Configuration                                                          |    |

| 32 | Preferred Configuration for EMU0 and EMU1 Terminations                                      |    |

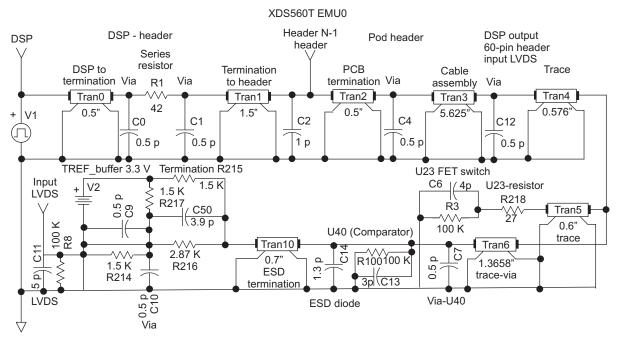

| 33 | EMU0 Simulation Model (TI's XDS560T Pod Assembly - 50-Ω and 75-Ω Target and Pod Model)      |    |

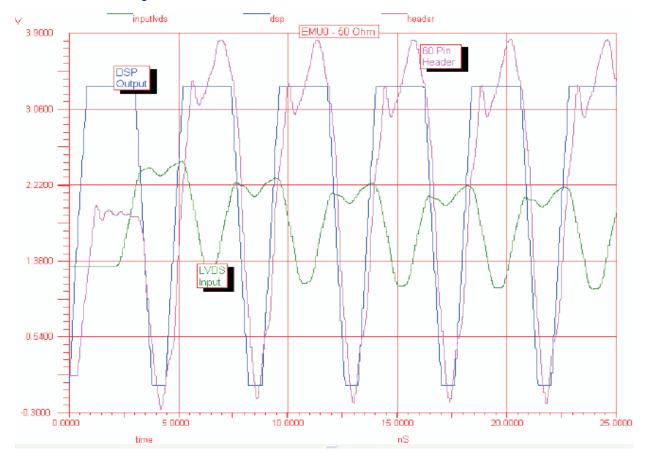

| 34 | EMU0 Acceptable Wave Form (Host Side, Tl's XDS560T Pod - 50 Ω)                              | 46 |

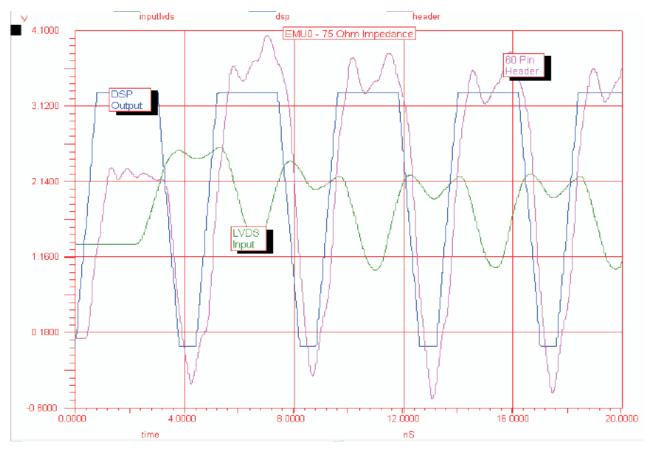

| 35 | EMU0 Wave Form (Host Side, TI's XDS560T - 75 Ω)                                             |    |

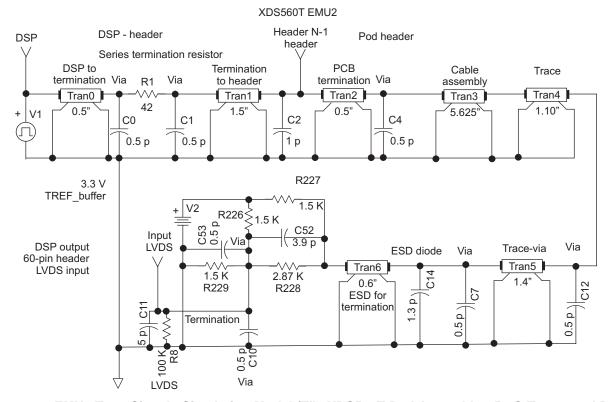

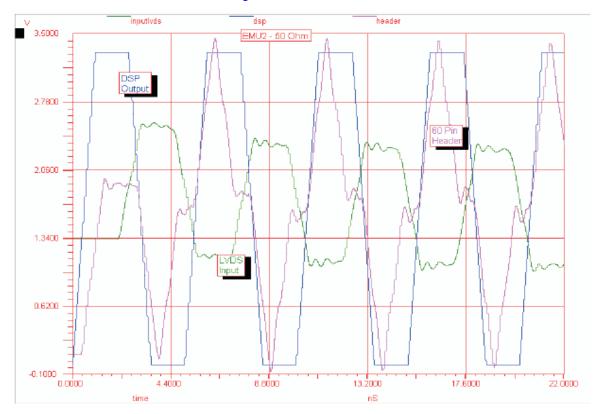

| 36 | EMU2 Type Signals Simulation Model (TI's XDS560T Pod Assembly - 50-Ω Target and Pod Model)  |    |

| 37 | EMU2 Type Signals Acceptable Wave Form (Host Side, TI's XDS560T Pod - 50 Ω)                 | 51 |

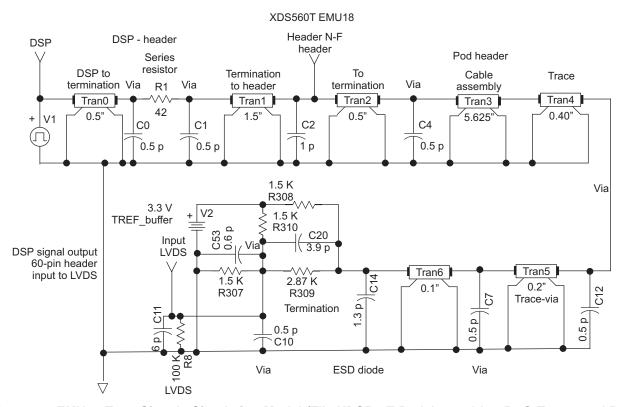

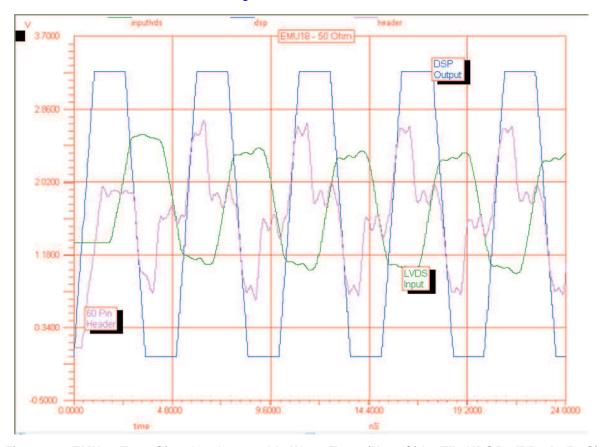

| 38 | EMU18 Type Signals Simulation Model (TI's XDS560T Pod Assembly - 50-Ω Target and Pod Model) | 52 |

| 39 | EMU18 Type Signals - Acceptable Wave Form (Host Side, Tl's XDS560T Pod - 50 Ω)              | 54 |

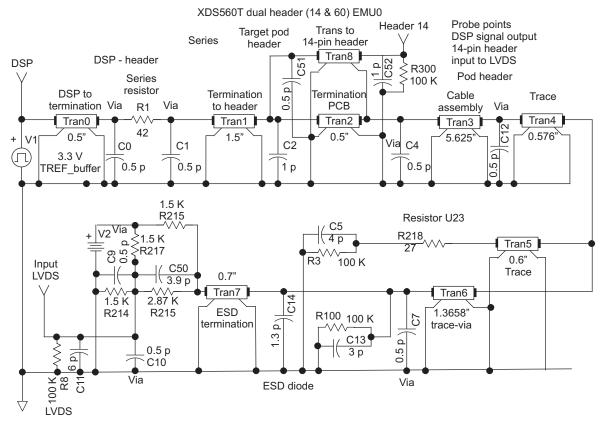

| 40 | EMU0 Dual-Header Simulation Model (TI's XDS560T Pod Assembly - 50-Ω Target and Pod Model)   | 55 |

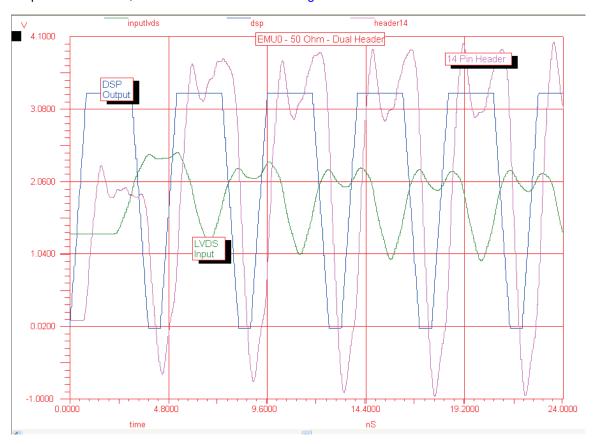

| 41 | EMU0 Dual-Header - Wave Form (Host Side, TI's XDS560T Pod - 50 Ω)                           | 57 |

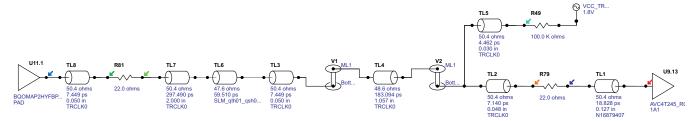

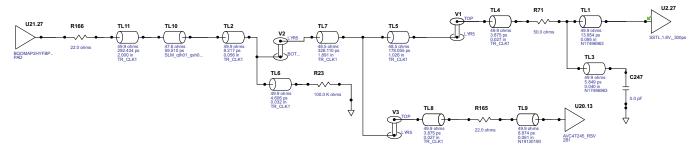

| 42 | TRCLK[0] Model Schematic                                                                    | 58 |

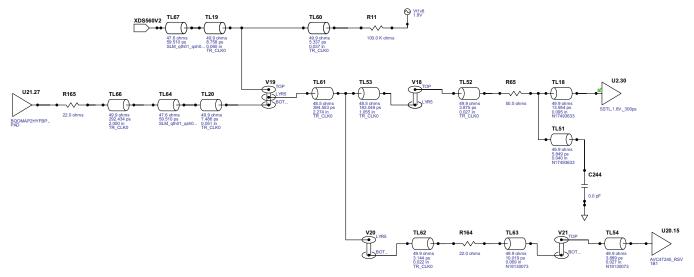

| 43 | TRC_CLK0 Model Schematic                                                                    |    |

| 44 | TRC_CLK1 Model Schematic                                                                    | 59 |

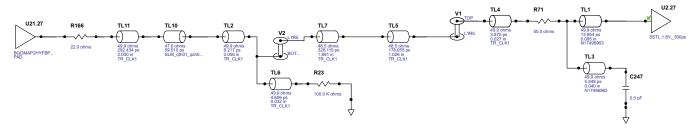

| 45 | TRC_DATA[n] Signal Schematic                                                                | 60 |

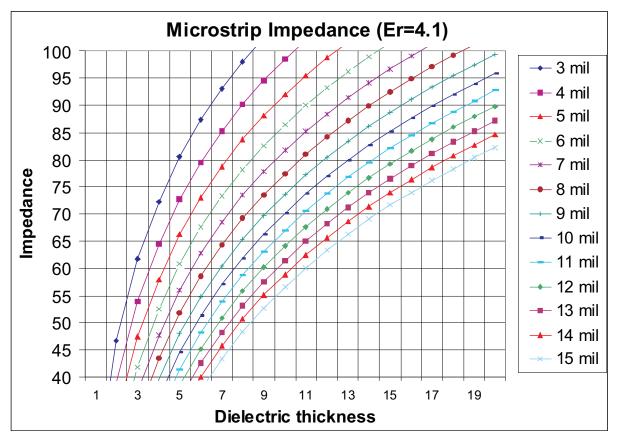

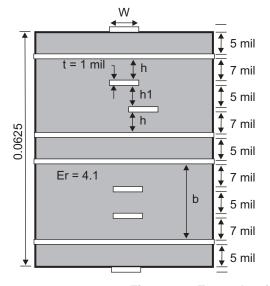

| 46 | Various PCB Impedance Calculations                                                          |    |

| 47 | Example of 10-Layer PCB Construction                                                        |    |

|    |                                                                                             |    |

## **List of Tables**

| 1  | TXDS Trace Support Platforms                                          | 7  |

|----|-----------------------------------------------------------------------|----|

| 2  | Emulation Header Use                                                  | 8  |

| 3  | Adapters                                                              | 9  |

| 4  | Summary: Alternate Target Impedance Configurations                    | 9  |

| 5  | Summary: TI 60-Pin Header Information                                 | 10 |

| 6  | Summary: MIPI 60-Pin Header Information                               | 10 |

| 7  | Summary: TI 20-Pin CTI Header Information                             | 10 |

| 8  | Summary: Header Footprint Comparisons                                 | 12 |

| 9  | Summary: Header Changes                                               | 12 |

| 10 | TI 60-Pin Header Signal Naming Convention                             | 12 |

| 11 | Summary: TI 60-Pin Header Pinout                                      | 14 |

| 12 | MIPI 60-Pin Header Signal Naming Convention                           | 14 |

| 13 | TI 20-Pin CTI Header Signal Naming Convention                         | 16 |

| 14 | Summary: Header Pin Assignments                                       | 18 |

| 15 | JTAG Signal Directions                                                | 21 |

| 16 | Summary: Electrical Requirements                                      | 22 |

| 17 | Termination Values and Use Cases                                      | 23 |

| 18 | Summary: Single-Processor Terminations                                | 23 |

| 19 | Summary: Buffering                                                    | 24 |

| 20 | General Specifications                                                | 24 |

| 21 | Summary: Acceptable Signals                                           | 26 |

| 22 | Summary: TI 14-Pin and 60-Pin Headers in Parallel                     | 27 |

| 23 | Summary: Advanced Emulation Layout and Routing                        | 30 |

| 24 | Summary: Layout and Routing - Mechanical Considerations (TI 60-Pin)   | 32 |

| 25 | Summary: Layout and Routing - Mechanical Considerations (MIPI 60-Pin) | 33 |

| 26 | Sizing Common Termination Resistor Values                             | 36 |

| 27 | EMU Pins Modeled as EMU2 or EMU18                                     | 44 |

| 28 | Buffer Name Decode and Output Impedance                               | 61 |

| 29 | Recommended Series Termination Resistor Value                         | 61 |

| 30 | Model name Evample                                                    | 62 |

### Read This First

#### **About This Manual**

This technical reference describes how to incorporate Texas Instruments' next-generation emulation header on a board with a trace-enabled DSP.

#### **Notational Conventions**

This document uses the following conventions.

- Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

- Measurements are in English standard units (inches, pounds, etc.).

#### **Related Documentation**

The following documents describe the TMS320C6000<sup>™</sup> DSP platform and related support tools. Copies of these documents are available on the Internet at <a href="www.ti.com">www.ti.com</a>. Tip: Enter the literature number in the search box provided at <a href="www.ti.com">www.ti.com</a>.

- SPRA439 Emulation Fundamentals for TI's DSP Solutions. This paper explains the fundamentals of how the emulation logic and emulation tools work together with the TI digital signal processors. By understanding the fundamentals of emulation, you will be able to accelerate the process of setting up and performing software debug, as well as aid in troubleshooting potential problems in the debugging setup. A detailed explanation of the setup of the emulator hardware systems for single and multi-processor applications, along with a discussion of how the system components interact during debug will be discussed in the sections to follow. Also included is a troubleshooting guide to assist in common setup problems.

- SPRU641 TMS320C6000 DSP Designing for JTAG Emulation Reference Guide. This document assists you in meeting the design requirements of the XDS510™ emulator with respect to JTAG designs and discusses the XDS510 cable. This cable supports both standard 3-volt and 5-volt target system power inputs.

- SPRU589 XDS560 Emulator Reference Guide. This technical reference describes the fundamentals of the XDS560™ PCI Emulator and Pod and how to interface it to a target system.

- SPDU079 JTAG/MPSD Emulation Technical Reference. A reference guide that provides detailed information to be used when designing for JTAG emulation.

- SPRAAK6 Common Trace Transmission Problems and Solutions. This document provides guidelines for identifying and solving common problems associated with the collecting of high speed data. On a trace-capable device, the trace interface is one of the highest performance interfaces. Although only used during design, development, and debug, the trace interface must be implemented correctly for full functionality and performance.

Related Documentation www.ti.com

# IEEE Std 1149.1-1990 — IEEE Std 1149.1-1990 IEEE Standard Test Access Port and Boundary-Scan Architecture -Description. Circuitry that may be built into an integrated circuit to assist in the test, maintenance, and support of assembled printed circuit boards is defined. The circuitry includes a standard interface through which instructions and test data are communicated. A set of test features is defined, including a boundary-scan register, such that the component is able to respond to a minimum set of instructions designed to assist with testing of assembled printed circuit boards.

SPRU655I-February 2003-Revised August 2012

# **Emulation and Trace Headers**

#### 1 Introduction

This technical reference describes the requirements necessary to incorporate an emulation header on a board that includes devices that support trace export through the device's EMU pins to an emulator with trace capture support. Texas Instruments device's support various combinations of DSP and ARM® core trace and system trace. Table 1 shows the TI XDS platforms that support trace capture. In all cases, the trace data rates require that the EMU pins be treated as high-speed clocks within your design. This specifically means that the EMU pins must be terminated properly and the correct header chosen for the number of EMU pins required. In the case of core trace or if core trace and system trace export are both supported, this requires utilizing a 60-pin header in place of the traditional TI 14-pin or TI 20-pin CTI emulation header. In the case where a device only supports export of system trace data, a TI 20-pin CTI header may be used.

**Table 1. TXDS Trace Support Platforms**

| XDS                    | DSP Core Trace | ARM Core Trace | System Trace |

|------------------------|----------------|----------------|--------------|

| XDS560v2 System Trace  | No             | No             | Yes          |

| XDS Pro Trace          | Yes            | Yes            | Yes          |

| XDS560T <sup>(1)</sup> | Yes            | No             | No           |

<sup>(1)</sup> Note that the XDS560T has been discontinued, and the TI-60 pin header required by the XDS560T is no longer recommended for new designs.

Core trace typically provides at least processor PC trace, and depending on the silicon implementation may also provide processor data trace and event trace. System trace is a message-based technology that, in enabled silicon, can export application instrumentation and hardware generated messages from system-level monitors. Many devices support on-chip embedded trace buffers (ETBs) either exclusively or in combination with support for exporting trace data through the device's EMU pins. In cases where a device exclusively utilizes an ETB, a 60-pin header is not required to replace the traditional TI 14-pin or TI 20-pin CTI headers on the board, but keep in mind that ETBs only allow visibility to shallow snapshots of data (typically in the 4K to 32K range). To determine if your device supports exporting core or system trace through the EMU pins and/or supports one or multiple ETBs, see the device-specific data sheet. The advantage of exporting core and system trace data through the EMU pins to an emulator with trace capture support is that the capture depth is much greater (typically many Mbytes), providing a much larger region of visibility and enabling precise profiling and code coverage tooling.

If the device supports any type of core trace export that you want to capture using a TI trace-enabled emulator, then a 60-pin header in place of the traditional TI 14-pin or TI 20-pin CTI TI emulation headers is a requirement. If your device supports only export of system trace data, then you can choose the header that fits your needs.

Introduction www.ti.com

#### Table 2. Emulation Header Use

| Trace Type                             | Emulator Type         | Native Emulator Header     |

|----------------------------------------|-----------------------|----------------------------|

| DSP/ARM Core Trace and<br>System Trace | XDS Pro Trace         | MIPI 60-Pin                |

| System Trace                           | XDS560v2 System Trace | MIPI 60-Pin <sup>(1)</sup> |

| DSP Trace                              | XDS560T               | TI 60-Pin                  |

<sup>(1)</sup> Since system trace only utilizes 5 EMU pins, if your processor only supports system trace export through EMU0:4, then you may choose to use a TI-20 pin connector with an adapter.

Even though the 60-pin header supports all the features provided by the original TI 14-pin header, not all emulators, target cables, and target device combinations support all features. To confirm that the desired functionality is supported, see the documentation and device user guides for your specific emulator.

#### **WARNING**

JTAG and Trace Design Problems: Many problems with JTAG and Trace designs are due to incorrect assumptions being utilized during the design. Copying previous known working designs, a common practice, may not always yield good results. For Trace, in cases where you are porting to a new device, make sure you size the termination resistors correctly and model the implementation if your design does not meet this document's requirements. For JTAG, follow the instructions in the <a href="Target Connection Guide">Target Connection Guide</a> and check your implementation against the <a href="XDS Connector Design Checklist">XDS Connector Design Checklist</a>.

www.ti.com Adapters

#### 2 Adapters

Adapters allow the XDS Pro Trace to be used with the TI-60 header or the XDS560 v2 System Trace to be used with standard TI 14-pin and TI 20-pin CTI target headers. Adaptors can also be used to allow a standard XDS100, XDS510, or XDS560 emulator to be used with a target board that is implemented with a TI 60-pin or MIPI 60-pin header. When using the XDS100, XDS510, or XDS560 with a MIPI 60-pin header, the XDS drives the nTRST\_PD pin and not the nTRST/EXTD pin. The adapters, listed in Table 3, are available (or may be available in the future) from TI or its third parties.

Table 3. Adapters

| For Emulator Type     | From Emulator | To Target     | Notes                 |

|-----------------------|---------------|---------------|-----------------------|

| XDS560/XDS510/XDS100  | TI 14-pin     | TI 60-pn      |                       |

| XDS560 Rev D          | TI 20-pin CTI | TI 60-pin     |                       |

| XDS560T               | TI 60-pin     | TI 14-pin     |                       |

| XDS560T               | TI 60-pin     | TI 20-pin CTI |                       |

| XDS560T               | TI 60-pin     | TI 60-pin     | Pin Saver             |

| XDS560v2 System Trace | MIPI 60-pin   | TI 60-pin     |                       |

| XDS560v2 System Trace | MIPI 60-pin   | TI 20-pin CTI |                       |

| XDS560v2 System Trace | MIPI 60-pin   | TI 14-pin     |                       |

| XDS560v2 System Trace | MIPI 60-pin   | ARM 20-pin    |                       |

| XDS Pro Trace         | MIPI 60-pin   | TI 60-pin     |                       |

| XDS Pro Trace         | MIPI 60-pin   | TI 20-pin CTI | For System Trace only |

| XDS Pro Trace         | MIPI 60-pin   | TI 14-pin     | For System Trace Only |

**NOTE:** Use of any adapter can have a negative impact on performance.

#### 3 Fundamental Information

This technical reference offers guidance for creating new designs that take advantage of the extended emulation capabilities. This document is not intended to be the sole design guide.

In addition to this guide, good engineering practices for high-speed logic design and mechanical layout must be followed. Any deviation from such practices and design techniques will affect the end-product performance.

#### 4 Alternate Target Impedance Configurations

Within specific end-use applications for TI's hardware emulation products, multiple printed circuit board (PCB) trace impedances may be required. The advanced emulation signals connecting to the emulation header require a  $50-\Omega$  trace impedance for optimal performance.

For additional information on DSP target applications that incorporate alternate interfaces including, but not limited to, PCI or external memory interfaces (EMIF), see Appendix A.

#### **Table 4. Summary: Alternate Target Impedance Configurations**

| 1 | Target boards without special considerations must be designed for a 50- $\Omega$ character impedance.                                                     |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | All header EMU signals must be routed as if they are clock signal lines operating at 200 MHz. TI recommends designing JTAG signals for 100-MHz operation. |

|   |                                                                                                                                                           |

Header Information www.ti.com

#### 5 Header Information

Table 5, Table 6, and Table 7 summarize the header information. For specific pin assignments, see Section 8.

Table 5. Summary: TI 60-Pin Header Information

| 1 | Connector Manufacturer is Samtec USA.                                                                                                                                                                                |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Table 7. Summary: TI 20-Pin CTI Header Information                                                                                                                                                                   |

| 5 | Connector Footprint Drawing is located at URL <a href="http://www.samtec.com/ftppub/cpdf/QSH-XXX-01-X-DXX-FOOTPRINT.pdf">http://www.samtec.com/ftppub/cpdf/QSH-XXX-01-X-DXX-FOOTPRINT.pdf</a> .                      |

| 4 | Connector Drawing is located at URL <a href="http://www.samtec.com/ftppub/cpdf/QSH-XXX-01-X-D-XXX-MKT.pdf">http://www.samtec.com/ftppub/cpdf/QSH-XXX-01-X-D-XXX-MKT.pdf</a> .                                        |

| 3 | Connector Specification Overview is located at URL <a href="http://www.samtec.com/technical_specifications/overview.aspx?series=QSH">http://www.samtec.com/technical_specifications/overview.aspx?series=QSH</a> .   |

| 2 | Connector Model Number is QSH030.                                                                                                                                                                                    |

| 1 | Connector Manufacturer is Samtec USA.                                                                                                                                                                                |

|   | Table 6. Summary: MIPI 60-Pin Header Information                                                                                                                                                                     |

| 5 | Connector Footprint Drawing is located at URL <a href="http://www.samtec.com/ftppub/cpdf/SOLC.PDF">http://www.samtec.com/ftppub/cpdf/SOLC.PDF</a>                                                                    |

| 4 | Connector Drawing is located at URL <a href="http://www.samtec.com/ftppub/cpdf/SOLC-MKT.PDF">http://www.samtec.com/ftppub/cpdf/SOLC-MKT.PDF</a>                                                                      |

| 3 | Connector Specification Overview is located at URL <a href="http://www.samtec.com/technical_specifications/overview.aspx?series=SOLC">http://www.samtec.com/technical_specifications/overview.aspx?series=SOLC</a> . |

| 2 | Connector Model Number is SOLC-115-02-S-Q-P.                                                                                                                                                                         |

| • | Connector Manufacturer is Samtec USA.                                                                                                                                                                                |

| <br>- |                                                                                                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5     | Connector Footprint Drawing is located at URL http://www.samtec.com/ftppub/cpdf/FTR-D.PDF.                                                                                                                         |

| 4     | Connector Drawing is located at URL <a href="http://www.samtec.com/ftppub/cpdf/FTR-MKT.PDF">http://www.samtec.com/ftppub/cpdf/FTR-MKT.PDF</a> .                                                                    |

| 3     | Connector Specification Overview is located at URL <a href="http://www.samtec.com/technical_specifications/overview.aspx?series=FTR">http://www.samtec.com/technical_specifications/overview.aspx?series=FTR</a> . |

| 2     | Connector Model Number is FTR-110-51-S-D-06.                                                                                                                                                                       |

| 1     | Connector Manufacturer is Samtec USA.                                                                                                                                                                              |

#### 6 Header Footprint Comparisons

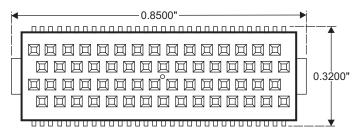

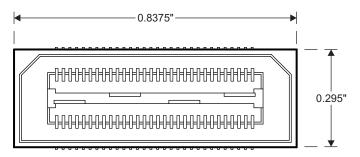

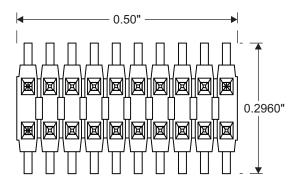

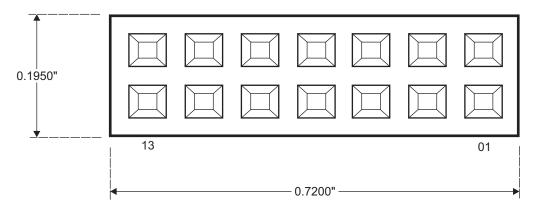

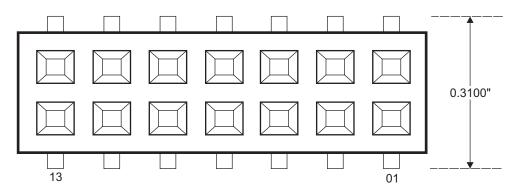

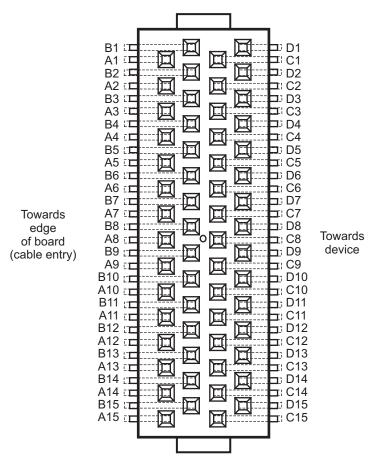

Figure 1 through Figure 3 show TI target connector footprint drawings and Table 8 shows a comparison of the board space required for each connector type.

In this case, dimensions include space required for the target cable mating connector.

Figure 1. TI 60-Pin Emulation Header

Figure 2. MIPI 60-Pin Header

Figure 3. TI 20-Pin CTI Header

Figure 4. TI 14-Pin Traditional Through-Hole Emulation Interface

Figure 5. TI 14-Pin Traditional SMT Emulation Interface Header

Target Mating Caution www.ti.com

| Table 8. Summary | v: Header | Footprint | Comparisons |

|------------------|-----------|-----------|-------------|

|                  |           |           |             |

|   | Common Emulation Interfaces                           | Area (in square inches) | Notes                      |

|---|-------------------------------------------------------|-------------------------|----------------------------|

| 1 | TI 60-pin                                             | 0.2720 in <sup>2</sup>  | Includes mounting pads     |

| 2 | MIPI 60-pin                                           | 0.2471 in <sup>2</sup>  | Includes mounting pads     |

| 3 | TI 20-pin CTI                                         | 0.148 in <sup>2</sup>   | Includes mounting pads     |

| 4 | 20-pin ARM ETM header                                 | 0.3451 in <sup>2</sup>  | Includes mounting pads     |

| 5 | Original through-hole TI 14-pin connector form factor | 0.2808 in <sup>2</sup>  | Includes both sides of PCB |

| 6 | Original TI 14-pin SMT connector form factor          | 0.2431 in <sup>2</sup>  | Includes mounting pads     |

#### 7 **Target Mating Caution**

NOTE: All headers (emulator and target) should be examined for possible damage before being mated together. Damaged or bent pins may affect functionality and performance.

Never apply excessive force when mating connectors; if excessive force is required, the mating connector pairs are not aligned.

#### **Table 9. Summary: Header Changes**

| 1 | Verify the target and emulator headers are intact and free of defects before mating. |

|---|--------------------------------------------------------------------------------------|

| 2 | Always use caution when mating connectors to ensure no damage occurs.                |

| 3 | Verify connectors are parallel to one another before mating.                         |

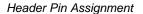

#### **Header Pin Assignment** 8

Table 10. TI 60-Pin Header Signal Naming Convention

| Pin<br>No. | Signal<br>Name       | Emulator<br>Signal<br>Direction | Notes                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|----------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1         | GND                  | -                               | May be used for cable detect per Appendix C.                                                                                                                                                                                                                                                                                                                                                            |

| A2         | GND                  | -                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A3         | GND                  | -                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A4         | GND                  | -                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A5         | GND                  | -                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A6         | GND                  | -                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A7         | GND                  | -                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A8         | TYPE0 <sup>(1)</sup> | Input                           | Type 0 is a No Connect.                                                                                                                                                                                                                                                                                                                                                                                 |

| A9         | GND                  | =                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A10        | GND                  | -                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A11        | GND                  | -                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A12        | GND                  | -                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A13        | GND                  | -                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A14        | GND                  | =                               | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| A15        | TGTRST               | Output                          | Even though the native TI 60-pin emulator (XDS560T) does not support the target reset function, other emulators, such as the XDS560 with the REV D cable do support this function. For compatibility, typically through the use of adapters, with emulators that support the target reset function it is recommended that on your target board this pin be pulled up with a $4.7$ -K $\Omega$ resistor. |

The TYPE pins are XDS inputs used to sense connector orientation. In the XDS, they are both pulled up and when you connect the XDS to the target, it is expected the TYPE1 pin is grounded by the target and TYPE0 pin is open if it is connected with the correct orientation. Therefore, TYPE1 (D8) should be connected directly to GND on the target.

#### Table 10. TI 60-Pin Header Signal Naming Convention (continued)

|            |                      |                                 | ou-Fin Header Signal Naming Convention (Continued)                                                                                                                                                        |  |

|------------|----------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin<br>No. | Signal<br>Name       | Emulator<br>Signal<br>Direction | Notes                                                                                                                                                                                                     |  |

| B1         | ID0                  | Input                           | Only header type 0000 is currently supported, where 0 is GND and 1 is a No Connect. All other combinations are reserved.                                                                                  |  |

| B2         | TMS                  | Output                          | Connect to device pin of same name.                                                                                                                                                                       |  |

| В3         | EMU17 <sup>(2)</sup> | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| B4         | TDI                  | Output                          | Connect to device pin of same name.                                                                                                                                                                       |  |

| B5         | EMU14 <sup>(2)</sup> | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| B6         | EMU12 <sup>(2)</sup> | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| B7         | TDO                  | Input                           | Connect to device pin of same name.                                                                                                                                                                       |  |

| B8         | TVD                  | Input                           | Chip I/O voltage current limited via 100- $\Omega$ resistor.                                                                                                                                              |  |

| B9         | EMU9 <sup>(2)</sup>  | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| B10        | EMU7 <sup>(2)</sup>  | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| B11        | EMU5 <sup>(2)</sup>  | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| B12        | TCK                  | Output                          | Connect to device pin of same name; may need to be buffered.                                                                                                                                              |  |

| B13        | EMU2 <sup>(2)</sup>  | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| B14        | EMU0 <sup>(2)</sup>  | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| B15        | ID1                  | Input                           | Only header type 0000 is currently supported, where 0 is GND and 1 is a No Connect. All other combinations are reserved.                                                                                  |  |

| C1         | ID2                  | Input                           | Only header type 0000 is currently supported, where 0 is GND and 1 is a No Connect. All other combinations are reserved.                                                                                  |  |

| C2         | EMU18 <sup>(2)</sup> | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C3         | TRST                 | Output                          | Connect to device pin of same name.                                                                                                                                                                       |  |

| C4         | EMU16 <sup>(2)</sup> | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C5         | EMU15 <sup>(2)</sup> | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C6         | EMU13 <sup>(2)</sup> | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C7         | EMU11 <sup>(2)</sup> | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C8         | TCKRTN               | Input                           | Connect to either a loopback of the emulation header's TCK or a target device-supplied RTCK. If your target device has an RTCK signal, you must connect this signal to TCKRTN on the emulator header. (3) |  |

| C9         | EMU10 <sup>(2)</sup> | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C10        | EMU8 <sup>(2)</sup>  | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C11        | EMU6 <sup>(2)</sup>  | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C12        | EMU4 <sup>(2)</sup>  | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C13        | EMU3 <sup>(2)</sup>  | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C14        | EMU1 <sup>(2)</sup>  | Bidirectional                   | Connect to device pin of same name.                                                                                                                                                                       |  |

| C15        | ID3                  | Input                           | Only header type 0000 is currently supported, where 0 is GND and 1 is a No Connect. All other combinations are reserved.                                                                                  |  |

| D1         | NC                   | -                               | Not connected.                                                                                                                                                                                            |  |

| D2         | GND                  | =                               | Ground pin.                                                                                                                                                                                               |  |

| D3         | GND                  | -                               | Ground pin.                                                                                                                                                                                               |  |

| D4         | GND                  | -                               | Ground pin.                                                                                                                                                                                               |  |

| D5         | GND                  | -                               | Ground pin.                                                                                                                                                                                               |  |

| D6         | GND                  | -                               | Ground pin.                                                                                                                                                                                               |  |

| D7         | GND                  | -                               | Ground pin.                                                                                                                                                                                               |  |

| D8         | TYPE1 <sup>(1)</sup> | Input                           | Type 1 must be connected to GND.                                                                                                                                                                          |  |

| D9         | GND                  | -                               | Ground pin.                                                                                                                                                                                               |  |

| D10        | GND                  | -                               | Ground pin.                                                                                                                                                                                               |  |

<sup>(2)</sup> The 60-pin header provides 19 EMU pins for advance emulation features. Not all devices support 19 EMU pins. Connect only the EMU pins present on the target DSP to the corresponding EMU pin on the header. Leave unused pins unconnected.

<sup>(3)</sup> For additional notes, see Table 14.

Header Pin Assignment www.ti.com

| Pin<br>No. | Signal<br>Name | Emulator<br>Signal<br>Direction | Notes       |

|------------|----------------|---------------------------------|-------------|

| D11        | GND            | -                               | Ground pin. |

| D12        | GND            | -                               | Ground pin. |

| D13        | GND            | -                               | Ground pin. |

| D14        | GND            | -                               | Ground pin. |

| D15        | GND            | -                               | Ground pin. |

#### Table 11. Summary: TI 60-Pin Header Pinout

| 1 | Pin D1 should be left unconnected.                                         |

|---|----------------------------------------------------------------------------|

| 2 | Pin A1, if required, enables or disables external multiplexers or buffers. |

| 3 | Only the appropriate trace pins should be connected.                       |

The MIPI 60-pin header provides for up to four channels of independently clocked trace data, where the first channel of data can span up to 40 bits, the second channel can span up to 20 bits, and the third and forth channels can span up to 10 bits each. By overlaying the channel bit mapping, multiple configurations are provided such as four 10-bit ports, two 20-bit ports, or a 32-bit port and an 8-bit port. Current trace capture products only support capture of trace data on port 0. We recommend connecting all the EMU pins provided by your device to the MIPI 60-pin connector per Table 12. Future trace capture products may support additional ports and pin mappings, so always check the latest revision of this document before starting a new design using the MIPI 60-pin header.

The MIPI 60-pin connector also provides two level-dependent nTRST signals and trace and JTAG independent voltage references.

Note that not all TI devices use the EMU pin naming convention for designating trace pins. Devices that export only an ARM ETM trace port have a trace clock, trace control, and trace data pins. Typical pin designators are ETK\_NAME and ETMNAME (where NAME is some variation of CLK, CNTL, and DATA). When connecting an ARM ETM port to the MIPI connector, trace clock is connected to TRC\_CLK[0], trace control is connected to TRC\_DATA[0][0], and trace data is connected to TRC\_DATA[0][1] to TRC\_DATA[0][n]. If your device has a *trace clock-in pin*, leave it disconnected or pull it up externally to increase noise immunity over the internal pull-up. Check with your emulator manufacturer on availability of ARM ETM trace support.

Table 12. MIPI 60-Pin Header Signal Naming Convention (1)(2)(3)

| Pin No. | MIPI Name  | Device Signal Name       | Notes                                                                |

|---------|------------|--------------------------|----------------------------------------------------------------------|

| 1       | VREF_DEBUG | JTAG IO V <sub>ref</sub> | JTAG IO voltage reference current limited via $100-\Omega$ resistor. |

| 2       | TMS/TMSC   | TMS                      |                                                                      |

| 3       | TCK        | TCK                      | May need to be buffered.                                             |

| 4       | TDO/EXTA   | TDO                      |                                                                      |

| 5       | TDI/EXTB   | TDI                      |                                                                      |

| 6       | nRESET     | Connect to system reset  | Open drain output from emulator; use 4.7-KΩ PU. <sup>(3)</sup>       |

<sup>(1)</sup> The QSH-030 connector also has an additional 4 pins (61, 62, 63 and 64) used to connect the cable's ground shield to the target boards ground plane.

<sup>(2)</sup> Leave unused TRC\_DATA and TRC\_CLK pins unconnected.

<sup>(3)</sup> For additional notes, see Table 14.

Table 12. MIPI 60-Pin Header Signal Naming Convention(1)(2)(3) (continued)

| Pin No. | MIPI Name                         | Device Signal Name               | Notes                                                                                                                                                                                                                                                                            |

|---------|-----------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7       | RTCK/EXTC                         | RTCK                             | Connect to either a loopback of<br>the emulation header's TCK or a<br>target device-supplied RTCK. If<br>your target device has an RTCK<br>signal, you must connect this<br>signal to RTCK on the emulator<br>header. (3)                                                        |

| 8       | nTRST_PD                          | nTRST                            | It is expected that this pin be connected only to devices with internal PDs on their nTRST pins, or in cases where a PD is required externally on the device's nTRST pin (for PD information and requirements, see your device's data sheet). (4)                                |

| 9       | nTRST/EXTD                        | nTRST                            | nTRST is an open drain output. It is expected that this pin be connected only to devices with internal PUs on their nTRST pins, or in cases where a PU is required externally on the device's nTRST pin (for PU information and requirements, see your device's data sheet). (4) |

| 10      | EXTE/TRIGIN                       | NC                               |                                                                                                                                                                                                                                                                                  |

| 11      | EXTF/TRIGOUT                      | NC                               |                                                                                                                                                                                                                                                                                  |

| 12      | VREF_TRACE                        | EMU IO Vref                      | EMU IO voltage reference current limited via $100-\Omega$ resistor.                                                                                                                                                                                                              |

| 13      | TRC_CLK[0]                        | EMU2                             |                                                                                                                                                                                                                                                                                  |

| 14      | TRC_CLK[1]                        | NC                               |                                                                                                                                                                                                                                                                                  |

| 15      | Target Presence Detect            | Connected to GND thru 0 $\Omega$ |                                                                                                                                                                                                                                                                                  |

| 16      | GND                               | GND                              |                                                                                                                                                                                                                                                                                  |

| 17      | TRC_DATA[0][0]                    | EMU3                             |                                                                                                                                                                                                                                                                                  |

| 18      | TRC_DATA[1][0] or TRC_DATA[0][20] | EMU21                            |                                                                                                                                                                                                                                                                                  |

| 19      | TRC_DATA[0][1]                    | EMU0                             |                                                                                                                                                                                                                                                                                  |

| 20      | TRC_DATA[1][1] or TRC_DATA[0][21] | EMU22                            |                                                                                                                                                                                                                                                                                  |

| 21      | TRC_DATA[0][2]                    | EMU1                             |                                                                                                                                                                                                                                                                                  |

| 22      | TRC_DATA[1][2] or TRC_DATA[0][22] | EMU23                            |                                                                                                                                                                                                                                                                                  |

| 23      | TRC_DATA[0][3]                    | EMU4                             |                                                                                                                                                                                                                                                                                  |

| 24      | TRC_DATA[1][3] or TRC_DATA[0][23] | EMU24                            |                                                                                                                                                                                                                                                                                  |

| 25      | TRC_DATA[0][4]                    | EMU5                             |                                                                                                                                                                                                                                                                                  |

| 26      | TRC_DATA[1][4] or TRC_DATA[0][24] | EMU25                            |                                                                                                                                                                                                                                                                                  |

| 27      | TRC_DATA[0][5]                    | EMU6                             |                                                                                                                                                                                                                                                                                  |

| 28      | TRC_DATA[1][5] or TRC_DATA[0][25] | EMU26                            |                                                                                                                                                                                                                                                                                  |

| 29      | TRC_DATA[0][6]                    | EMU7                             |                                                                                                                                                                                                                                                                                  |

| 30      | TRC_DATA[1][6] or TRC_DATA[0][26] | EMU27                            |                                                                                                                                                                                                                                                                                  |

| 31      | TRC_DATA[0][7]                    | EMU8                             |                                                                                                                                                                                                                                                                                  |

| 32      | TRC_DATA[1][7] or TRC_DATA[0][27] | EMU28                            |                                                                                                                                                                                                                                                                                  |

| 33      | TRC_DATA[0][8]                    | EMU9                             |                                                                                                                                                                                                                                                                                  |

| 34      | TRC_DATA[1][8] or TRC_DATA[0][28] | EMU29                            |                                                                                                                                                                                                                                                                                  |

| 35      | TRC_DATA[0][9]                    | EMU10                            |                                                                                                                                                                                                                                                                                  |

<sup>&</sup>lt;sup>(4)</sup> A device's nTRST pin may be connected to either nTRST\_PD or nTRST/EXTD, not both at the same time. Also, the XDS Pro Trace only drives the nTRST\_PD pin, and not the nTRST/EXTD pin. In the case where you have connected the device's nTRST pin to the MIPI 60-pin connector's nTRST/EXTD pin and you are using the XDS Pro Trace, an adapter is required.

Header Pin Assignment www.ti.com

Table 12. MIPI 60-Pin Header Signal Naming Convention(1)(2)(3) (continued)

| Pin No. | MIPI Name                                            | Device Signal Name | Notes                                        |

|---------|------------------------------------------------------|--------------------|----------------------------------------------|

| 36      | TRC_DATA[1][9] or TRC_DATA[0][29]                    | EMU30              |                                              |

| 37      | TRC_DATA[3][0] or TRC_DATA[0][10]                    | EMU11              |                                              |

| 38      | TRC_DATA[2][0] or TRC_DATA[1][10] or TRC_DATA[0][30] | EMU31              |                                              |

| 39      | TRC_DATA[3][1] or TRC_DATA[0][11]                    | EMU12              |                                              |

| 40      | TRC_DATA[2][1] or TRC_DATA[1][11] or TRC_DATA[0][31] | EMU32              |                                              |

| 41      | TRC_DATA[3][2] or TRC_DATA[0][12]                    | EMU13              |                                              |

| 42      | TRC_DATA[2][2] or TRC_DATA[1][12] or TRC_DATA[0][32] | EMU33              |                                              |

| 43      | TRC_DATA[3][3] or TRC_DATA[0][13]                    | EMU14              |                                              |

| 44      | TRC_DATA[2][3] or TRC_DATA[1][13] or TRC_DATA[0][33] | NC                 |                                              |

| 45      | TRC_DATA[3][4] or TRC_DATA[0][14]                    | EMU15              |                                              |

| 46      | TRC_DATA[2][4] or TRC_DATA[1][14] or TRC_DATA[0][34] | NC                 |                                              |

| 47      | TRC_DATA[3][5] or TRC_DATA[0][15]                    | EMU16              |                                              |

| 48      | TRC_DATA[2][5] or TRC_DATA[1][15] or TRC_DATA[0][35] | NC                 |                                              |

| 49      | TRC_DATA[3][6] or TRC_DATA[0][16]                    | EMU17              |                                              |

| 50      | TRC_DATA[2][6] or TRC_DATA[1][16] or TRC_DATA[0][36] | NC                 |                                              |

| 51      | TRC_DATA[3][7] or TRC_DATA[0][17]                    | EMU18              |                                              |

| 52      | TRC_DATA[2][7] or TRC_DATA[1][17] or TRC_DATA[0][37] | NC                 |                                              |

| 53      | TRC_DATA[3][8] or TRC_DATA[0][18]                    | EMU19              |                                              |

| 54      | TRC_DATA[2][8] or TRC_DATA[1][18] or TRC_DATA[0][38] | NC                 |                                              |

| 55      | TRC_DATA[3][9] or TRC_DATA[0][19]                    | EMU20              |                                              |

| 56      | TRC_DATA[2][9] or TRC_DATA[1][19] or TRC_DATA[0][39] | NC                 |                                              |

| 57      | GND                                                  | GND                | Must be directly tied to GND.                |

| 58      | GND                                                  | GND                | May be used for cable detect per Appendix C. |

| 59      | TRC_CLK[3]                                           | NC                 |                                              |

| 60      | TRC_CLK[2]                                           | NC                 |                                              |

|         | ,                                                    |                    |                                              |

Table 13. TI 20-Pin CTI Header Signal Naming Convention

| Pin No. | Signal Name         | Notes                                                                         |

|---------|---------------------|-------------------------------------------------------------------------------|

| 1       | TMS                 |                                                                               |

| 2       | TRST                |                                                                               |

| 3       | TDI                 |                                                                               |

| 4       | TDIS <sup>(1)</sup> | Connect to target GND.                                                        |

| 5       | VTRef               | JTAG and EMU IO voltage reference current limited via 100- $\Omega$ resistor. |

| 6       | KEY                 | This pin may need to be cut to mate with the emulator's target cable.         |

| 7       | TDO                 |                                                                               |

| 8       | GND                 | May be used for cable detect per Appendix C.                                  |

| -       |                     |                                                                               |

A pulldown or current-limiting resistor on TDIS will not work with all XDS models. With TDIS connected directly to GND, some XDS models will sink a small amount of current (by design) through a pullup in the XDS. A pulldown or a current-limiting resistor connected to TDIS on the target may cause the XDS to not detect the target and result in a "far cable break" error.

## Table 13. TI 20-Pin CTI Header Signal Naming Convention (continued)

| Pin No. | Signal Name | Notes                                                                                                                                                                                                   |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9       | RTCK        | Connect to either a loopback of the emulation header's TCK or a target device-supplied RTCK. If your target device has an RTCK signal, you must connect this signal to RTCK on the emulator header. (2) |

| 10      | GND         |                                                                                                                                                                                                         |

| 11      | TCK         | May need to be buffered.                                                                                                                                                                                |

| 12      | GND         |                                                                                                                                                                                                         |

| 13      | EMU0        |                                                                                                                                                                                                         |

| 14      | EMU1        |                                                                                                                                                                                                         |

| 15      | RESET       | Open drain output from emulator, use 4.7-KΩ PU. (2)                                                                                                                                                     |

| 16      | GND         |                                                                                                                                                                                                         |

| 17      | EMU2        |                                                                                                                                                                                                         |

| 18      | EMU3        |                                                                                                                                                                                                         |

| 19      | EMU4        |                                                                                                                                                                                                         |

| 20      | GND         |                                                                                                                                                                                                         |

For additional notes, see Table 14.

Header Pin Assignment www.ti.com

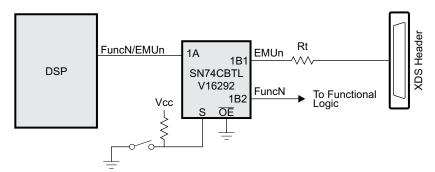

| 1 | EMU0 and EMU1 should always be treated as bidirectional signals. For bidirectional debug port functions, check your device data sheet. Other EMU pins may also be bidirectional, but typically they are used for unidirectional core and system trace export.                                                                                                                       |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

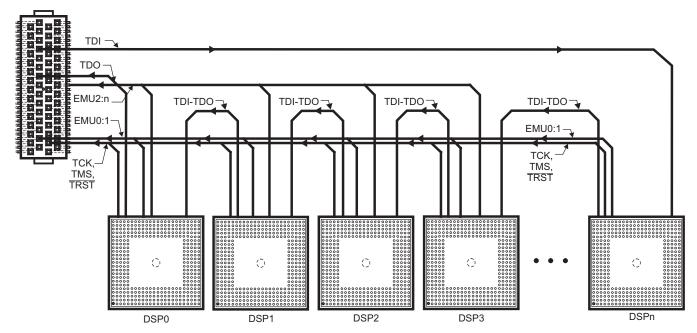

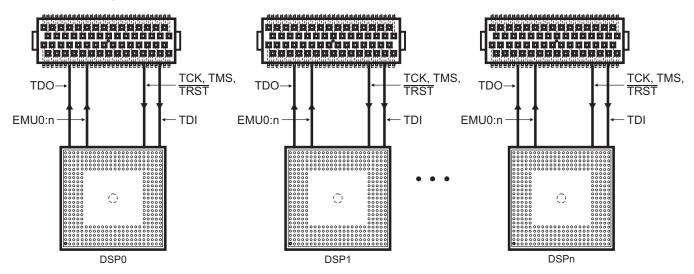

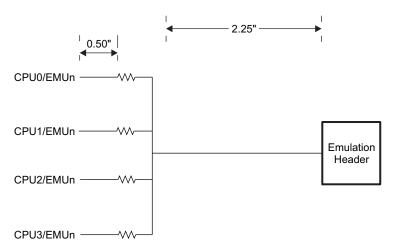

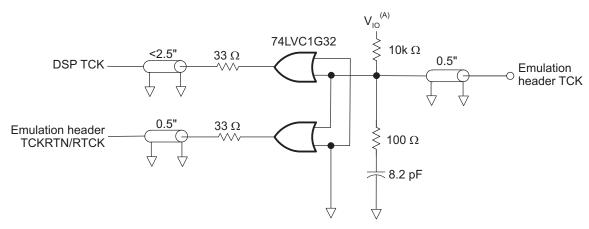

| 2 | If your target card contains multiple devices with RTCK pins see the <i>Adaptive Clock</i> article at <a href="http://tiexpressdsp.com/index.php/Adaptive_Clocking">http://tiexpressdsp.com/index.php/Adaptive_Clocking</a> .                                                                                                                                                       |