## TMS320x281x DSP System Control and Interrupts Reference Guide

Literature Number: SPRU078G April 2002 – Revised August 2012

### Preface

## **Read This First**

#### About This Manual

This guide describes how various 281x digital signal processor (DSP) system controls and interrupts work with peripherals. It includes information on the:

- □ Flash and one-time programmable (OTP) memories

- Code security module (CSM), which is a security feature incorporated in 28x devices

- Clocking mechanisms including the oscillator, PLL, the watchdog function, and the low-power modes

- GPIO MUX registers used to select the operation of shared pins

- Peripheral frames and the device emulation registers

- Peripheral interrupt expansion (PIE) block that multiplexes numerous interrupt sources into a smaller set of interrupt inputs

#### **Related Documentation From Texas Instruments**

The following books describe the TMS320x281x and related support tools that are available on the TI website.

- TMS320F2810, TMS320F2811, TMS320F2812, TMS320C2810, TMS320C2811, and TMS320C2812 Digital Signal Processors (literature number SPRS174) data sheet contains the electrical and timing specifications for these devices, as well as signal descriptions and pinouts for all of the available packages.

- **TMS320R2811 and TMS320R2812 Digital Signal Processors** (literature number SPRS257) data sheet contains the electrical and timing specifications for these devices, as well as signal descriptions and pinouts for all of the available packages.

- **TMS320C28x DSP CPU and Instruction Set Reference Guide** (literature number SPRU430) describes the central processing unit (CPU) and the assembly language instructions of the TMS320C28x<sup>™</sup> fixed-point digital signal processors (DSPs). It also describes emulation features available on these DSPs.

- **TMS320x281x Analog-to-Digital Converter (ADC) Reference Guide** (literature number SPRU060) describes the ADC module. The module is a 12-bit pipelined ADC. The analog circuits of this converter, referred to as the core in this document, include the front-end analog multiplexers (MUXs), sample-and-hold (S/H) circuits, the conversion core, voltage regulators, and other analog supporting circuits. Digital circuits, referred to as the wrapper in this document, include programmable conversion sequencer, result registers, interface to analog circuits, interface to device peripheral bus, and interface to other on-chip modules.

- **TMS320x281x Boot ROM Reference Guide** (literature number SPRU095) describes the purpose and features of the bootloader (factory-programmed boot-loading software). It also describes other contents of the device on-chip boot ROM and identifies where all of the information is located within that memory.

- TMS320x281x Event Manager (EV) Reference Guide (literature number SPRU065) describes the EV modules that provide a broad range of functions and features that are particularly useful in motion control and motor control applications. The EV modules include general-purpose (GP) timers, full-compare/PWM units, capture units, and quadrature-encoder pulse (QEP) circuits.

- TMS320x281x External Interface (XINTF) Reference Guide (literature number SPRU067) describes the external interface (XINTF) of the 28x digital signal processors (DSPs).

- *TMS320x281x Multi-channel Buffered Serial Ports (McBSPs) Reference Guide* (literature number SPRU061) describes the McBSP) available on the C28x devices. The McBSPs allow direct interface between a DSP and other devices in a system.

- TMS320x28xx, 28xxx Enhanced Controller Area Network (eCAN) Reference Guide (literature number SPRU074) describes the eCAN that uses established protocol to communicate serially with other controllers in electrically noisy environments. With 32 fully configurable mailboxes and time-stamping feature, the eCAN module provides a versatile and robust serial communication interface. The eCAN module implemented in the C28x DSP is compatible with the CAN 2.0B standard (active).

- *TMS320x28xx, 28xxx Peripheral Reference Guide* (literature number SPRU566) describes the peripheral reference guides of the 28x digital signal processors (DSPs).

- TMS320x28xx, 28xxx Serial Communication Interface (SCI) Reference Guide (literature number SPRU051) describes the SCI that is a two-wire

asynchronous serial port, commonly known as a UART. The SCI modules support digital communications between the CPU and other asynchronous peripherals that use the standard non-return-to-zero (NRZ) format.

- TMS320x28xx, 280xxx Serial Peripheral Interface (SPI) Reference Guide (literature number SPRU059) describes the SPI – a high-speed synchronous serial input/output (I/O) port that allows a serial bit stream of programmed length (one to sixteen bits) to be shifted into and out of the device at a programmed bit-transfer rate. The SPI is used for communications between the DSP controller and external peripherals or another controller.

- The TMS320C28x Instruction Set Simulator Technical Overview (literature number SPRU608) describes the simulator, available within the Code Composer Studio for TMS320C2000 IDE, that simulates the instruction set of the C28x core.

- TMS320C28x DSP/BIOS Application Programming Interface (API) Reference Guide (literature number SPRU625) describes development using DSP/BIOS.

- **3.3 V DSP for Digital Motor Control Application Report** (literature number SPRA550) describes a scenario of a 3.3-V-only motor controller indicating that for most applications, no significant issue of interfacing between 3.3 V and 5 V exists. On-chip 3.3-V analog-to-digital converter (ADC) versus 5-V ADC is also discussed. Guidelines for component layout and printed circuit board (PCB) design that can reduce system noise and EMI effects are summarized.

- Thermo-Electric Cooler Control Using a TMS320F2812 DSP & DRV592 (literature number SPRA873) presents a thermoelectric cooler system consisting of a Texas Instruments TMS320F2812 digital signal processor (DSP) and DRV592 power amplifier. The DSP implements a digital proportional-integral-derivative feedback controller using an integrated 12-bit analog-to-digital converter to read the thermistor, and direct output of pulse-width-modulated waveforms to the H-bridge DRV592 power amplifier. A complete description of the experimental system, along with software and software operating instructions, is provided.

#### Running an Application from Internal Flash Memory on the TMS320F281x DSP Application Report (literature number SPRA958) covers the requirements needed to properly configure application software for execution from on-chip flash memory. Requirements for both DSP/BIOS and non-DSP/BIOS projects are presented. Example code projects are included.

v

#### Trademarks

Code Composer Studio and C28x are trademarks of Texas Instruments.

## Contents

| Mem   | ory 1                                                                     | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | •                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.1   | Flash and OTP Memory 1                                                    | -2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 1.1.1 Flash Memory                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | 1.1.2 OTP Memory                                                          | -2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.2   | Flash and OTP Power Modes 1                                               | 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 1.2.1 Flash and OTP Performance 1                                         | 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 1.2.2 28x Flash Pipeline Mode 1                                           | 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 1.2.3 Procedure to Change the Flash Configuration Registers 1             | -8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.3   | Flash and OTP Registers    1                                              | 1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Code  | e Security Module (CSM) 2                                                 | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Desci | ribes clocking and system control.                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.1   | Functional Description                                                    | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2   | CSM Impact on Other On-Chip Resources 2                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.3   | Incorporating Code Security in User Applications                          | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 2.3.1 Environments That Require Security Unlocking                        | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

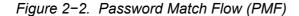

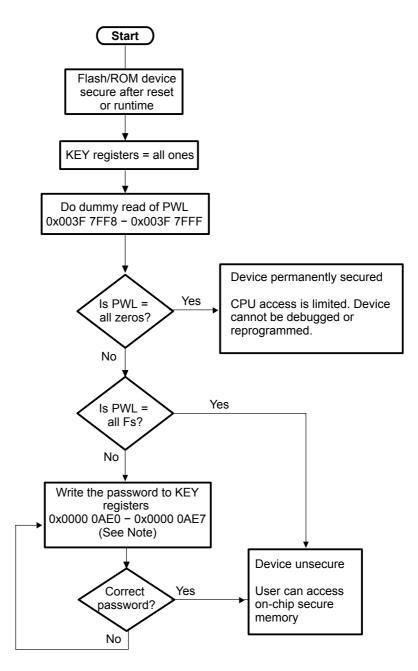

|       | 2.3.2 Password Match Flow 2                                               | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 2.3.3 Unsecuring Considerations for Devices With/Without Code Security 2- | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.3.4 C Code Example to Unsecure 2-                                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.3.5 C Code Example to Resecure 2-                                       | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.4   | DOs and DON'Ts to Protect Security Logic 2-                               | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.4.1 DOs                                                                 | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 2.4.2 DON'Ts                                                              | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2.5   | CSM Features – Summary 2-                                                 | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | Desc<br>1.1<br>1.2<br>1.3<br>Code<br>Desc<br>2.1<br>2.2<br>2.3            | 1.1.1       Flash Memory       1         1.2       OTP Memory       1         1.2       Flash and OTP Power Modes       1         1.2.1       Flash and OTP Performance       1         1.2.2       28x Flash Pipeline Mode       1         1.2.3       Procedure to Change the Flash Configuration Registers       1         1.3       Flash and OTP Registers       1         Code Security Module (CSM)       2         Describes clocking and system control.       2         2.1       Functional Description       2         2.2       CSM Impact on Other On-Chip Resources       2         2.3       Incorporating Code Security in User Applications       2         2.3.1       Environments That Require Security Unlocking       2         2.3.2       Password Match Flow       2         2.3.3       Unsecuring Considerations for Devices With/Without Code Security       2         2.3.4       C Code Example to Unsecure       2         2.3.5       C Code Example to Resecure       2         2.4       DOS and DON'Ts to Protect Security Logic       2         2.4.2       DON'Ts       2 |

#### Contents

| 3 | Clock                        | king                                             |                                                                                                                        | 3-1                       |

|---|------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------|

|   |                              | -                                                | ocking and system control.                                                                                             |                           |

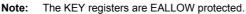

|   | 3.1                          | Clocki                                           | ng and System Control                                                                                                  |                           |

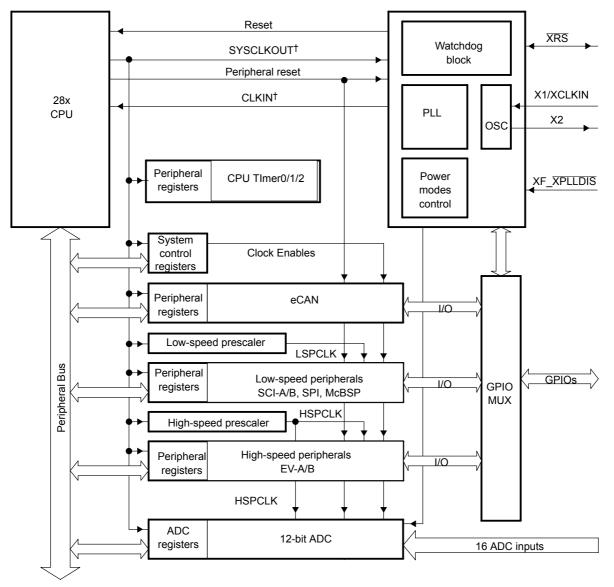

|   | 3.2                          |                                                  | and PLL Block                                                                                                          |                           |

|   |                              | 3.2.1                                            | PLL-Based Clock Module                                                                                                 | 3-7                       |

|   |                              | 3.2.2                                            | External Reference Oscillator Clock Option                                                                             | 3-9                       |

|   | 3.3                          | Low-P                                            | ower Modes Block                                                                                                       | 3-10                      |

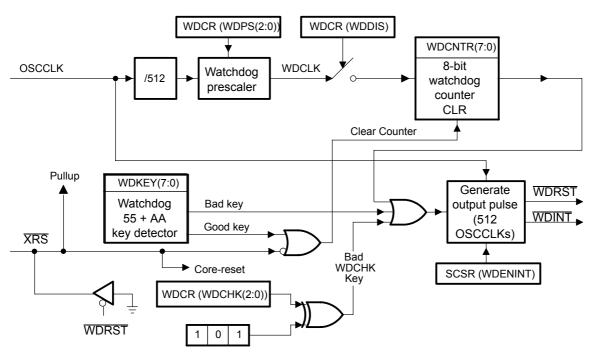

|   | 3.4                          | Watch                                            | dog Block                                                                                                              | 3-14                      |

|   |                              | 3.4.1                                            | Servicing the Watchdog Timer                                                                                           |                           |

|   |                              | 3.4.2                                            | Watchdog Reset or Watchdog Interrupt Mode                                                                              | 3-16                      |

|   |                              | 3.4.3                                            | Watchdog Operation in Low Power Modes                                                                                  | 3-16                      |

|   |                              | 3.4.4                                            | Emulation Considerations                                                                                               | 3-17                      |

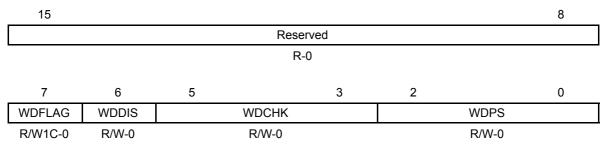

|   |                              | 3.4.5                                            | Watchdog Registers                                                                                                     | 3-17                      |

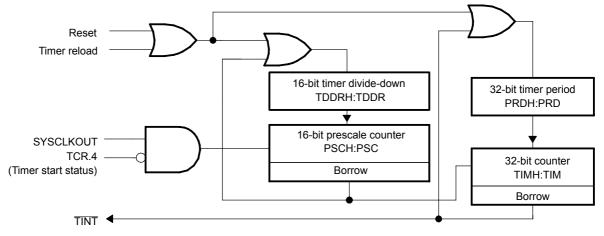

|   | 3.5                          | 32-Bit                                           | CPU Timers 0/1/2                                                                                                       | 3-21                      |

| 4 | Gene                         | ral-Pur                                          | pose Input/Output (GPIO)                                                                                               | 4-1                       |

|   |                              |                                                  | PIO shared pins and operation selection.                                                                               |                           |

|   | 4.1                          |                                                  | MUX                                                                                                                    | 4-2                       |

|   | 4.2                          |                                                  | Qualification                                                                                                          |                           |

|   | 4.3                          |                                                  | er Functional Overview                                                                                                 |                           |

|   |                              | 4.3.1                                            | GPxMUX Registers                                                                                                       |                           |

|   |                              | 4.3.2                                            | GPxDIR Registers                                                                                                       |                           |

|   |                              | 4.3.3                                            | GPxDAT Registers                                                                                                       |                           |

|   |                              | 4.3.4                                            | GPxSET Registers                                                                                                       |                           |

|   |                              | 4.3.5                                            | GPxCLEAR Registers                                                                                                     |                           |

|   |                              | 400                                              | GPxTOGGLE Registers                                                                                                    |                           |

|   |                              | 4.3.6                                            |                                                                                                                        |                           |

| _ | 4.4                          |                                                  | er Bit to I/O Mapping                                                                                                  |                           |

| 5 |                              | Regist                                           | er Bit to I/O Mapping                                                                                                  | 4-11                      |

| 5 | Perip                        | Regist                                           | -                                                                                                                      | 4-11                      |

| 5 | Perip                        | Regist<br>heral F<br>ribes ho                    | rames                                                                                                                  | 4-11<br><b>5-1</b>        |

| 5 | <b>Perip</b><br>Desc         | Regist<br>heral F<br>ribes ho<br>Periph          | rer Bit to I/O Mapping         rames         w to configure 28x systems for peripherals.         peral Frame Registers | 4-11<br><b>5-1</b><br>5-2 |

| 5 | <b>Perip</b><br>Desci<br>5.1 | Regist<br>heral F<br>ribes ho<br>Periph<br>EALLC | rames                                                                                                                  |                           |

| 6 | -     | heral Interrupt Expansion (PIE)6-<br>ribes the peripheral interrupt expansion (PIE).   | 1 |

|---|-------|----------------------------------------------------------------------------------------|---|

|   |       |                                                                                        | ~ |

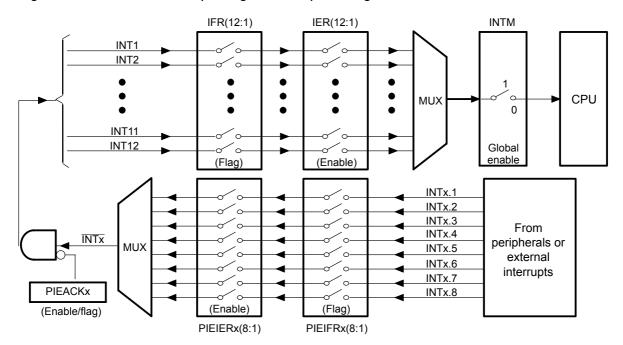

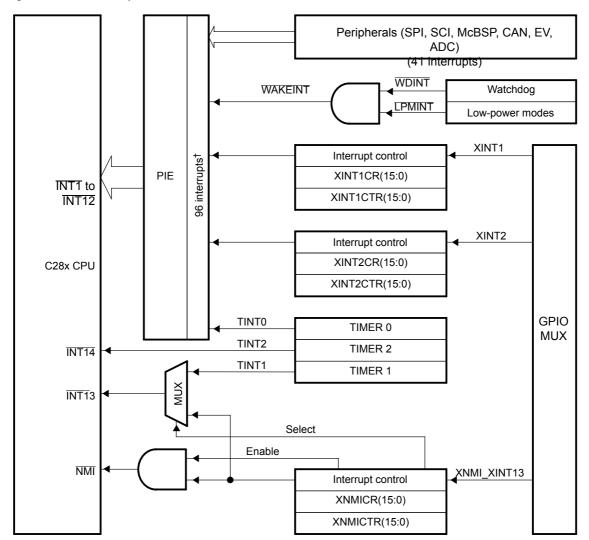

|   | 6.1   | Overview of the PIE Controller                                                         |   |

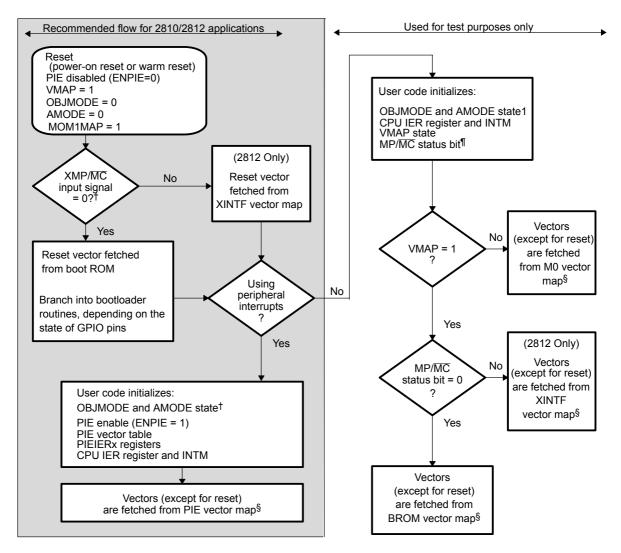

|   | 6.2   | Vector Table Mapping                                                                   |   |

|   | 6.3   | Interrupt Sources                                                                      |   |

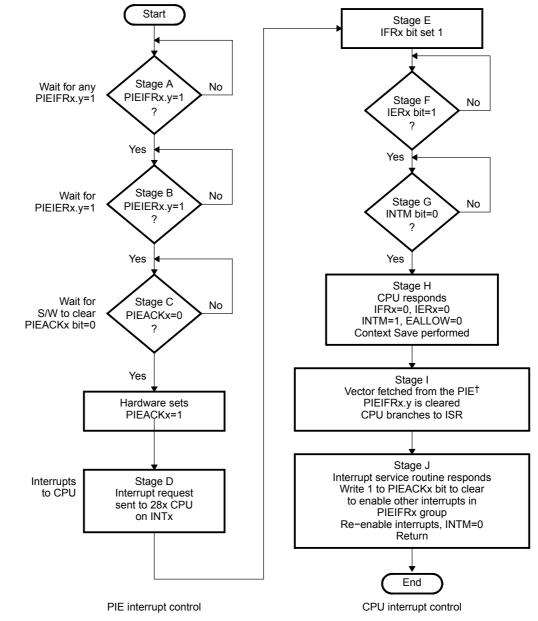

|   |       | 6.3.1 Procedure for Handling Multiplexed Interrupts                                    |   |

|   |       | 6.3.2 Procedures for Enabling And Disabling Multiplexed Peripheral Interrupts 6-1.     |   |

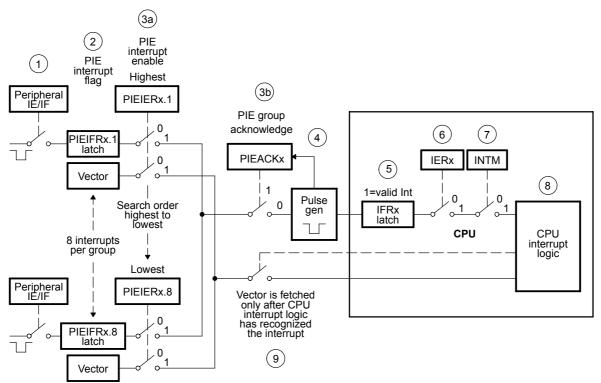

|   |       | 6.3.3 Flow of a Multiplexed Interrupt Request From a Peripheral to the CPU 6-14        |   |

|   |       | 6.3.4 The PIE Vector Table                                                             |   |

|   | 6.4   | PIE Configuration Registers                                                            |   |

|   | 6.5   | PIE Interrupt Registers                                                                |   |

|   |       | 6.5.1 PIE Interrupt Flag Registers 6-2                                                 |   |

|   |       | 6.5.2 PIE Interrupt Enable Registers 6-2                                               |   |

|   |       | 6.5.3 CPU Interrupt Flag Register (IFR) 6-2                                            |   |

|   |       | 6.5.4 Interrupt Enable Register (IER) and Debug Interrupt Enable Register (DBGIER) -32 | 6 |

|   | 6.6   | External Interrupt Control Registers 6-3                                               | 9 |

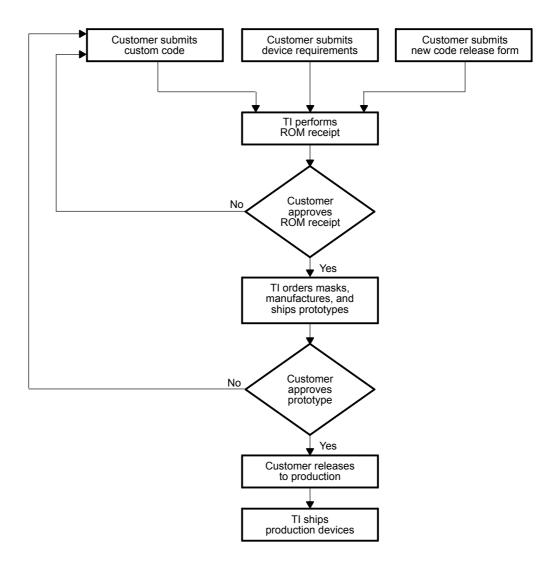

| Α | Subr  | nitting ROM Codes to TI                                                                | 1 |

|   | A.1   | Scope A-                                                                               |   |

|   | A.2   | Procedure A-                                                                           |   |

|   |       | A.2.1 Customer Required Information A-                                                 |   |

|   |       | A.2.2 TI Performs ROM Receipt                                                          |   |

|   |       | A.2.3 Customer Approves ROM Receipt                                                    |   |

|   |       | A.2.4 TI Orders Masks, Manufactures, and Ships Prototypes                              |   |

|   |       | A.2.5 Customer Approves Prototype                                                      |   |

|   |       | A.2.6 Customer Release to Production                                                   |   |

|   | A.3   | Code Submittal                                                                         |   |

|   | A.4   | Ordering                                                                               |   |

| в | Revis | sion History A-                                                                        | 1 |

|   | B.1   | Changes Made in This Revision A-                                                       |   |

# Figures

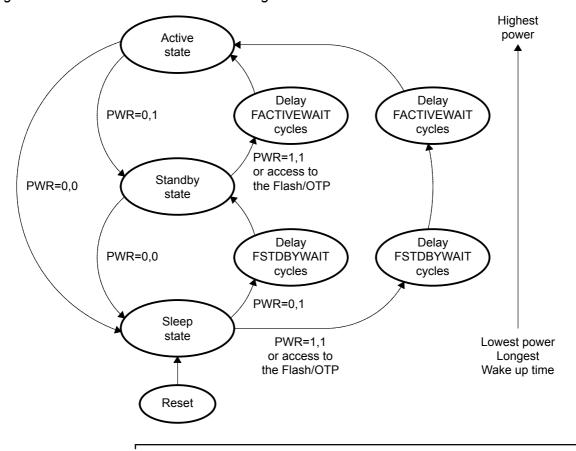

| 1-1.  | Flash Power Mode State Diagram 1-                           | 4  |

|-------|-------------------------------------------------------------|----|

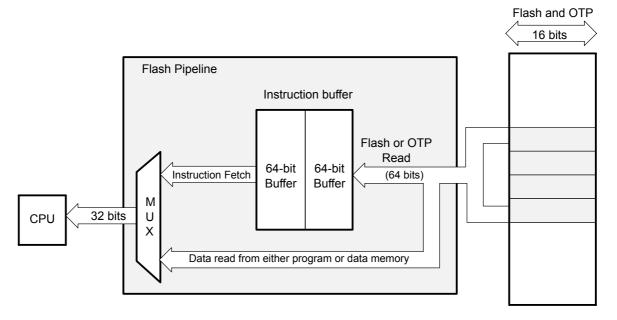

| 1-2.  | Flash Pipeline                                              | 7  |

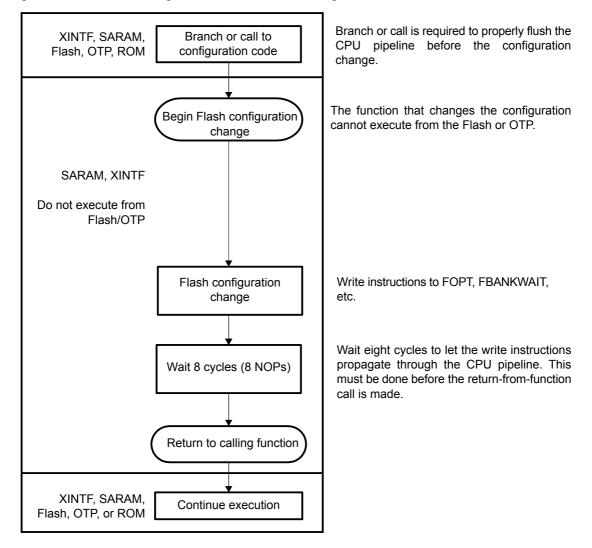

| 1-3.  | Flash Configuration Access Flow Diagram 1-                  | .9 |

| 1-4.  | Flash Options (FOPT) Register 1-1                           | 1  |

| 1-5.  | Flash Power Register (FPWR) 1-1                             | 1  |

| 1-6.  | Flash Status Register (FSTATUS) 1-1                         | 2  |

| 1-7.  | Flash Standby Wait (FSTDBYWAIT) Register 1-1                | 3  |

| 1-8.  | Flash Standby to Active Wait Counter (FACTIVEWAIT) Register | 4  |

| 1-9.  | Flash Waitstate (FBANKWAIT) Register 1-1                    | 4  |

| 1-10. | OTP Waitstate (FOTPWAIT) Register 1-1                       | 5  |

| 2-1.  | CSM Status and Control (CSMSCR) Register 2-                 | 7  |

| 2-2.  | Password Match Flow (PMF) 2-                                | .9 |

| 3-1.  | Clock and Reset Domains                                     | 2  |

| 3-2.  | Peripheral Clock Control (PCLKCR) Register 3-               | 4  |

| 3-3.  | High-Speed Peripheral Clock Prescaler (HISPCP) Register 3-  | -5 |

| 3-4.  | Low-Speed Peripheral Clock Prescaler (LOSPCP) Register      | 6  |

| 3-5.  | OSC and PLL Block                                           | 7  |

| 3-6.  | PLLCR Register                                              | 8  |

| 3-7.  | Low Power Mode Control 0 (LPMCR0) Register 3-1              | 2  |

| 3-8.  | Low Power Mode Control 1 (LPMCR1) Register 3-1              | 3  |

| 3-9.  | Watchdog Module                                             | 4  |

| 3-10. | Watchdog Counter (WDCNTR) Register                          | 7  |

| 3-11. | Watchdog Reset Key (WDKEY) Register 3-1                     | 8  |

| 3-12. | System Control and Status (SCSR) Register 3-1               | 8  |

| 3-13. | Watchdog Control (WDCR) Register 3-1                        | 9  |

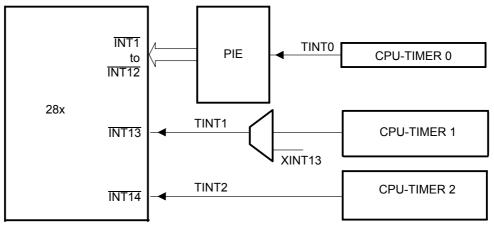

| 3-14. | CPU-Timers                                                  | 1  |

| 3-15. | CPU-Timer Interrupt Signals and Output Signal 3-2           | 1  |

| 3-16. | TIMERxTIM Register 3-2                                      | 3  |

| 3-17. | TIMERxTIMH Register 3-2                                     | 3  |

| 3-18. | TIMERxPRD Register <sup>+</sup> 3-2                         | 4  |

| 3-19. | TIMERxPRDH Register † 3-2                                   | 4  |

| 3-20. | TIMERxTCR Register† 3-2                                     | 5  |

| 3-21. | TIMERxTPR Register† 3-2                                     |    |

| 3-22. | TIMERxTPRH Register† 3-2                                    | 7  |

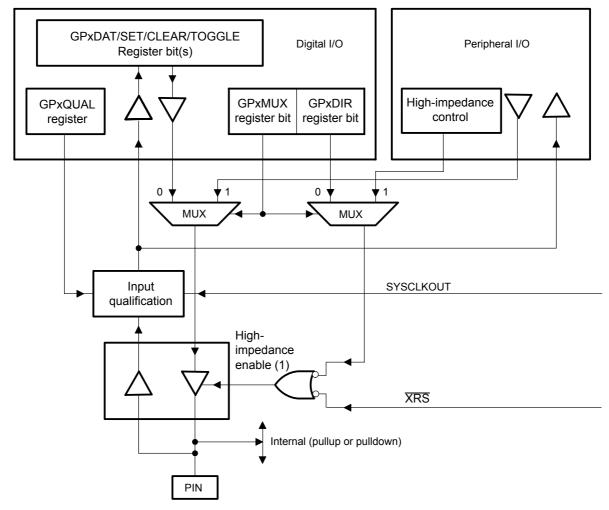

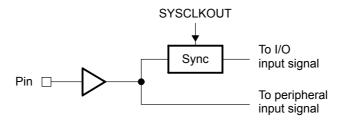

| 4-1.  | GPIO/Peripheral Pin MUXing                                  | -5 |

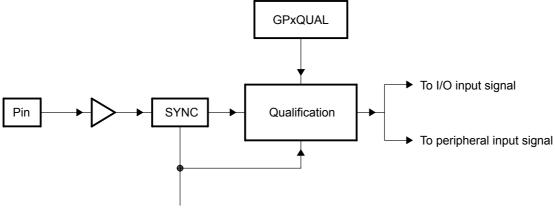

| 4-2.  | Type 1 Input Qualification                                  | 6  |

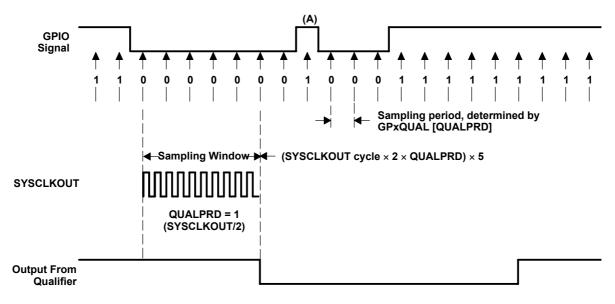

| 4-3.  | Input Qualifier Clock Cycles                                     | 4-7  |

|-------|------------------------------------------------------------------|------|

| 4-4.  | Type 2 Input Qualification                                       | 4-7  |

| 4-5.  | GPIO A Input Qualification Control (GPAQUAL) Register            | 4-12 |

| 4-6.  | GPIO B Input Qualification Control (GPBQUAL) Register            | 4-13 |

| 4-7.  | GPIO D Input Qualification Control (GPDQUAL) Register            |      |

| 4-8.  | GPIO E Input Qualification Control (GPEQUAL) Register            |      |

| 5-1.  | Device Configuration (DEVICECNF) Register                        | 5-10 |

| 5-2.  | Part ID Register                                                 | 5-11 |

| 5-3.  | DEVICEID Register                                                | 5-12 |

| 6-1.  | Overview: Multiplexing of Interrupts Using the PIE Block         | 6-2  |

| 6-2.  | Typical PIE/CPU Interrupt Response – INTx.y                      | 6-5  |

| 6-3.  | Reset Flow Diagram                                               | 6-9  |

| 6-4.  | Interrupt Sources                                                | 6-10 |

| 6-5.  | Multiplexed Interrupt Request Flow Diagram                       | 6-14 |

| 6-6.  | PIE Interrupt Acknowledge Register (PIEACK) Register-Address CE1 | 6-26 |

| 6-7.  | PIEIFRx Register (x = 1 to 12)                                   | 6-27 |

| 6-8.  | PIEIERx Register (x = 1 to 12)                                   | 6-28 |

| 6-9.  | Interrupt Flag Register (IFR) — CPU Register                     | 6-30 |

| 6-10. | Interrupt Enable Register (IER) — CPU Register                   | 6-33 |

| 6-11. | Debug Interrupt Enable Register (DBGIER) — CPU Register          | 6-36 |

| 6-12. | External Interrupt 1 Control Register (XINT1CR) — Address 7070h  | 6-39 |

| 6-13. | External Interrupt 2 Control Register (XINT2CR) — Address 7071h  | 6-40 |

| 6-14. | External NMI Interrupt Control Register (XNMICR) — Address 7077h | 6-40 |

| 6-15. | External Interrupt 1 Counter (XINT1CTR) — Address 7078h          | 6-42 |

| 6-16. | External Interrupt 2 Counter (XINT2CTR) — Address 7079h          | 6-42 |

| 6-17. | External NMI Interrupt Counter (XNMICTR) — Address 707Fh         | 6-43 |

| A−1.  | TMS320 ROM Code Prototype and Production Flowchart               | A-3  |

# **Tables**

| 1-1.         | Flash/OTP Configuration Registers(1)(2)                                    | . 1-10         |

|--------------|----------------------------------------------------------------------------|----------------|

| 1-2.         | Flash Options (FOPT) Register Field Descriptions                           | . 1-11         |

| 1-3.         | Flash Power Register (FPWR) Field Descriptions                             | . 1-12         |

| 1-4.         | Flash Status Register (FSTATUS) Field Descriptions                         | . 1-12         |

| 1-5.         | Flash Standby Wait (FSTDBYWAIT) Register Field Descriptions                |                |

| 1-6.         | Flash Standby to Active Wait Counter (FACTIVEWAIT) Register Field          | 1 1 1          |

| 1-7.         | Descriptions                                                               | . 1-14<br>1 1/ |

| 1-8.         | OTP Waitstate (FOTPWAIT) Register                                          |                |

| 1-0.<br>2-1. | Security Levels                                                            |                |

| 2-1.         | 281x Resources Not Affected by the CSM                                     |                |

| 2-2.<br>2-3. | F281x/C281x Resources Affected by the CSM                                  |                |

| 2-3.<br>2-4. | Code Security Module (CSM) Registers                                       |                |

|              | CSM Status and Control (CSMSCR) Register Field Descriptions                |                |

| 2-5.         |                                                                            |                |

| 3-1.         | PLL, Clocking, Watchdog, and Low-Power Mode Registers                      |                |

| 3-2.         | Peripheral Clock Control (PCLKCR) Register Field Descriptions              |                |

| 3-3.         | High-Speed Peripheral Clock Prescaler (HISPCP) Register Field Descriptions | 3-5            |

| 3-4.         | Low-Speed Peripheral Clock Prescaler (LOSPCP) Register Field Descriptions  | . 3-6          |

| 3-5.         | Possible PLL Configuration Modes                                           | . 3-8          |

| 3-6.         | PLLCR Register Field Descriptions                                          |                |

| 3-7.         | 281x Low-Power Modes                                                       |                |

| 3-8.         | Low Power Mode Control 0 (LPMCR0) Register Field Descriptions              |                |

| 3-9.         | Low Power Mode Control 1 (LPMCR1) Register Field Descriptions              |                |

| 3-10.        | Example Watchdog Key Sequences                                             |                |

| 3-11.        | Watchdog Counter (WDCNTR) Register Field Descriptions                      |                |

| 3-12.        | Watchdog Reset Key (WDKEY) Register Field Descriptions                     |                |

| 3-13.        | System Control and Status (SCSR) Register Field Descriptions               |                |

| 3-14.        | Watchdog Control (WDCR) Register Field Descriptions                        |                |

| 3-15.        | CPU-Timers 0, 1, 2 Configuration and Control Registers                     |                |

| 3-16.        | TIMERxTIM Register Field Descriptions                                      |                |

| 3-17.        | TIMERxTIMH Register Field Descriptions                                     |                |

| 3-18.        | TIMERxPRD Register Field Descriptions                                      |                |

| 3-19.        | TIMERxPRDH Register Field Description                                      |                |

| 3-20.        | TIMERxTCR Register Field Descriptions                                      |                |

| 3-21.        | TIMERxTPR Register Field Descriptions                                      |                |

| 3-22.        | TIMERxTPRH Register Field Descriptions                                     |                |

|              | - '                                                                        |                |

| 4-1.                     | GPIO MUX Registers <sup>†</sup>                                                                                    | 4-2  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|------|

| 4-2.                     | GPIO Data Registers†‡                                                                                              |      |

| 4-3.                     | GPIO A Register Bit to I/O Mapping                                                                                 |      |

| 4-4.                     | GPIO A Input Qualification Control (GPAQUAL) Register Field Descriptions                                           |      |

| 4-5.                     | GPIO B Register Bit to I/O Mapping                                                                                 |      |

| 4-6.                     | GPIO B Input Qualification Control (GPBQUAL) Register Field Descriptions                                           |      |

| 4-7.                     | GPIO D Register Bit to I/O Mapping                                                                                 |      |

| 4-8.                     | GPIO D Input Qualification Control (GPDQUAL) Register Field Descriptions                                           |      |

| 4-9.<br>4-10.            | GPIO E MUX Register Bit to I/O Mapping<br>GPIO E Input Qualification Control (GPEQUAL) Register Field Descriptions |      |

| 4-10.<br>4-11.           | GPIO F Register to Bit I/O Mapping                                                                                 |      |

| 4-11.<br>4-12.           | GPIO G Register to Bit I/O Mapping                                                                                 |      |

| 4-12.<br>5-1.            | Peripheral Frame 0 Registers                                                                                       |      |

| 5-1.<br>5-2.             | Peripheral Frame 1 Registers                                                                                       |      |

| 5 2.<br>5-3.             | Peripheral Frame 2 Registers†                                                                                      |      |

| 5-5.<br>5-4.             | Access to EALLOW Protected Registers                                                                               |      |

| 5 <del>4</del> .<br>5-5. | EALLOW Protected Device Emulation Registers                                                                        |      |

| 5-5.<br>5-6.             | EALLOW Protected Flash/OTP Configuration Registers                                                                 |      |

| 5-0.<br>5-7.             | EALLOW Protected Code Security Module (CSM) Registers                                                              |      |

| 5-8.                     | EALLOW Protected PIE Vector Table                                                                                  |      |

| 5-0.<br>5-9.             | EALLOW Protected PLL, Clocking, Watchdog, and Low-Power Mode Registers                                             |      |

| 5-10.                    | EALLOW Protected GPIO MUX Registers                                                                                |      |

| 5-11.                    | EALLOW Protected eCAN Registers                                                                                    |      |

| 5-12.                    | Device Emulation Registers                                                                                         |      |

| 5-13.                    | Device Configuration (DEVICECNF) Register Field Descriptions                                                       |      |

| 5-14.                    | Part ID Register Field Descriptions                                                                                |      |

| 5-15.                    | DEVICEID Register Field Descriptions                                                                               |      |

| 5-16.                    | PROTSTART and PROTRANGE Registers                                                                                  |      |

| 5-17.                    | PROTSTART Valid Values                                                                                             |      |

| 5-18.                    | PROTRANGE Valid Values #                                                                                           |      |

| 6-1.                     | Enabling Interrupt                                                                                                 |      |

| 6-2.                     | Interrupt Vector Table Mapping                                                                                     |      |

| 6-3.                     | Vector Table Mapping After Reset Operation +                                                                       |      |

| 6-4.                     | 281x PIE Vector Table                                                                                              |      |

| 6-5.                     | 281x PIE Peripheral Interrupts <sup>+</sup>                                                                        | 6-23 |

| 6-6.                     | PIE Configuration and Control Registers                                                                            | 6-24 |

| 6-7.                     | PIECTRL Register-Address CE0                                                                                       |      |

| 6-8.                     | PIECTRL Register-Field Descriptions                                                                                | 6-26 |

| 6-9.                     | PIE Interrupt Acknowledge Register (PIEACK) Register Field Descriptions                                            | 6-26 |

| 6-10.                    | PIEIFRx Register (x = 1 to 12) Field Descriptions                                                                  | 6-27 |

| 6-11.                    | PIEIERx Register (x = 1 to 12) Field Descriptions                                                                  | 6-28 |

| 6-12.                    | Interrupt Flag Register (IFR) Field Descriptions                                                                   | 6-30 |

| 6-13.                    | Interrupt Enable Register (IER) Field Descriptions                                                                 | 6-33 |

| 6-14.                    | Debug Interrupt Enable Register (DBGIER) Field Descriptions                                                        | 6-36 |

#### Tables

| 6-15. | External Interrupt 1 Control Register (XINT1CR) Field Descriptions  | 6-39 |

|-------|---------------------------------------------------------------------|------|

| 6-16. | External Interrupt 2 Control Register (XINT2CR) Field Descriptions  | 6-40 |

| 6-17. | External NMI Interrupt Control Register (XNMICR) Field Descriptions | 6-41 |

| 6-18. | XNMICR Register Settings and Interrupt Sources                      | 6-41 |

| 6-19. | External Interrupt 1 Counter (XINT1CTR) Field Descriptions          | 6-42 |

| 6-20. | External Interrupt 2 Counter (XINT2CTR) Field Descriptions          | 6-42 |

| 6-21. | External NMI Interrupt Counter (XNMICTR) Field Descriptions         | 6-43 |

## Chapter 1

# Memory

This chapter describes how Flash and one-time programmable (OTP) memories can be used with the 28x digital signal processor (DSP) device and peripherals. It also includes the registers associated with memory.

On ROM-only devices, this information applies to the ROM that replaced the Flash and the OTP memory, with the exception that you cannot program memory in ROM-only devices (including the OTP area).

# TopicPage1.1Flash and OTP Memory1-21.2Flash and OTP Power Modes1-31.3Flash and OTP Registers1-9

#### 1.1 Flash and OTP Memory

This section describes how to configure two kinds of memory – Flash and one-time programmable (OTP).

#### 1.1.1 Flash Memory

The on-chip Flash in Flash devices is uniformly mapped in both program and data memory space. This Flash memory is always enabled on 28x devices and features:

Multiple sectors

The minimum amount of flash memory that can be erased is a sector. Having multiple sectors provides the option of leaving some sectors programmed and only erasing specific sectors.

Code security

The flash is protected by the Code Security Module (CSM). By programming a password into the flash, you can prevent access to the flash by unauthorized persons. See Chapter 2 for information on using the CSM.

Low power modes

To save power when the flash is not in use, two levels of low power modes are available. See Section 1.2 for more information on the available flash power modes.

Configurable waitstates

Configurable wait states can be adjusted based on CPU frequency to give the best performance for a given execution speed.

Enhanced performance

A flash pipeline mode is provided to improve performance of linear code execution.

#### 1.1.2 OTP Memory

The  $1K \times 16$  block of one-time programmable (OTP) memory can be used to program data or code. This block can be programmed one time and cannot be erased.

#### 1.2 Flash and OTP Power Modes

The following operating states apply to the Flash and OTP memory:

- Reset or Sleep State: This is the state after a device reset. In this state, the bank and pump are in a sleep state (lowest power). A CPU read or fetch accesses to the Flash/OTP memory map area stalls the CPU. This access automatically initiates a change in power modes to the active or read state.

- Standby State: In this state, the bank and pump are in standby power mode state. A CPU read or fetch accesses to the Flash/OTP memory map area stalls the CPU. This access automatically initiates a change in power modes to the active state.

- Active or Read State: In this state, the bank and pump are in active power mode state (highest power). The CPU read or fetch access wait states to the Flash/OTP memory map area is controlled by the FBANKWAIT and FOTPWAIT registers. A prefetch mechanism called Flash pipeline can also be enabled for improving fetch performance for linear code execution.

The Flash/OTP bank and pump are always in the same power mode during read or execution operations from the Flash/OTP. See Figure 1–1 for a graphic depiction of the states.

You can change the current Flash/OTP memory power state as follows:

- To move to a lower power state: Change the PWR mode bits from a higher power mode to a lower power mode. This change instantaneously moves the Flash/OTP bank to the lower power state. This register should be accessed only by code running outside the Flash/OTP memory.

- To move from a lower power state to a higher power state, there are two options:

- Change the FPWR register from a lower state to a higher state. This access brings the Flash/OTP memory to the higher state.

- Access the Flash or OTP memory by a read access or program fetch access. This access automatically brings the Flash/OTP memory to the active state.

There is a delay when moving from a lower power state to a higher one. See Figure 1–1. This delay is required to allow the Flash to stabilize at the higher power mode. If any access to the Flash/OTP memory occurs during this delay the CPU automatically stalls until the delay is complete.

Figure 1–1. Flash Power Mode State Diagram

Note:

During the boot process, the Boot ROM performs a dummy read of the Code Security Module (CSM) password locations located in the flash. This read is performed to unlock a new or erased device that has no password stored in it so that flash programming or loading of code into CSM-protected SARAM can be performed. On devices with a password stored, this read has no effect and the CSM remains locked (see Chapter 2 for information on the CSM). One effect of this read is that the flash will transition from the sleep (reset) state to the active state.

The duration of the delay is determined by the FSTDBYWAIT and FACTIVEWAIT registers. Moving from the sleep state to a standby state is delayed by a count determined by the FSTDBYWAIT register. Moving from the standby state to the active state is delayed by a count determined by the FACTIVEWAIT register. Moving from the sleep mode (lowest power) to the active mode (highest power) is delayed by FSTDBYWAIT + FACTIVEWAIT.

1-4 Memory

#### 1.2.1 Flash and OTP Performance

CPU read or fetch operations to the Flash/OTP can take one of the following forms:

- □ 32-bit instruction fetch

- 16 or 32-bit data space read

- 16-bit program space read

Once Flash is in the active power state, then a read or fetch access to the bank memory map area can be classified as three types:

- Flash Memory Random Access: The number of wait states, for a random access, is configured by the RANDWAIT bits in the FBANKWAIT register. This register defaults to a worst-case count and the user needs to program the appropriate number of wait states to improve performance based on the CPU clock rate and the access time of the Flash.

- Flash Memory Paged Access: The Flash array is organized into rows and columns. The rows contain 2048 bits of information. The first access to a row is considered a random access. Subsequent accesses within the same row can be made with a faster access time. This is termed a PAGE access.

The Flash can take advantage of this by the user configuring a lower number of wait states in the PAGEWAIT bits in the FBANKWAIT register. This mode works for data space and program space reads as well as instruction fetches. See the device data sheet for more information on the access time of the Flash.

- OTP Access: Read or fetch accesses to the OTP are controlled by the OTPWAIT register bits in the FOTPWAIT register. Accesses to the OTP take longer than the Flash and there is no paged mode.

- **Notes:** 1) Writes to the Flash/OTP memory map area are ignored. They complete in a single cycle.

- 2) When the Code Security Module (CSM) is secured, reads to the Flash/OTP memory map area from outside the secure zone take the same number of cycles as a normal access. However, the read operation returns a zero.

- The Flash supports 0-wait accesses when the PAGEWAIT bits are set to zero. This assumes that the CPU speed is low enough to accommodate the access time.

#### 1.2.2 28x Flash Pipeline Mode

Flash memory is typically used to store application code. During code execution, instructions are fetched from sequential memory addresses, except when a discontinuity occurs. Usually the portion of the code that resides in sequential addresses makes up the majority of the application code and is

referred to as linear code. To improve the performance of linear code execution, a Flash pipeline mode has been implemented. Setting the ENPIPE bit in the FOPT register enables this mode. The Flash pipeline mode is independent of the CPU pipeline. To allow you to maintain code timing compatibility between Flash and ROM devices, the Flash pipeline mode has also been implemented on ROM devices.

An instruction fetch from the Flash or OTP reads out 64 bits per access. The starting address of the access from Flash is automatically aligned to a 64-bit boundary such that the instruction location is within the 64 bits to be fetched. With Flash pipeline mode enabled (see Figure 1–2), the 64 bits read from the instruction fetch are stored in a 64-bit wide by 2-level deep instruction pre-fetch buffer. The contents of this pre-fetch buffer are then sent to the CPU for processing as required.

Up to two 32-bit instructions or up to four 16-bit instructions can reside within a single 64-bit access. The majority of C28x instructions are 16 bits, so for every 64-bit instruction fetch from the Flash bank it is likely that there are up to four instructions in the pre-fetch buffer ready to process through the CPU. During the time it takes to process these instructions, the Flash pipeline automatically initiates another access to the Flash bank to pre-fetch the next 64 bits. In this manner, the Flash pipeline mode works in the background to keep the instruction pre-fetch buffers as full as possible. Using this technique, the overall efficiency of sequential code execution from Flash or OTP is improved significantly.

The Flash pipeline pre-fetch is aborted only on a PC discontinuity caused by executing an instruction such as a branch, BANZ, call, or loop. When this occurs, the pre-fetch is aborted and the contents of the pre-fetch buffer are flushed. There are two possible scenario's when this occurs:

- □ If the destination address is within the Flash or OTP, the pre-fetch aborts and then resumes at the destination address.

- ☐ If the destination address is outside of the Flash and OTP, the pre-fetch is aborted and begins again only when a branch is made back into the Flash or OTP. The Flash pipeline pre-fetch mechanism only applies to instruction fetches from program space. Data reads from data memory and from program memory do not utilize the pre-fetch buffer capability and thus bypass the pre-fetch buffer. For example, instructions such as MAC, DMAC, and PREAD read a data value from program memory. When this read happens, the pre-fetch buffer is bypassed but the buffer is not flushed. If an instruction pre-fetch is already in progress when a data read operation is initiated, then the data read will be stalled until the pre-fetch completes.

#### NOTE:

For code security operation, all addresses between 0x3F7F80 and 0x3F7F55 cannot be used as program code or data, but must be programmed to 0x0000 when the Code Security Password is programmed. If security is not a concern, then these addresses may be used for code or data.

The 128-bit password (at 0x3F 7FF8 – 0x3F 7FFF) must *not* be programmed to zeros. Doing so would permanently lock the device.

#### 1.2.3 Procedure to Change the Flash Configuration Registers

During Flash configuration, no accesses to the Flash or OTP can be in progress. This includes instructions still in the CPU pipeline, data reads, and instruction pre-fetch operations. To be sure that no access takes place during the configuration change, you should follow the procedure shown in Figure 1–3 for any code that modifies the FOPT, FPWR, FBANKWAIT, or FOTPWAIT registers.

This procedure also applies to the ROM on devices where the Flash and OTP have been replaced with ROM.

Figure 1–3. Flash Configuration Access Flow Diagram

#### 1.3 Flash and OTP Registers

The Flash and OTP memory can be configured by the registers shown in Table 1–1. The bit descriptions are in Figure 1–4 through Figure 1–6.

| Name                       | Address     | Size<br>(x16) | Description                           |

|----------------------------|-------------|---------------|---------------------------------------|

|                            |             | C             | Configuration Registers               |

| FOPT                       | 0x0000-0A80 | 1             | Flash Option Register                 |

| Reserved                   | 0x0000-0A81 | 1             | Reserved                              |

| FPWR                       | 0x0000-0A82 | 1             | Flash Power Modes Register            |

| FSTATUS                    | 0x0000-0A83 | 1             | Status Register                       |

| FSTDBYWAIT <sup>(3)</sup>  | 0x0000-0A84 | 1             | Flash Sleep To Standby Wait Register  |

| FACTIVEWAIT <sup>(3)</sup> | 0x0000-0A85 | 1             | Flash Standby To Active Wait Register |

| FBANKWAIT                  | 0x0000-0A86 | 1             | Flash Read Access Wait State Register |

| FOTPWAIT                   | 0x0000-0A87 | 1             | OTP Read Access Wait State Register   |

1) These registers are EALLOW protected. See Section 5.2 for information.

2) These registers are protected by the CSM. See Chapter 2 for information.

3) These registers are reserved for TI and should be left in their default state.

## Note: Flash configuration registers should not be accessed while an access is in progress in Flash or OTP memory