# Migration Between TMS320F28004x and TMS320F28002x

Joseph Casuga, Frank Ankapong, and Jason Whiles

### **ABSTRACT**

This migration guide describes the hardware and software differences to be aware of when moving between F28004x and F28002x C2000™ MCUs. This document shows the block diagram between the two MCUs as a visual representation on what blocks are similar or different. It also highlights the features that are unique between the two devices for all available packages in a device comparison table. A good starting point for migration would be the 64-PM package, which is pinout compatible between F28004x and F28002x, so a 64-PM PCB hardware section has been added. Section 2 discusses hardware considerations when migrating between F28004x and F28002x with the 64-PM package. The digital general-purpose input/output (GPIO) and analog multiplex comparison tables show pin functionality between the two MCUs. This is a good reference for hardware design and signal routing when considering a move between the two devices. Lastly, the F28002x software support is only in EABI format. The EABI migration is discussed in Section 4.

### Contents

| 1  | Feature Differences Between F28004x and F28002x       | . 3 |

|----|-------------------------------------------------------|-----|

| 2  | PCB Hardware Changes for the 64-Pin PM Package        | . 5 |

| 3  | Feature Differences for System Consideration          |     |

| 4  | Application Code Migration From F28004x to F28002x    | 21  |

| 5  | References                                            | 24  |

|    | List of Figures                                       |     |

| 1  | F28002x and F28004x Overlaid Functional Block Diagram | . 3 |

|    | List of Tables                                        |     |

| 1  | F28004x and F28002x Superset Device Comparison        | . 4 |

| 2  | Communication Module Instances                        | . 7 |

| 3  | Control Module Differences                            | . 8 |

| 4  | Analog Module Instances                               | . 8 |

| 5  | XTAL Module Differences                               | . 9 |

| 6  | PLL Features                                          | . 9 |

| 7  | Pie Channel Legend                                    | . 9 |

| 8  | Pie Table Comparison                                  | 10  |

| 9  | Bootrom Comparison Table                              | 11  |

| 10 | Boot options Legend                                   | 11  |

| 11 | Bootloaders and GPIO Assignment Comparison            | 11  |

| 12 | Boot Modes Comparison                                 | 12  |

| 13 | CLA, CLB, DMA and Motor Control Libraries             | 13  |

| 14 | ERAD Module Differences                               | 13  |

| 15 | Mux Legend                                            | 14  |

| 16 | GPIO Mux Table Comparison                             | 15  |

| 17 | Mux Legend                                            | 17  |

| 18 | F28004x and F28002x Analog Mux Table Differences      | 18  |

## www.ti.com

| 19 | Section Names         | 23 |

|----|-----------------------|----|

| 20 | Flash API Differences | 23 |

### **Trademarks**

C2000, Code Composer Studio are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 1 Feature Differences Between F28004x and F28002x

F28002x is a subset of F28004x with a few new features. They have one package in common, 64-pin PM. It is possible to migrate between F28002x and F28004x with the caveats in this document taken into account.

NOTE: This comparison guide focuses on the super-set devices: F280049 and F280025. Other part numbers in this product family have reduced feature support. For details specific to part numbers, see the device-specific data sheet.

#### 1.1 F28004x and F28002x Feature Comparison

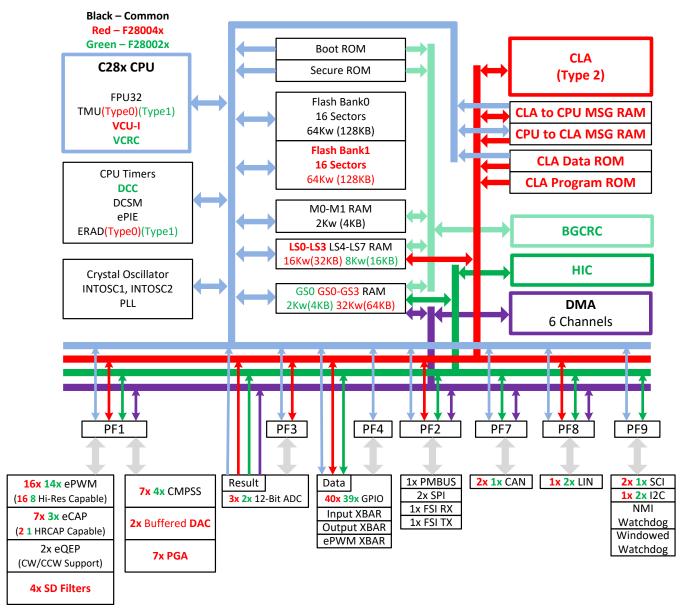

An overlaid block diagram of F28004x and F28002x is shown in Figure 1 while feature comparison of the superset part numbers for the F28002x and F28004x devices is shown in Table 1.

Figure 1. F28002x and F28004x Overlaid Functional Block Diagram

Table 1. F28004x and F28002x Superset Device Comparison

|                                      |                                       | F2                                                       | 80049 F28004  | 49C                           | F2                                                         | 80025 F28002    | .5C |  |

|--------------------------------------|---------------------------------------|----------------------------------------------------------|---------------|-------------------------------|------------------------------------------------------------|-----------------|-----|--|

| Fea                                  | 100-Pin PZ                            | 64-Pin PM                                                | 56-Pin RSH    | 80-Pin PN 64-Pin PM 48-Pin PT |                                                            |                 |     |  |

|                                      |                                       | Processor and                                            | d Accelerator | 'S                            |                                                            | I               |     |  |

|                                      | Frequency (MHz)                       |                                                          | 100           |                               |                                                            | 100             |     |  |

|                                      | FPU                                   |                                                          | Yes           |                               | Yes (with new instructions for Fas                         |                 |     |  |

| C28x                                 | VCU-I                                 |                                                          | Yes           |                               |                                                            | No              |     |  |

|                                      | VCRC                                  |                                                          | No            |                               |                                                            | Yes             |     |  |

|                                      | TMU                                   |                                                          | Yes - Type 0  |                               |                                                            | e 1 (with new i |     |  |

| CLA Type 2                           | Available                             |                                                          | Yes           |                               |                                                            | No              |     |  |

| CLA – Type 2                         |                                       | 100                                                      |               |                               | _                                                          |                 |     |  |

| 6-Channel DMA - Type 0               |                                       | Yes                                                      |               |                               | Yes                                                        |                 |     |  |

|                                      |                                       | Men                                                      | nory          |                               |                                                            |                 |     |  |

| Flash                                |                                       | 2                                                        | 256KB (128Kv  | v)                            |                                                            | 128KB (64Kw     | )   |  |

|                                      | Dedicated and Local<br>Shared RAM     |                                                          | 36KB (18Kw)   | 1                             |                                                            | 20KB (10Kw)     |     |  |

| RAM                                  | Global Shared RAM                     |                                                          | 64KB (32Kw)   |                               |                                                            | 4KB (2Kw)       |     |  |

|                                      | Total RAM                             |                                                          | 100KB (50Kw   | ·)                            |                                                            | 24KB (12Kw)     |     |  |

| Code security for on-chip f          | lash and RAM                          |                                                          | Yes           |                               |                                                            | Yes             |     |  |

|                                      |                                       | Sys                                                      | tem           |                               |                                                            |                 |     |  |

| Configurable Logic Block (           | · · · · · · · · · · · · · · · · · · · |                                                          | F28004xC      |                               | F28002xC                                                   |                 |     |  |

| Motor Control Libraries in I         | ROM                                   |                                                          | F28004xC      |                               | F28002xC                                                   |                 |     |  |

| 32-bit CPU timers                    |                                       |                                                          | 3             |                               | 3                                                          |                 |     |  |

| Watchdog timers                      |                                       |                                                          | 1             |                               | 1                                                          |                 |     |  |

| Nonmaskable Interrupt Wa             | atchdog (NMIWD) timers                |                                                          | 1             |                               | 1                                                          |                 |     |  |

| Crystal oscillator/External          | clock input                           |                                                          | 1             |                               | 1                                                          |                 |     |  |

| 0-pin internal oscillator            |                                       |                                                          | 2             |                               |                                                            | 2               |     |  |

| GPIO pins                            |                                       | 40                                                       | 26            | 25                            | 39                                                         | 26              | 14  |  |

| Additional GPIO                      |                                       | 3 (If 2-pin cJTAG is used and INTOSC used instead of X1) |               |                               | 4 (If 2-pin cJTAG is used and INTOS used instead of X1/X2) |                 |     |  |

| AIO inputs                           |                                       | 21                                                       | 14            | 12                            | 1                                                          | 6               | 14  |  |

| External interrupts                  |                                       | 5                                                        |               |                               | 5                                                          |                 |     |  |

|                                      |                                       | Analog Po                                                | eripherals    |                               |                                                            |                 |     |  |

|                                      | Number of ADCs                        | 3                                                        |               |                               | 2                                                          |                 |     |  |

| ADC 12-bit                           | MSPS                                  | 3.45                                                     |               |                               | 3.45                                                       |                 |     |  |

|                                      | Conversion Time (ns)                  | 300                                                      |               |                               | 300                                                        |                 | 1   |  |

| ADC channels (single-end             | ed)                                   | 21                                                       | 14            | 12                            | 1                                                          | 6               | 14  |  |

| Temperature sensor                   |                                       |                                                          | 1             |                               | 1                                                          |                 |     |  |

| Buffered DAC                         |                                       | 2                                                        |               | _                             |                                                            |                 |     |  |

| CMPSS (each CMPSS has internal DACs) | 7                                     | 6                                                        | 5             | 4                             |                                                            |                 |     |  |

| PGA (Gain Settings: 3, 6,            | 7                                     | 5                                                        | 4             | -                             |                                                            |                 |     |  |

|                                      |                                       | Control P                                                | eripherals    |                               |                                                            |                 |     |  |

| eCAP/HRCAP modules – I<br>Type 2     | 7 (2 with HRCAP capability)           |                                                          |               | 3 (1 with HRCAP capability)   |                                                            |                 |     |  |

| ePWM/HRPWM channels                  | * *                                   | 16 (16 with HRPWM capability)                            |               |                               | 14 (8 with HRPWM capability)                               |                 |     |  |

| eQEP modules - F28004x               | : Type 1 F28002x: Type 2              | 2                                                        |               | 1                             | 2                                                          |                 |     |  |

| SDFM channels – Type 1               |                                       | 4                                                        |               | 3                             | _                                                          |                 |     |  |

Table 1. F28004x and F28002x Superset Device Comparison (continued)

|                                                 | F2             | 80025 F280025C                    |               |                   |                                   |           |  |

|-------------------------------------------------|----------------|-----------------------------------|---------------|-------------------|-----------------------------------|-----------|--|

| Feature                                         | 100-Pin PZ     | 100-Pin PZ 64-Pin PM 56-Pin RSH   |               |                   | 64-Pin PM                         | 48-Pin PT |  |

|                                                 | Communication  | on Peripheral                     | S             |                   | •                                 |           |  |

| CAN – Type 0                                    | 2 1            |                                   |               |                   |                                   |           |  |

| I2C – Type 1                                    |                | 1 2                               |               |                   |                                   |           |  |

| SCI – Type 0                                    |                | 2                                 |               | 1                 |                                   |           |  |

| SPI – Type 2                                    |                | 2                                 |               | 2                 |                                   |           |  |

| LIN – Type 1                                    |                | 1                                 |               | 2                 |                                   |           |  |

| PMBus – Type 0                                  |                | 1                                 |               |                   | 1                                 |           |  |

| FSI – Type 0                                    | 1              | (1 RX and 1 T                     | X)            | 1 (1 RX and 1 TX) |                                   |           |  |

| Package (                                       | Options, Tempe | erature, and G                    | Qualification |                   |                                   |           |  |

| S: -40°C to 125°C (TJ)                          |                | Yes                               |               | Yes               |                                   |           |  |

| Q: -40°C to 125°C (TA) (AEC Q100 qualification) | Yes            | No (use<br>F280048 or<br>F280040) | _             | Yes               | No (use<br>F280024 or<br>F280022) | Yes       |  |

### 2 PCB Hardware Changes for the 64-Pin PM Package

This section describes some considerations to note when switching boards between F28004x and F28002x devices, or designing boards for the 64-pin package option on either device.

### 2.1 Internal DC-DC Regulator

F28002x does not have the internal DC-DC regulator. Due to this, GPIO22 and GPIO23 do not have the alternate functions of VFBSW and VSW, respectively. Also, VDDIO\_SW is just another VDDIO and VSS SW is just another VSS.

If using a F28002x device in a F28004x board, DC-DC is not available so VFBSW (GPIO22) and VSW (GPIO23) can be used as regular GPIOs.

If using a F28004x device in a F28002x board, DC-DC is available so GPIO22 and GPIO23 can be used as the alternate functions VFBSW and VSW, respectively, for the DC-DC. However, due to how sensitive the DC-DC is to board layout, if the F28002x board was not built with a DC-DC layout in mind, it should not be used as such.

### 2.2 VREGENZ Pin

F28002x does not have a VREGENZ pin. The VREGENZ pin is converted to a GPIO (GPIO39) and the VREGENZ signal is internally tied low. Due to this, the internal VREG is always enabled and hence supplying the 1.2 V externally is not an option.

If using a F28002x device in a F28004x board, the VREGENZ pin can be used as GPIO39 or you can follow the unused pins practice for GPIOs found in the device-specific data sheet.

If using a F28004x device in a F28002x board, tie GPIO39 to VDDIO to supply the 1.2 V externally or tie GPIO39 to VSS to use the internal VREG.

### 2.3 XTAL X1 GPIO Mux Capability

On the F28002x device, the crystal pin X1 also doubles as a GPIO (GPIO19).

If using a F28002x device in a F28004x board, the X1 pin can be used as GPIO19 after making the required software changes. Remove the load cap on X1 if one exists and a crystal is not being used as the clock source.

If using a F28004x device in a F28002x board, install the load cap on X1 if using a crystal as the clock source. GPIO19 functionality is not available.

### 2.4 PGA Ground

The F28002x device does not have PGAs. The two PGA\_GND pins on the 64-pin package are converted to ADC channels. PGA135 GND is now A15/C7/AIO233, and PGA246 GND is now A8/C11/AIO241.

If using a F28002x device in a F28004x board:

- If PGA135\_GND and PGA246\_GND pins are not tied to GND, they can be used as the ADC channels.

- If PGA135\_GND and PGA246\_GND pins are tied to GND, those two ADC channels will read a low conversion.

If using a F28004x device in a F28002x board, tie A15/C7/AIO233 and A8/C11/AIO241 to VSSA.

### 2.5 Analog Pin Assignment

For more information, see Section 3.10.

### 2.6 GPIO Pin Assignment

For more information, see Section 3.9.

### 3 Feature Differences for System Consideration

This section outlines the differences and similarities that exist when moving between the F28002x and F28004x devices.

### 3.1 New Features in F28002x

This section outlines features that only exist in the F28002x device.

### 3.1.1 TMU Type1

Two instructions have been added to the instruction set of the Trigonometrical Math Unit (TMU) on F28002x to support computation of the floating-point power function "powf". These instructions calculate the inverse binary exponent in the base two logarithm and can be combined to compute the power of a floating-point number raised to the power of another floating-point number. This calculation would typically take 300 cycles using library emulation, but takes less than ten cycles using the new instructions. An example of the application of the power function is non-linear proportional integral derivative control (NLPID), which is a component of the C2000 Digital Control Library.

### 3.1.2 Fast Integer Division (FINTDIV)

The C28x processor Fast Integer Division (FINTDIV) unit provides an open and scalable approach to facilitate different data type sizes (16/16, 32/16, 32/32, 64/32, 64/64), signed and unsigned or mixed data type versions (ui32/ui32, i32/ui32, i32/i32) and for additional performance, the operations return both the integer and remainder portion of the calculation simultaneously. The division operations are interruptible so as to enable minimum latency for higher priority tasks, a critical requirement for high performance real-time control applications. Unique to this fast integer division unit is support for Truncated, Modulo and Euclidean division formats without any cycle penalty. Each of these formats represents the integer and remainder result in different forms. Below is a brief summary of the various division formats:

- Truncated format is the traditional division performed in C language (/ = integer, % = remainder), however, the integer value is non-linear around zero.

- Modulo division is commonly found when performing division on an Excel worksheet.

- Euclidean format is another format similar to Modulo, the difference is the sign on the remainder value.

Both the Euclidean and Modulo formats are more appropriate for precise control applications because the integer value is linear around the zero point and, hence, avoid potential calculation hysteresis. The C28x compiler supports all three division formats for all data types.

### 3.1.3 Host Interface Controller (HIC)

The Host Interface Controller (HIC) is a new module for the F28002x device that allows an external host controller to directly access resources of the F28002x device using the ASRAM protocol. For details on the HIC, see the *TMS320F28002x microcontrollers technical reference manual* (SPRUIN7).

### 3.1.4 Background CRC (BGCRC)

The Background CRC (BGCRC) is a new module for the F28002x device that can compute the CRC-32 value of a configurable block of memory. It is an upgrade on the CLAPROMCRC found in the F28004x device to test more memories than just the CLA ROM. Note that the F28002x device does not have a CLA. BGCRC was first introduced in F2838x. For details on the BGCRC, see the *TMS320F28002x microcontrollers technical reference manual* (SPRUIN7) or the *TMS320F2838x microcontrollers technical reference manual* (SPRUII0).

### 3.1.5 Standby Low Power Mode

In F28004x, standby low power mode was deprecated. In F28002x, standby low power mode is available for applications requiring this power saving feature.

### 3.1.6 X1 GPIO Functionality

In the F28002x device, the crystal pin X1 can also be used as a GPIO, GPIO19. This is a new feature for the F28002x. The X1 pin can either be used as the crystal input pin or as GPIO19, but not both simultaneously. For details on this functionality, see the *TMS320F28002x microcontrollers technical reference manual* (SPRUIN7).

### 3.1.7 Diagnostic Features (PBIST/HWBIST)

F28004x documents refer to PBIST as the controller that executes configurable memory tests routines as part of the boot up sequence. In F28002x documents and in future C2000 device documents, this module is referred to as MPOST (memory power on self-test). PBIST (MPOST) is enabled as part of the boot up sequence in both F28004x and F28002x devices. HWBIST is a self-test controller for the CPU for fault coverage in safety applications. HWBIST can be invoked from user application code. HWBIST is available only in the F28002x device.

### 3.2 Communication Module Changes

The communication module changes between the F28004x and F28002x devices only affect the number of peripherals. Module functionality is maintained for both devices. Table 2 shows the module instances differences which should be considered when migrating applications between F28004x and F28002x.

| Module | F28004x        | F28002x        |

|--------|----------------|----------------|

| LIN    | 1 - LINA       | 2 - LINA, LINB |

| CAN    | 2 - CANA, CANB | 1 - CANA       |

| SCI    | 2 - SCIA, SCIB | 1 - SCIA       |

| SPI    | 2 - SPIA, SPIB | 2 - SPIA SPIB  |

| I2C    | 1 - I2CA       | 2 - I2CA, I2CB |

| PMBUS  | 1 - PMBUSA     | 1 - PMBUSA     |

| FSI    | 1 - FSIA       | 1 - FSIA       |

**Table 2. Communication Module Instances**

### 3.3 Control Module Changes

There are changes in the control modules between the F28004x and F28002x devices. The biggest change comes from the EPWM on the F28002x device which has a new generic and simple sync scheme that allows any EPWM/ECAP to be the master sync source for another EPWM/ECAP. Table 3 shows the module instances differences which should be considered when migrating applications between F28004x and F28002x.

Module Category F28004x F28002x Note **SDFM** 4 - SD1 C1..C4 Number eQEP 2 - EQEP1, EQEP2 2 - EQEP1, EQEP2 Number Select source as either device pins or Registers **QEPSRCSEL** cmpss/epwmxbar Support for SinCos Other Transducers **eCAP** Number 7 - ECAP1..7 3 - ECAP1..3 Registers **ECAPSYNCINSEL** Select sync source for ecap **HRCAP** Number 2 - HRCAP6, HRCAP7 1 - HRCAP3 **ePWM** Number 8 - EPWM1..8 7 - EPWM1..7 F28002x can now generate an TBCTL3.OSSFRCEN EPWMxSYNCO with Registers GLDCTL2[OSHTLD] EPWMxSYNCI to EPWMxSYNCO SYNCSEL **EPWMSYNCINSEL** path removed from F28002x TBCTL.SYNCOSEL DCAEVT1 and DCBEVT1 are new **EPWMSYNCOUTEN** sync options for F28002x TBCTL2.SYNCOSELX

**Table 3. Control Module Differences**

### 3.4 Analog Module Differences

Number Clock Source

**HRPWM**

This section outlines the analog differences between F28002x and F28004x. The GPDAC and PGA are not present on the F28002x and the analog mux table is re-mapped.

8 - HRPWM1..8

EPWM1CLK

| Module               | F28004x              | F28002x              |

|----------------------|----------------------|----------------------|

| ADC <sup>(1)</sup>   | 3 - ADCA, ADCB, ADCC | 2 - ADCA, ADCC       |

| GPDAC                | 2 - GPDACA, GPDACB   | -                    |

| CMPSS <sup>(1)</sup> | 7 - CMPSS1 to CMPSS7 | 4 - CMPSS1 to CMPSS4 |

| PGA                  | 7 - PGA1 to PGA7     | -                    |

| Temp Sensor          | 1 - (in ADCB ch 14)  | 1 - (in ADCC ch 12)  |

**Table 4. Analog Module Instances**

4 - HRPWM1..4

Respective EPWM

### 3.5 Other Device Changes

This section describes feature differences between F28004x and F28002x that were not covered in the previous sections, as such the changes identified below must be considered when migrating applications between devices.

8

<sup>(1)</sup> In porting software from F28004x to F28002x (or the other way around), care must be taken to ensure that the correct ADC channels are used because of a difference in channel assignment, see Section 3.10.

### 3.5.1 System Control Changes

This section highlights the System Control differences between F28002x and F28004x. There are XTAL module, PLL feature and Pie channel mapping changes between the two devices which are outlined in this section.

### 3.5.1.1 XTAL Module

The XTAL module has a few changes between F28004x and F28002x as highlighted in Table 5.

**Table 5. XTAL Module Differences**

| Module | Category  | F28004x                  | F28002x                   | Note                                        |

|--------|-----------|--------------------------|---------------------------|---------------------------------------------|

|        |           | X1CNT.X1CNT[90]          | X1CNT.X1CNT[100]          |                                             |

| XTAL   | Registers | -                        | XTALCR2                   | For pre-conditioning the GPIO mode of X1/X2 |

|        | Other     | X1CNT.CLR is synchronous | X1CNT.CLR is asynchronous |                                             |

### 3.5.1.2 PLL

The PLL blocks of F28004x and F28002x devices are different. Table 6 lists the PLL features for both devices for comparison. For more information, see the *TMS320F28002x microcontrollers technical reference manual* (SPRUIN7).

**Table 6. PLL Features**

| Feature                      | F28004x       | F28002x       |

|------------------------------|---------------|---------------|

| VCO Range                    | 120 - 400 MHz | 220 - 500 MHz |

| PLL Raw Clock Range          | 15 - 200 MHz  | 6 - 200 MHz   |

| X1 Input Range (PLL enabled) | 2 - 20 MHz    | 2 - 25 MHz    |

| REFCLK Divider               | No            | Yes [132]     |

| PLL Slip Detect              | Yes           | No (use DCC)  |

| Fractional PLLMULT           | Yes           | No            |

Due to the PLL differences between the two devices, TI recommends to use the PLL set up function, SysCtrl\_setClock() in C2000Ware to ensure proper PLL setting.

### 3.5.1.3 Pie Channel Mapping

Pie channel mapping between F28004x and F28002x is different due to peripheral module changes between these devices. Table 8 summarizes the common and unique pie channels on these two devices.

Table 7. Pie Channel Legend

| Color | Description                             |

|-------|-----------------------------------------|

|       | Pie channel common for both devices     |

|       | Pie channel applicable only for F28004x |

|       | Pie channel applicable only for F28002x |

## **Table 8. Pie Table Comparison**

|         | INTx.1       | INTx.2        | INTx.3       | INTx.4           | INTx.5       | INTx.6       | INTx.7           | INTx.8                | INTx.9       | INTx.10                           | INTx.11                             | INTx.12                          | INTx.13                         | INTx.14         | INTx.15          | INTx.16               |

|---------|--------------|---------------|--------------|------------------|--------------|--------------|------------------|-----------------------|--------------|-----------------------------------|-------------------------------------|----------------------------------|---------------------------------|-----------------|------------------|-----------------------|

| INT1.y  | ADCA1        | ADCB1         | ADCC1        | XINT1            | XINT2        | -            | TIMER0           | WAKE/W<br>DOG         | -            | -                                 | -                                   | -                                | -                               | -               | -                | -                     |

| INT2.y  | EPWM1_<br>TZ | EPWM2_<br>TZ  | EPWM3_<br>TZ | EPWM4_<br>TZ     | EPWM5_<br>TZ | EPWM6_<br>TZ | EPWM7_<br>TZ     | EPWM8_<br>TZ          | -            | -                                 | -                                   | -                                | -                               | -               | -                | -                     |

| INT3.y  | EPWM1        | EPWM2         | EPWM3        | EPWM4            | EPWM5        | EPWM6        | EPWM7            | EPWM8                 | -            | -                                 | -                                   | -                                | -                               | -               | -                | -                     |

| INT4.y  | ECAP1        | ECAP2         | ECAP3        | ECAP4            | ECAP5        | ECAP6        | ECAP7            | -                     | -            | -                                 | ECAP3_<br>HRC                       | -                                | -                               | ECAP6_<br>HRCAL | ECAP7_<br>HRCAL  | -                     |

| INT5.y  | EQEP1        | EQEP2         | -            | CLB1             | CLB2         | -            | -                | -                     | SDFM1        | -                                 | -                                   | -                                | SDFM1D<br>R1                    | SDFM1D<br>R2    | SDFM1D<br>R3     | SDFM1D<br>R4          |

| INT6.y  | SPIA_RX      | SPIA_TX       | SPIB_RX      | SPIB_TX          | -            | -            | -                | -                     | -            | -                                 | -                                   | -                                | -                               | -               | -                | -                     |

| INT7.y  | DMA_CH<br>1  | DMA_CH<br>2   | DMA_CH       | DMA_CH<br>4      | DMA_CH<br>5  | DMA_CH<br>6  | -                | -                     | -            | -                                 | FSITX_I<br>NT1                      | FSITX_I<br>NT2                   | FSIRX_I<br>NT1                  | FSIRX_I<br>NT2  | CLAPRO<br>MCRC   | DCC0                  |

| INT8.y  | I2CA         | I2CA_FIF<br>O | I2CB         | I2CB_FIF<br>O    | -            | -            | -                | -                     | LINA_0       | LINA_1                            | LINB_0                              | LINB_1                           | PMBUSA                          | -               | -                | DCC1                  |

| INT9.y  | SCIA_RX      | SCIA_TX       | SCIB_RX      | SCIB_TX          | CANA_0       | CANA_1       | CANB_0           | CANB_1                | -            | -                                 | -                                   | -                                | BGCRC                           | -               | -                | HICA                  |

| INT10.y | ADCA_E<br>VT | ADCA2         | ADCA3        | ADCA4            | ADCB_E<br>VT | ADCB2        | ADCB3            | ADCB4                 | ADCC_E<br>VT | ADCC2                             | ADCC3                               | ADCC4                            | -                               | -               | -                | -                     |

| INT11.y | CLA1_1       | CLA1_2        | CLA1_3       | CLA1_4           | CLA1_5       | CLA1_6       | CLA1_7           | CLA1_8                | -            | -                                 | -                                   | -                                | -                               | -               | -                | -                     |

| INT12.y | XINT3        | XINT4         | XINT5        | PBIST<br>(MPOST) | FMC          | -            | FPU_OV<br>ERFLOW | FPU_UN<br>DERFLO<br>W | -            | RAM_CO<br>RRECTA<br>BLE_ER<br>ROR | FLASH_<br>CORRE<br>CTABLE<br>_ERROR | RAM_AC<br>CESS_VI<br>OLATIO<br>N | SYS_PL<br>L_SLIP <sup>(1)</sup> | -               | CLA_OV<br>ERFLOW | CLA_UN<br>DERFLO<br>W |

<sup>(1)</sup> Not implemented in F28002x

### 3.5.2 Bootrom

This section outlines bootrom similarities and differences between F28004x and F28002x devices.

### 3.5.2.1 Bootrom Features

For specific bootrom features on F28004x and F28002x for hardware or software consideration, see Table 9.

**Table 9. Bootrom Comparison Table**

|                                     | F28004x                                                                                                                                                                                                                            | F28002x                                                               |  |  |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| System Debug (ERAD)                 | NMI is disabled                                                                                                                                                                                                                    | NMI is enabled. Bootrom exception handler is updated for this NMI     |  |  |  |

| HWBIST                              | HWBIST is not available                                                                                                                                                                                                            | HWBIST is available                                                   |  |  |  |

| CPU Boot Mode GPIO<br>Assignments   | On 64-pin package, F28004x and F28002x have similar options however the BOOTDEFx values are different. For boot mode GPIO assignment on the other pin package types, see the <i>Bootrom</i> section in device-specific data sheet. |                                                                       |  |  |  |

| BMSP Restrictions - Do not use pins | GPIO20-33, GPIO36, GPIO38 and GPIO60-233                                                                                                                                                                                           | GPIO20, GPIO21,GPIO36,GPIO38,GPIO47-60 and GPIO63-223                 |  |  |  |

| RAM Initialization                  | RAM initialization occurs on POR and XRS                                                                                                                                                                                           | RAM initialization occurs only on POR                                 |  |  |  |

| ROM Table                           | ROM tables for F28004x and F28002x are different. For details, see the device-specific TRM.                                                                                                                                        |                                                                       |  |  |  |

| PBIST(MPOST) Status Flag            | Flag is reset for every reset type                                                                                                                                                                                                 | Flag is reset only for POR reset type                                 |  |  |  |

| PBIST(MPOST) Execution Speed        | Will execute either at maximum SYSCLK speed or INTOSC clock                                                                                                                                                                        | Will execute either at maximum SYSCLK or half of maximum SYSCLK speed |  |  |  |

### 3.5.2.2 BOOTDEF Values Comparison

Due to GPIO and Flash memory differences between F28004x and F28002x, BOOTDEF values and options between the two devices will not be the same. Table 11 and Table 12 outlines these differences that will have to be considered when migrating an application from F28004x to F28002x.

Table 10. Boot options Legend

| Color | Description                                                    |

|-------|----------------------------------------------------------------|

|       | Options common for both devices but BOOTDEFx values may differ |

|       | Options applicable only for F28004x                            |

|       | Options applicable only for F28002x                            |

Table 11. Bootloaders and GPIO Assignment Comparison

| Bootloader | Option <sup>(1)</sup> | BOOTDEFx | F28004x                       | F28002x                          |

|------------|-----------------------|----------|-------------------------------|----------------------------------|

| Parallel   | 0                     | 0x00     | D0-D7=0 to 7; DSP=16; Host=11 | D0-D7=28,1 to 7; DSP=16; Host=29 |

| Farallel   | 1                     | 0x20     | n/a                           | D0-D7=0 to 7; DSP=16; Host=11    |

|            | 0                     | 0x01     | TX=29; RX=28                  | TX=29; RX=28                     |

|            | 1                     | 0x21     | TX=16; RX=17                  | TX=16; RX=17                     |

| SCIA       | 2                     | 0x41     | TX=8; RX=9                    | TX=8; RX=9                       |

|            | 3                     | 0x61     | TX=48; RX=49                  | TX=2; RX=3                       |

|            | 4                     | 0x81     | TX=24; RX=25                  | TX=16; RX=3                      |

|            | 0                     | 0x02     | TX=32; RX=33                  | TX=4; RX=5                       |

| CANA       | 1                     | 0x22     | TX=4; RX=5                    | TX=32; RX=33                     |

| CANA       | 2                     | 0x42     | TX=31; RX=30                  | TX=2; RX=3                       |

|            | 3                     | 0x62     | TX=37; RX=35                  | n/a                              |

<sup>(1)</sup> Consult device datasheet to ensure that the GPIOs assigned to these options are available for a specific package

Table 11. Bootloaders and GPIO Assignment Comparison (continued)

| Bootloader | Option <sup>(1)</sup> | BOOTDEFx | F28004x                          | F28002x                        |

|------------|-----------------------|----------|----------------------------------|--------------------------------|

|            | 0                     | 0x06     | n/a                              | SIMO=2; SOMI=1; CLK=3; STE=5   |

|            | 1                     | 0x26     | SIMO=8; SOMI=10; CLK=9; STE=11   | SIMO=16; SOMI=1; CLK=3; STE=0  |

| SPI        | 2                     | 0x46     | SIMO=54; SOMI=55; CLK=56; STE=57 | SIMO=8; SOMI=10; CLK=9; STE=11 |

|            | 3                     | 0x66     | SIMO=16; SOMI=17; CLK=56; STE=57 | SIMO=8; SOMI=17; CLK=9; STE=11 |

|            | 4                     | 0x86     | SIMO=8; SOMI=17; CLK=9; STE=11   | n/a                            |

|            | 0                     | 0x07     | SDA=32; SCL=33                   | SDA=32; SCL=33                 |

| I2C        | 1                     | 0x27     | n/a                              | SDA=0; SCL=1                   |

| 120        | 2                     | 0x47     | SDA=26; SCL=27                   | SDA=10; SCL=8                  |

|            | 3                     | 0x67     | SDA=42; SCL=43                   | n/a                            |

### **Table 12. Boot Modes Comparison**

| Boot Mode | Option | BOOTDEFx | F28004x                             | F28002x                            |

|-----------|--------|----------|-------------------------------------|------------------------------------|

|           | 0      | 0x03     | Entry=0x00080000; Bank/Sector=0/0   | Entry=0x00080000; Bank/Sector=0/0  |

| Flash     | 1 0:   |          | Entry=0x0008EFF0; Bank/Sec\tor=0/14 | Entry=0x00084000; Bank/Sector=0/4  |

| riasii    | 2      | 0x43     | Entry=0x00090000; Bank/Sector=1/0   | Entry=0x00088000; Bank/Sector=0/8  |

|           | 3      | 0x63     | Entry=0x0009EFF0; Bank/Sector=1/14  | Entry=0x0008EFF0; Bank/Sector=0/14 |

| Moit      | 0      | 0x04     | Watchdog enabled                    | Watchdog enabled                   |

| vvaii     | Wait 1 |          | Watchdog disabled                   | Watchdog disabled                  |

| RAM       | 0      | 0x05     | Entry=0x00000000                    | Entry=0x00000000                   |

### 3.5.3 CLA, CLB, DMA and Motor Control Libraries

There are no functional changes in CLB, DMA and Motor Control Libraries.

Table 13. CLA, CLB, DMA and Motor Control Libraries

| Modules                        | F28004x               | F28002x               |

|--------------------------------|-----------------------|-----------------------|

| CLA                            | Yes                   | No                    |

| CLB                            | 4 tiles               | 2 tiles               |

| DMA                            | 6 channels            | 6 channels            |

| Motor Control Libraries in ROM | Available in F28004xC | Available in F28002xC |

### 3.5.4 ERAD

The ERAD module has a number of changes between F28004x and F28002x as highlighted in Table 14.

**Table 14. ERAD Module Differences**

| Module | Category  | F28004x                         | F28002x                     | Note                                                                                       |  |  |  |  |

|--------|-----------|---------------------------------|-----------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

|        |           | -                               | Event Masking and Exporting | EBC Unit on F28002x supports event OR/AND, masking and exporting                           |  |  |  |  |

|        |           | -                               | Cumulative Mode             | SEC Unit on F28002x supports a cummulative mode over several start/stop events             |  |  |  |  |

|        | Features  | -                               | CRC Unit                    | F28002x has CRC units to monitor CPU buses and compute CRC when self-test code is executed |  |  |  |  |

|        |           | 32 Event<br>Selector<br>Options | 128 Event Selector Options  | Connections to ADC, CMPSS, EPWM and other sources have been added to F28002x               |  |  |  |  |

|        |           | -                               | GLBL_NMI_CTL                | Global Debug NMI Control                                                                   |  |  |  |  |

| ERAD   |           | -                               | GLBL_EVENT_AND_MASK         | Global Bus Comparator Event AND Mask Register                                              |  |  |  |  |

|        |           | -                               | GLBL_EVENT_OR_MASK          | Global Bus Comparator Event OR Mask Register                                               |  |  |  |  |

|        |           | -                               | GLBL_AND_EVENT_INT_MASK     | Global AND Event Interrupt Mask Register                                                   |  |  |  |  |

|        |           | -                               | GLBL_OR_EVENT_INT_MASK      | Global OR Event Interrupt Mask Register                                                    |  |  |  |  |

|        | Registers | -                               | CTM_INPUT_SEL_2             | Counter Input Select Extension Register                                                    |  |  |  |  |

|        |           | -                               | CTM_INPUT_COND              | Counter Input Conditioning Register                                                        |  |  |  |  |

|        |           | -                               | CRC_GLOBAL_CTRL             | CRC Global Control Register                                                                |  |  |  |  |

|        |           | =                               | CRC_CURRENT                 | Reads Current CRC Value                                                                    |  |  |  |  |

|        |           | -                               | CRC_SEED                    | CRC Seed Register                                                                          |  |  |  |  |

|        |           | -                               | CRC_QUALIFIER               | CRC Compute Qualification Register                                                         |  |  |  |  |

### 3.5.5 GPIO

The GPIO module in F28002x has a new registers for reading back the value written in GPyDAT. These registers is not available in F28004x. The registers are GPyDAT\_R and description is as follows:

• **GPyDAT\_R** are read-only registers which return the values written on GPyDAT registers instead of pin status. Writes to these registers have no effect.

### 3.6 Power Management

There are different options to power the F28004x and F28002x devices. F28004x has flexibility in that it supports both dual-rail (3.3 V and 1.2 V) or single-rail (3.3 V) with internal VREG or DCDC to provide the 1.2 V rail. F28002x only supports single-rail 3.3 V supply with the internal VREG providing the 1.2 V rail. This section describes the power management differences and similarities between the two devices.

#### LDO/VREG 3.6.1

The F28002x device supports internal VREG only. External VREG is not supported because the VREGENZ pin on the F28002x device has been converted to a GPIO, GPIO39. F28004x supports both internal VREG or external source.

#### 3.6.2 **DCDC**

The F28002x device does not have a DCDC while F28004x has an internal DCDC that requires minimal external components (inductor and capacitor).

#### POR/BOR 3.6.3

There are no functional changes for the POR and BOR.

### 3.7 **Power Consumption**

There is not a significant difference in power consumption between the F28002x and the F28004x if the same number of peripherals are being utilized and internal VREG is being used for both. However, since the F28004x device has the option to supply VREG externally or through the internal DCDC, it has the capability to be more power efficient.

### 3.8 Memory Module Changes

The available FLASH and RAM memories on the F28002x family of devices are reduced compared to the F28004x devices. For specific details on available memory capacity on the F28002x family of devices, see the TMS320F28002x microcontrollers data sheet (SPRSP45).

#### 3.8.1 **FLASH**

F28004x has a total of 256 KBytes of Flash memory in two banks while F28002x has 128KBytes in one

#### 3.8.2 RAM

F28004x has a total RAM size of 100.5KBytes while F28002x has 24KBytes.

#### 3.9 GPIO Multiplexing Diagram

Table 16 outlines the differences and similarities that exist in the GPIO mux between F28002x and F28004x. The legend for this table is Table 15. The main changes highlighted in Table 16 are the absence of SDFM mux positions and the DCDC GPIO support pins from F28002x. The other notable change is the addition of HIC mux positions and the use of X1 as a GPIO pin in the F28002x device if external clock is not used.

NOTE: This comparison guide focuses on the super-set devices F280049 and F280025. The Qgrade Q100 Part Numbers do not have GPIO12 or GPIO13 in either device.

### Table 15. Mux Legend

| Color | Description                              |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

|       | mux function common for both devices     |  |  |  |  |  |  |  |

|       | ux function applicable only for F28004x  |  |  |  |  |  |  |  |

|       | mux function applicable only for F28002x |  |  |  |  |  |  |  |

### **Table 16. GPIO Mux Table Comparison**

|          | 8.12 1 2 3 5 6 7 9 10 11 13 14 15 |                  |             |                  |                  |                  |                  |                     |                     |              |                     |              |       |  |

|----------|-----------------------------------|------------------|-------------|------------------|------------------|------------------|------------------|---------------------|---------------------|--------------|---------------------|--------------|-------|--|

| 0,4,8,12 | 1                                 | 2                | 3           | 5                | 6                | 7                | 9                | 10                  | 11                  | 13           | 14                  | 15           | ALT   |  |

| GPIO0    | EPWM1_A                           |                  |             |                  | I2CA_SDA         | SPIA_STE         | FSIRXA_CLK       |                     | CLB_OUTPUTX<br>BAR8 |              |                     | HIC_BASESEL1 |       |  |

| GPIO1    | EPWM1_B                           |                  |             |                  | I2CA_SCL         | SPIA_SOMI        |                  |                     | CLB_OUTPUTX<br>BAR7 | HIC_A2       | FSI_TDM_TX1         | HIC_D10      |       |  |

| GPIO2    | EPWM2_A                           |                  |             | OUTPUTXBAR1      | PMBUSA_SDA       | SPIA_SIMO        | SCIA_TX          | FSIRXA_D1           | I2CB_SDA            | HIC_A1       | CANA_TX             | HIC_D9       |       |  |

| GPIO3    | EPWM2_B                           | OUTPUTXBAR2      |             | OUTPUTXBAR2      | PMBUSA_SCL       | SPIA_CLK         | SCIA_RX          | FSIRXA_D0           | I2CB_SCL            | HIC_NOE      | CANA_RX             | HIC_D4       |       |  |

| GPIO4    | EPWM3_A                           |                  |             | OUTPUTXBAR3      | CANA_TX          | SPIB_CLK         | EQEP2_STROB<br>E | FSIRXA_CLK          | CLB_OUTPUTX<br>BAR6 | HIC_BASESEL2 |                     | HIC_NWE      |       |  |

| GPIO5    | EPWM3_B                           |                  | OUTPUTXBAR3 |                  | CANA_RX          | SPIA_STE         | FSITXA_D1        | CLB_OUTPUTX<br>BAR5 |                     | HIC_A7       | HIC_D4              | HIC_D15      |       |  |

| GPIO6    | EPWM4_A                           | OUTPUTXBAR4      | SYNCOUT     | EQEP1_A          | CANB_TX          | SPIB_SOMI        | FSITXA_D0        |                     | FSITXA_D1           | HIC_NBE1     | CLB_OUTPUTX<br>BAR8 | HIC_D14      |       |  |

| GPIO7    | EPWM4_B                           |                  | OUTPUTXBAR5 | EQEP1_B          | CANB_RX          | SPIB_SIMO        | FSITXA_CLK       | CLB_OUTPUTX<br>BAR2 |                     | HIC_A6       |                     | HIC_D14      |       |  |

| GPIO8    | EPWM5_A                           | CANB_TX          | ADCSOCAO    | EQEP1_STROB<br>E | SCIA_TX          | SPIA_SIMO        | I2CA_SCL         | FSITXA_D1           | CLB_OUTPUTX<br>BAR5 | HIC_A0       | FSI_TDM_CLK         | HIC_D8       |       |  |

| GPIO9    | EPWM5_B                           | SCIB_TX          | OUTPUTXBAR6 | EQEP1_INDEX      | SCIA_RX          | SPIA_CLK         |                  | FSITXA_D0           | LINB_RX             | HIC_BASESEL0 | I2CB_SCL            | HIC_NRDY     |       |  |

| GPIO10   | EPWM6_A                           | CANB_RX          | ADCSOCBO    | EQEP1_A          | SCIB_TX          | SPIA_SOMI        | I2CA_SDA         | FSITXA_CLK          | LINB_TX             | HIC_NWE      | FSI_TDM_TX0         |              |       |  |

| GPIO11   | EPWM6_B                           | SCIB_RX          | OUTPUTXBAR7 | EQEP1_B          | SCIB_RX          | SPIA_STE         | FSIRXA_D1        | LINB_RX             | EQEP2_A             | SPIA_SIMO    | HIC_D6              | HIC_NBE0     |       |  |

| GPIO12   | EPWM7_A                           | CANB_TX          |             | EQEP1_STROB<br>E | SCIB_TX          | PMBUSA_CTL       | FSIRXA_D0        | LINB_TX             | SPIA_CLK            | CANA_RX      | HIC_D13             | HIC_INT      |       |  |

| GPIO13   | EPWM7_B                           | CANB_RX          |             | EQEP1_INDEX      | SCIB_RX          | PMBUSA_ALER<br>T | FSIRXA_CLK       | LINB_RX             | SPIA_SOMI           | CANA_TX      | HIC_D11             | HIC_D5       |       |  |

| GPIO14   | EPWM8_A                           | SCIB_TX          |             | I2CB_SDA         | OUTPUTXBAR3      | PMBUSA_SDA       | SPIB_CLK         | EQEP2_A             | LINB_TX             | EPWM3_A      | CLB_OUTPUTX<br>BAR7 | HIC_D15      |       |  |

| GPIO15   | EPWM8_B                           | SCIB_RX          |             | I2CB_SCL         | OUTPUTXBAR4      | PMBUSA_SCL       | SPIB_STE         | EQEP2_B             | LINB_RX             | EPWM3_B      | CLB_OUTPUTX<br>BAR6 | HIC_D12      |       |  |

| GPIO16   | SPIA_SIMO                         | CANB_TX          | OUTPUTXBAR7 | EPWM5_A          | SCIA_TX          | SD1_D1           | EQEP1_STROB<br>E | PMBUSA_SCL          | XCLKOUT             | EQEP2_B      | SPIB_SOMI           | HIC_D1       |       |  |

| GPIO17   | SPIA_SOMI                         | CANB_RX          | OUTPUTXBAR8 | EPWM5_B          | SCIA_RX          | SD1_C1           | EQEP1_INDEX      | PMBUSA_SDA          | CANA_TX             |              |                     | HIC_D2       |       |  |

| GPIO18   | SPIA_CLK                          | SCIB_TX          | CANA_RX     | EPWM6_A          | I2CA_SCL         | SD1_D2           | EQEP2_A          | PMBUSA_CTL          | XCLKOUT             | LINB_TX      | FSI_TDM_CLK         | HIC_INT      | X2    |  |

| GPIO19   | SPIA_STE                          |                  | CANA_TX     | EPWM6_B          | I2CA_SDA         |                  | EQEP2_B          | PMBUSA_ALER<br>T    | CLB_OUTPUTX<br>BAR1 | LINB_RX      | FSI_TDM_TX0         | HIC_NBE0     | X1    |  |

| GPIO22   | EQEP1_<br>STROBE                  |                  | SCIB_TX     |                  | SPIB_CLK         | SD1_D4           | LINA_TX          | CLB_OUTPUTX<br>BAR1 | LINB_TX             | HIC_A5       | EPWM4_A             | HIC_D13      | VFBSW |  |

| GPIO23   | EQEP1_INDEX                       |                  |             |                  | SPIB_STE         |                  | LINA_RX          |                     | LINB_RX             | HIC_A3       | EPWM4_B             | HIC_D11      | VSW   |  |

| GPIO24   | OUTPUTXBAR1                       | EQEP2_A          |             | EPWM8_A          | SPIB_SIMO        | SD1_D1           | LINB_TX          | PMBUSA_SCL          | SCIA_TX             | ERRORSTS     |                     | HIC_D3       |       |  |

| GPIO25   | OUTPUTXBAR2                       | EQEP2_B          |             | EQEP1_A          | SPIB_SOMI        | SD1_C1           | FSITXA_D1        | PMBUSA_SDA          | SCIA_RX             |              | HIC_BASESEL0        |              |       |  |

| GPIO26   | OUTPUTXBAR3                       | EQEP2_INDEX      |             | OUTPUTXBAR3      | SPIB_CLK         | SD1_D2           | FSITXA_D0        | PMBUSA_CTL          | I2CA_SDA            |              | HIC_D0              | HIC_A1       |       |  |

| GPIO27   | OUTPUTXBAR4                       | EQEP2_<br>STROBE |             | OUTPUTXBAR4      | SPIB_STE         | SD1_C2           | FSITXA_CLK       | PMBUSA_ALER<br>T    | I2CA_SCL            |              | HIC_D1              | HIC_A4       |       |  |

| GPIO28   | SCIA_RX                           |                  | EPWM7_A     | OUTPUTXBAR5      | EQEP1_A          | SD1_D3           | EQEP2_STROB<br>E | LINA_TX             | SPIB_CLK            | ERRORSTS     | I2CB_SDA            | HIC_NOE      |       |  |

| GPIO29   | SCIA_TX                           |                  | EPWM7_B     | OUTPUTXBAR6      | EQEP1_B          | SD1_C3           | EQEP2_INDEX      | LINA_RX             | SPIB_STE            | ERRORSTS     | I2CB_SCL            | HIC_NCS      |       |  |

| GPIO30   | CANA_RX                           |                  | SPIB_SIMO   | OUTPUTXBAR7      | EQEP1_STROB<br>E | SD1_D4           | FSIRXA_CLK       |                     | EPWM1_A             |              | HIC_D8              |              |       |  |

| GPIO31   | CANA_TX                           |                  | SPIB_SOMI   | OUTPUTXBAR8      | EQEP1_INDEX      | SD1_C4           | FSIRXA_D1        |                     | EPWM1_B             |              | HIC_D10             |              |       |  |

## **Table 16. GPIO Mux Table Comparison (continued)**

| 0,4,8,12 | 1           | 2       | 3           | 5                | 6          | 7          | 9           | 10                  | 11                  | 13       | 14          | 15           | ALT |

|----------|-------------|---------|-------------|------------------|------------|------------|-------------|---------------------|---------------------|----------|-------------|--------------|-----|

| GPIO32   | I2CA_SDA    |         | SPIB_CLK    | EPWM8_B          | LINA_TX    | SD1_D3     | FSIRXA_D0   | CANA_TX             |                     | ADCSOCBO |             | HIC_INT      |     |

| GPIO33   | I2CA_SCL    |         | SPIB_STE    | OUTPUTXBAR4      | LINA_RX    | SD1_C3     | FSIRXA_CLK  | CANA_RX             | EQEP2_B             | ADCSOCAO |             | HIC_D0       |     |

| GPIO34   | OUTPUTXBAR1 |         |             |                  | PMBUSA_SDA |            |             |                     |                     | HIC_NBE1 | I2CB_SDA    | HIC_D9       |     |

| GPIO35   | SCIA_RX     |         | I2CA_SDA    | CANA_RX          | PMBUSA_SCL | LINA_RX    | EQEP1_A     | PMBUSA_CTL          |                     |          | HIC_NWE     | TDI          |     |

| GPIO37   | OUTPUTXBAR2 |         | I2CA_SCL    | SCIA_TX          | CANA_TX    | LINA_TX    | EQEP1_B     | PMBUSA_ALER<br>T    |                     |          | HIC_NRDY    | TDO          |     |

| GPIO39   |             |         |             |                  | CANB_RX    | FSIRXA_CLK | EQEP2_INDEX |                     | CLB_OUTPUTX<br>BAR2 | SYNCOUT  | EQEP1_INDEX | HIC_D7       |     |

| GPIO40   | SPIB_SIMO   |         |             | EPWM2_B          | PMBUSA_SDA | FSIRXA_D0  | SCIB_TX     | EQEP1_A             | LINB_TX             |          | HIC_NBE1    | HIC_D5       |     |

| GPIO41   |             |         |             | EPWM2_A          | PMBUSA_SCL | FSIRXA_D1  |             | EQEP1_B             | LINB_RX             | HIC_A4   | SPIB_SOMI   | HIC_D12      |     |

| GPIO42   |             | LINA_RX | OUTPUTXBAR5 | PMBUSA_CTL       | I2CA_SDA   |            |             | EQEP1_STROB<br>E    | CLB_OUTPUTX<br>BAR3 |          | HIC_D2      | HIC_A6       |     |

| GPIO43   |             |         | OUTPUTXBAR6 | PMBUSA_ALER<br>T | I2CA_SCL   |            |             | EQEP1_INDEX         | CLB_OUTPUTX<br>BAR4 |          | HIC_D3      | HIC_A7       |     |

| GPIO44   |             |         | OUTPUTXBAR7 | EQEP1_A          |            | FSITXA_CLK |             | CLB_OUTPUTX<br>BAR3 |                     | HIC_D7   |             | HIC_D5       |     |

| GPIO45   |             |         | OUTPUTXBAR8 |                  |            | FSITXA_D0  |             | CLB_OUTPUTX<br>BAR4 |                     |          |             | HIC_D6       |     |

| GPIO46   |             |         | LINA_TX     |                  |            | FSITXA_D1  |             |                     |                     |          |             | HIC_NWE      |     |

| GPIO56   | SPIA_CLK    |         |             | EQEP2_STROB<br>E | SCIB_TX    | SD1_D3     | SPIB_SIMO   |                     | EQEP1_A             |          |             |              |     |

| GPIO57   | SPIA_STE    |         |             | EQEP2_INDEX      | SCIB_RX    | SD1_C3     | SPIB_SOMI   |                     | EQEP1_B             |          |             |              |     |

| GPIO58   |             |         |             | OUTPUTXBAR1      | SPIB_CLK   | SD1_D4     | LINA_TX     | CANB_TX             | EQEP1_STROB<br>E    |          |             |              |     |

| GPIO59   |             |         |             | OUTPUTXBAR2      | SPIB_STE   | SD1_C4     | LINA_RX     | CANB_RX             | EQEP1_INDEX         |          |             |              |     |

| AIO224   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_A3       |     |

| AIO225   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_NWE      |     |

| AIO226   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_A1       |     |

| AIO227   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_NBE0     |     |

| AIO228   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_A0       |     |

| AIO230   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_BASESEL2 |     |

| AIO231   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_BASESEL1 |     |

| AIO232   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_BASESEL0 |     |

| AIO233   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_A4       |     |

| AIO237   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_A6       |     |

| AIO238   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_NCS      |     |

| AIO239   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_A5       |     |

| AIO241   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_NBE1     |     |

| AIO242   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_A2       |     |

| AIO244   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_A7       |     |

| AIO245   |             |         |             |                  |            |            |             |                     |                     |          |             | HIC_NOE      |     |

### 3.10 Analog Multiplexing Diagram

Table 18 outlines the differences and similarities that exist in the analog mux between F28002x and F28004x. The legend for this table is Table 17. The main changes highlighted in Table 18 are the absence of ADCB, DAC, PGA and the reduction of the number of CMPSS modules in F28002x from the seven that exist in F28004x to four. The other notable change is that in the F28004x device, the analog modules were grouped. This grouping does not exist in F28002x. This is particularly important for the CMPSS as highlighted in the table.

Table 17. Mux Legend

| Color | Description                              |

|-------|------------------------------------------|

|       | mux function common for both devices     |

|       | mux function applicable only for F28004x |

|       | mux function applicable only for F28002x |

## Table 18. F28004x and F28002x Analog Mux Table Differences

| (F28004x Pin Name) | F28004x    | PKG     |              | Always | Connected ( | NO MUX)  |      |                  | Comparator Su    | ıbsystem (MUX)      |                  |           |

|--------------------|------------|---------|--------------|--------|-------------|----------|------|------------------|------------------|---------------------|------------------|-----------|

| F28002x Pin Name   | Group Name | 64 PM   | ADCA         | ADCB   | ADCC        | PGA      | DAC  | High Positive    | High Negative    | Low Positive        | Low Negative     | AIO Input |

| VREFHIA            | -          | 16      |              |        |             |          |      |                  |                  |                     |                  |           |

| VREFHIB            | -          |         |              |        |             |          |      |                  |                  |                     |                  |           |

| VREFHIC            | -          |         |              |        |             |          |      |                  |                  |                     |                  |           |

| VREFLOA            | -          | 17      | A13          |        |             |          |      |                  |                  |                     |                  |           |

| VREFLOB            | -          |         |              | B13    |             |          |      |                  |                  |                     |                  |           |

| VREFLOC            | -          |         |              |        | C13         |          |      |                  |                  |                     |                  |           |

|                    |            | F28004x | Analog Group | 1      |             |          |      |                  |                  | F28004x CMP1        |                  |           |

| ( A3 )             | G1_ADCAB   |         | A3           |        |             |          |      | HPMXSEL = 3      | HNMXSEL = 0      | LPMXSEL = 3         | LNMXSEL = 0      | AIO233    |

| ( A2/B6/PGA1_OF )  | PGA1_OF    | 9       | A2           | B6     | C9          | PGA1_OF  |      | HPMXSEL = 0      |                  | LPMXSEL = 0         |                  | AIO224    |

| A2/C9              |            |         |              |        |             |          |      |                  |                  |                     |                  |           |

| (CO)               | G1_ADCC    | 12      | A11          |        | C0          |          |      | HPMXSEL = 1      | HNMXSEL = 1      | LPMXSEL = 1         | LNMXSEL = 1      | AIO237    |

| A11/C0             |            |         |              |        |             |          |      |                  |                  |                     |                  |           |

| ( PGA1_IN )        | PGA1_IN    |         |              |        |             | PGA1_IN  |      | HPMXSEL = 2      |                  | LPMXSEL = 2         |                  |           |

| ( PGA1_GND )       | PGA1_GND   | 10      | A15          |        | C7          | PGA1_GND |      | HPMXSEL = 3      | HNMXSEL = 0      | LPMXSEL = 3         | LNMXSEL = 0      | AIO233    |

| A15/C7             |            |         |              |        |             |          |      |                  |                  |                     |                  |           |

| (-)                | PGA1_OUT   |         | A11          | B7     |             | PGA1_OUT |      | HPMXSEL = 4      |                  | LPMXSEL = 4         |                  |           |

|                    |            | F28004x | Analog Group | 2      |             |          |      |                  | •                | F28004x CMP2        |                  | I.        |

| (A5)               | G2_ADCAB   |         | A5           |        |             |          |      | HPMXSEL = 3      | HNMXSEL = 0      | LPMXSEL = 3         | LNMXSEL = 0      | AIO234    |

| ( A4/B8/PGA2_OF )  | PGA2_OF    | 23      | A4           | B8     | C14         | PGA2_OF  |      | HPMXSEL = 0      | CMP4_HNMXSEL = 0 | LPMXSEL = 0         | CMP4_LNMXSEL = 0 | AIO225    |

| A4/C14             |            |         |              |        |             |          |      | CMP4_HPMXSEL = 3 |                  | CMP4_LPMXSEL = 3    |                  |           |

| (C1)               | G2_ADCC    | 18      | A12          |        | C1          |          |      | HPMXSEL = 1      | HNMXSEL = 1      | LPMXSEL = 1         | LNMXSEL = 1      | AIO238    |

| A12/C1             |            |         |              |        |             |          |      | CMP4_HPMXSEL = 2 |                  | CMP4_LPMXSEL = 2    |                  |           |

| ( PGA2_IN )        | PGA2_IN    |         |              |        |             | PGA2_IN  |      | HPMXSEL = 2      |                  | LPMXSEL = 2         |                  |           |

| ( PGA2_GND )       | PGA2_GND   | 20      | A8           |        | C11         | PGA2_GND |      | HPMXSEL = 4      |                  | LPMXSEL = 4         |                  | AIO241    |

| A8/C11             |            |         |              |        |             |          |      | CMP4_HPMXSEL = 4 |                  | $CMP4\_LPMXSEL = 4$ |                  |           |

| (-)                | PGA2_OUT   |         | A12          | В9     |             | PGA2_OUT |      | HPMXSEL = 4      |                  | LPMXSEL = 4         |                  |           |

|                    |            | F28004x | Analog Group | 3      | •           |          |      |                  |                  | F28004x CMP3        |                  |           |

| (B3/VDAC)          | G3_ADCAB   | 8       | A3           | B3     | C5          |          | VDAC | HPMXSEL = 3      | HNMXSEL = 0      | LPMXSEL = 3         | LNMXSEL = 0      | AIO242    |

| A3/C5/VDAC         |            |         |              |        |             |          |      |                  |                  |                     |                  |           |

| ( B2/C6/PGA3_OF )  | PGA3_OF    | 7       |              | B2     | C6          | PGA3_OF  |      | HPMXSEL = 0      |                  | LPMXSEL = 0         |                  | AIO226    |

| C6                 |            |         |              |        |             |          |      |                  |                  |                     |                  |           |

| (C2)               | G3_ADCC    | 13      | A5           |        | C2          |          |      | HPMXSEL = 1      | HNMXSEL = 1      | LPMXSEL = 1         | LNMXSEL = 1      | AIO244    |

| A5/C2              |            |         |              |        |             |          |      |                  |                  |                     |                  |           |

| ( PGA3_IN )        | PGA3_IN    |         |              |        |             | PGA3_IN  |      | HPMXSEL = 2      |                  | LPMXSEL = 2         |                  |           |

| ( PGA3_GND )       | PGA3_GND   | 10      |              |        |             | PGA3_GND |      |                  |                  |                     |                  |           |

| (-)                | PGA3_OUT   |         |              | B10    |             | PGA3_OUT |      | HPMXSEL = 4      |                  | LPMXSEL = 4         |                  |           |