# Processor-SDK RTOS Power Management and Measurement

Vrinda Khetan, Elvita Lobo, and Justin Sobota

## ABSTRACT

Processor-SDK RTOS provides out-of-the-box power management examples that empower customers to tailor Sitara processors' (ARM and DSP) power-performance points per use case. You can configure all supported operating points and run CPU Idle and Dhrystone benchmarking workloads while employing a minimal kernel with real-time assurance. This application report provides an overview of the Processor-SDK RTOS power management library and power consumption data on Sitara processors.

## Contents

| 1 | Introduction                         | 1 |

|---|--------------------------------------|---|

| 2 | Processor-SDK-RTOS Power Management  | 2 |

| 3 | Processor-SDK-RTOS Power Consumption | 4 |

| 4 | References                           | 5 |

## List of Figures

| 1 | Power Management Software Stack                                       | 3 |

|---|-----------------------------------------------------------------------|---|

| 2 | SOC-PMIC Communication Over I2C Bus                                   | 3 |

| 3 | Dhrystone Processor-SDK RTOS Power Measurement Data for AM335x GP EVM | 5 |

## Trademarks

Sitara is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

# 1 Introduction

With the advent of real-time automation and sensing, power management is proving to be increasingly important in system-on-chip (SoC) devices used in industrial and building or home automation applications.

The discussion topics are applicable for Sitara<sup>™</sup> processors such as AM335x, AM437x and AM57x. This paper provides an introduction to Processor-SDK RTOS power management and measurement using AM335x as a vehicle for discussion.

**NOTE:** It is important to note that the measurements are within datasheet recommendations. Extreme operating conditions that may have an effect on device lifetime have not been considered. For example, operating the device under extreme operating conditions such as high voltage and frequency over high temperatures while running heavy applications involving PCIe or HDMI may shorten the lifetime of the device.

# 1.1 Why is Power Management Important?

Wherever possible, system engineers are shying away from bulky thermal solutions and cooling fans due to reliability concerns. Heat sinks and cooling fans become unavoidable when device power consumption exceeds 5W, posing serious reliability concerns over time. Thermal management is the main focus of the mechanical design for industrial applications such as programmable logic controllers or motor control.

## www.ti.com

# 1.2 Power Management on Linux and RTOS

Linux users have had a variety of out of box power management features at their fingertips for complex systems where power management is mostly controlled in kernel space. Systems engineers that use RTOS as their choice of operating system are frequently looking for a solution where the application has more control. RTOS power management features are perfect for systems that require a minimal kernel while giving autonomous control to the application and providing real-time guarantees. Legacy RTOS devices also stand to benefit from the new RTOS power management features in Texas Instruments' Processor Software Development Kit (SDK) RTOS, based on TI-RTOS. TI-RTOS provides application program interfaces that can be used to easily configure operating points for desired power and performance.

# 1.3 Which Applications Benefit From RTOS Power Management?

In building automation applications, such as meeting room controllers that may be idle up to 99% of the time, low power devices are preferred, thereby reducing power consumption. In factory automation, when a factory worker uses a handheld battery powered controller, longer period between charges is preferred. Similarly, in defense applications, battery operated radios need low power devices.

In military applications as well as factory automation, users want real time guarantees. In such applications RTOS may be preferable.

## 1.4 Low Power Sitara Processors

Sitara Processors, such as AM335x, provide low power consumption which prolongs battery life and reduces heat emissions, enabling convenient, compact, fan-less applications. Currently, AM335x supports various operating points for active and sleep states as well as heavy workload operating modes.

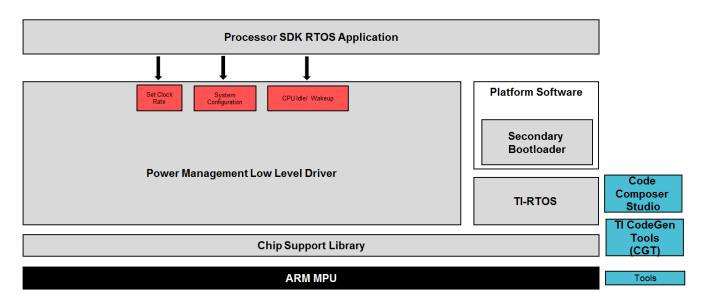

## 2 Processor-SDK-RTOS Power Management

The Texas Instruments Processor Software Development Kit (Processor-SDK) is a single scalable software platform that offers streamlined development across TI processors, including both Sitara ARM and DSP devices. The Processor-SDK for TI-RTOS provides fundamental platform software and tools for development, deployment and execution of RTOS-based applications.

Processor-SDK-RTOS provides power management features for Sitara devices. The Power Management (PM) software APIs supply a basic power management framework. PM APIs are supported for ARM on AM335x GP EVM and AM437x GP EVM as well as M4, DSP and ARM on AM572x GP EVM. In general, the key features supported by this framework include:

- CPU Operating Performance Points

- Low Power CPU Idle

- Enable/Disable Control of Device Modules and Clocks

- Thermal Management

- Power Event Notification Infrastructure

Figure 1. Power Management Software Stack

# 2.1 CPU Operating Performance Points

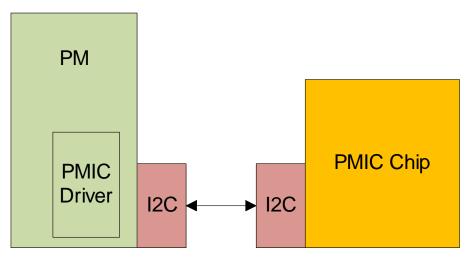

The PM framework has the capability to switch devices between different Operating Performance Points (OPP) at run time. These OPP are aligned with the device specifications. When the PM framework's OPP modification API is invoked, the PM software stack changes the voltage level and frequency. The PM software stack modifies the voltage level by accessing the device's Power Management Integrated Chip, or PMIC, driver via the I2C bus.

Figure 2. SOC-PMIC Communication Over I2C Bus

PM adjusts the processor frequency by updating the multiplier and divider settings of the Phased Lock Loop, or PLL, feeding the processor. Detailed information of OPP voltage and frequency settings for the ARM master core, MPU, on Sitara devices can be found in the datasheets for AM335x, AM437x and AM572x GP EVM.

**NOTE:** Currently, AM571x and AM570x are not supported.

# 2.2 Low Power CPU Idle

The PM framework enables Sitara processor low power modes when the system is idle. PM provides instrumentation through which the Operating System (OS) can invoke the CPU to go into an idle mode to save power. Typically, the low power capabilities are invoked during OS idle. When the low-power capabilities are invoked a couple things happen:

- The CPU clock state is moved to the auto-clock gate. As a result, when the CPU itself enters a low power state the device hardware will clock gate the CPU clock.

- CPU local memory retention is enabled (AM572x MPU only)

- CPU power domain configured to go to off state on CPU transition to low power state (AM572x MPU, M4, and C66x only)

- CPU WFI instruction is executed putting the CPU into a low power state and, as described above, clock gating the CPU

The CPU can be brought out of low power idle via any interrupt source configured for wakeup.

# 2.3 Device Module and Clock Enable/Disable Control

PM has a set of application program interfaces (APIs) that provide system control of individual device modules, including peripherals and clocks. The APIs can be used to enable and disable subsections of the device and its clock tree on demand. This capability allows customization of the device's power profile based on the needs of the use case.

# 2.4 Thermal Management

The PM framework also provides a set of thermal management capabilities, currently supported only for the AM572x device family.

The AM572x devices contain on-die temperature sensors with high and low temperature threshold alerts. PM ties to these alerts and provides a basic temperature threshold interrupt handler that can be expanded upon by the OS through a callback functionality implemented within PM's interrupt handler. The OS can use the callback registration functionality to take actions specific to which threshold was hit, high or low, in order to bring the temperature in line with what is expected for the use case. In other words, if a high temperature is detected the CPU can move the device into a low power consumption state to reduce the temperature. You can specify which mode the device should move to, for example, using PM APIs to lower OPP or enter idle mode.

# 2.5 Power Event Notification Infrastructure

Most actions taken by the PM framework are tracked and instrumented with an event notification scheme. The PM event notification scheme allows the OS to register callback functions with the PM infrastructure which the OS can specify be invoked during certain power events. Through these means the OS can gain feedback on the actions taking place within the PM infrastructure. A system designer can also supplement PM events with additional focused device actions based on the use case the system designer is targeting.

# 3 Processor-SDK-RTOS Power Consumption

The Sitara RTOS Power Measurement metrics contained in this document serve to give users a better understanding of AM335x active power behaviors -- making it easier to determine a suitable configuration to meet a given power budget. If you are interested in power measurement information about other Sitara devices such as AM437x and AM572x, please post your question on the Sitara<sup>™</sup> Processors Section of the TI E2E Support Community.

Power consumption is highly dependent on the individual user's application; however, this document focuses on providing AM335x power measurement data during OS idle (WFI, wait for interrupt) mode.

AM335x Power Estimation Tool wiki: The Power Estimation Tool (PET) provides insight into gaining power consumption of select Sitara processors. The tool includes the ability to choose multiple application scenarios and understand the power consumption as well as how advanced power saving techniques can be applied to further reduce overall power consumption.

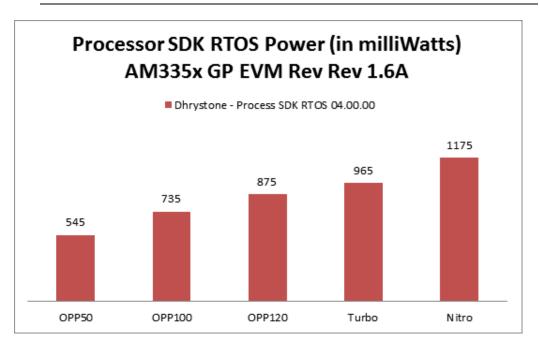

Figure 3 shows how a collection of real total power measurements (all power rails) were measured on an AM335x GP EVM with a high-precision digital multimeter. All tests were not conducted in a controlled environment. The ambient room temperature was approximately 25°C.

#### NOTE: These test cases have not been optimized for low power.

## Figure 3. Dhrystone Processor-SDK RTOS Power Measurement Data for AM335x GP EVM

For additional details about the AM335x processor, please visit the TI.com product page.

## 4 References

- AM335x Sitara<sup>™</sup> Processors Data Manual

- AM335x and AMIC110 Sitara™ Processors Technical Reference Manual

- AM335x Sitara™ Processors Silicon Revisions 2.1, 2.0, 1.0 Silicon Errata

- AM335x Linux Power Management User Guide wiki page

- AM335x Evaluation Module

- AM335x General Purpose EVM HW User Guide wiki page

- AM335x General Purpose EVM Board Design Files wiki page

- AM335x Low Power Design Guide

- AM335x Power Estimation Tool wiki page

- Linux Core Power Management User's Guide (v4.4) wiki page

- AM335x Schematic Checklist wiki page

- Thermal Design Guide for DSP and ARM Application Processors

- Demonstrating Manual Power Measurements on the AM335x GP EVM using Shunt Resistors How-To Video

## IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated