Application Report SPRAC22-March 2016

# ADAS Power Management

Piyali Goswami, Stanley Liu, Chetan Matad, and Sushaanth Srirangapathi

ADAS Software, Processor BU

#### ABSTRACT

Power Management (PM) in Advanced Driver Assist Systems (ADAS) requires setting the right power and clock configurations that allow any IP to consume optimal power. This helps not only reduce the total power consumed by the device, but also manage thermal dissipation of the silicon. This application report looks at different ways in which power in the TDA2xx, TDA2ex and TDA3xx family of devices can be managed, and the software APIs to achieve the same.

#### Contents

| 1 | PRCM Hardware – An Introduction                   | . 2 |

|---|---------------------------------------------------|-----|

| 2 | PM Software Stack                                 | 4   |

| 3 | System Clock Frequency and Voltage Initialization | . 4 |

| 4 | System Power Initialization                       | 13  |

| 5 | Dynamic CPU Power Management                      | 17  |

| 6 | Software Thermal Management                       | 42  |

| 7 | Reference                                         | 45  |

#### List of Figures

| 1  | PRCM Power Management Levels                                       | 2  |

|----|--------------------------------------------------------------------|----|

| 2  | Starterware (STW) Power Management Software Stack                  | 4  |

| 3  | AVS Class 0 Voltage Scaling Mechanism                              | 5  |

| 4  | VDD and VBBNW Supply to Device Transistors                         | 6  |

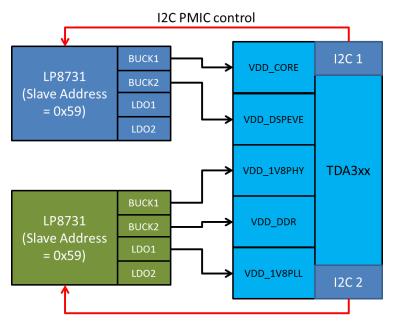

| 5  | Example Integration of LP8731 PMIC to TDA3xx SoC                   | 8  |

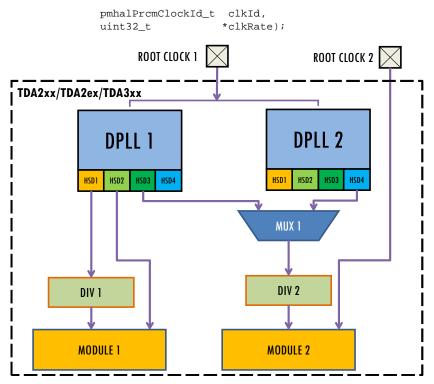

| 6  | PRCM Representative Clock Tree Structure                           | 10 |

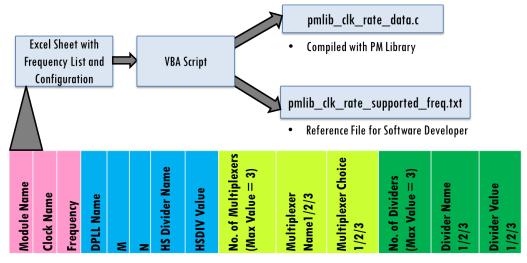

| 7  | PMLIB Clock Rate Database Excel Sheet Generator Flow               | 13 |

| 8  | GEL Script Menu Option Screen Shot                                 | 17 |

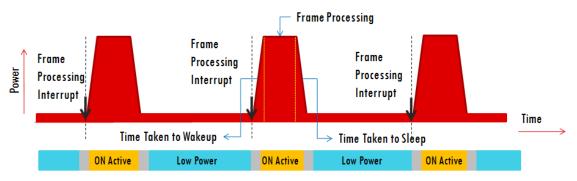

| 9  | Dynamic CPU Power Management                                       | 17 |

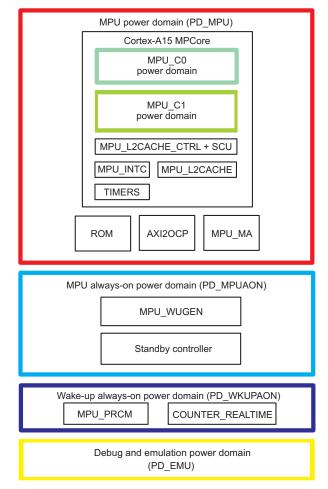

| 10 | MPU Subsystem Power Domains                                        | 19 |

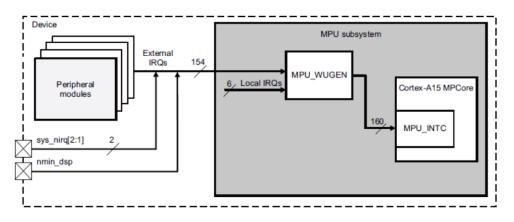

| 11 | MPU Wake Up Generator Block in MPU Subsystem                       | 22 |

| 12 | MPU Recommended Dynamic Power Management Software Flow             | 26 |

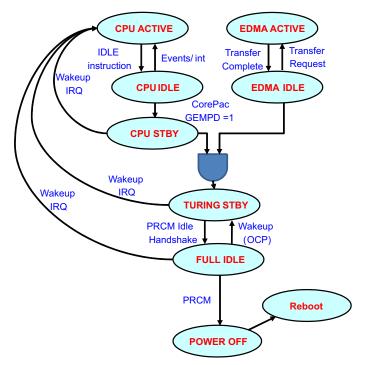

| 13 | DSP Power States and Transitions                                   | 27 |

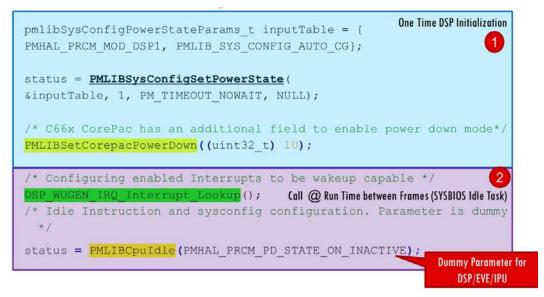

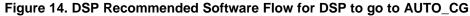

| 14 | DSP Recommended Software Flow for DSP to go to AUTO_CG             | 31 |

| 15 | IPU Power States and Transitions                                   | 32 |

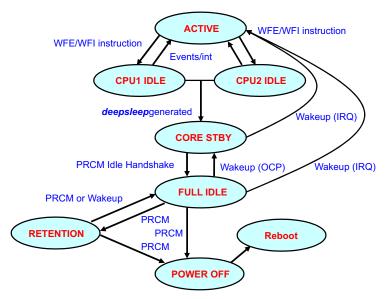

| 16 | IPU Recommended Software Flow to Put IPU in AUTO_CG                | 37 |

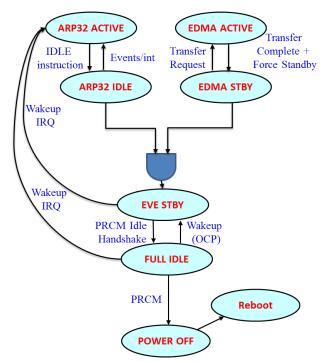

| 17 | EVE Power States and Transitions                                   | 38 |

| 18 | Recommended Software Flow for EVE to go to AUTO_CG                 | 42 |

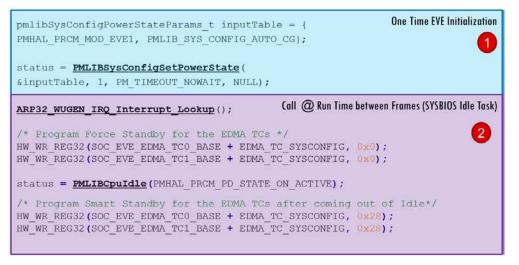

| 19 | Functional Block Diagram of the Thermal Sensors                    | 42 |

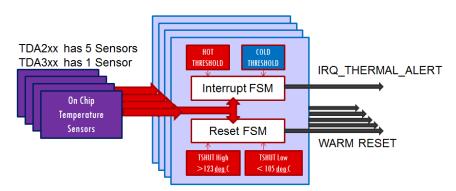

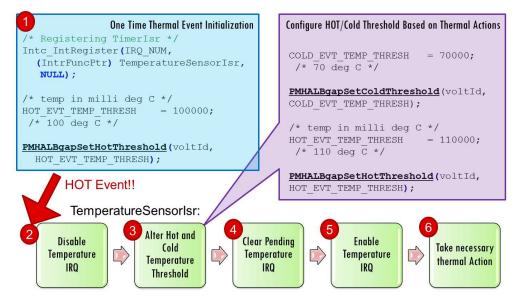

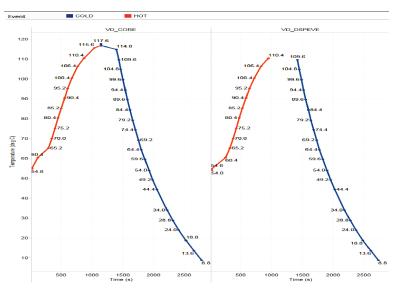

| 20 | Thermal Management Steps                                           | 43 |

| 21 | Thermal Management Software Sequence                               | 44 |

| 22 | Thermal Tracking by Changing Thermal Thresholds in Temperature ISR | 45 |

|    |                                                                    |    |

Code Composer Studio is a trademark of Texas Instruments. Cortex, ARM are registered trademarks of ARM Limited. All other trademarks are the property of their respective owners.

1

#### List of Tables

| 1  | Key Differences Between PRCM Architecture of TDA2xx/TDA2ex and TDA3xx                        | . 3 |

|----|----------------------------------------------------------------------------------------------|-----|

| 2  | Adaptive Body Bias (ABB) Impact on Strong and Weak Samples                                   | . 5 |

| 3  | Sample Information for Supported Clock Frequencies Captured in the PMLIB Clock Rate Database | 10  |

| 4  | TDA2xx/TDA2ex/TDA3xx Root Clock List                                                         | 11  |

| 5  | Example Structure for Ganging of Voltage Rails                                               | 12  |

| 6  | Execution time for PMLIB Clock Rate APIs                                                     | 12  |

| 7  | Suggested Module Power States for TDA2xx/TDA2ex/TDA3xx Modules                               | 14  |

| 8  | Example Input Table for PMLIB Set System Configuration                                       | 15  |

| 9  | Execution time for PMLIB System Configuration APIs                                           | 16  |

| 10 | Different Power States supported by CPU Subsystems                                           | 18  |

| 11 | MPU CPU1 Forced Off Time Profile                                                             | 21  |

| 12 | MPU Power Management States and Latency                                                      | 25  |

| 13 | DSP Power Management States and Latency                                                      | 31  |

| 14 | IPU1 Voltage, Power and Clock Domain Mapping                                                 | 32  |

| 15 | IPU Power Management States and Latency                                                      | 36  |

| 16 | EVE Voltage, Power and Clock Domain Mapping                                                  | 38  |

| 17 | EVE Power Management States and Latency                                                      | 41  |

# **1 PRCM Hardware – An Introduction**

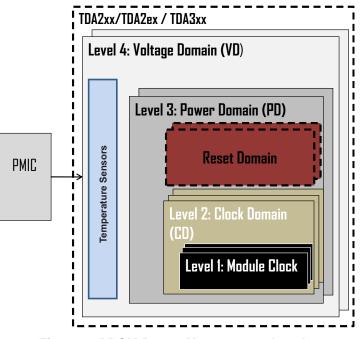

The Power Reset Clock and Module (PRCM) power management hardware is built with four levels of resource management: module, clock, power, and voltage. These management levels are enforced by defining the managed entities or building blocks of the power management architecture, called the clock, power, and voltage domains. A domain is a group of modules or subsections of the device that share a common entity (for example, common clock source, common voltage source, or common power switch). Figure 1 shows the different PRCM levels of resource management in the TDA2xx/TDA2ex and TDA3xx family of devices.

Figure 1. PRCM Power Management Levels

There are four levels of power management:

2

- Level 1 is at the module level where certain module clocks may be active when operating in specific modes, or they may be gated. They are typically controlled by PRCM registers such as CM\_<\*>\_CLKCTRL.

- Level 2 is at the clock domain level where dynamic power consumption is controlled. By gating the clocks in a clock domain, the clocks to all the modules belonging to that clock domain can be cut to lower their active power consumption (that is, the device is on and the clocks to the modules are dynamically switched to ACTIVE or INACTIVE [gated] state). Clock domain behavior can be controlled by CM\_<\*>\_CLKSTCTRL registers.

- Level 3 is at the power domain level where leakage power consumption can be lowered by turning off or by entering a retention state for a given power domain without affecting the other parts of the device. Power domains of the device can be controlled by PM\_<\*>\_PWRSTCTRL registers and their status can be read from PM\_<\*>\_PWRSTST registers.

Additionally a power domain also contains reset domains. Reset domains are a group of modules that share a reset line. The modules within a given reset domain can have their reset lines asserted or deasserted using the RM\_<\*>\_RSTCTRL register of the reset domain. The corresponding status of the reset signal can be read from the RM\_<\*>\_RSTST register.

• Level 4 is at the voltage domain level. A voltage domain is a section of the device supplied by a dedicated voltage source (that is, an internal LDOs or external switch mode power supply [SMPS]). The software can optimally configure the domain voltage levels to specific values with in the operational voltage range of the device by reading Efuse values specific to the silicon sample.

The TDA2xx/TDA2ex/TDA3xx device also has on-chip thermal sensors that sense the junction temperature of the device and convert it to a 10-bit ADC value. This value can then be used to perform thermal management of the device through software.

Some key differences between the TDA2xx/TDA2ex and TDA3xx PRCM architecture are highlighted in Table 1.

| PRCM Feature              | TDA2xx/TDA2ex                                                        | TDA3xx                                    |  |

|---------------------------|----------------------------------------------------------------------|-------------------------------------------|--|

| Number of Voltage Domains | Five voltage domains (VD_CORE, VD_MPU, VD_DSPEVE, VD_GPU and VD_IVA) | Two voltage domains (VD_CORE, VD_DSPEVE). |  |

| Temperature Sensors       | Five (one in each voltage domain)                                    | One (in VD_CORE)                          |  |

| Adaptive Body Bias        | Supported                                                            | Not Supported                             |  |

| Number of DPLLs           | 13 + 2 <sup>(1)</sup> Video PLLs                                     | 5                                         |  |

Table 1. Key Differences Between PRCM Architecture of TDA2xx/TDA2ex and TDA3xx

(1) TDA2ex has only 1 Video PLL.

The number of DPLLs are different between TDA2xx/TDA2ex and TDA3xx, making the clocking architecture between TDA2xx/TDA2ex and TDA3xx different.

For more details on the PRCM subsystem and its components, see the *Power, Reset, and Clock Management* section in the *TDA2x ADAS Applications Processor Technical Reference Manual* (SPRUHK5) [5] and the *TDA3x SoC for Advanced Driver Assistance Systems (ADAS) Silicon Revision 1.0 Technical Reference Manual* (SPRUHQ7).

The following sections discuss the ways in which the power consumption of the device and the thermal dissipation of the device can be kept in check. Section 2 describes how the system can be initialized by setting the right power modes for different modules. Section 3 describes how the modules can be sourced with appropriate clock frequencies and voltage to allow different portions of the device work at the appropriate OPP (Operating Performance Point) taking into account process variations of the device samples. Section 4 describes the method of dynamic power management of the CPUs, which allows the CPU to be in low-power mode when the CPU has nothing to do and then wake up from the low-power mode when it has to resume processing. Section 5 describes a thermal management technique where once the device temperature has become too high the software can configure the use case parameters to allow the device to cool down and then again resume normal use case operation.

#### 2 PM Software Stack

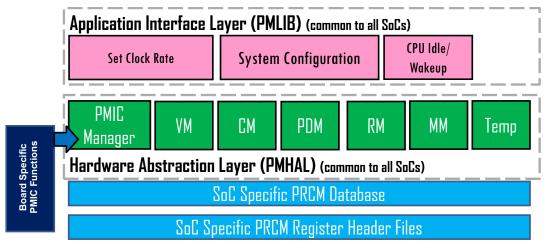

Figure 2 provides the top level view of the power management software stack. Essentially, the software stack is divided in to two layers: PMHAL and PMLIB.

Figure 2. Starterware (STW) Power Management Software Stack

PM Hardware Abstraction Layer (PMHAL) provides low level APIs that allow:

- Programming PRCM registers

- Power Domain Manager (PDM)

<STW Install Dir>\include\pm\pmhal\pmhal\_pdm.h

- Clock Domain Manager (CM) <STW Install Dir>\include\pm\pmhal\pmhal\_cm.h

- Reset Manager (RM) <STW Install Dir>\include\pm\pmhal\pmhal\_rm.h

- Module Manager (MM)

<STW Install Dir>\include\pm\pmhal\pmhal\_mm.h

- Programming Temperature Sensor Registers (Temp) <STW Install Dir>\include\pm\pmhal\pmhal\_bgap.h

- Programming Voltage Domain Adaptive Voltage Scaling (AVS) and Adaptive Body Bias (ABB) (VM) <STW Install Dir>\include\pm\pmhal\pmhal\_vm.h

- Programming board specific Power Management IC (PMIC) <STW Install Dir>\include\pm\pmhal\pmhal\_pmic.h

- Example implementations for TPS659039, TPS65917, L8731, and so forth: <STW Install Dir>\pm\pmhal\pmhal\_tps659039.c, pmhal\_tps65917.c, pmhal\_18731.c

PM Library (PMLIB) provides application interface to:

- Configure system level clock frequencies (Section 3)

<STW Install Dir>\include\pm\pmlib\pmlib\_clkrate.h and pmlib\_videopll.h

- Perform dynamic CPU power optimization (Section 5) <STW Install Dir>\include\pm\pmlib\pmlib\_cpuidle.h

# 3 System Clock Frequency and Voltage Initialization

The initialization of the device to run a given use case involves setting the right frequency for the clocks for the CPUs and peripherals. Along with the frequency setting, the right voltage for the voltage rails is also important to ensure the leakage is kept minimal and the silicon performance is kept optimal.

### 3.1 Setting the Voltage at Boot

Setting the voltage requires setting the right AVS voltage for the given voltage rail of the given frequency of operation for the CPU in that voltage domain.

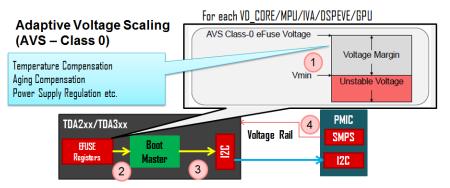

The basic mechanism of AVS Class 0 is described in Figure 3.

- For a given silicon sample, the minimum voltage is determined at which the device is operational; some of the voltage margin is added to the minimum voltage.

- This voltage value is fused into the device registers readable from the software.

- This voltage value is then programmed into the PMIC via the I2C instance on the device.

- Once programmed, the PMIC can provide the required voltage on the device voltage rails.

The advantage of using the AVS Class-0 is to ensure that the voltages supplied to the device are adaptable to the process variations of the device and the power consumption is kept optimal.

For more details on AVS voltages and I2C to program, see the *TDA2x SoC* for Advanced Driver Assistance Systems (ADAS) Silicon Revision 2.0, 1.x Technical Reference Manual (SPRUHK5) [2], *TDA3x SoC* for Advanced Driver Assistance Systems (ADAS) Silicon Revision 1.0 Technical Reference Manual (SPRUHQ7) [3], *TDA2x ADAS Application Processor 23mm Package (ABC Package) Processor* Data Manual (SPRS859) [6], and the *TDA3x ADAS Applications Processor 15mm Package (ABF Package) Data Manual* (SPRS916) [7].

Figure 3. AVS Class 0 Voltage Scaling Mechanism

On system boot, before the DPLLs are configured, the voltage rails should be set to the required voltages as per AVS Class 0 in the SBL. This ensures hot devices do not enter a thermal condition on boot. Setting the AVS Class 0 ensures silicon reliability and ensured lifetime POHs are achieved.

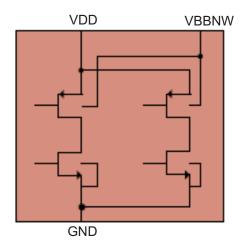

The TDA2xx/TDA2ex family of devices also support Adaptive Body Bias (ABB), which helps control further leakage, improve the performance of the silicon by applying a voltage to the NWELL of the PMOS transistors of the device, and change  $V_{TH}$  of the transistors.

| Table Li Adaptive Body Blas (ABB) impact on Otiong and Weak oumpies | Table 2. Adaptive Bod | y Bias (ABB | ) Impact on Strong | and Weak Samples |

|---------------------------------------------------------------------|-----------------------|-------------|--------------------|------------------|

|---------------------------------------------------------------------|-----------------------|-------------|--------------------|------------------|

| Reverse Body Bias (RBB)  | Forward Body Bias (FBB)  |

|--------------------------|--------------------------|

| VBBNW > VDD              | VBBNW < VDD              |

| For Strong Samples       | For Weak Samples         |

| Increase V <sub>th</sub> | Decrease V <sub>th</sub> |

| Reduce Leakage           | Increase Performance     |

## Figure 4. VDD and VBBNW Supply to Device Transistors

There are given values of AVS-Class 0 and ABB LDO voltage for each OPP. The PMHAL provides APIs to program the voltage rails with AVS and ABB (if available) for a given OPP (OPP\_LOW/OPP\_NOM/OPP\_OD/OPP\_HIGH).

The API sequence during boot, to set the AVS and ABB voltages for voltage domain VD\_DSPEVE, is shown in Figure 6. Note the board specific PMIC operation functions are registered with the PMHAL PMIC Manager by the application before the Voltage Manager API is called. This is done to ensure the use of the same software across multiple boards using different PMIC solutions. STW PM HAL provides sample implementations of the PMIC functions corresponding to TI TPS659039Q, TPS65917, LP8731, and so forth.

```

#include "pmlib_sysconfig.h"

#include "pmhal_vm.h"

#include "pmhal_pmic.h"

#include "pmhal_tps65917.h"

pmlibSysConfigPowerStateParams_t inputTable[] =

{{PMHAL_PRCM_MOD_I2C1, PMLIB_SYS_CONFIG_ALWAYS_ENABLED}};

pmhalVmOppId_t oppId;

const pmhalPmicOperations_t *pmicOps;

retVal = PMLIBSysConfigSetPowerState(inputTable, 1U, PM_TIMEOUT_INFINITE, NULL);

if (PM SUCCESS == retVal)

{

/* Get the pmic ops and register with the pmic interface. */

pmicOps = PMHALTps65917GetPMICOps();

retVal = PMHALPmicRegister(pmicOps);

/* Configure AVS and ABB */

retVal |= PMHALVMSetOpp(PMHAL_PRCM_VD_DSPEVE,

PMHAL_VM_OPP_NOM,

PM_TIMEOUT_INFINITE);

}

```

# 3.2 Taking Care of Differences in Device Voltage Rail and PMIC Integration

The PMIC integration with the device on different board designs can differ in the following three aspects:

- Different PMIC regulator outputs (LDO, BUCK, SMPS) to different input device voltage rails

- · Different I2C instance of the device is used to communicate with the PMIC

- Different PMIC I2C slave address as determined by the PMIC One Time Programmed (OTP) code.

```

www.ti.com

```

System Clock Frequency and Voltage Initialization

In order to take care of these differences each PMHAL PMIC driver provides an API to register the mapping, device I2C instance and I2C slave address with the driver in case these parameters differ from the default configuration provided. Note the default configurations correspond to the TI EVMs. The API for the LP8731 PMIC driver is as shown below:

/\*\*  $\ast$  \brief  $% \left( {{\mathbb{T}}} \right)$  The PMIC regulator output to the device input mapping can be \* different on different boards. This API can be used to provide a different mapping to the PMIC driver if the mapping does not match the default. Example table is shown below: \* \_\_\_\_\_ \* Device voltage Rail Ptr to Regulator \* -----\* PMHAL\_PRCM\_PMIC\_REGULATOR\_CORE | PMHAL\_LP8731\_REGULATOR\_BUCK1 \* PMHAL\_PRCM\_PMIC\_REGULATOR\_DSPEVE PMHAL\_LP8731\_REGULATOR\_BUCK2 \* . . . . \* index (Refer | For index of the \* #pmhalPrcmPmicRegulatorId\_t) gPmhalLP8731Regulator \* refer \* #pmhalLP8731RegulatorId\_t \_\_\_\_\_ \* This table when translated to code is as below: \* pmhalLP8731RegulatorMap\_t regulatorMap[ \* PMHAL\_PRCM\_PMIC\_REGULATOR\_COUNT] = { \* { \* &gPmhalLP8731Regulator[PMHAL\_LP8731\_REGULATOR\_BUCK1], i2C\_INSTANCE, \* PMIC\_I2C\_SLAVE\_ADDRESS }, { \* &gPmhalLP8731Regulator[PMHAL\_LP8731\_REGULATOR\_BUCK2], i2C\_INSTANCE, \* \* PMIC\_I2C\_SLAVE\_ADDRESS \* }, . . . . . . }; \* \param regulatorMap Pointer to the array of pointers which gives the mapping. The array is defined as above. \* \return None \*/ void PMHALLP8731ConfigureRegulatorMap(pmhalLP8731RegulatorMapPtr\_t regulatorMap);

7

For instance, the custom configuration of PMIC regulator mapping, I2C instance number and PMIC I2C Slave address for the LP8731 could be as shown in Figure 5.

Figure 5. Example Integration of LP8731 PMIC to TDA3xx SoC

In this case the input to the configuration API is as given below. Note that for boards which use the default TI EVM integration, this API need not be called.

```

/* Table mapping from SMPS/LDO to Voltage Rails on the device */

pmhalLP8731RegulatorMap_t

gCustomLP8731RegulatorTable[

PMHAL_PRCM_PMIC_REGULATOR_COUNT] =

{

/* HW Regulator for PMHAL_PRCM_PMIC_REGULATOR_CORE */

{

&gPmhalLP8731Regulator[PMHAL_LP8731_REGULATOR_BUCK1],

(uint8_t) PMHAL_LP8731_I2C_NUM_1,

(uint8_t) PMHAL_LP8731_CHIP_ADDRESS

},

HW Regulator for PMHAL_PRCM_PMIC_REGULATOR_DSPEVE */

/*

{

&gPmhalLP8731Regulator[PMHAL_LP8731_REGULATOR_BUCK2],

(uint8_t) PMHAL_LP8731_I2C_NUM_1,

(uint8_t) PMHAL_LP8731_CHIP_ADDRESS

},

/* HW Regulator for PMHAL_PRCM_PMIC_REGULATOR_1V8PHY */

{

&gPmhalLP8731Regulator[PMHAL_LP8731_REGULATOR_BUCK2],

(uint8_t) PMHAL_LP8731_I2C_NUM_2,

(uint8_t) PMHAL_LP8731_CHIP_ADDRESS

},

/* HW Regulator for PMHAL_PRCM_PMIC_REGULATOR_DDR */

{

&gPmhalLP8731Regulator[PMHAL_LP8731_REGULATOR_BUCK1],

(uint8_t) PMHAL_LP8731_I2C_NUM_2,

(uint8_t) PMHAL_LP8731_CHIP_ADDRESS

},

HW Regulator for PMHAL_PRCM_PMIC_REGULATOR_1V8PLL */

/*

{

&gPmhalLP8731Regulator[PMHAL_LP8731_REGULATOR_LD01],

(uint8_t) PMHAL_LP8731_I2C_NUM_2,

(uint8_t) PMHAL_LP8731_CHIP_ADDRESS

}

```

8

};

PMHALLP8731ConfigureRegulatorMap (gCustomLP8731RegulatorTable);

Once this API has been called in the beginning of the application the PMIC driver continues to use the registered mapping for any further communication with the PMIC. Application developers are advised to ensure appropriate I2C Pin Mux configuration and I2C instance power configuration is done before attempting to program the PMIC.

# 3.3 Setting the Frequency of Modules

Based on the expected CPU operations, the CPUs in the system can be configured to operate at different frequencies as determined by the OPP and speed bin of the device. Setting the OPP of the CPU involves setting the DPLLs to provide the desired clock frequency and setting the PMIC to provide the desired voltage as determined in the AVS EFuse registers. Similarly, different peripherals require different frequencies to meet a given speed of operation (for example, Inter-Integrated Circuit (I2C), Universal Asynchronous Receiver/Transmitter (UART), Multichannel Audio Serial Port (McASP), and so forth).

The generic clocking scheme in the device can be visualized as a tree where a certain input clock to the device is the root node (or Root Clock) of the clock tree and the modules are leaf nodes. Between these two levels are multiple levels consisting of DPLLs, multiplexers and dividers. Configuring a clock frequency for the module requires programming these DPLLs, multiplexers and dividers. The generic view of the device internal clocking is as shown in Figure 6.

The PM software provides two APIs to set and get the frequency of any clock of any given module. The interface of the two APIs is as given below:

```

/**

* \brief Set the clock rate of the given module.

*

*

\param modId

Module ID

Refer Enum #pmhalPrcmModuleId_t for values.

*

\param clkId

Clock Id present in the module

Refer Enum #pmhalPrcmClockId_t for values.

*

\param clkRate

new clock rate in Hz to be provided for the

clockID

*

\retval errorStatus Status of API call. Can be any of the following,

*

PM_SUCCESS

Indicates the operation is success

*

PM FAIL

Can Indicate the following:

*

-modId is not valid.

*

-clockRate provided is not supported

*

Refer Enum #pmErrCode_t for detailed values.

* /

pmErrCode_t PMLIBClkRateSet(pmhalPrcmModuleId_t modId,

pmhalPrcmClockId_t clkId,

uint32_t

clkRate);

/**

* \brief Get the current clock rate of the given module.

*

\param modId

Module ID

Refer Enum #pmhalPrcmModuleId_t for values.

Clock Id present in the module

\param clkId

Refer Enum #pmhalPrcmClockId_t for values.

*

\param clkRate

new clock rate in Hz returned for the clockID

*

\retval errorStatus Status of API call. Can be any of the following,

PM_SUCCESS

Indicates the operation is success

*

PM_FAIL

Can Indicate the following:

-modId is not valid.

*

-clockId provided is not valid

*

-Structure provided is not properly initialized

Refer Enum #pmErrCode_t for detailed values.

*/

```

pmErrCode\_t PMLIBClkRateGet(pmhalPrcmModuleId\_t modId,

System Clock Frequency and Voltage Initialization

Figure 6. PRCM Representative Clock Tree Structure

The PMLIBClkRateSet API configures the necessary DPLL, Mux and divider registers for a given input frequency. The API uses an internal database, which is used to find the necessary DPLL, Mux and Divider programming for a given frequency. The list of supported frequencies for a given clock of a given module can be seen in the following files:

- <STW Install Directory>\pm\pmlib\tda2xx\pmlib\_clk\_rate\_supported\_freq\_tda2xx.txt

- <STW Install Directory>\pm\pmlib\tda2xx\pmlib\_clk\_rate\_supported\_freq\_tda2ex.txt

- <STW Install Directory>\pm\pmlib\tda3xx\pmlib\_clk\_rate\_supported\_freq\_tda3xx.txt

A sample table is shown in Table 3. The first column in the table is the name of the module, the second is the clock name and the third column is the list of supported frequencies in Hz. Each row is a unique combination of module and clock name.

| Module Name                       | Clock Name                                 | Supported Frequencies (Hz)      |  |  |

|-----------------------------------|--------------------------------------------|---------------------------------|--|--|

| PMHAL_PRCM_MOD_ATL                | PMHAL_PRCM_CLK_ATL_GFCLK                   | 26600000, 32786, 451584000      |  |  |

| PMHAL_PRCM_MOD_ATL                | PMHAL_PRCM_CLK_ATL_L3_GICLK                | 26600000                        |  |  |

| PMHAL_PRCM_MOD_IO_SRCOMP_CO<br>RE | PMHAL_PRCM_CLK_COREAON_IO_SR<br>COMP_GFCLK | 2000000                         |  |  |

| PMHAL_PRCM_MOD_EVE1               | PMHAL_PRCM_CLK_EVE1_GFCLK                  | 53500000, 65000000              |  |  |

| PMHAL_PRCM_MOD_EVE2               | PMHAL_PRCM_CLK_EVE2_GFCLK                  | 53500000, 65000000              |  |  |

| PMHAL_PRCM_MOD_EVE3               | PMHAL_PRCM_CLK_EVE3_GFCLK                  | 53500000, 65000000              |  |  |

| PMHAL_PRCM_MOD_EVE4               | PMHAL_PRCM_CLK_EVE4_GFCLK                  | 53500000, 65000000              |  |  |

| PMHAL_PRCM_MOD_UART6              | PMHAL_PRCM_CLK_UART6_GFCLK                 | 19200000, 4800000               |  |  |

| PMHAL_PRCM_MOD_IPU1               | PMHAL_PRCM_CLK_IPU1_GFCLK                  | 212800000                       |  |  |

| PMHAL_PRCM_MOD_IPU2               | PMHAL_PRCM_CLK_IPU2_GFCLK                  | 212800000                       |  |  |

| PMHAL_PRCM_MOD_IVA                | PMHAL_PRCM_CLK_IVA_GCLK                    | 388333333, 43000000, 532000000  |  |  |

| PMHAL_PRCM_MOD_SL2                | PMHAL_PRCM_CLK_IVA_GCLK                    | 388333333, 430000000, 532000000 |  |  |

# Table 3. Sample Information for Supported Clock Frequencies Captured in the PMLIB Clock Rate Database

| Database (continueu)  |                               |                                                   |  |  |

|-----------------------|-------------------------------|---------------------------------------------------|--|--|

| Module Name           | Clock Name                    | Supported Frequencies (Hz)                        |  |  |

| PMHAL_PRCM_MOD_TIMER2 | PMHAL_PRCM_CLK_L4PER_L3_GICLK | 26600000                                          |  |  |

| PMHAL_PRCM_MOD_TIMER2 | PMHAL_PRCM_CLK_L4PER_L4_GICLK | 13300000                                          |  |  |

| PMHAL_PRCM_MOD_TIMER2 | PMHAL_PRCM_CLK_TIMER2_GFCLK   | 20000000, 10000000, 32786, 22579200,<br>451584000 |  |  |

| PMHAL_PRCM_MOD_TIMER3 | PMHAL_PRCM_CLK_L4PER_L3_GICLK | 26600000                                          |  |  |

| PMHAL_PRCM_MOD_TIMER3 | PMHAL_PRCM_CLK_L4PER_L4_GICLK | 13300000                                          |  |  |

| PMHAL_PRCM_MOD_TIMER3 | PMHAL_PRCM_CLK_TIMER3_GFCLK   | 20000000, 10000000, 32786, 22579200,<br>451584000 |  |  |

# Table 3. Sample Information for Supported Clock Frequencies Captured in the PMLIB Clock Rate Database (continued)

**NOTE:** The file shown in Table 3 is an auto generated file and should not be modified manually. In order to add any frequency to this table (in case the frequency you are looking for is not available), see Section 3.3.1. TI provides the sample database corresponding to 20 MHz input SYSCLK1 frequency as a part of the STW software package. To include support for any other SYSCLK1 frequencies kindly contact your TI representative.

The API makes sure when the frequency of a CPU is changed such that the OPP shifts, the PMIC is also programmed to change the voltage to correspond to this OPP shift. The API also takes into account the ganging of voltage rails which can happen outside the device boundaries. The user input table in the format as shown in Table 5. Table 5 is parsed through to find all the dependent CPUs in the voltage rails, which are ganged and if the new voltage is found to satisfy the OPP requirement of any ganged CPU the voltage is changed along with the DPLL configuration.

**NOTE:** The Clock Rate APIs do not take care of dependencies between the different paths in the database. For instance, if the same DPLL is sourcing multiple clocks and two different clocks require frequencies such that the DPLL needs to be locked to two different frequencies, the API/Database does not recognize this conflict and would program the DPLL to the latest configuration to which it has been asked to be programmed. The Application developer needs to be aware of any such conflicts to avoid unwanted behavior from the device.

The PMLIBClkRateSet and PMLIBClkRateGet APIs need an initialization step that populates the root clock frequencies and the information regarding the ganging of voltage rails in order for the APIs to work correctly. The two initialization structures are shown in Table 4 and Table 5. The root clock frequencies are represented as an array of 32-bit unsigned numbers. The list of root clock frequencies that need to be populated for TDA2xx/TDA2ex and TDA3xx devices is given in Table 4.

| TDA2xx/TDA2ex Root Clock List    | TDA3xx Root Clock List         |

|----------------------------------|--------------------------------|

| PMHAL_PRCM_ROOT_CLK_PCIESREF_ACS | PMHAL_PRCM_ROOT_CLK_SYS_CLKIN1 |

| PMHAL_PRCM_ROOT_CLK_RMII         | PMHAL_PRCM_ROOT_CLK_SYS_CLKIN2 |

| PMHAL_PRCM_ROOT_CLK_SYS_32K      |                                |

| PMHAL_PRCM_ROOT_CLK_SYS_CLKIN1   |                                |

| PMHAL_PRCM_ROOT_CLK_SYS_CLKIN2   |                                |

# Table 4. TDA2xx/TDA2ex/TDA3xx Root Clock List

System Clock Frequency and Voltage Initialization

www.ti.com

The ganging of voltage rails is represented as an array of structures for each voltage rail in the device. For example, if the voltage rails VD\_DSPEVE, VD\_IVA and VD\_GPU are ganged together outside the device on the board one can populate the voltage ganging input structure as shown in Table 5.

| Voltage ID           | List of Ganged Voltage Rails                 | Number of Ganged Rails |

|----------------------|----------------------------------------------|------------------------|

| PMHAL_PRCM_VD_MPU    | NA                                           | 0                      |

| PMHAL_PRCM_VD_CORE   | NA                                           | 0                      |

| PMHAL_PRCM_VD_IVAHD  | PMHAL_PRCM_VD_DSPEVE,<br>PMHAL_PRCM_VD_GPU   | 2                      |

| PMHAL_PRCM_VD_DSPEVE | PMHAL_PRCM_VD_IVAHD,<br>PMHAL_PRCM_VD_GPU    | 2                      |

| PMHAL_PRCM_VD_GPU    | PMHAL_PRCM_VD_IVAHD,<br>PMHAL_PRCM_VD_DSPEVE | 2                      |

### Table 5. Example Structure for Ganging of Voltage Rails

TI provides reference software for both root clock list and ganging of voltage rails corresponding to TI EVMs in the following files:

- <STW Install Directory>\starterware\_\pm\pmlib\tda2xx\pmlib\_boardconfig.c

- <STW Install Directory>\starterware\_\pm\pmlib\tda3xx\pmlib\_boardconfig.c.

Table 6 gives the average time the PMLIBClkRateSet and PMLIBClkRateGet APIs take to set and get the frequency of a given clock. The measurements were done on A15 (in TDA2xx/TDA2ex) running at 750 MHz and M4 (in TDA3xx) running at 212.8 MHz.

## Table 6. Execution time for PMLIB Clock Rate APIs

|                       | A15 Time Taken (µs) |        | M4 Time 1 | Γaken (μs) |

|-----------------------|---------------------|--------|-----------|------------|

| Application Interface | MAX                 | AVG    | MAX       | AVG        |

| PMLIBClkRateSet       | 2461.65             | 716.24 | 690.6     | 274.2      |

| PMLIBClkRateGet       | 1375.1              | 387.5  | 519.6     | 236.4      |

# 3.3.1 Modifying the Clock Frequency Database

The clock frequency database is generated using an excel sheet that captures the DPLL configuration, multiplexer and divider configurations for each module and its corresponding clock in the device. The excel sheets are located in the following folders:

- <STW Install Dir>\pm\pmlib\tda2xx

- <STW Install Dir>\pm\pmlib\tda3xx

The flow to convert the excel sheet to code is as shown in Figure 7. The different columns of the excel sheet are also described in Figure 7.

Figure 7. PMLIB Clock Rate Database Excel Sheet Generator Flow

In order to add a new frequency in the database, do the following steps:

- 1. In the corresponding device clock tree excel sheet, find the module and clock pair whose frequency needs to be added.

- 2. For the new clock frequency, insert a row after the current list of frequencies.

- 3. Populate this new row, with the module name, clock name, new frequency, DPLL, multiplexer and divider configurations.

- 4. Once done with the editing, click on the Generate PM Clock Rate DB \_\_\_\_\_\_\_ button (refer to Cell B1 in the excel sheet). Two files (C file and text file) are generated (overwriting the existing default C and text file) in the same directory as the excel sheet.

- 5. Confirm that the text file shows the updated list of supported frequencies.

- 6. Re-build the PMLIB library with the generated C file.

# 4 System Power Initialization

In order to make sure the device power consumption is optimal, the software should ensure that only the modules required by the use case are kept ON and all the other modules are placed in OFF state.

Setting the module to have different power states involves programming the Power Domain (Level 3), the Clock Domain (Level 2) and Module (Level 1) to appropriate values that allow the modules to be in different power states. Essentially the module power states can be abstracted to fall in three categories:

- DISABLED Lowest Power Configuration

- Power Domain State: OFF or RETENTION

- Clock Domain State: SW SLEEP or HW AUTO

- Module State: DISABLED or HW\_AUTO

- AUTO CLOCK GATE (AUTO\_CG) Clocks disabled when module is not used or else clocks are on

- Power Domain State: ON when module is active, ON or RETENTION or ON\_INACTIVE when module is not used.

- Clock Domain State: HW\_AUTO (Clocks are running when the module is used and the clocks are gated when the module is not used.)

- Module State: HW\_AUTO

- ALWAYS ENABLED Highest Power Configuration

- Power Domain State: ON

- Clock Domain State: SW\_WKUP (Clocks are always on)

- Module State: ENABLED

Different modules have different default power states after the device boots up. Modules like MMC2, MLB\_SS, SATA, OCP2SCP1, OCP2SCP3, USB\_OTG\_SS1, USB\_OTG\_SS2, USB\_OTG\_SS3, USB\_OTG\_SS4, PCIESS1, PCIESS2, and so forth are disabled by default. Modules like EVE1/2/3/4 have their power domain ON (thus drawing leakage power) but have their clocks gated. ROM also initializes certain peripherals to ON state to be able to boot from them.

Given this varied state of power of different modules at boot, the Secondary Boot Loader (SBL) should initialize the system intelligently to make sure only the modules getting used for a given use case are ENABLED and the ones not getting used are DISABLED.

Suggested module power states that can be applied when deciding the optimal power state of the TDA2xx, TDA2ex and TDA3xx devices are summarized in Table 7.

| Module Name               | Power State after ROM boot | SBL Desired Action                                                         |

|---------------------------|----------------------------|----------------------------------------------------------------------------|

| MPU Core 0 and Core 1 (1) | ON                         | Force Off Core 1 when not used                                             |

| IPU, DSP1 and 2           | OFF <sup>(2)</sup>         | Initialize core when valid application image is present. Power Off if not. |

| EVE1/2/3/4 (3)            | ON (Clock Gated)           | Initialize core when valid application image is present. Power Off if not. |

| Peripherals               | Varied                     | Disable Module if not used.                                                |

#### Table 7. Suggested Module Power States for TDA2xx/TDA2ex/TDA3xx Modules

(1) Valid only for TDA2xx.

(2) IPU, DSP1 and DSP2 are ON after ROM boot in TDA3xx.

(3) EVE IP not present in TDA2ex.

The STW PMLIB provides the necessary APIs to be able to set the power state of the module and also get the power status of a given module. The two APIs are as below:

| /*: | *          |          |           |                                                           |

|-----|------------|----------|-----------|-----------------------------------------------------------|

| *   | \brief     | This AP  | I configu | ares the given module to the desired power state.         |

| *   | \param     | inputTal | ble       | Table of modules and their desired power and clock state. |

| *   | \param     | numConf  | ia        | Number of entries in the system configuration table.      |

| *   |            | timeout  | 5         | Desired time out for which one should wait for each       |

| *   | · <b>-</b> |          |           | of the modules to reach its desired power state.          |

| *   |            |          |           | PM_TIMEOUT_NOWAIT (0) - The API does not wait.            |

| *   |            |          |           | PM_TIMEOUT_INFINITE (0xFFFFFFFF) - The API waits          |

| *   |            |          |           | infinitely.                                               |

| *   |            |          |           | Any other value - The API waits to any one of the         |

| *   |            |          |           | events to happen first : (1) Success of operation         |

| *   |            |          |           | (2) The timeout is reached.                               |

| *   | \param     | resultR  | eturn     | Table which returns success or error codes got            |

| *   |            |          |           | while programming the power state. Useful for debug       |

| *   |            |          |           | One must allocate the same number of entries as the       |

| *   |            |          |           | input table to ensure the API has sufficient space        |

| *   |            |          |           | to return the error or pass codes. The structure          |

| *   |            |          |           | returns in the format                                     |

| *   |            |          |           | [module, return code (success/fail code)] for all         |

| *   |            |          |           | the modules given in a one to one mapping.                |

| *   |            |          |           |                                                           |

| *   | \return    | status   | Returns   | the status of the API. This can be the following          |

| *   |            |          | values:   |                                                           |

| *   |            |          | PM_SUCCI  | ESS If the desired power state was met.                   |

| *   |            |          | PM_FAIL   | If the desired power state was not met. One must          |

| *   |            |          |           | check the resultReturn to check the cause for             |

14

#### System Power Initialization

Texas

www.ti.com

TRUMENTS

```

*

failure.

* /

pmErrCode_t PMLIBSysConfigSetPowerState(

const pmlibSysConfigPowerStateParams_t *inputTable,

uint32 t

numConfig,

uint32 t

timeout.

pmlibSysConfigErrReturn t

*resultReturn);

*

\brief

This API is used to get the power state for a given module.

*

\param

moduleId

Module ID of the module one is interested in. Refer

#pmhalPrcmModuleId_t for details.

\param

currState

Returns the final state of the module. Refer

#pmlibSysConfigPowerState_t for details.

detailedState

This is an optional parameter which can be used to

\param

return the detailed state of the module broken

down into module state, clock state and power state.

*

If one is not interested in knowing the detailed

state one can put NULL for this parameter.

*

\return status Returns the status of the API. This can be the following

values:

PM_SUCCESS If the status is obtained correctly.

PM_BADARGS If currState pointer is NULL.

*/

pmErrCode_t PMLIBSysConfigGetPowerState(

pmhalPrcmModuleId_t

moduleId,

```

pmlibSysConfigPowerState\_t \*currState, pmlibSysConfigDetailedState\_t \*detailedState);

The *PMLIBSysConfigSetPowerState* API configures the power domain, clock domain and the module registers at the PRCM level and additionally the module SYSCONFIG registers wherever available to be able to place the module in any one of the three power states *DISABLED*, *AUTO\_CG or ALWAYS ENABLED*. The API also configures the static dependencies for the clock domain in which the module resides.

The API takes a table of input modules and their desired power states to initialize the power state of the system. An example input table is as shown in Table 8.

| Module Name           | Power State                     |

|-----------------------|---------------------------------|

| PMHAL_PRCM_MOD_DSP1   | PMLIB_SYS_CONFIG_ALWAYS_ENABLED |

| PMHAL_PRCM_MOD_MCASP1 | PMLIB_SYS_CONFIG_DISABLED       |

| PMHAL_PRCM_MOD_IPU1   | PMLIB_SYS_CONFIG_AUTO_CG        |

#### Table 8. Example Input Table for PMLIB Set System Configuration

For subsystems that have a reset configuration available with them, the API also performs the subsystem reset management. For example, when the EVE1 subsystem is configured to be ALWAYS ENABLED, the API enables the EVE subsystem power, clock and module and lifts the subsystem reset (RM\_EVE1\_RSTCTRL.RST\_EVE1 = 0). Similarly, when the EVE1 subsystem is configured to be DISABLED, the subsystem reset is asserted by the API. The API does not configure any reset for a module configured for AUTO\_CG.

**NOTE:** The PMLIBSysConfigSetPowerState does not take care of dependencies between modules. For instance, if a module A requires module B and C to be enabled before module A can be enabled, the application must call the enable operation of B and C before enabling A.

System Power Initialization

www.ti.com

```

An example sequence of the PMLIBSysConfigSetPowerState API to initialize the DSP1 and IPU1

subsystem is given below:

#include "pmlib_sysconfig.h"

pmlibSysConfigPowerStateParams_t inputTable[] =

```

```

{{PMHAL_PRCM_MOD_DSP1, PMLIB_SYS_CONFIG_ALWAYS_ENABLED},

{PMHAL_PRCM_MOD_IPU1, PMLIB_SYS_CONFIG_ALWAYS_ENABLED}};

const uint32_t numTableEntries = sizeof (inputTable) /

sizeof (pmlibSysConfigPowerStateParams_t);

pmErrCode t

status = PM SUCCESS;

/* Initialize the system modules to be enabled. Subsystem resets if any are

* de-asserted */

status = PMLIBSysConfigSetPowerState(inputTable, (uint32_t) numTableEntries,

PM TIMEOUT INFINITE,

NULT.T.);

if (PM_SUCCESS == status)

{

/* Load the code for the DSP 1 subsystem */

DSP1 LoadCode();

/* Configure AMMU for IPU1 */

IPU1_ConfigAmmu();

/* Load the IPU1 Code*/

IPU1_LoadCode();

/* Lift the IPU1 C0 CPU reset to start the CPU execute instructions */

PMHALResetRelease(PMHAL_PRCM_RG_IPU1_CPU0_RST, PM_TIMEOUT_INFINITE);

/* Lift the DSP CPU reset to start the CPU execute instructions ^{\star/}

PMHALResetRelease(PMHAL_PRCM_RG_DSP1_RST, PM_TIMEOUT_INFINITE);

```

Similarly, the PMLIBSysConfigGetPowerState API can be used to know the power status of the module. The API returns the derived power state (DISABLED, AUTO\_CG or ALWAYS ENABLED) and the individual power domain, clock domain and module status for detailed analysis.

Table 9 gives the average time the API takes for the API to set and get the power state per module. The measurements were done on A15 (in TDA2xx/TDA2ex) running at 750 MHz and M4 (in TDA3xx) running at 212.8 MHz.

| Application Interface       | Power State    | A15 Time Taken (µs) | M4 Time Taken (µs) |

|-----------------------------|----------------|---------------------|--------------------|

| PMLIBSysConfigSetPowerState | ALWAYS_ENABLED | 19.5                | 142.7              |

|                             | DISABLED       | 51.4                | 258.8              |

|                             | AUTO_CG        | 26.4                | 190.4              |

| PMLIBSysConfigGetPowerState | NA             | 10.7                | 68.5               |

Table 9. Execution time for PMLIB System Configuration APIs

# 4.1 Knowing System Power State With GEL Script

In order to know the state of the modules in the system at use case development time, the developer can use Code Composer Studio<sup>™</sup> GEL scripts TDA2xx\_PRCM\_Get\_Config.gel,

TDA3xx\_PRCM\_Get\_Config.gel or TDA2ex\_PRCM\_Get\_Config.gel to find the power state of all the modules in the device. Once the device is booted, connect to the device master from CCS and run the PRCM\_GetConfig GEL menu as shown in Figure 8. This feature is available in GEL version 9 onwards.

| Scripts Run Window Help                  |   |                |

|------------------------------------------|---|----------------|

| TDA2xx Misc Module configurations        | • | 🔳 🏇 🕶 🔗 🕶 🖻    |

| TDA2xx EMU Utilities                     | • |                |

| TDA2xx PRCM MODULE Configuration         | • |                |

| TDA2xx PRCM CLOCK Configuration - ADAS   | • |                |

| TDA2xx PRCM CLOCK Configuration - Common | • |                |

| Temperature Sensor Readings              | • |                |

| TDA2xx Pad Configurations                | • |                |

| TDA2xx MULTICORE Initialization          | • |                |

| DDR Memory config                        | • |                |

| TDA2xx PRCM Get Configuration            | • | PRCM_GetConfig |

Figure 8. GEL Script Menu Option Screen Shot

The GEL function prints the PRCM state of all the modules in the system. Based on their ON/OFF state, the use case developer can appropriately call the *PMLIBSysConfigSetPowerState* APIs to enable only those modules that are required and disable the rest. The output format of the GEL script is as shown below:

| GEL | Output: |                                                                                                         |

|-----|---------|---------------------------------------------------------------------------------------------------------|

| GEL | Output: | Module : <module name=""> (CD_<clock_domain>, PD_<power_domain>)</power_domain></clock_domain></module> |

| GEL | Output: | Module State : <module_state_from_clkctrl></module_state_from_clkctrl>                                  |

| GEL | Output: | Clock State : <clock_state_from_clkstctrl></clock_state_from_clkstctrl>                                 |

| GEL | Output: | <pre>Power State : <power_state_from_pwrstctrl></power_state_from_pwrstctrl></pre>                      |

| GEL | Output: | Final State : <final as="" derived="" from="" module,<="" state="" td=""></final>                       |

|     |         | Clock and Power State>                                                                                  |

| GEL | Output: |                                                                                                         |

# 5 Dynamic CPU Power Management

Dynamic power management of the CPUs involves setting the CPU power state to a lower power state when the CPU has nothing to do and then wakes up when the CPU has to resume its operations. The process of dynamic CPU power management is as shown in Figure 9. The CPU context is maintained every time the CPU goes to low-power mode. Interrupts that are configured during the normal CPU operation can be configured as wake up events, which bring the CPU out of its low-power state.

Figure 9. Dynamic CPU Power Management

#### Dynamic CPU Power Management

www.ti.com

The following subsections provide an in-depth analysis of the different power states of the CPUs in the system (MPU, DSP, IPU, EVE) and the time taken for going into and waking up from the low-power states. Based on the latency requirements, the application developer can decide on a fixed-power state for the CPUs for the low-power state. The different power states for the different CPUs in the system, from highest (left most) to lowest (right most), are summarized in Table 10. The following sections dive deep into the power and clock state of the different subsystems and the programming sequence to achieve the desired power state.

| CPU Subsystem | Highest Power<br>State |                   |                                   |                              | Lowest Power<br>State  |

|---------------|------------------------|-------------------|-----------------------------------|------------------------------|------------------------|

| MPU           | On                     | Core 1 Forced Off | Core 1 Forced Off,<br>Core 0 Idle | Subsystem Auto<br>Clock Gate | Subsystem<br>Retention |

| DSP           | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

| IPU           | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

| EVE           | On                     | CPU Idle          | Subsystem Standby                 | Subsystem Auto<br>Clock Gate | Subsystem Off          |

Table 10. Different Power States supported by CPU Subsystems

Some recommended power states for the different CPUs are shown below:

- MPU: Subsystem Retention <STW\_Install\_Dir>\examples\pm\cpuidle\main\_a15host.c

- IPU: Subsystem Auto Clock Gate <STW\_Install\_Dir>\examples\pm\cpuidle\main\_m4.c

- DSP: Subsystem Auto Clock Gate <STW\_Install\_Dir>\examples\pm\cpuidle\main\_c66x.c

- EVE: Subsystem Auto Clock Gate <STW\_Install\_Dir>\examples\pm\arp32\_cpuidle\main\_arp32.c

## 5.1 MPU Power Management

**NOTE:** This section is valid for TDA2xx. TDA2ex has a single A15 core in the MPU subsystem.

#### 5.1.1 MPU PM Blocks

The MPU (Dual Cortex®-A15 Subsystem) has its internal Local PRCM (MPU\_PRCM) and is also controlled by the system-on-chip (SoC) level Global PRCM. The MPU\_PRCM is responsible for power management of the Cortex-A15 CPU power domains and corresponding L1 Cache highlighted in sea green and light green boxes in Figure 10.

Figure 10. MPU Subsystem Power Domains

The global PRCM is responsible for the MPU Power domain including the L2 Cache, Interrupt Controllers, and MPU Memory Adapter, and so forth (highlighted in red in Figure 10).

The MPU Wake up Generator (WUGEN) responsible for waking up MPU from a low-power state when a wake up event occurs is in the MPU always on power domain along with the MPU standby controller.

The MPU MPU\_PRCM resides in the always on wake up power domain (PD\_WKUPAON).

In addition to the standard power-management technique supported in the device, the MPU subsystem also employs a SR3-APG (SmartReflex3 automatic power gating) power-management technology to reduce leakage.

This technology allows for full logic and memory retention on MPU\_C0 and MPU\_C1, and is controlled by the MPU\_PRCM. The SR3-APG power management can be enabled by setting the PRM\_PSCON\_COUNT [24] HG\_EN bit.

#### 5.1.2 MPU PM States

This section discusses the different power states of the MPU subsystem and understands the power down and wake up latencies based on the power savings. Contact your TI representative to get access to the TDA2xx/TDA2ex Power Estimation Spread Sheet and analyze the exact power savings for the different supported low power modes.

• CASE 1: MPU ON (Core 0 (C0) and Core 1 (C1) On)

In this configuration, the Cortex-A15 CPUs are both alive and running their respective software. This is the highest power consumption configuration and the power consumption is determined by the kind of operations the A15 is performing. The sub-modules in the MPU subsystem are ON and the clocks are enabled for the subsystem and the CPUs.

#### CASE 2: MPU C1 Forced Off

In this configuration, the MPU C1 is forced off and the MPU C0 is alive and running its own software. In this configuration, the MPU C1 logic, L1 Cache is off, the clocks to the MPU C1 are gated and the MPU C1 LPRM shows the CPU to be in power off mode.

In order to force the CPU1 to OFF state one must perform the following operations:

- 1. Clear the SCTLR.C bit or HSCTLR.C bit if in Hypervisor mode, to prevent additional data cache allocation.

- Clean and invalidate all data from the L1 data cache. This prevents any new data cache snoops or data cache maintenance operations from other processors in the multiprocessor being issued to this processor.

- Switch the processor from Symmetric Multiprocessing (SMP) mode to Asymmetric Multiprocessing (AMP) mode by clearing the ACTLR SMP bit. Clearing the SMP bit enables the processor to be taken out of coherency by preventing the processor from receiving cache, TLB, or BTB maintenance operations broadcast by other processors in the multiprocessor.

- 4. Ensure that the system does not send interrupts to the processor that is being powered down.

- 5. Execute an ISB instruction to ensure that all of the CP15 register changes from the previous steps have been committed.

- Execute a DSB instruction to ensure that all cache, TLB and branch predictor maintenance operations issued by any processor in the multiprocessor before the SMP bit was cleared have completed.

- 7. Execute a WFI instruction and wait until the STANDBYWFI output is asserted to indicate that the processor is in idle and low-power state.

The MPU CPU 1 can be forced off using the STW PM API as given below:

```

/**

* \brief Enter CPU1 into FORCE_OFF mode.

*

*

* This function can be used by the application to enter CPU1

* into FORCE_OFF mode when no binary is loaded for CPU1.

*

* \param none

*

* \return none

*/

void PMLIBCpulForcedOff(void);

An example programming sequence to put the MPLLC1 to forced off is applied.

```

An example programming sequence to put the MPU C1 to forced off is as given below:

MPU\_WUGEN\_1\_DisableAll();

```

/* Flushing the DCache is required to ensure Core 0 does not get

* pipeline stalled when the cache is enabled later and the

* cache invalidate is performed. */

CP15DCacheCleanFlush();

```

```

PMLIBCpulForcedOff();

```

The time taken to bring the CPU1 to forced off state when MPU is operating at 750 MHz and a GP Timer operating at 20 MHz is used to measure the time taken is given in Table 11.

## Table 11. MPU CPU1 Forced Off Time Profile

| Function                  | Time Taken (micro second (μs)) |

|---------------------------|--------------------------------|

| MPU_WUGEN_1_DisableAll(); | 1.65                           |

| CP15DCacheCleanFlush();   | 7668.6                         |

| PMLIBCpu1ForcedOff();     | 7.5                            |

Putting MPU C1 to a forced off state is a one-time configuration and is typically done in the SBL when there is no application that is to run on CPU1.

### CAUTION

In order to wake up the CPU1 from a forced off state the TDA2x would require a full system reboot.

# • CASE 3: MPU C1 Forced Off and C0 in IDLE

In this configuration, the MPU C1 is put to a forced off state with the steps as mentioned in Case 2. Additionally the CORE 0 is made to go to IDLE state whenever the CORE 0 has nothing to run and is again woken up by an event when the CORE 0 has to resume processing.

The steps to take the CORE 0 to IDLE are shown below:

1. Program the MPU LPRM Domain state to the desired power state.

2. Execute WFI instruction.

The STW API to enable the CORE 0 going into low-power mode is shown below:

```

/**

*

Enter the CPU specified into the given low power state.

\brief

*

*

NOTE:

To keep the ADAS power management simple, we only

support one low-power mode per CPU. The power state is

used in the API to enable supporting multiple low power

states in future w/o breaking compatibility.

Low power state to enter into. Refer enum

\param

pwrst

#pmhalPrcmPdState_t for details.

*

\return status Returns the status of the API. This can be the following

values:

*

PM_SUCCESS If the desired power state was met.

PM_FAIL

If the desired power state was not met.

* /

```

pmErrCode\_t PMLIBCpuIdle(pmhalPrcmPdState\_t pwrst);

The possible inputs to this API are shown below. Program the global PRCM along with the MPU\_PRCM to be able to get to a lower MPU Power state. An example of this is shown in CASE 4.

```

PMHAL_PRCM_PD_STATE_OFF = 0U,

/**< Power to the domain is off. */

PMHAL_PRCM_PD_STATE_RETENTION = 1U,

/**< Power to the domain is in retention mode and it will not be functional

* but the memory will be retained. */

PMHAL_PRCM_PD_STATE_ON_INACTIVE = 2U,

/**< Power to the domain is ON INACTIVE. */

PMHAL_PRCM_PD_STATE_ON_ACTIVE = 3U,

/**< Power to the domain is ON. */</pre>

```

The usage of this API (shown below) when CPU 0 wants to go to an IDLE state with no power transition:

/\* Set the CORE 0 to IDLE state with no Power Domain Transition \*/

status = PMLIBCpuIdle(PMHAL\_PRCM\_PD\_STATE\_ON\_ACTIVE);

#### Dynamic CPU Power Management

In order to wake up the CORE 0 based on a certain interrupt from low power state one must program the MPU WUGEN (Wake Up GENerator) module. The WUGEN unit is responsible for generating a wake up event from the incoming interrupts and enable bits. The WUGEN is implemented in MPU Always-On power domain.

MPU\_WUGEN has a 160-bit enable fields (from WKG\_ENB\_A\_x to WKG\_ENB\_E\_x for MPU\_Cx, where x = 0 or 1), which define the interrupt that wakes up the MPU cores. Note that each MPU core cannot be independently woken up by interrupts. Instead, an enabled interrupt wakes up both MPU cores (except if MPU\_C1 is in FORCED\_OFF state). Therefore, the MPU\_WUGEN is designed to handle interrupts for both MPU cores and generates a single wake-up request.

All interrupts are enabled after reset as wake up events. Software must first disable the WUGEN events during the interrupt initialization and then set the wake up event enable bit that corresponds to the desired interrupt. A given interrupt for a given MPU core is either enabled at both MPU\_INTC and MPU\_WUGEN, or disabled at both; no other combination is allowed.

Figure 11. MPU Wake Up Generator Block in MPU Subsystem

The following STW APIs can be used to initialize and enable the MPU WUGEN to enable the wake up event:

```

This API is used to initialize MPU_WUGEN. All wake up events will

\brief

be disabled after initialization.

\param

*

None

*

\return None.

*

**/

void MPU_WUGEN_Init(void);

/**

*

\brief

This API enables the CORE 0 wake up event for requested interrupt.

\param

intrNum - Interrupt number

*

\return None.

**/

void MPU_WUGEN_0_Enable(uint16_t intrNum);

*

\brief

This API enables the CPU1 wake up event for requested interrupt.

*

intrNum - Interrupt number

\param

*

\return None.

**/

```

void MPU\_WUGEN\_1\_Enable(uint16\_t intrNum);

The latency to enter the CPU IDLE state and wake up from it is given in Table 12.

• CASE 4: MPU Subsystem Auto Clock Gate (C1 Forced Off and C0 in Clock Gate)

In this configuration the MPU C1 is put to a forced off state with the steps mentioned in Case 2. Additionally, the CORE 0 along with the MPU Clock Domain is made to go to the Auto Clock Gate State whenever the CORE 0 has nothing to run and is again woken up by an event when the CORE 0 has to resume processing.

The steps to take the CORE 0 and subsequently CD\_MPU to clock gate state are shown below:

- 1. Program the MPU Clock Domain state to HW\_AUTO Mode.

- 2. Program the MPU LPRM Domain state to retention state.

- 3. Execute WFI instruction.

### CASE 5: MPU Subsystem Retention (C1 Forced Off and C0 in retention)

In this configuration, the MPU C1 is put to a forced off state with the steps as mentioned in Case 2. Additionally, the CORE 0 along with the MPU Power Domain is made to go to Closed Switch Retention State whenever the CORE 0 has nothing to run and is again woken up by an event when the CORE 0 has to resume processing.

The RETENTION low-power state is not natively supported by the MPU\_CLUSTER. This mode is implemented with SR3-APG power-management technology. The MPU subsystem power-management hardware is designed to ensure that the system does not have an L1 cache coherency problem when putting both MPU cores in retention mode. In this mode, the MPU\_Cx logic is in full retention with all memory content preserved by keeping the array of memories fully powered and the logic of the memory peripheries shut down. In slow wake-up mode, memories are put into retention to prevent more leakage.

The steps to take the CORE 0 and subsequently PD\_MPU to retention are shown below:

- 1. Program the Retention mode for MPU Subsystem.

- 2. Program the MPU Power Domain state to RET mode.

- 3. Program the MPU Clock Domain state to HW\_AUTO Mode.

- 4. Program the MPU CPU Domain state to RET mode.

- 5. Execute WFI instruction.

The STW APIs to configure the Retention and Fast Ramp-up are shown below:

```

/**

* \brief

Function to set the HG_EN bit for MPU Mercury retention.

\param None.

*

* \return None.

*/

void PMHALMpuLprmSetMercuryRetention(void);

/**

* \brief Function to set the Mercury Retention ramp parameters. This is to

*

be used only If the HG_EN bit is set.

*

Structure which holds the parameters to be set for

*

\param hgRampParam

*

correct mercury retention ramp.

*

If fast ramp is used then no need to fill the

*

hgSlowRampTime field.

```

#### Dynamic CPU Power Management

```

* \return status PM_SUCCESS If the ramp parameters are set

correctly.

* PM_BADARGS If the slow ramp is enabled and the

* ramp time provided is 0.

*/

```

int32\_t PMHALMpuLprmSetHgRampParams(

const pmhalMpuLprmHgRampParams\_t \*hgRampParam);

# The usage of these APIs is shown below when CPU 0 wants to go to Retention state along with the power domain configuration to retention:

```

/* Enable Fast Ramp Up */

pmhalMpuLprmHgRampParams_t hgRampParam = {1, 0};

/* Program the MPU to AUTO_CG. This will put the MPU PD to Retention */

pmlibSysConfigPowerStateParams_t inputTable = {

PMHAL_PRCM_MOD_MPU, PMLIB_SYS_CONFIG_AUTO_CG};

```

/\* CONFIG MPU MPU\_PRCM: Enable FastRamp-up in Retention \*/

PMHALMpuLprmSetHgRampParams(&hgRampParam);

/\* CONFIG MPU MPU\_PRCM: Enable Mercury Retention \*/

PMHALMpuLprmSetMercuryRetention();

```

/* CONFIG GLOBAL PRCM: Request AUTO CG and Retention */

status = PMLIBSysConfigSetPowerState(

&inputTable, 1, PM_TIMEOUT_NOWAIT, NULL);

```

```

/* Put MPU LPRM to retention and execute WFI */

status = PMLIBCpuIdle(PMHAL_PRCM_PD_STATE_RETENTION);

```

In order to wake up the MPU from retention, program the MPU WUGEN as described in CASE 3.

Table 12 summarizes the MPU power and clock states for the different cases seen and the associated latency to bring the MPU to low power state and wake up.

For an example implementation, see the STW examples in the folder: <STW Install Dir>\examples\pm\cpuidle.

# Table 12. MPU Power Management States and Latency

|                             |                                                               | С                               | ASE 1                          | CASE                            | 2          | CA                | SE 3       | CAS      | E 4            | CA       | ASE 5      |

|-----------------------------|---------------------------------------------------------------|---------------------------------|--------------------------------|---------------------------------|------------|-------------------|------------|----------|----------------|----------|------------|

|                             |                                                               | MPU C0                          | MPU C1                         | MPU C0                          | MPU C1     | MPU C0            | MPU C1     | MPU C0   | MPU C1         | MPU C0   | MPU C1     |

| Power state                 |                                                               | Always enabled                  | Always enabled                 | Always enabled                  | Disabled   | Always<br>enabled | Disabled   | Auto     | Disabled       | Auto     | Disabled   |

| Processing                  | Reference profile                                             | Dhrystone/Max/S<br>tall/ memcpy | Dhrystone/Max/Stall/<br>memcpy | Dhrystone/Max/Stal<br>I/ memcpy | idle       | idle              | idle       | idle     | idle           | idle     | idle       |

|                             | Utilization (%<br>Active)                                     | 100                             | 100                            | 100                             | 0          | 0                 | 0          | 0        | 0              | 0        | 0          |

| HGEN (LPRM<br>Retention Ena |                                                               |                                 | any                            | any                             | ,          | а                 | ny         | 1        | 1              |          | 1          |

|                             | P (LPRM Mercury<br>st Ramp Enable)                            |                                 | any                            | any                             | ,          | а                 | ny         | 1        |                |          | 1          |

| MPU LPRM<br>programed       | LPRM Power<br>State                                           | any                             | any                            | any                             | FORCED_OFF | ON                | FORCED_OFF | RET      | FORCED_O<br>FF | RET      | FORCED_OFF |

| Values                      | LPRM ClkTrCtrl                                                | any                             | any                            | any                             | HW_ AUTO   | HW_ AUTO          | HW_ AUTO   | HW_ AUTO | HW_ AUTO       | HW_ AUTO | HW_ AUTO   |

| MPU Core                    | Logic                                                         | ON                              | ON                             | ON                              | OFF        | ON                | OFF        | SR3-APG  | OFF            | SR3-APG  | OFF        |

| State MPU<br>Programmed     | L1\$                                                          | ON                              | ON                             | ON                              | OFF        | ON                | OFF        | RET      | OFF            | RET      | OFF        |

| Values                      | CPU internal<br>clock                                         | ON                              | ON                             | ON                              | OFF        | OFF               | OFF        | OFF      | OFF            | OFF      | OFF        |

|                             | Power state (at LPRM)                                         | ON                              | ON                             | ON                              | OFF        | ON                | OFF        | CSWRET   | OFF            | CSWRET   | OFF        |

|                             | PRCM<br>PowerState                                            |                                 | any                            | any                             |            | any               |            | ON       |                | RET      |            |

|                             | PRCM<br>LogicRetState                                         |                                 | any                            | any                             |            | any               |            | ON       |                | RET      |            |

|                             | PRCM<br>L2MemRetState                                         | any                             |                                | any                             |            | any               |            | ON       |                | RET      |            |

|                             | PRCM ClkTrCtrl                                                |                                 | any                            | any                             |            | any               |            | HW_AUTO  |                | HW_AUTO  |            |

| Resulting                   | Logic                                                         |                                 | ON                             | ON                              |            | ON                |            | ON       |                | ON       |            |

| MPU/System state            | L2\$                                                          |                                 | ON                             | ON                              |            | ON                |            | ON       |                | RET      |            |

| oluto                       | Clock State (at PRCM)                                         | ON                              |                                | ON                              |            | ON                |            | OFF      |                | OFF      |            |

|                             | Power state (at PRCM)                                         | ON                              |                                | ON                              |            | ON                |            | ON       |                | CSWRET   |            |

| Measured                    | Time taken to go<br>to low Power<br>state (µs) <sup>(1)</sup> |                                 | NA                             | 7.5                             |            | 1:                | 5.9        | 17       | .7             | 2        | 27.1       |

|                             | Time taken to<br>wake up (us)                                 |                                 | NA                             | NA <sup>(</sup>                 | 2)         | 3.15              |            | 5.1      |                |          | 6.7        |

(1) Contains Software Programming overhead.

(2) Requires full boot of the system for CPU1 to come out of Forced off state.

Dynamic CPU Power Management

# 5.1.3 Recommended Software Flow

The recommended software flow for the MPU dynamic power management is as shown in Figure 12 corresponding to Case 4.

- 1. The first step is to ensure the MPU C1 is put in forced-off state from the SBL.

- 2. The second step is a one-time initialization of the Retention parameters of the MPU subsystem and the system configuration of the MPU subsystem to allow it to go to the AUTO\_CG state. This step can be done during the application initialization phase.

- 3. The third step to allow the MPU to go to the low-power state can be called at run time between frames in the SYSBIOS Idle Task. The MPU wake up generation is programmed each time with any newly enabled interrupts to ensure the newly enabled interrupts can wake up the MPU from retention. Note that the PMLIBCpuldle API programs the MPU\_PRCM to allow the MPUs to go to retention.

| <pre>MPU WUGEN 1 DisableAll(); /* Flushing the DCache is required to ensure CPU0 does not get pipeline * stalled when the cache is enabled later and the cache invalidate is * performed. */ CP15DCacheCleanFlush(); PMLIBCpu1ForcedOff(); OFF in SBL</pre>                                 | <pre>/* Enable Hg/FastRampup in Retention*/ PMHALMpuLprmSetHgRampParams(</pre>                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>2 One Time CPU 0 Initialization (Beginning of Application) /* 1st param indicates the type of the ramp 0 - Slow Ramp up, 1 - Fast Ramp up, 2<sup>nd</sup> param The value set in this field determines the slow ramp-up time */ pmhalMpuLprmHgRampParams_t hgRampParam = {1, 0};</pre> | <pre>status = PMLIBSysConfigSetPowerState( &amp;inputTable, 1, PM_TIMEOUT_NOWAIT, NULL); 3 Call @ Run Time between Frames (SYSBIOS Idle Task) /* Configuring enabled Interrupts to be wakeup capable */ MPU WUGEN 0 Interrupt Lookup(); PMLIBCpuIdle(</pre> |

| Programs MPU_PRCM                                                                                                                                                                                                                                                                           | PMHAL_PRCM_PD_STATE_RETENTION);                                                                                                                                                                                                                             |

Figure 12. MPU Recommended Dynamic Power Management Software Flow

# 5.2 DSP Power Management

**NOTE:** This section is valid for TDA2x, TDA2ex and TDA3x.

# 5.2.1 DSP PM Blocks

The DSP performs power management with the help of the DSP Power-Down Controller (PDC) at the TMS320C66x DSP CorePac level and Sys Control/Wake up Logic at the a Subsystem level, which interacts with the SoC level Global PRCM. The Sys Control Logic is in the always on power domain.

The DSP PDC in the C66x CorePac can help enter the following power-down modes:

- During SPLOOP instruction execution L1P Memory is powered down.

- The L2 Memory is treated as Retention unTil Access (RTA) memory providing dynamic page-based automatic wake up.

- Cache control hardware is powered down when caches are disabled.

- DSP is powered down upon issuing an IDLE instruction.

Entire that C66x Core Pac is powered down when the IDLE instruction is executed by the DSP and the PDCCMD register is programmed to put the C66x Core Pac to power down.

Further details on the DSP C66x Core Pac Power Management are shared in the *Power-Down Controller* section of the *TMS320C66x DSP CorePac User's Guide* (SPRUGW0) [5].

## 5.2.2 DSP PM States

This section looks at the different power states of the DSP subsystem and understands the power down and wake up latencies based on the power savings. Contact your TI representative to get access to the TDA2xx/TDA2ex Power Estimation Spread Sheet and analyze the exact power savings for the different supported low power modes.

Figure 13. DSP Power States and Transitions

# • CASE 1: DSP ON

In this configuration, the DSP CPU is alive and running its software. This is the highest power consumption configuration; the power consumption is determined by the kind of operations the DSP is performing. The sub-modules in the DSP subsystem are ON and the clocks are running to the Subsystem and the C66x core.

CASE 2: DSP CPU Idle

In this configuration, the DSP is made to go to Idle state when the DSP has nothing to run and is woken up by an event when the DSP has to resume the operation.

- 1. Configure the wake up event by configuring IRQWAKEN or DMAWAKEN.