## ABSTRACT

The AM26x Hardware Design Guidelines is an essential document for hardware designers creating PCB systems based on the AM26x family of MCU devices. This document serves to integrate device-specific schematic and PCB layout recommendations by utilizing hardware design examples from the various AM263x, AM263Px, and AM261x evaluation modules (EVMs). The AM26x EVMs include the following hardware platforms:

| Device Family | Hardware Platform |              |                        |

|---------------|-------------------|--------------|------------------------|

|               | LaunchPad         | ControlCARD  | System on Module (SOM) |

| AM263x        | LP-AM263          | TMDSCNCD263  |                        |

| AM263Px       | LP-AM263P         | TMDSCNCD263P |                        |

| AM261x        | LP-AM261          |              | AM261-SOM-EVM          |

#### Table 1-1. AM26x Evaluation Module (EVM) Platforms

In general, AM26x LaunchPads are lower-cost, entry-level evaluation platforms, while ControlCARDs and SOMs are meant for engineers designing complex systems with higher I/O requirements.

Additional collateral documents and tools can be found in Section 16.

## **Table of Contents**

| 1 Introduction                                     | 5   |

|----------------------------------------------------|-----|

| 2 Power                                            |     |

| 2.1 Discrete DC-DC Power Solution                  | 11  |

| 2.2 Integrated PMIC Power Solution                 |     |

| 2.3 Power Decoupling and Filtering                 |     |

| 2.4 Estimated Power Consumption                    | 21  |

| 2.5 Power Distribution Network                     | 21  |

| 2.6 eFuse Power                                    |     |

| 3 Clocking                                         |     |

| 3.1 Crystal and Oscillator Input Options           |     |

| 3.2 Output Clock Generation                        |     |

| 3.3 Crystal Selection and Shunt Capacitance        |     |

| 3.4 Crystal Placement and Routing                  |     |

| 4 Resets                                           |     |

| 5 Bootstrapping                                    |     |

| 5.1 SOP Signal Implementation                      |     |

| 6 OSPI and QSPI Memory Implementation              |     |

| 6.1 ROM OSPI and QSPI Boot Requirements            |     |

| 6.2 Additional OSPI and QSPI References            |     |

| 7 Debug Interfaces                                 |     |

| 7.1 JTAG Emulators and Trace                       |     |

| 7.2 UART                                           | 54  |

| 8 USB                                              |     |

| 8.1 USB Device Mode                                |     |

| 8.2 USB Host Mode                                  | ••• |

| 9 Multiplexed Peripherals                          |     |

| 10 Digital Peripherals                             |     |

| 10.1 General Digital Peripheral Routing Guidelines |     |

| 10.2 Trace Length Matching                        | 58        |

|---------------------------------------------------|-----------|

| 11 Analog Peripherals                             |           |

| 11.1 General Analog Peripheral Routing Guidelines | 59        |

| 12 Layer Stackup                                  | <u>60</u> |

|                                                   |           |

| 12.1 Key Stackup Features<br>13 Vias              | 65        |

| 14 BGA Power Fan-Out and Decoupling Placement     |           |

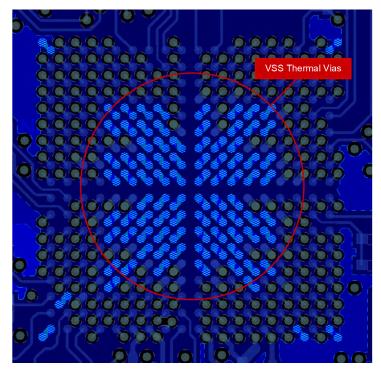

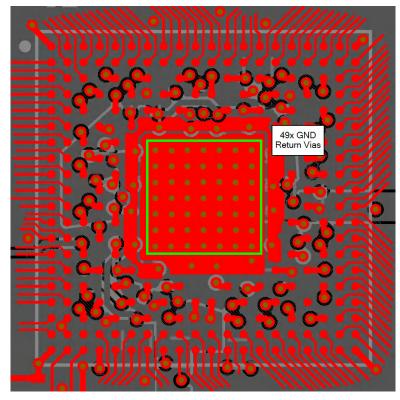

| 14.1 Ground Return                                | <u>66</u> |

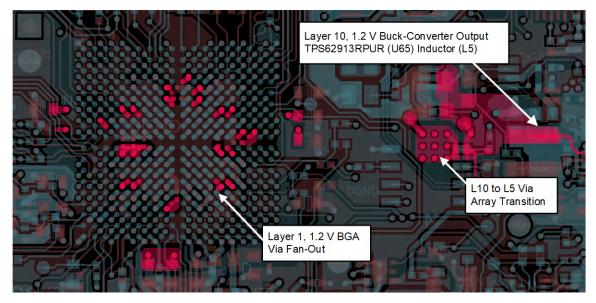

| 14.2 1.2V Core Digital Power                      | 69        |

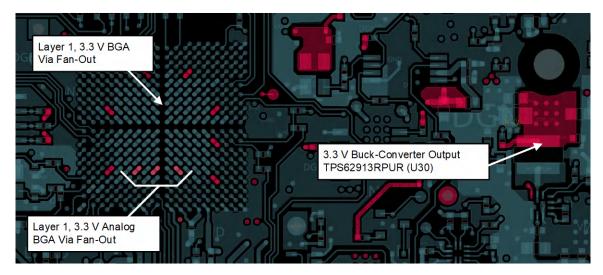

| 14.3 3.3V Digital and Analog Power                | 74        |

| 14.4 1.8V Digital and Analog Power                | 80        |

| 15 Summary                                        | 85        |

| 16 References                                     |           |

| 17 Revision History                               |           |

## List of Figures

| Figure 1-1. Typical AM26x System Block Diagram with Discrete Power (Based on LP-AM263 Launchpad Design)        |    |

|----------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2. Typical AM26x System Block Diagram with PMIC Power (Based on TMDSCNCD263P controlCard Design)      |    |

| Figure 1-3. Typical AM261x System Block Diagram with PMIC Power (Based on LP-AM261 Design)                     |    |

| Figure 2-1. AM263x DC-DC Regulator Example Design                                                              |    |

| Figure 2-2. AM263x LP-AM263 Schematic Excerpt 1.2V Core Power Implementation                                   |    |

| Figure 2-3. AM263x LP-AM263 Schematic Excerpt 3.3V System Digital, Analog I/O Power Implementation             |    |

| Figure 2-4. AM263x LP-AM263 Schematic Excerpt – Power Good Implementation (see PORz Reset Implementation)      |    |

| Figure 2-5. AM263Px TMDSCNCD263P PMIC Implementation                                                           |    |

| Figure 2-6. LP-AM261 PMIC Implementation                                                                       |    |

| Figure 2-7. AM263x LaunchPad Excerpt – 1.2V Power Decoupling Schematic                                         |    |

| Figure 2-8. AM263x LaunchPad Excerpt – 3.3V Digital I/O and Analog I/O Decoupling and Filtering Schematic      |    |

| Figure 2-9. AM263x LaunchPad Excerpt – 1.8V Digital I/O and Analog I/O Decoupling and Filtering Schematic      | 19 |

| Figure 2-10. AM263x LaunchPad Excerpt – ADC and DAC VREF Decoupling Schematic                                  |    |

| Figure 2-11. AM263Px controlCard Excerpt – additional VREFHI_G3 and VREFLO_G3 connections                      |    |

| Figure 2-12. AM26x PDN Requirements – Example Diagram                                                          |    |

| Figure 2-13. AM263x LaunchPad PDN Simulations – 1.2V Core Power Simulation Domain                              |    |

| Figure 2-14. AM263x LaunchPad PDN Simulations – 1.2V Core Power Simulated Z11                                  |    |

| Figure 2-15. AM263x LaunchPad PDN Simulations – 3.3V Digital and Analog I/O Power Simulation Domain (A)        | 26 |

| Figure 2-16. AM263x LaunchPad PDN Simulations – 3.3V Digital and Analog I/O Power Simulation Domain (layer 8,  |    |

| bottom)                                                                                                        | 26 |

| Figure 2-17. AM263x LaunchPad PDN Simulations – 3.3V Digital I/O Power Simulated Z11                           |    |

| Figure 2-18. AM263x LaunchPad PDN Simulations – 3.3V Analog I/O Power Simulated Z11                            |    |

| Figure 2-19. AM26x eFuse VPP - External Power Supply Implementation                                            |    |

| Figure 2-20. AM263Px/AM261x eFuse VPP - Internal Analog LDO Implementation.                                    |    |

| Figure 3-1. Excerpt From AM263x Control Card Schematics (for full crystal and oscillator input requirements)   |    |

| Figure 3-2. Excerpt From AM263x controlCard Schematics - Oscillator Clock Source and Clock Distributor         |    |

| Figure 3-3. Excerpt From AM263x LaunchPad Layout – CLKOUT0 and EXT_REFCLK0 Output                              |    |

| Figure 3-4. Excerpt From AM263x Launchpad Layout - Crystal Layout and Ground Ring Structure                    |    |

| Figure 4-1. Excerpt From AM263x Launchpad Schematic – PORz Generation                                          |    |

| Figure 4-2. Excerpt from AM263Px controlCARD Schematic- PORz Generation                                        | 34 |

| Figure 4-3. Excerpt from AM261x LaunchPad Schematic - PORz Generation.                                         |    |

| Figure 4-4. Excerpt From AM263x Control Card Schematic – PORz and WARMRSTn Pinout                              |    |

| Figure 4-5. Excerpt From AM263x Control Card Schematic – WARMRSTn Push-Button Open-Drain Driver                |    |

| Figure 5-1. Excerpt From AM263x Launchpad Schematic – SOP[3:0] Functional and SOP Paths                        |    |

| Figure 5-2. Excerpt From AM263x Launchpad Layout – All SOP[3:0] Functional and SOP Paths                       |    |

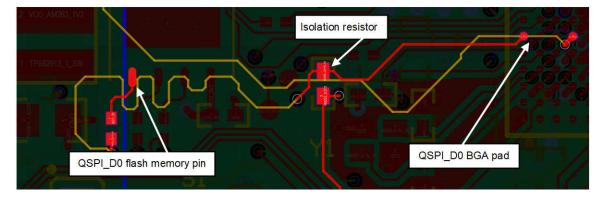

| Figure 5-3. Excerpt From AM263x Launchpad Layout – Highlighting SOP0/QSPI_D0 Path and SOP Isolation Resistor   |    |

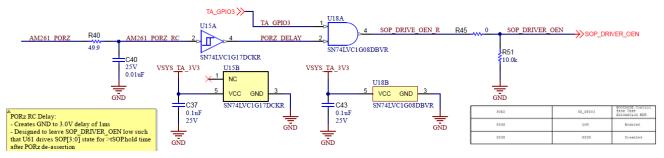

| Figure 5-4. LP-AM261 SOP Isolation Resistors.                                                                  |    |

| Figure 5-5. LP-AM261 SOP Isolation Mux                                                                         |    |

| Figure 5-6. LP-AM261 PORz SOP Driver RC Delay                                                                  |    |

| Figure 5-7. LP-AM261 SOP State Driver                                                                          |    |

| Figure 5-8. LP-AM261 SOP Isolation Mux Output Enable Generation                                                |    |

| Figure 5-9. LP-AM261 SOP Isolation - Layout                                                                    |    |

| Figure 6-1. Example AM263x QSPI Controller and NOR Flash Memory Schematic                                      |    |

| Figure 6-2. Example AM263Px OSPI Controller and NOR Flash Memory Schematic                                     | 43 |

| Figure 6-3. Excerpt From LP-AM263 Launchpad Layout – Highlighting SOP0/QSPI_D0 Path and SOP Isolation Resistor |    |

| Figure 6-4. AM26x QSPI - Routing Rules Diagram                                                                 | 45 |

| Figure 6-5. AM263Px. AM261x OSPI - Routing Rules Diagram                                                   | 45              |

|------------------------------------------------------------------------------------------------------------|-----------------|

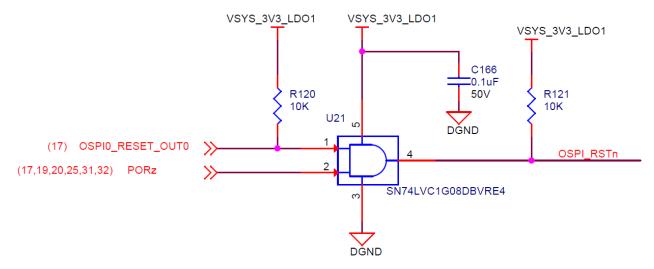

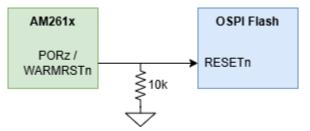

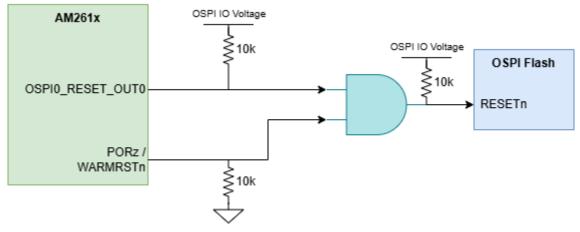

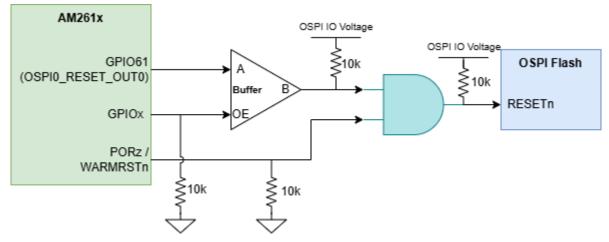

| Figure 6-6. AM263Px OSPI Reset Scheme                                                                      |                 |

| Figure 6-7. Resetting OSPI Flash Using PORz or WARMRESETn                                                  | 49              |

| Figure 6-8. Resetting OSPI Flash Using OSPI0_RESET_OUT0 and PORz, WARMRESETn                               | 50              |

| Figure 6-9. Resetting OSPI Flash using Buffered GPIO61 and PORz, WARMRESETn                                | <mark>51</mark> |

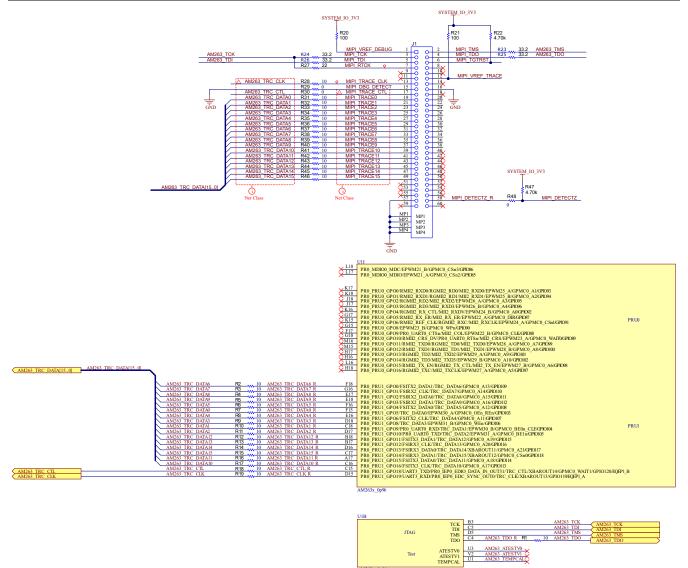

| Figure 7-1. Example MIPI-60 JTAG and 16-bit Trace Implementation                                           |                 |

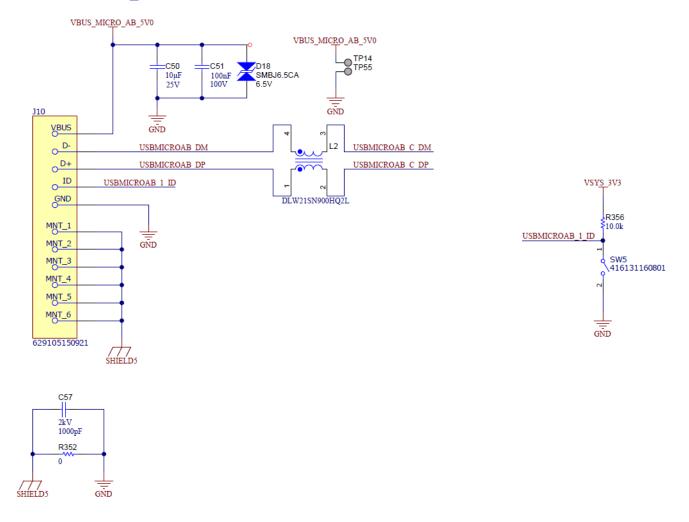

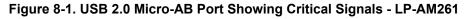

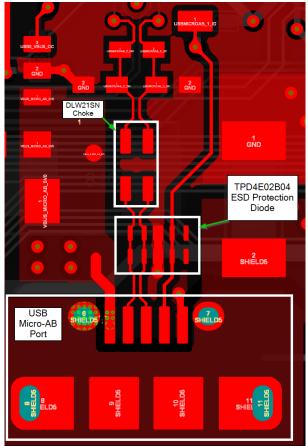

| Figure 8-1. USB 2.0 Micro-AB Port Showing Critical Signals - LP-AM261                                      | 54              |

| Figure 8-2. USB ESD Suppression - LP-AM261                                                                 |                 |

| Figure 8-3. USB Routing Example                                                                            |                 |

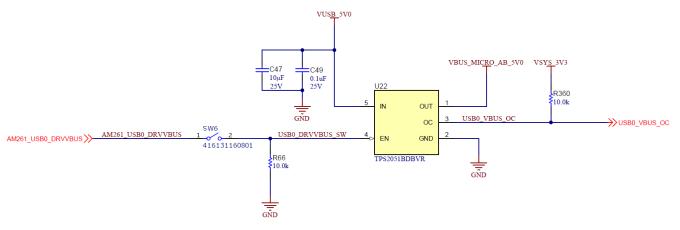

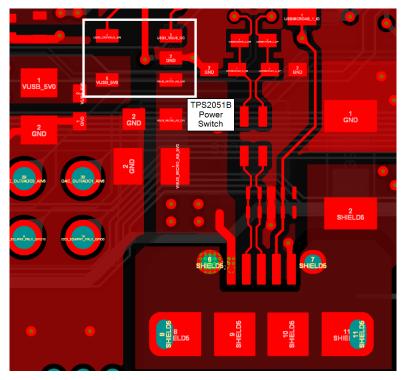

| Figure 8-4. USB Host Mode Power Switch - LP-AM261                                                          |                 |

| Figure 8-5. TPS2051B Layout Example - LP-AM261                                                             |                 |

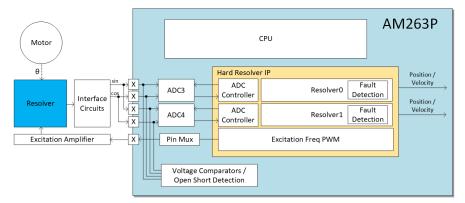

| Figure 11-1. AM263P Resolver ADC System                                                                    | <mark>59</mark> |

| Figure 12-1. LP-AM263 Stackup                                                                              |                 |

| Figure 12-2. LP-AM261 Stackup                                                                              |                 |

| Figure 12-3. AM261x ZFG/ZNC PCB System Stackup                                                             |                 |

| Figure 14-1. AM263x controlCARD Excerpt – Ground Return Vias Under AM263x BGA Layer 1 and Layer 2          |                 |

| Figure 14-2. AM263x controlCARD Excerpt – Ground Return Vias Under AM263x BGA Layer 10                     |                 |

| Figure 14-3. AM261x ZFG Routing Study - Ground Return Vias on Layer 1                                      |                 |

| Figure 14-4. AM261x ZNC Routing Study - Ground Return Vias on Layer 1                                      |                 |

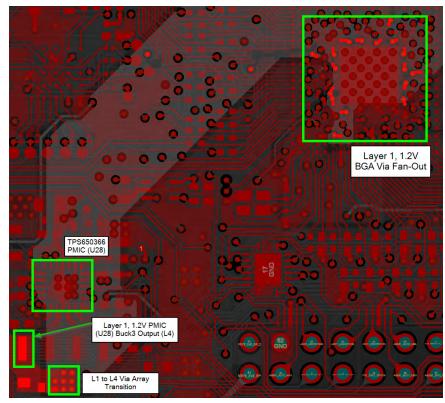

| Figure 14-5. AM263x controlCARD Excerpt - 1.2V Core Power Output, Power Plane Vias and BGA Vias            |                 |

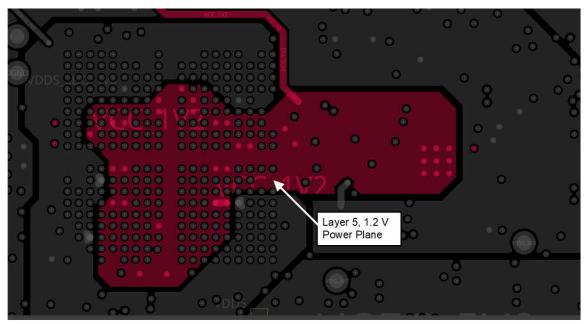

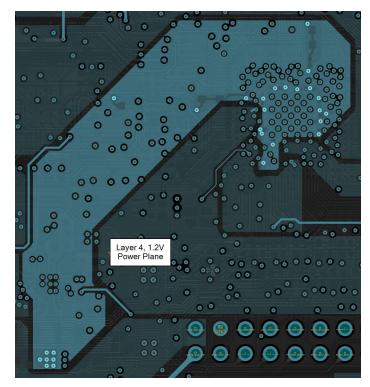

| Figure 14-6. AM263x controlCARD Excerpt – 1.2V Core Power Plane, Layer 5                                   | 70              |

| Figure 14-7. AM263x controlCARD Excerpt – 1.2V Core Power Decoupling Mounting, Layer 10                    |                 |

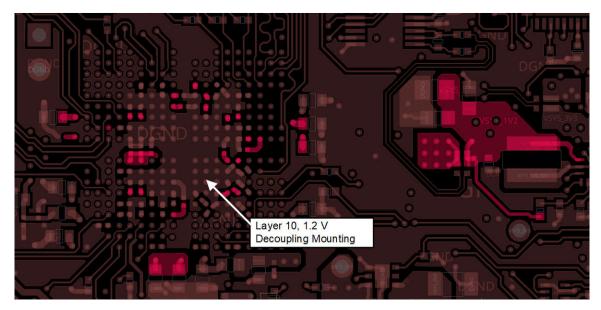

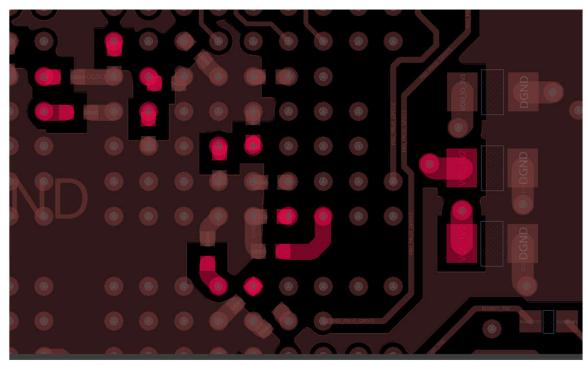

| Figure 14-8. AM263x controlCARD Excerpt – 1.2V Core Power Decoupling Mounting, Layer 10                    |                 |

| Figure 14-9. AM261x LaunchPad Excerpt – 1.2V Core Power Output, Power Plane Vias and BGA Vias              |                 |

| Figure 14-10. AM261x LaunchPad Excerpt – 1.2V Core Power Plane, Layer 4                                    |                 |

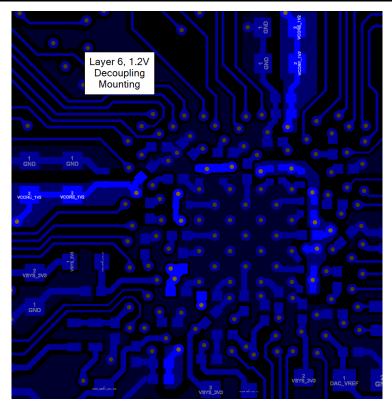

| Figure 14-11. AM261x LaunchPad Excerpt – 1.2V Core Power Decoupling Mounting, Layer 6                      |                 |

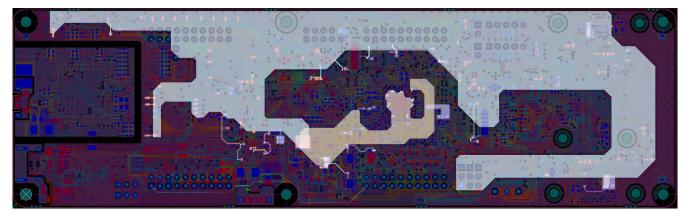

| Figure 14-12. AM263x controlCARD Excerpt – 3.3V Digital and Analog Power Planes on Layer 5 and Layer 6     |                 |

| Figure 14-13. AM263x controlCARD Excerpt – 3.3V Digital I/O and Analog I/O BGA Pinout and Regulator Output |                 |

| Figure 14-14. AM263x controlCARD Excerpt – Common 3.3V Plane Transition Vias                               |                 |

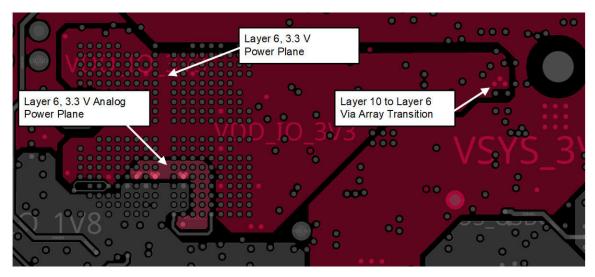

| Figure 14-15. AM263x controlCARD Excerpt – 3.3V Digital and Analog Planes Layer 6                          |                 |

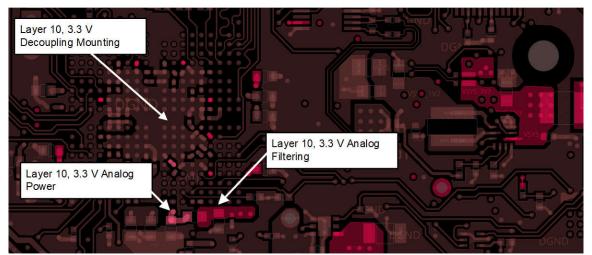

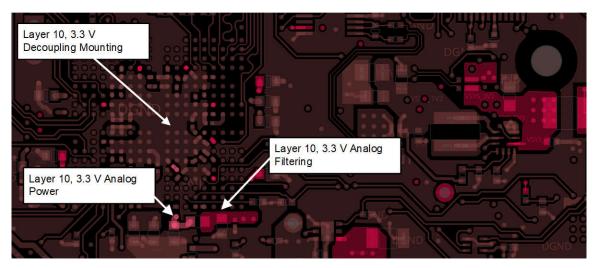

| Figure 14-16. AM263x controlCARD Excerpt – 3.3V Digital and Analog Power Decoupling Mounting, Layer 10     |                 |

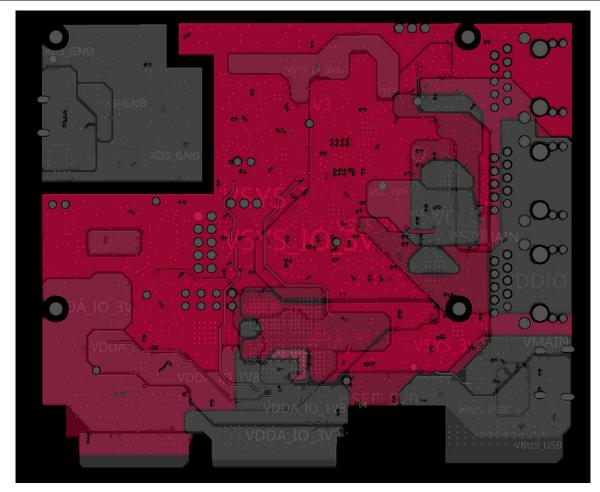

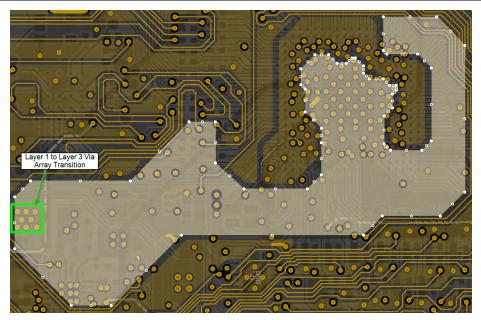

| Figure 14-17. AM261x LaunchPad Excerpt – 3.3V Digital and Analog Power Planes on Layer 3 and Layer 4       | 77              |

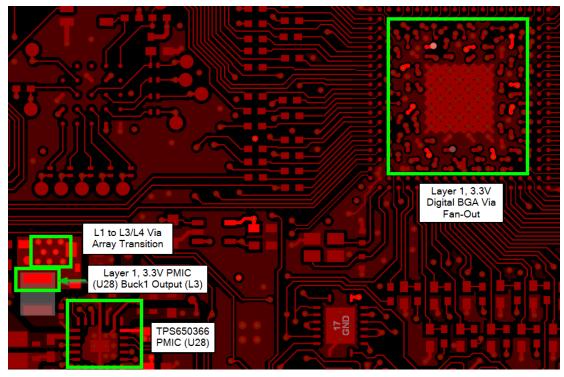

| Figure 14-18. AM261x LaunchPad Excerpt – 3.3V Digital I/O BGA Pinout and PMIC Output                       | 78              |

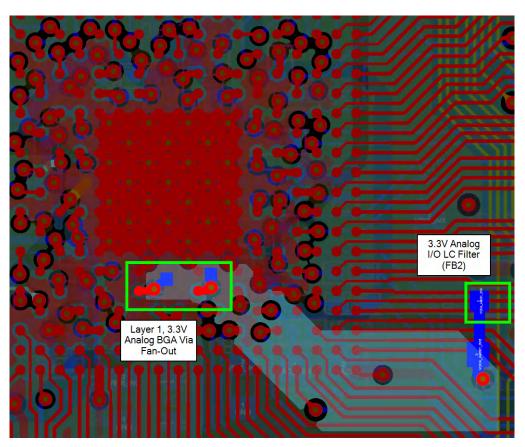

| Figure 14-19. AM261x LaunchPad Excerpt - 3.3V Analog IO BGA Pinout                                         |                 |

| Figure 14-20. AM261x LaunchPad Excerpt – 3.3V Digital Plane on Layer 3                                     |                 |

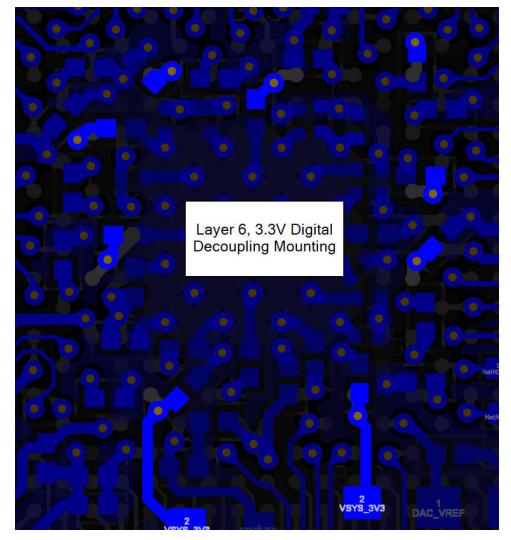

| Figure 14-21. AM261x LaunchPad Excerpt – 3.3V Digital Power Decoupling Mounting, Layer 6                   |                 |

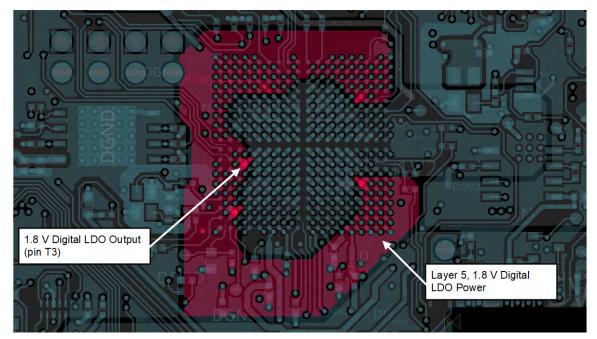

| Figure 14-22. AM263x controlCARD Excerpt – 1.8V Digital Power Via Fan-Out and Plane Routing Layer 6        | 80              |

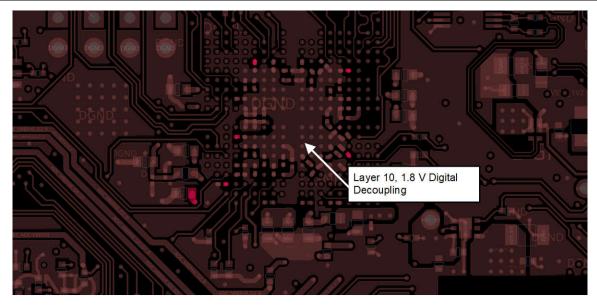

| Figure 14-23. AM263x controlCARD Excerpt – 1.8V Digital Power Decoupling on Layer 10                       |                 |

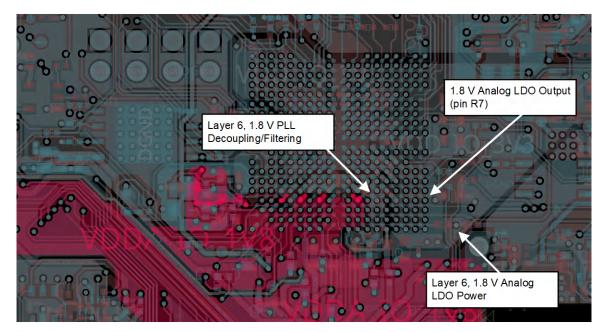

| Figure 14-24. AM263x controlCARD Excerpt – 1.8V Analog Power Via Fan-Out and Plane Routing Layer 6         |                 |

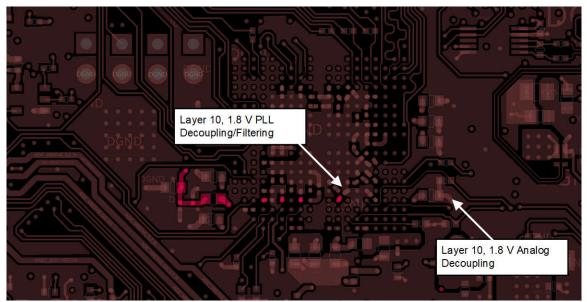

| Figure 14-25. AM263x controlCARD Excerpt – 1.8V Analog Power Decoupling on Layer 10                        |                 |

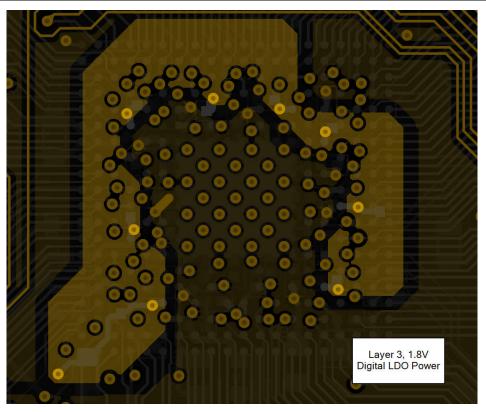

| Figure 14-26. AM261x LaunchPad Excerpt – 1.8V Digital Power Via Fan-Out and Plane Routing - Layer 3        |                 |

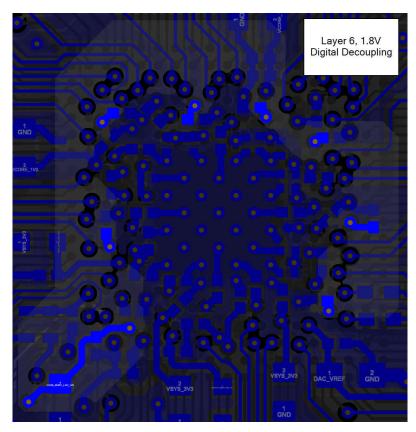

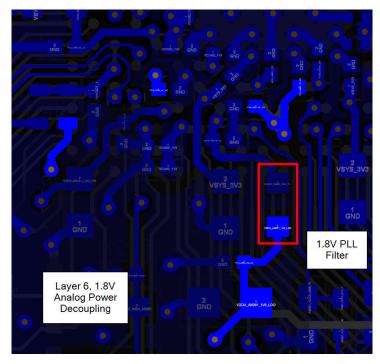

| Figure 14-27. AM261x LaunchPad Excerpt – 1.8V Digital Power Decoupling on Layer 6                          |                 |

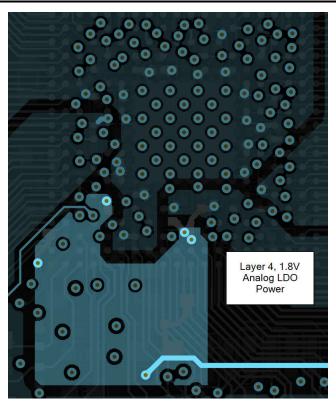

| Figure 14-28. AM261x LaunchPad Excerpt – 1.8V Analog Power Via Fan-Out and Plane Routing - Layer 4         |                 |

| Figure 14-29. AM261x LaunchPad Excerpt – 1.8V Analog Power Decoupling on Layer 6                           | 84              |

## List of Tables

| Table 1-1. AM26x Evaluation Module (EVM) Platforms                                                   | 1                |

|------------------------------------------------------------------------------------------------------|------------------|

| Table 1-1. Acronyms Used in This Document                                                            | 9                |

| Table 2-1. AM26x Core Voltage Requirements         Table 2-2. AM26x IO Voltage Requirements          | 10               |

| Table 2-2. AM26x IO Voltage Requirements                                                             | 10               |

| Table 2-3. AM26x PMICs                                                                               | 1 <mark>3</mark> |

| Table 2-4. TPS6538600QDCARQ1 Configuration for AM26x Devices                                         | 14               |

| Table 2-5. TPS65036x Configuration on LP-AM261                                                       | 15               |

| Table 2-6. TPS65036x Variants for AM261x                                                             | 15               |

| Table 2-7. AM263x, AM263Px, AM261x-ZCZ Recommended Decoupling per Power Net                          | 16               |

| Table 2-8. AM261x (all other packages) Recommended Decoupling per Power Net                          | 17               |

| Table 2-9. AM26x ADC/DAC VREF Decoupling                                                             | 20               |

| Table 2-10. Estimated Peak Power Consumption - Automotive-grade AM26x, R5F = 400MHz, 150°C Junction  |                  |

| Temperature                                                                                          | 21               |

| Table 2-11. Estimated Peak Power Consumption - Industrial-grade AM261x, R5F = 500MHz, 125°C Junction |                  |

| Temperature                                                                                          | <mark>21</mark>  |

| Table 2-12. AM26x Transient Current Model – Use-case Conditions                                      |                  |

|                                                                                                      |                  |

| Table 2-13. AM26x Transient Current Model – Resulting PDN Requirements                              |    |

|-----------------------------------------------------------------------------------------------------|----|

| Table 5-1. SOP and Functional Mode Signal Mapping.                                                  |    |

| Table 6-1. AM261x ZFG, ZEJ, ZNC Flash Power Nets                                                    |    |

| Table 6-2. AM26x QSPI – Recommended Routing Rules                                                   |    |

| Table 6-3. AM263Px, AM261x OSPI – Recommended Routing Rules                                         |    |

| Table 6-4. AM263x QSPI Pins Configured in Boot ROM.                                                 |    |

| Table 6-5. AM263Px OSPI Pins Configured in Boot ROM                                                 |    |

| Table 6-6. AM263Px-SIP Package OSPI Pins Configured in Boot ROM                                     |    |

| Table 6-7. AM261x ZCZ Package OSPI Pins Configured in Boot ROM                                      |    |

| Table 6-8. AM261x ZFG, ZEJ, ZNC Package OSPI Pins Configured in Boot ROM                            |    |

| Table 6-9. OSPI0_RESET_OUT0 Pin Options                                                             |    |

| Table 10-1. AM26x Digital Peripherals - Trace Length Matching                                       |    |

| Table 12-1. AM261x Package Sizes                                                                    | 60 |

| Table 12-2. Stackup Features by Package Size                                                        |    |

| Table 12-3. 6-Layer PCB: Layer Utilization                                                          |    |

| Table 12-4. AM263x, AM263Px, AM261x ZCZ Package, 6-Layer PCB: Controlled Impedance Planning Options |    |

| Table 12-5. 4-Layer PCB: Layer Utilization                                                          |    |

| Table 12-6. AM261x ZFG Package, 4-Layer PCB: Controlled Impedance Planning Options                  |    |

| Table 12-7. AM261x ZNC Package, 4-Layer PCB: Controlled Impedance Planning Options                  |    |

| Table 13-1. AM26x EVM Via Types                                                                     |    |

| Table 14-1. BGA Attribute Sections by Device Package                                                |    |

|                                                                                                     |    |

## Trademarks

Sitara<sup>™</sup> and LaunchPad<sup>™</sup> are trademarks of Texas Instruments. Arm<sup>®</sup> and Cortex<sup>®</sup> are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All trademarks are the property of their respective owners.

## **1** Introduction

The AM263x, AM263Px, and AM261x devices are single, dual, or quad-core Arm<sup>®</sup> Cortex<sup>®</sup>-R5F based MCUs in the Sitara<sup>™</sup> MCU family intended for industrial and automotive motion control applications.

#### Note

In this document, AM26x refers to the TI Sitara<sup>™</sup> MCU family of high-performance microcontrollers. This includes the AM263x, AM263Px, and AM261x devices. Device-specific references are denoted by the full general product number (AM263x, AM263Px, AM263Px, AM261x), while general device information are denoted by AM26x.

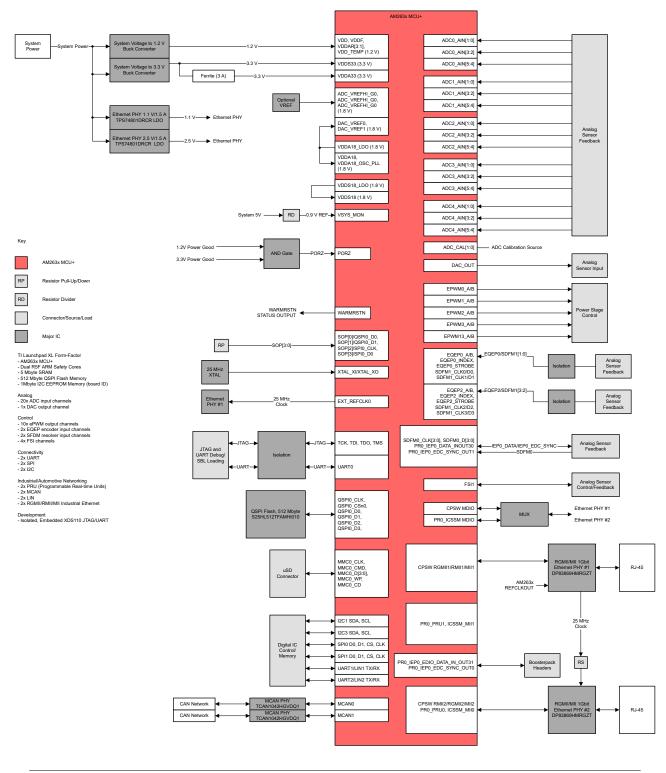

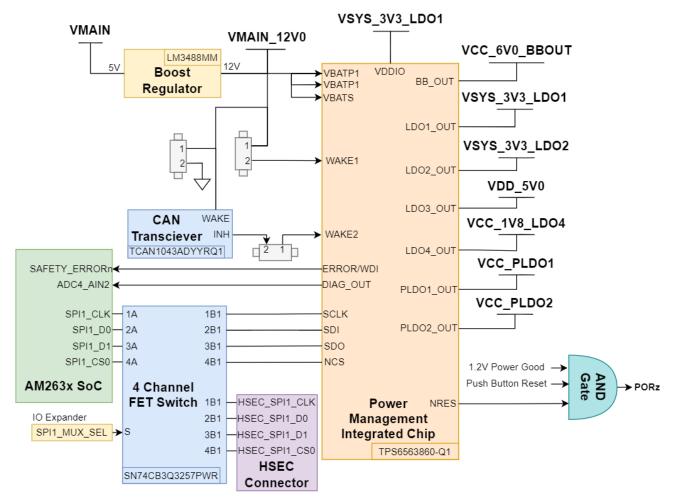

A typical AM26x design with a discrete power design is shown in Figure 1-1. This diagram is excerpted from the AM263x LaunchPad<sup>™</sup> (LP-AM263) system block diagram.

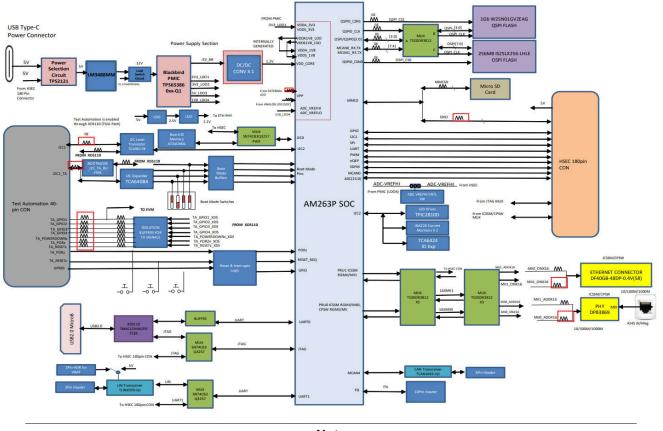

A typical AM26x design with a Power Management Integrated Circuit (PMIC)-based power design is shown in Figure 1-2. This diagram is excerpted from the AM263Px controlCard (TMDSCNCD263P) system block diagram.

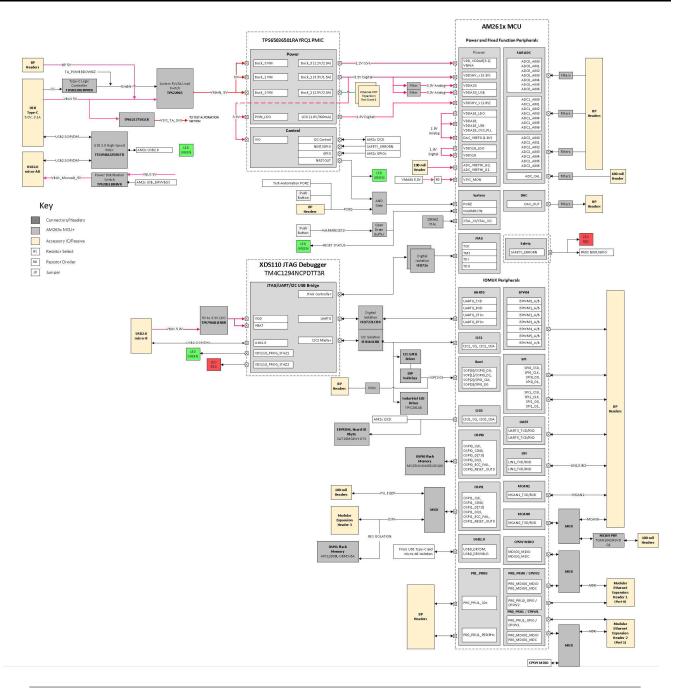

A typical AM261x design with a smaller footprint PMIC is shown in Figure 1-3. This diagram is taken from the AM261x LaunchPad (LP-AM261) system block diagram.

As seen in the following block diagrams, the AM26x devices offer designers a wide range of digital connectivity, control and analog sensor feedback options with multiple power design options supported.

The current requirement for the *System Voltage to 1.2V Buck Converter* for AM263x, AM263Px is 3A. For AM261x, the current limit is 2A.

# Figure 1-1. Typical AM26x System Block Diagram with Discrete Power (Based on LP-AM263 Launchpad Design)

For AM263x, AM263Px, the 1.2V DC/DC converter must output 3A. For AM261x, the DC/DC converter must be current limited to 2A.

# Figure 1-2. Typical AM26x System Block Diagram with PMIC Power (Based on TMDSCNCD263P controlCard Design)

Due to the current output of the Buck\_3 of the TPS6503600 (2A), this system block diagram is only applicable to AM261x systems. Note that for industrial-grade AM261x devices, the core voltage requirement is 1.25V. For automotive-grade AM261x devices, the core voltage requirement is 1.2V.

## Figure 1-3. Typical AM261x System Block Diagram with PMIC Power (Based on LP-AM261 Design)

This document must be referenced along with the other key AM26x collateral references. See Section 16 for a complete list of supplementary documents for the AM26x MCU devices.

| Acronym | Description                                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|

| EVM     | Evaluation Module. Referencing TI PCB assemblies such as the AM263x controlCard (TMDSCNCD263) or AM263x LaunchPad (LP-AM263).        |

| PDN     | Power Distribution Network. The active and passive components providing regulated power to a load such as the AM263x MCU power pins. |

| EMI     | Electromagnetic Interference                                                                                                         |

| PI      | Power Integrity                                                                                                                      |

| SI      | Signal Integrity                                                                                                                     |

| BOM     | Bill of Materials                                                                                                                    |

| PMIC    | Power Management Integrated Circuit                                                                                                  |

| SOM     | System on Module                                                                                                                     |

| LP      | LaunchPad                                                                                                                            |

| SoC     | System on a Chip                                                                                                                     |

#### Table 1-1. Acronyms Used in This Document

## 2 Power

### AM26x Device Power Rails

AM26x devices have two main device power nets: The core voltage rail, and the IO voltage rail. Table 2-1 details the core voltage requirements for AM26x devices. Table 2-2 details the IO voltage requirements for AM26x devices.

Table 2-1 AM26x Core Voltage Requirements

| Device                                         | Core Voltage | Associated Core Power Nets |  |

|------------------------------------------------|--------------|----------------------------|--|

| AM263x                                         | 1.2V         | VDD_CORE                   |  |

|                                                |              | VDDAR                      |  |

| AM263Px                                        | 1.2V         | VDD_CORE                   |  |

|                                                |              | VDDAR                      |  |

| AM261x (Automotive-grade, 400MHz)              | 1.2V         | VDD_CORE                   |  |

|                                                |              | VDDAR                      |  |

| AM261x (Industrial-grade, 400MHz OR<br>500MHz) | 1.25V        | VDD_CORE                   |  |

|                                                |              | VDDAR                      |  |

#### Note

AM261x core voltage differs depending on the microcontroller Orderable Part Number (OPN). Industrial-grade AM261xA**O**... devices require 1.25V for the core supply for operation at 500MHz or 400MHz. Automotive-grade AM261xA**L**...Q1 and AM261xA**P**...Q1 devices require 1.2V for the core supply for operation at 400MHz or 200MHz. For more details on the AM261x OPNs, refer to the AM261x Sitara<sup>™</sup> Microcontroller data sheet.

| Device                                 | IO Voltage   | Associated Power Nets |

|----------------------------------------|--------------|-----------------------|

| AM263x                                 | 3.3V         | VDDS33                |

|                                        |              | VDDA33                |

| AM263Px                                | 3.3V         | VDDS33                |

|                                        |              | VDDA33                |

| AM261x (Industrial & Automotive-grade) | 3.3V         | VDDSHV_A              |

|                                        |              | VDDSHV_B              |

|                                        |              | VDDSHV_C              |

|                                        |              | VDDSHV_F              |

|                                        |              | VDDSHV_G              |

|                                        | 3.3V or 1.8V | VDDSHV_D              |

|                                        |              | VDDSHV_E              |

#### Note

AM261x power nets VDDSHV\_D and VDDSHV\_E can be either 3.3V or 1.8V, depending on what voltage level external flash is used. For more information, refer to Section 6.

Different power topologies, such as discrete supplies or Power Management ICs (PMICs) can be used to supply an AM26x system. The following sections detail the different types of topologies used.

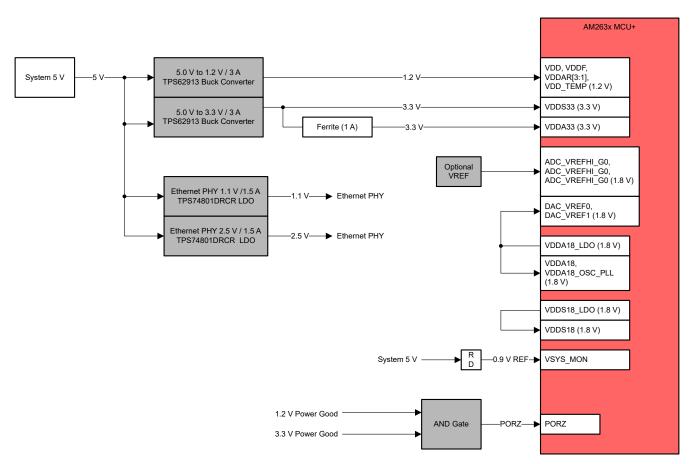

## 2.1 Discrete DC-DC Power Solution

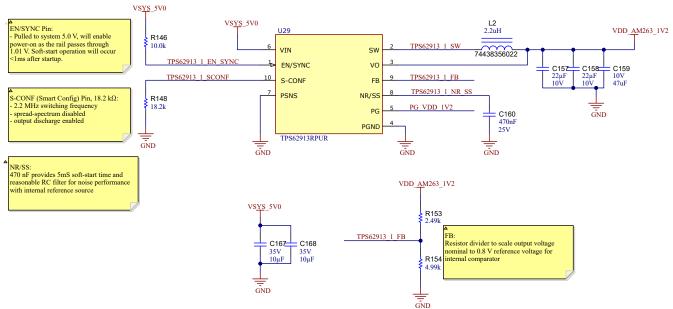

The AM263x LaunchPad and AM263x controlCard EVM designs both integrate a set of buck-converter, DC-DC regulators that are useful as a reference power design for some systems. This design consists of a pair of TPS62913 buck-converter regulators for the AM26x MCU core, system digital and analog I/O power, and a set of TPS74801 LDO for powering paired industrial Ethernet PHY.

Current and transient requirements of the DC-DC closed-loop and passive power plane and decoupling network are taken from the power consumption and transient loading tables: Table 2-12 and Table 2-13. Many DC-DC regulators can be matched to fit within these requirements and the maximum power consumption.

TI also recommends to use the power-good generation circuits available on these and similar DC-DC regulators to drive the power on reset (PORz) into the AM26x.

#### Note

For AM263x, AM263Px, and Automotive-grade AM261x devices, the core voltage (VDD) requirement is 1.2V. For Industrial-grade AM261x devices, the core voltage (VDD) requirement is 1.25V.

Figure 2-1. AM263x DC-DC Regulator Example Design

Figure 2-2. AM263x LP-AM263 Schematic Excerpt 1.2V Core Power Implementation

Figure 2-3. AM263x LP-AM263 Schematic Excerpt 3.3V System Digital, Analog I/O Power Implementation

# Figure 2-4. AM263x LP-AM263 Schematic Excerpt – Power Good Implementation (see PORz Reset Implementation)

## 2.2 Integrated PMIC Power Solution

A PMIC-based power tree allows for a more streamlined, single-chip design for controlling the power rails in an AM26x system. Several Texas Instruments PMICs are recommended for use with AM26x MCUs, and are detailed in the table below:

Table 2-3 AM26x PMICs

| PMIC Orderable Part Number                                                                                                                                               | AM26x Target Device | TI EVM / Reference Design Example  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|--|

| <ul> <li>TPS6538600QDCARQ1 + TPS6290x-Q1<sup>(1)</sup></li> <li>TPS62903x-Q1 = 3A supply for AM263x/<br/>AM263Px</li> <li>TPS62902x-Q1 = 2A supply for AM261x</li> </ul> | AM263x              |                                    |  |

|                                                                                                                                                                          | AM263Px             | AM263Px controlCARD (TMDSCNCD263P) |  |

|                                                                                                                                                                          | AM261x              | AM261x controlSOM (AM261-SOM-EVM)  |  |

| TPS65036x <sup>(2)</sup>                                                                                                                                                 | AM261x              | AM261x LaunchPad (LP-AM261)        |  |

| TPS65219x                                                                                                                                                                | AM263Px             |                                    |  |

| TPS65214x                                                                                                                                                                | AM261x              |                                    |  |

(1) TPS6290x-Q1 is required to supply the 1.2V (AM263x, AM263Px, Automotive-grade AM261x) / 1.25V (Industrial-grade AM261x) core voltage to the AM26x device. The correct orderable part number to supply 3A for AM263x and AM263Px and 2A for AM261x is required.

(2) There are multiple orderable part numbers of this PMIC associated with AM261x. See Table 2-6 for additional details.

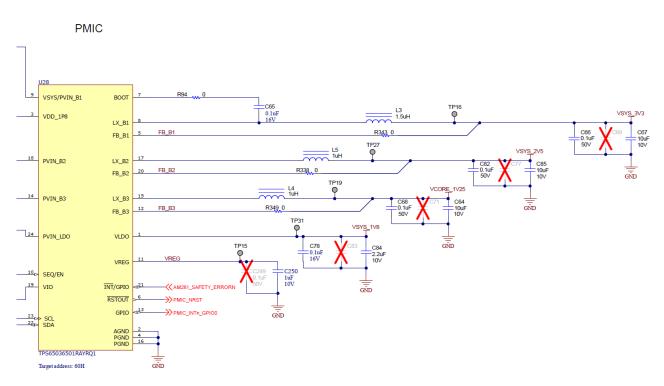

### Using TPS653860 with AM26x

The AM263Px controlCard EVM and AM261x controlSOM EVM designs make use of a multirail power supply for microcontrollers in safety-relevant applications (TPS6538600QDCARQ1). The PMIC integrates **four** supply rails to power the MCU, CAN, and other on-board peripherals.

**Note** This implementation requires a separate TPS62902QRYTQ1 (3A for AM263x/AM263Px) / TPS62902QRYTQ1 (2A for AM261x) buck converter to supply the AM26x core voltage

The NRES output of the PMIC needs to be used to help drive the PORz reset input to the AM263x, AM263Px, or AM261x device to make sure the power on sequencing of the power rails is complete before releasing the MCU from reset.

| Output Power Rail | Voltage      | Purpose                                                                 | Enabled at Power-On? |

|-------------------|--------------|-------------------------------------------------------------------------|----------------------|

| BB_OUT            | 6V           | Power input to separate 1.2V/1.25V regulator for AM26x VDD/VDDAR supply | √                    |

| LDO1_OUT          | 3.3V         | AM26x IO voltage supply                                                 | √                    |

| LDO2_OUT          | 3.3V         | System IO and peripheral hardware voltage supply                        | ✓                    |

| LDO3_OUT          | 5V           | System supply and peripheral hardware voltage                           |                      |

| LDO4_OUT          | 1.8V         | ADC voltage refrence supply                                             |                      |

| PLDO1_OUT         | CONFIGURABLE |                                                                         |                      |

| PLDO2_OUT         | CONFIGURABLE |                                                                         |                      |

SPI writes to the PMIC internal registers are required to enable power rails that do not come up by default at power-on.

#### Using TPS650360x with AM261x

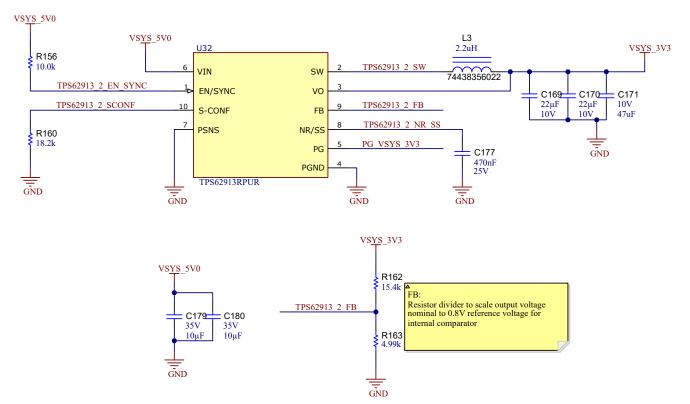

The AM261x LaunchPad EVM design makes use of the smaller-package, lower-cost TPS65036x PMIC. This PMIC integrates four supply rails to power the MCU and other on-board peripherals.

This PMIC can output 1.2V or 1.25V at 2A, which meets the VDD CORE supply requirements of the AM261x MCU. AM263x and AM263Px require 1.2V at 3A, so this PMIC must not be used to power these devices.

#### Figure 2-6. LP-AM261 PMIC Implementation

#### Table 2-5. TPS65036x Configuration on LP-AM261

| Output Power Rail | Voltage                                   | Purpose                                 | Enabled at Power-On? |

|-------------------|-------------------------------------------|-----------------------------------------|----------------------|

| •                 |                                           | •                                       |                      |

| BUCK1             | 3.3V                                      | AM261x IO voltage and peripheral supply | ✓                    |

| BUCK2             | 2.5V                                      | System Ethernet PHY supply              | √                    |

| BUCK3             | 1.25V (500MHz Industrial-grade<br>AM261x) | AM261x core voltage supply              | ✓                    |

| LDO               | 1.8V                                      | Flash IO voltage supply                 | ✓                    |

There are several variants of this PMIC depending on what supply voltages and features are required for an AM261x system.

| Orderable Part Number | BUCK1 | BUCK2 | BUCK3                                  | LDO                                  | WD Enabled |  |

|-----------------------|-------|-------|----------------------------------------|--------------------------------------|------------|--|

| TPS65036501RAYRQ1     | 3.3V  | 2.5V  | 1.25V (for Industrial-grade AM261x)    | 1.8V (for 1.8V IO<br>external flash) | YES        |  |

| TPS65036601RAYRQ1     | 3.3V  | 2.5V  | 1.2V (for Automotive-grade<br>AM261x)  | 1.8V (for 1.8V IO<br>external flash) | YES        |  |

| PTPS65036605RAYRQ1    | 5V    | 3.3V  | 1.25V (for Industrial-grade<br>AM261x) | 1.8V or 3.3V                         | YES        |  |

| TPS65036608RAYRQ1     | 3.3V  | 1.8V  | 1.25V (for Industrial-grade<br>AM261x) | BYPASS                               | YES        |  |

*Watchdog Enabled* refers to the PMIC's watchdog Long Window Timer, a 12 minute timer that stops the PMIC, MCU operation from hanging if the system is idle for 12 minutes or longer. This feature is relevant for applications where safety is a priority. When the Watchdog is enabled, the PMIC asserts a reset if left idle for 12 minutes.

For the TPS650360x variants with the Watchdog enabled, this can be disabled via an I2C write to the PMIC registers, or by connecting the GPIO pin (pin 13) to the VDD\_1P8 pin (pin 3) or any other supply that comes up **before** the PMIC ramps. If the watchdog is to be disabled using this hardware method, then the power supply pulling the GPIO pin high **must** ramp before the PMIC turns on. This way, the internal bit to disable the PMIC is set before the PMIC powers on.

The nRSTOUT output of the PMIC must be used to help drive the PORz reset input to the AM261x device to make sure the power on sequencing of the power rails is complete before releasing the MCU from reset. For more information, see Figure 4-3.

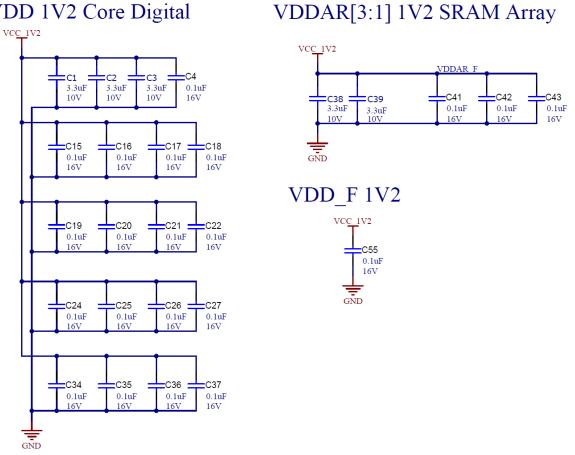

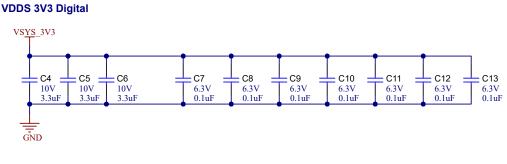

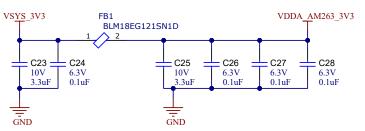

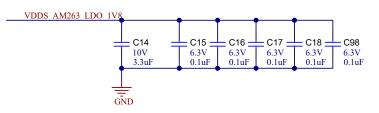

## 2.3 Power Decoupling and Filtering

Table 2-7 describes the initial BGA decoupling and power filtering required for the ZCZ package of the AM263x, AM263Px. and AM261x microcontrollers. These decoupling capacitor quantities and sizes were based on the initial simulation feedback of the Control Card EVM PCB and AM263x package with the transient use-cases shown in Table 2-12. Table 2-8 describes the BGA decoupling and power filtering required for the ZFG, ZNC, and ZEJ packages of the AM261x MCU. These packages support 3.3V and 1.8V flash IO on the OSPI/QSPI peripherals, and thus have slightly different device power rails compared to the ZCZ package devices, which only support 3.3V flash IO on the OSPI peripherals. Variation in overall power pin counts also account for differences in decoupling on the AM261x ZFG/ZNC/ZEJ packages.

The decoupling network presented in the sections below and in the AM263x EVM schematics and layouts are reasonable starting points for any AM263x, AM263Px, or AM261x PCB design. However, due to specific PCB routing differences and the resulting plane capacitance and decoupling mounting inductances and other parasitics, TI highly recommends that designers simulate and measure the specific power distribution network performance. Simulations and measurements are usually done with target application software active, and intended operating environment conditions applied to the system.

| Device Supply            | Quantity | Comment          | Part #              | Manufacturer |

|--------------------------|----------|------------------|---------------------|--------------|

| VDD_CORE                 | 17       | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |

|                          | 3        | 3.3uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |

| VDDAR[3:1]               | 2        | 3.3uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |

|                          | 3        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |

| VDDS18_LDO               | 1        | 3.3uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |

|                          | 1        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |

| VDDS18                   | 4        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |

| VDDA18_LDO               | 1        | 4.7uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |

|                          | 1        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |

| VDDA18                   | 2        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |

| VDDA18_OSC_PLL LC filter | 1        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |

|                          | 1        | Ferrite bead     | BLM18EG121SN1D      | Murata       |

| VDDS33                   | 7        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |

|                          | 1        | 3.3uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |

| VDDA33                   | 3        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |

|                          | 1        | 3.3uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |

|                          | 1        | Ferrite bead     | BLM18EG121SN1D      | Murata       |

#### Table 2-7. AM263x, AM263Px, AM261x-ZCZ Recommended Decoupling per Power Net

#### Table 2-7. AM263x, AM263Px, AM261x-ZCZ Recommended Decoupling per Power Net (continued)

| Device Supply               | Quantity | Comment          | Part #              | Manufacturer |

|-----------------------------|----------|------------------|---------------------|--------------|

| System 3.3V Power LC filter | 1        | 3.3uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |

|                             | 1        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |

## Table 2-8. AM261x (all other packages) Recommended Decoupling per Power Net

| Devrice Commite   | Package or Quantity |     |                  | Comment            | Devit #             | Manufacturer |

|-------------------|---------------------|-----|------------------|--------------------|---------------------|--------------|

| Device Supply     | ZFG                 | ZEJ | ZNC              | Comment            | Part #              | Manufacturer |

| VDD_CORE          | 13 12 18            |     | 0.1uF, 0201, X5R | GRM033R61A104KE15D | Murata              |              |

|                   |                     | 3   |                  | 3.3uF, 0603, X5R   | C1608X5R1A335K080AC | TDK          |

| VDDAR[3:2]        |                     | 2   |                  | 3.3uF, 0603, X5R   | C1608X5R1A335K080AC | TDK          |

|                   |                     | 2   |                  | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

| VDDS18_LDO        |                     | 1   |                  | 3.3uF, 0603, X5R   | C1608X5R1A335K080AC | TDK          |

|                   |                     | 1   |                  | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

| VDDS18            |                     | 1   |                  | 3.3uF, 0603, X5R   | C1608X5R1A335K080AC | TDK          |

|                   | 7                   | 8   | 8                | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

| VDDA18_LDO        |                     | 1   |                  | 4.7uF, 0603, X5R   | C1608X5R1A335K080AC | TDK          |

|                   | 2                   | 1   | 1                | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

| VDDA18_USB        |                     | 1   |                  | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

| VDDA18            |                     | 2   |                  | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

| VDDA18_OSC_PLL    | 1                   |     | 0.1uF, 0201, X5R | GRM033R61A104KE15D | Murata              |              |

| LC filter         | 1                   |     | Ferrite bead     | BLM18EG121SN1D     | Murata              |              |

| VDDSHV_D 1        |                     | 2   | 2                | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

|                   |                     | 1   |                  | 3.3uF, 0603, X5R   | C1608X5R1A335K080AC | Murata       |

| VDDSHV_E          |                     | 1   |                  | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

|                   |                     | 1   |                  | 3.3uF, 0603, X5R   | C1608X5R1A335K080AC | Murata       |

| VDDSHV_A          | 6                   | 5   | 6                | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

|                   |                     | 3   |                  | 3.3uF, 0603, X5R   | C1608X5R1A335K080AC | TDK          |

| VDDSHV_B          |                     | 1   |                  | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

| VDDSHV_C          |                     | 1   |                  | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

| VDDSHV_F          | 1                   |     | 0.1uF, 0201, X5R | GRM033R61A104KE15D | Murata              |              |

| VDDSHV_G          | N/A                 | 2   | N/A              | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

| VDDA33            | 2                   |     | 0.1uF, 0201, X5R | GRM033R61A104KE15D | Murata              |              |

| -                 | 1                   |     |                  | 3.3uF, 0603, X5R   | C1608X5R1A335K080AC | TDK          |

|                   | 1                   |     | Ferrite bead     | BLM18EG121SN1D     | Murata              |              |

| System 3.3V Power |                     | 1   |                  | 3.3uF, 0603, X5R   | C1608X5R1A335K080AC | TDK          |

| LC filter         | 1                   |     |                  | 0.1uF, 0201, X5R   | GRM033R61A104KE15D  | Murata       |

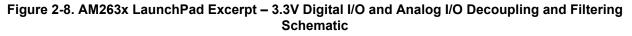

## VDD 1V2 Core Digital

Figure 2-7. AM263x LaunchPad Excerpt – 1.2V Power Decoupling Schematic

#### VDDS 1V8 Digital

#### VDDA 1V8 Analog

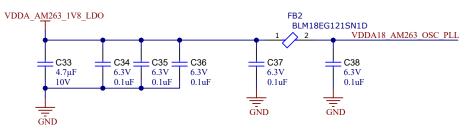

Figure 2-9. AM263x LaunchPad Excerpt – 1.8V Digital I/O and Analog I/O Decoupling and Filtering Schematic

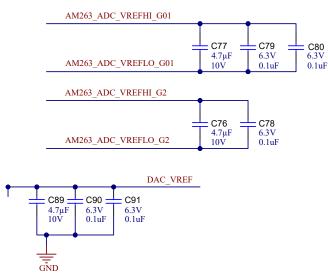

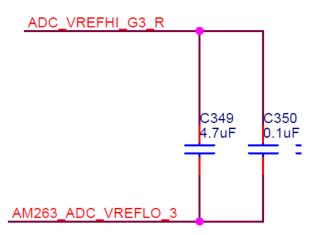

## 2.3.1 ADC/DAC Voltage Reference Decoupling

The ADC and DAC voltage reference pins on AM26x devices also require specific decoupling. The requirements are outlined in the table below.

| Table 2-3. AWZOX ADO/DAO VICET Decouping |          |                  |                     |              |  |  |

|------------------------------------------|----------|------------------|---------------------|--------------|--|--|

| ADC VREF                                 | Quantity | Comment          | Part #              | Manufacturer |  |  |

| ADC_VREFHI_G[1:0]                        | 1        | 4.7uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |  |  |

|                                          | 2        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |  |  |

| ADC_VREFHI_G[2]                          | 1        | 4.7uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |  |  |

|                                          | 1        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |  |  |

| ADC_VREFHI_G[3] <sup>(1)</sup>           | 1        | 4.7uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |  |  |

|                                          | 1        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |  |  |

| DAC_VREF[0]                              | 1        | 4.7uF, 0603, X5R | C1608X5R1A335K080AC | TDK          |  |  |

|                                          | 1        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |  |  |

| DAC_VREF[1] <sup>(2)</sup>               | 1        | 0.1uF, 0201, X5R | GRM033R61A104KE15D  | Murata       |  |  |

### Table 2-9. AM26x ADC/DAC VREF Decoupling

(1) The AM263Px Sensor Package (ZCZ\_S) has additional set of ADC reference voltages, ADC\_VREFHI\_G3 and ADC\_VREFLO\_G3.

(2) AM263x and AM263Px have an additional DAC reference voltage, DAC\_VREF1. An additional 0.1uF decoupling capacitor must be used at this pin.

#### Figure 2-10. AM263x LaunchPad Excerpt – ADC and DAC VREF Decoupling Schematic

Figure 2-11. AM263Px controlCard Excerpt – additional VREFHI\_G3 and VREFLO\_G3 connections

## 2.4 Estimated Power Consumption

This section outlines the latest estimates of the AM263x, AM263Px, and AM261x peak power consumption on a per device power net basis. These values can change as more power modeling and characterization is performed. This data can be used to scale peak DC-DC conversion power margin, perform IR drop analysis of the PCB layout, and help with thermal loading analysis.

These estimates are based on initial power simulations of the device when operating at 150°C junction temperature. For the latest characterized, peak power numbers, see the specific AM26x device data sheet.

A use-case based power estimation tool (PET) is also provided for the AM26x MCUs. These tools can help further bound the peak power based on specific core and peripheral utilization duty-cycle. The device-specific PET can be downloaded from the AM263x, AM263Px, and AM261x product pages.

# Table 2-10. Estimated Peak Power Consumption - Automotive-grade AM26x, R5F = 400MHz, 150°C Junction Temperature

| Device<br>Supply Name | Nominal<br>Voltage (V) | AM263x<br>Peak Current (mA) | AM263Px<br>Peak Current (mA) | AM261x<br>Peak Current (mA)     |     | Supply Description     |

|-----------------------|------------------------|-----------------------------|------------------------------|---------------------------------|-----|------------------------|

| VDD + VDDARn          | 1.2                    | 2500                        | 2800                         | 1750                            |     | Digital core power     |

| VDDS33                | 3.3                    | 200                         | 200                          | 3.3V IOs only <sup>(1)</sup>    | 200 | 3.3V digital I/O power |

|                       |                        |                             |                              | 1.8Vand 3.3V IOs <sup>(2)</sup> | 120 |                        |

| VDDA33                | 3.3                    | 100                         | 200                          | 100                             |     | 3.3V analog I/O power  |

(1) When all IOs are operating in the 3.3V domain

(2) When OSPI0 and OSPI1 IOs are operating in the 1.8V domain

# Table 2-11. Estimated Peak Power Consumption - Industrial-grade AM261x, R5F = 500MHz, 125°C Junction Temperature

| Device<br>Supply Name | Nominal<br>Voltage (V) | AM261x<br>Peak Current (mA)     |     | Supply Description     |

|-----------------------|------------------------|---------------------------------|-----|------------------------|

| VDD + VDDARn          | 1.25                   | 1500 [                          |     | Digital core power     |

| VDDS33                | 3.3                    | 3.3V IOs only <sup>(1)</sup>    | 200 | 3.3V digital I/O power |

|                       |                        | 1.8Vand 3.3V IOs <sup>(2)</sup> | 120 |                        |

| VDDA33                | 3.3                    | 100                             |     | 3.3V analog I/O power  |

(1) When all IOs are operating in the 3.3V domain

(2) When OSPI0 and OSPI1 IOs are operating in the 1.8V domain

## **2.5 Power Distribution Network**

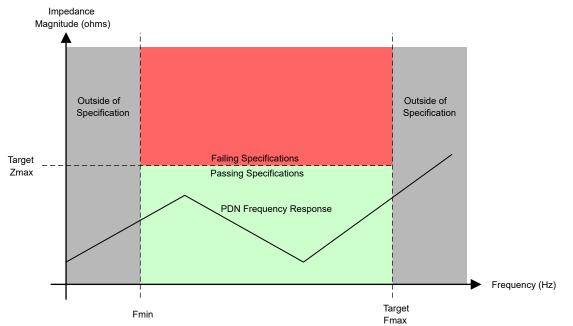

This section outlines the latest estimates of the AM26x transient current requirements on a per net basis. These values can change as more power modeling and characterization is performed.

These transient use-case values were used to constrain the PDN design of the AM26x EVMs (controlCards, LaunchPads, and controlSOM) by creating a set of minimum/maximum operating frequency and PDN impedance ( $Z_{max}$ ) target limits. These limits were based on the magnitude and slew-rate of simulated transient current use-cases. The use-cases were used to estimate the PDN bandwidth needed to adequately decouple the resulting transient event. Additional z-parameter simulation of the EVM PDN was used to verify that the power plane design and decoupling placement and component values meet the defined limits. This is summarized in Figure 2-12.

Figure 2-12. AM26x PDN Requirements – Example Diagram

| Transient Case         | Net Name  | Nominal<br>Voltage<br>(V) | DC IR<br>Budget<br>(%) | AC<br>Ripple<br>Budget<br>(%) | ldle<br>Current<br>(mA) | Peak<br>Current<br>(mA) | Idle to<br>Peak<br>Slew Rate<br>(ns) | Comment                                                                                            |

|------------------------|-----------|---------------------------|------------------------|-------------------------------|-------------------------|-------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------|

| VDDBASELINE<br>1       | VDD       | 1.2                       | 2.5                    | 2.5                           | 0                       | 2402                    | 2.5                                  | Baseline, simple transient model<br>assuming 0 to peak transition in<br>minimal 1 R5F clock cycle. |

| VDDXTAL_PLL<br>1       | VDD       | 1.2                       | 2.5                    | 2.5                           | 42                      | 875                     | 10                                   | XTAL to PLL turn-on transient                                                                      |

| VDD WFI1               | VDD       | 1.2                       | 2.5                    | 2.5                           | 750                     | 1117                    | 12.5                                 | 4x RF5 WFI event transient                                                                         |

| VDDS33BASELI<br>NE1    | VDDS33    | 3.3                       | 2.5                    | 2.5                           | 0                       | 84                      | 2.5                                  | Baseline, simple transient model<br>assuming 0 to peak transition in a<br>single R5F clock cycle   |

| VDDA33BASELI<br>NE1    | VDDA33    | 3.3                       | 2.5                    | 2.5                           | 0                       | 34                      | 2.5                                  | Baseline, simple transient model<br>assuming 0 to peak transition in a<br>single R5F clock cycle   |

| VDDS18LDOBA<br>SELINE1 | VDDS18LDO | 1.8                       | 2.5                    | 2.5                           | 0                       | 01                      | 2.5                                  | Baseline, simple transient model<br>assuming 0 to peak transition in<br>minimal 1 R5F clock cycle  |

| VDDA18LDOBA<br>SELINE1 | VDDA18LDO | 1.8                       | 2.5                    | 2.5                           | 0                       | 66                      | 2.5                                  | Baseline, simple transient model<br>assuming 0 to peak transition in<br>minimal 1 R5F clock cycle  |

| Transient Case         | Net Name  | Fmax<br>(MHz) | Current<br>Step(mA) | PCB DC<br>Tolerance<br>(mV) | PCB AC<br>Tolerance<br>(mV) | PCB<br>Target DC<br>IR(mΩ) | PCB<br>Target AC<br>Zmax(m<br>Ω) | Comment                                                                                            |  |

|------------------------|-----------|---------------|---------------------|-----------------------------|-----------------------------|----------------------------|----------------------------------|----------------------------------------------------------------------------------------------------|--|

| VDD<br>BASELINE1       | VDD       | 200           | 2402                | 30                          | 30                          | 12                         | 12                               | Baseline, simple transient model<br>assuming 0 to peak transition in<br>minimal 1 R5F clock cycle. |  |

| VDD<br>XTAL_PLL1       | VDD       | 50            | 833                 | 30                          | 30                          | 36                         | 36                               | XTAL to PLL turn-on transient.                                                                     |  |

| VDD<br>WFI1            | VDD       | 40            | 367                 | 30                          | 30                          | 82                         | 82                               | 4x RF5 WFI event transient.                                                                        |  |

| VDDS33<br>BASELINE1    | VDDS33    | 200           | 84                  | 83                          | 83                          | 982                        | 982                              | Baseline, simple transient model<br>assuming 0 to peak transition in<br>minimal 1 R5F clock cycle. |  |

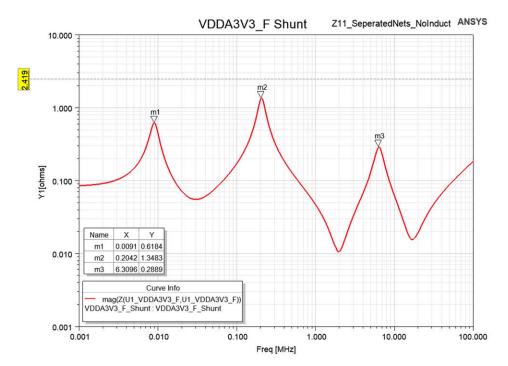

| VDDA33<br>BASELINE1    | VDDA33    | 200           | 34                  | 83                          | 83                          | 2419                       | 2419                             | Baseline, simple transient model<br>assuming 0 to peak transition in<br>minimal 1 R5F clock cycle. |  |

| VDDS18LDO<br>BASELINE1 | VDDS18LDO | 200           | 1                   | 45                          | 45                          | 45                         | 45                               | Baseline, simple transient model<br>assuming 0 to peak transition in<br>minimal 1 R5F clock cycle. |  |

| VDDA18LDO<br>BASELINE1 | VDDA18LDO | 200           | 66                  | 45                          | 45                          | 682                        | 682                              | Baseline, simple transient model<br>assuming 0 to peak transition in<br>minimal 1 R5F clock cycle. |  |

## Table 2-13. AM26x Transient Current Model – Resulting PDN Requirements

## 2.5.1 Simulations

The following simulated PDN z-parameter performance was extracted from the AM263x LaunchPad and controlCard layouts using Ansys SI wave. Wide-band s-parameter models of each of the selected capacitors were taken from the manufacturer. Simulations capture only 25°C (room temperature) PCB and capacitor model performance.

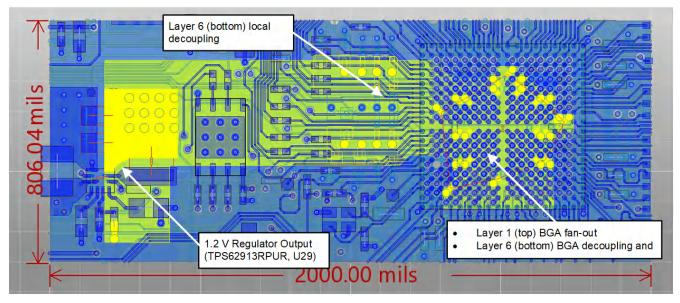

#### 2.5.1.1 Core Digital Power 1.2V

Z11 simulations were performed on the 1.2V core digital power net of the AM263x LaunchPad EVM to verify transient power margin. The simulation domain included the:

- AM263x BGA (UI) 1.2V digital and GND return fan-out

- Internal PCB 1.2V and GND return planes

- Decoupling placed on the 1.2V power net,

- U29 buck regulator output LC filter up to switch node

These simulations were done iteratively with multiple capacitor BOM changes made between each iteration. Each iteration was characterized primarily by the maximum and minimum frequency bandwidth below Ztarget (see above sections) and the BOM selection changed to maximize bandwidth and maximum Ztarget margin. Only the initial and final chosen BOM iterations are shown in Figure 2-13 and Figure 2-14.

Figure 2-13. AM263x LaunchPad PDN Simulations – 1.2V Core Power Simulation Domain

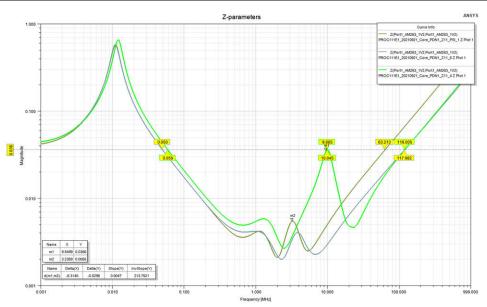

Figure 2-14. AM263x LaunchPad PDN Simulations – 1.2V Core Power Simulated Z11

- AM263x LaunchPad PDN Simulations 1.2V Core Power Simulated Z11

- This resulted in the marker (m2) point of  $5.5m\Omega$

- $Z_{target}$  requirement of 36m $\Omega$  maintained from 50KHz to 63MHz

- Major difference in BOM was replacing all 0.1µF BGA and local decoupling capacitors with 1.0µF capacitors this entirely removed the 10MHz resonant point in the PDN impedance spectrum

#### 2.5.1.2 Digital and Analog I/O Power 3.3V

Z11 simulations were performed on the 3.3V digital and analog power net of the controlCard EVM to verify transient power margin. The simulation domain included the:

- AM263x BGA (U1) 3.3V power and ground return BGA and fan-out

- Internal power and ground return routing layers

- Regulator output

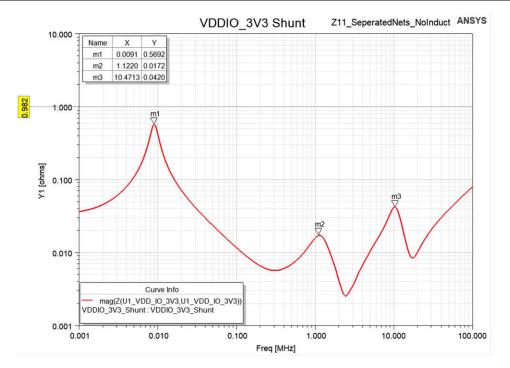

Initial runs of these simulations showed that no BOM changes were needed to meet the maximum and minimum frequency bandwidth below Ztarget (see above sections). Only the initial simulation with the final chosen BOM iterations are shown below.

The simulations were divided between the VDDS33 digital 3.3V plane and decoupling network and the VDDA33 analog 3.3V traces and decoupling local to the design. The difference between these simulations is the FL18 ferrite bead element that was used to separate these two decoupling performance simulations.

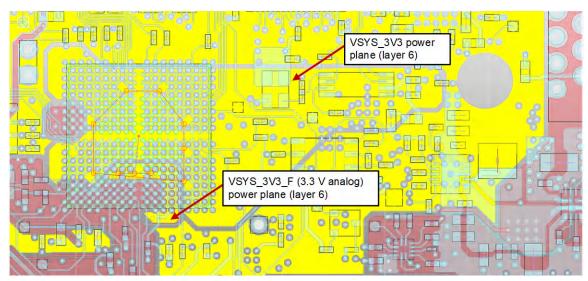

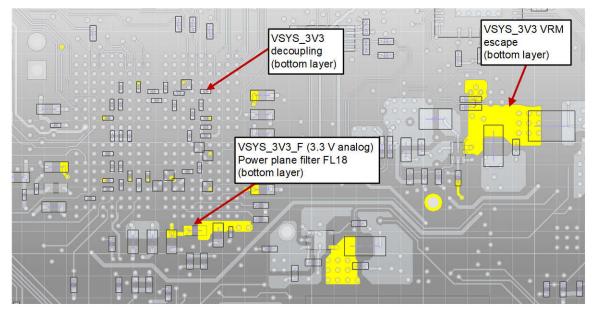

Figure 2-15. AM263x LaunchPad PDN Simulations – 3.3V Digital and Analog I/O Power Simulation Domain (A)

Figure 2-16. AM263x LaunchPad PDN Simulations – 3.3V Digital and Analog I/O Power Simulation Domain (layer 8, bottom)

Figure 2-17. AM263x LaunchPad PDN Simulations – 3.3V Digital I/O Power Simulated Z11

Figure 2-18. AM263x LaunchPad PDN Simulations – 3.3V Analog I/O Power Simulated Z11

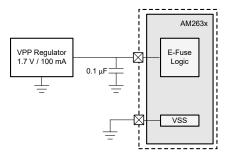

## 2.6 eFuse Power

The AM26x MCUs have a one-time programmable eFuse memory that can be utilized for storing customer cryptographic keys and other information specific to individual devices. These e-Fuse memory locations can only be programmed when the target device eFuse power pin (VPP), is powered by a 1.7V nominal output voltage, 100mA peak current supply. This 1.7V VPP power supply can be on-board, off-board or sourced from the AM26x devices' internal 1.8V LDO, re-programmed to the required 1.7V/100mA supply.

The eFuse programming typically follows one or both of the following scenarios:

- **Factory programming** eFuse memory programmed during post assembly test of the AM26x system.

- Field programming eFuse memory is programmed after the device has left the factory and is installed in the end-equipment.

If the factory programming scenario is required for a product, then implementing the VPP power supply off-board reduces the number of components required to be placed on the PCB assembly. The VPP supply is only be used during this programming sequence, so keeping this hardware on the board is not an efficient use of PCB floor plan area, BOM cost, or test time.

However, if the eFuse memory must be programmed outside the factory environment, the VPP power must either be supplied from an onboard component or from an attached accessory board that can supply this power as needed.

## External VPP Supply

The specific placement of the VPP supply and implementation depend on how the eFuse memory is utilized by the designer. The implementation must follow the diagram shown in Figure 2-19

Figure 2-19. AM26x eFuse VPP - External Power Supply Implementation

On the AM263x controlCARD design, the VPP supply is populated on the board to enable convenient eFuse programming for customers experimenting with this process. On the controlCARD, the TLV75801PDRVR LDO (U66) is used to drop down the 3.3V system I/O voltage to the VPP 1.7V.

## **On-Chip VPP Supply**

The AM263Px and AM261x MCUs have the option to source VPP internally using the 1.8V Analog LDO (ANALDO). The ANALDO must be overwritten to provide 1.7V during eFuse programming, then reverted back to normal operation.

Figure 2-20. AM263Px/AM261x eFuse VPP - Internal Analog LDO Implementation

For the full VPP electrical requirements and eFuse programming sequence, see the VPP Specifications for One-Time Programmable (OTP) eFuses section in the device-specific AM26x Technical Reference Manual.

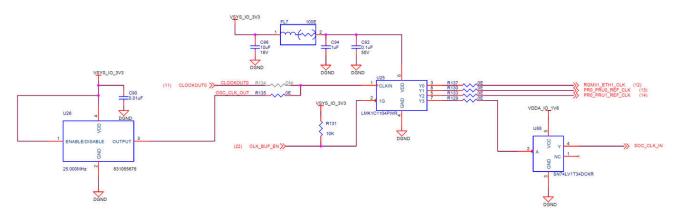

## 3 Clocking

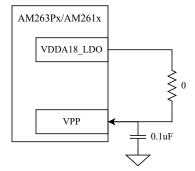

## 3.1 Crystal and Oscillator Input Options

The AM26x XTAL\_XI and XTAL\_XO clock input can be sourced from either an attached crystal or a single-ended oscillator output.

## **Crystal Clocking Mode**

The attached crystal needs to be a fundamental mode crystal operating at 25MHz. The crystal requires shunt capacitors, with capacitance ranging from 12pF-24pF. Figure 3-1 shows an example of the AM26x being clocked in crystal mode.

# Figure 3-1. Excerpt From AM263x Control Card Schematics (for full crystal and oscillator input requirements)

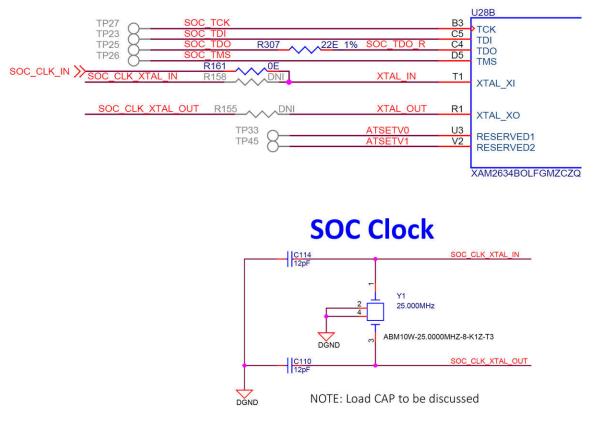

#### **Oscillator Clocking Mode**

If operating from a single-ended oscillator output, then the XTAL\_XI pin needs to be connected to the oscillator and the XTAL\_XO pin must be left floating, unconnected on the PCB. In oscillator input mode, the XTAL\_XI pin can be tied to either a 1.8V square wave or sine wave oscillator. For full oscillator input requirements, see the device specific AM26x data sheet. Figure 3-2 shows an example of an AM26x clock tree using a clock distributor and buffer circuit.

Figure 3-2. Excerpt From AM263x controlCard Schematics - Oscillator Clock Source and Clock Distributor

In the case of the AM263x Control Card, an onboard ABM10W-25.0000MHZ-8-K1Z-T3 25MHz crystal provides crystal mode clocking. Alternatively, an LMK1C1104PWR clock distributor circuit and SN74LV1T34 buffer provide the 1.8V square-wave clock to the XTAL\_XI pin. The LMK1C1104PWR is also used to provide a clock source to the onboard Ethernet PHY.

## 3.2 Output Clock Generation

The AM26x devices include two output clock sources, CLKOUT0 and CLKOUT1. These are intended to be used to clock attached peripheral IC such as Industrial/Automotive Ethernet PHYs. This can save on BOM cost and additional IC placement and routing space. The AM263x and AM263Px Launchpads include an optional path for the CLKOUT0 (pin M2) signal to clock the onboard DP83869HMRGZT Ethernet PHY. The AM261x LaunchPad includes an optional path for the CLKOUT1 pin signal to clock an Ethernet PHY via the Ethernet Add-on Board Connector. Unused CLKOUT pins can be left unconnected on the PCB.

The AM26x devices include one external reference clock source, EXT\_REFCLK0. This pin is intended to be used as an external reference clock input to the device clock generator PLL circuits. Unused EXT\_REFCLK pins can be left unconnected on the PCB. For more information on EXT\_REFCLK0, see the device-specific Technical Reference Manual.

## 3.3 Crystal Selection and Shunt Capacitance

In crystal operating mode, the AM26x can be interfaced to a wide variety of compatible crystals. Based on PCB parasitic capacitance and crystal selected, the additional load capacitance needs to be modified to achieve the best start-up stability and frequency accuracy.

For full crystal loading tolerances, see the device-specific AM26x data sheet.

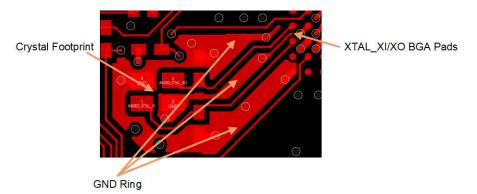

## 3.4 Crystal Placement and Routing

Crystal oscillator input needs to be placed as close as possible to the AM26x XTAL\_XI/XO with minimal length traces between crystal and MCU pads. A ground ring shorted to the local VSS plane needs to be placed adjacent and between the XTAL\_XI and XTAL\_XO traces to help prevent coupling from adjacent signals onto the clock higher impedance crystal input paths.

Figure 3-4. Excerpt From AM263x Launchpad Layout - Crystal Layout and Ground Ring Structure

## 4 Resets

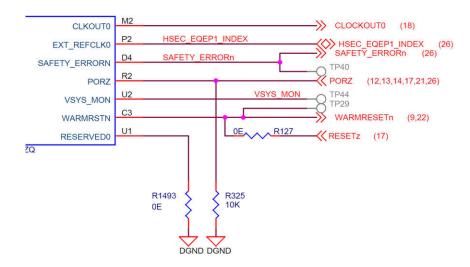

The AM26x MCUs have two hardware reset sources:

- PORz: Power on reset (logic low enable) pin

- Must be driven from the power-good circuits of the associated VDD 1.2V core and VDDS33 3.3V I/O regulators or PMIC reset signal

- For a valid reset the PORz signal must transition from logic low to logic high only after the VDD 1.2V core and VDDS33 3.3V I/O regulators are stable at the nominal values. For power-on-reset timing requirements, see the device-specific data sheet.

- WARMRSTn: Warm reset (logic low enable) input and reset status output pin

- At power-on, the default configuration sets this pin as open-drain output, which outputs the reset status of the device.

- When the device enters reset, this signal is driven logic low.

- When the device is fully out of reset, this signal is driven logic high.

### PORz

The PORz is intended to be kept at logic low at initial startup of the system. Once each regulator sourcing the AM26x power pins has been verified to be operating at nominal output voltage, then the PORz signal can be brought up to logic high. This action starts the MCU boot ROM execution, beginning with sampling of the SOP pins.

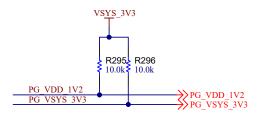

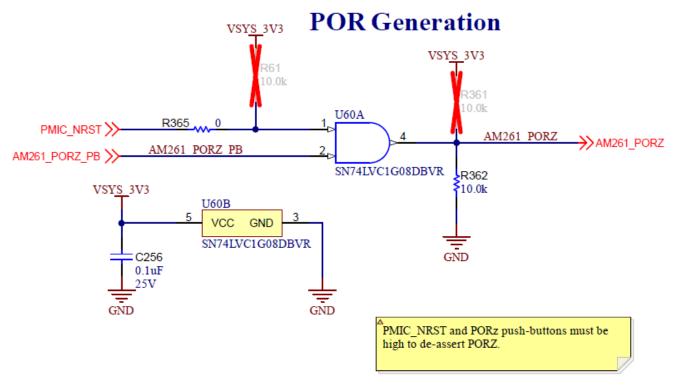

#### **PORz - Discrete Power Tree Implementation**

The AM263x LaunchPad implementation utilizes a single SN74LVC1G11 AND gate which takes the open-drain output power-good signals from the onboard DC-DC regulators and an optional push-button reset switch as inputs to the AND gate. A weak pull-down resistor is recommended on the PORz signal to keep the signal at logic low before system startup. PORz must be forced low if either VDD 1.2V or VDDS33 3.3V rail power goes below the nominal operating range.

Figure 4-1. Excerpt From AM263x Launchpad Schematic – PORz Generation

## **PORz - PMIC Based Power Design Implementation**

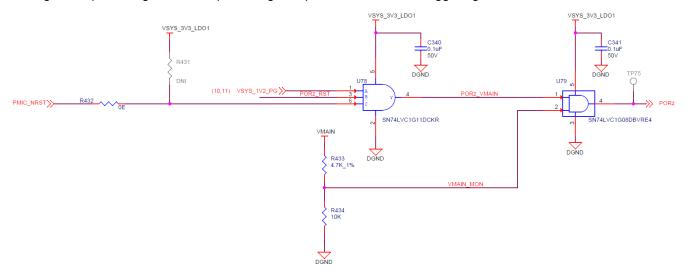

For AM26x systems that utilize a PMIC-based power design, the PORz logic is slightly more complex. On the AM263Px controlCARD, the open-drain output power-good signal from the 1.2V regulator, the optional push-button reset switch, and the nRST signal from the PMIC are inputs to a SN74LVC1G11 AND gate. The output of the 3-input AND gate is connected to the input of a 2-input SN74LVC1G08 AND gate, with the other input being the output of a voltage divider of the system input voltage (5V) divided down to 0.88V. The output of the SN74LVC1G08 is connected to the AM26x PORz. The SN74LVC1G08 low-level input voltage is 0.8V, so the AND gate outputs a logic 0 if the input voltage drops below 0.8V, thus triggering a reset.

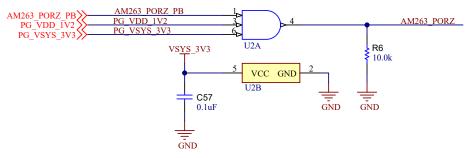

For AM261x system designs that use a single PMIC power design, such as TPS650360, the PORz generation is sourced from the PMIC nRSTOUT signal ANDed with a reset pushbutton. This is a simple and valid design that involves less redundancy and components.

For a full description of the power-on and power-off reset sequencing requirements, see the device-specific AM26x data sheet.

## WARMRSTn

The WARMRSTn pin is a multipurpose software reset input and hardware reset status pin. In the power-ondefault configuration, this pin is configured as an open-drain output and requires an external pull-up resistor to VDDS33 3.3V I/O voltage rail. In this mode, WARMRSTn can be used as an MCU reset indicator and can be used to drive reset input for attached peripheral IC such as Ethernet PHY and memories.

### Figure 4-4. Excerpt From AM263x Control Card Schematic – PORz and WARMRSTn Pinout

WARMRSTn can also be configured as a software reset. Additional software reset sources are available on the AM26x devices. For more information on reset functionality, see the *Reset* chapter in the device specific AM26x Technical Reference Manual.

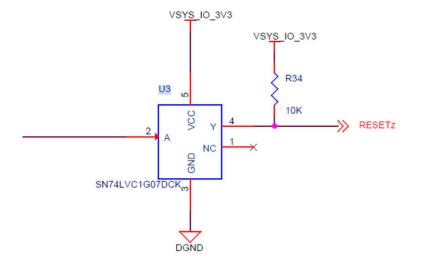

Because of the default open-drain configuration of this pin, if both the reset status output mode and the software reset input mode is needed in a design, open-drain buffers are recommended to drive the optional reset input status. In the case of the AM263x Control Card, a SN74LVC1G07 open-drain buffer is used to optionally drive the push-button WARMRSTn without conflicting with the reset status output which is used to reset the Ethernet PHY onboard during initial board power-on.

Figure 4-5. Excerpt From AM263x Control Card Schematic – WARMRSTn Push-Button Open-Drain Driver

# 5 Bootstrapping

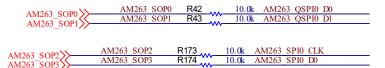

The sense-on-power (SOP) signals are used to latch in the selected boot mode into the AM26x device. During the PORz rising edge (low to high logic transition) the SOP[3:0] signals are sampled. The resulting 4 bits are used to branch the boot ROM into the selected boot mode. Not all combinations are supported. For a full description of the SOP pin states and supported boot modes, see the device-specific AM26x Technical Reference Manual.

# 5.1 SOP Signal Implementation

Each SOP bootmode selection signal is multiplexed with a subset of OSPI/QSPI and SPI peripheral functional mode signals. For all signal descriptions, see the *Signal Description* tables in the device-specific AM26x Data Sheet. The SOP signal descriptions are excerpted in Figure 5-1. The SoC pin number differs depending on device package type.

|                 |                       |                  | <u> </u>          | 1 0               |                   |

|-----------------|-----------------------|------------------|-------------------|-------------------|-------------------|

| SOP Mode Signal | Primary Pinmux Signal | AM26x<br>ZCZ Pin | AM261x<br>ZFG Pin | AM261x<br>ZNC Pin | AM261x<br>ZEJ Pin |

| SOP[0]          | OSPI0/QSPI0_D0        | N1               | R2                | N2                | M2                |

| SOP[1]          | OSPI0/QSPI_D1         | N4               | R1                | N1                | N1                |

| SOP[2]          | SPI0_CLK              | A11              | A13               | A12               | A12               |

| SOP[3]          | SPI0_D0               | C10              | B12               | B12               | A10               |

### Table 5-1. SOP and Functional Mode Signal Mapping

Because of this SOP/functional-mode multiplexing additional care must be taken in schematic and layout to make sure that the SOP mode selection resistors, jumpers or switch paths are routed in such a way that the SOP mode branches do not present inductive PCB trace stubs to the functional mode signal paths. Failing to take care of this can result in non-functional OSPI/QSPI or SPI.

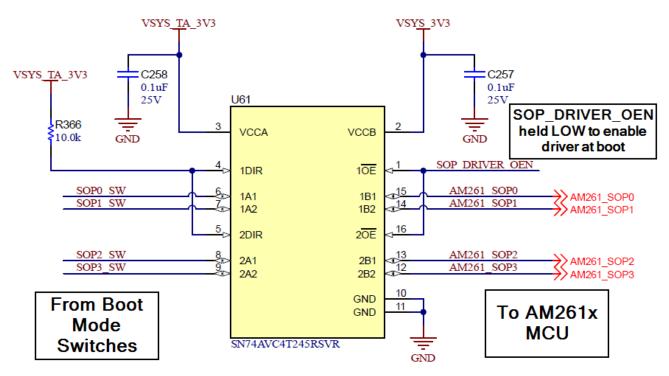

### Figure 5-1. Excerpt From AM263x Launchpad Schematic – SOP[3:0] Functional and SOP Paths

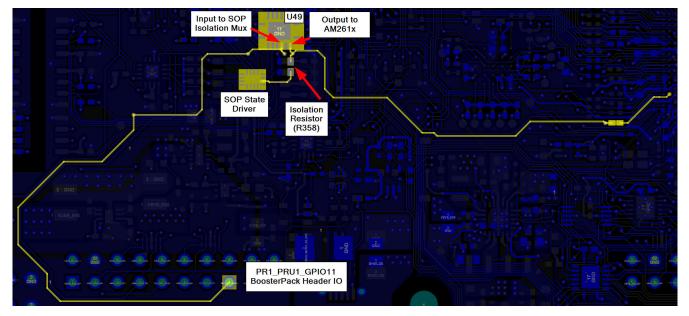

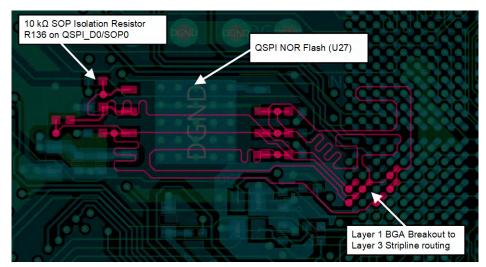

In the AM263x and AM263Px EVM designs, this SOP mode isolation is accomplished by including a  $10K\Omega$  resistor in the SOP signal path. The resistor is placed such that one pad is as close to the AM263x BGA pad and in-line with the functional mode path. This creates a layout where the additional stub length necessary to breakout the SOP path results in minimal impact to the functional mode operation of the signals, as shown in Figure 5-2 and Figure 5-3.

Figure 5-2. Excerpt From AM263x Launchpad Layout – All SOP[3:0] Functional and SOP Paths

Figure 5-3. Excerpt From AM263x Launchpad Layout – Highlighting SOP0/QSPI\_D0 Path and SOP Isolation Resistor

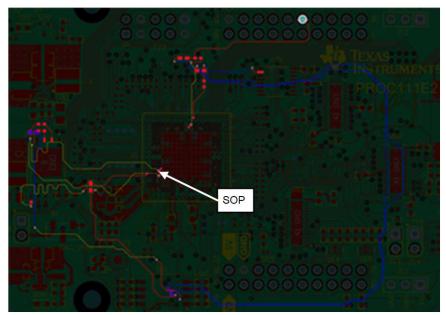

### AM261x ZFG, ZEJ, ZNC Package SOP Isolation

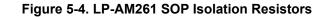

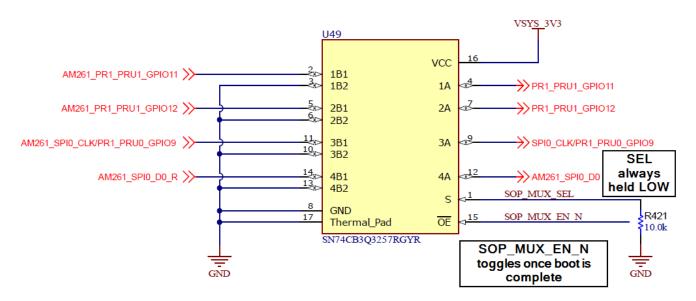

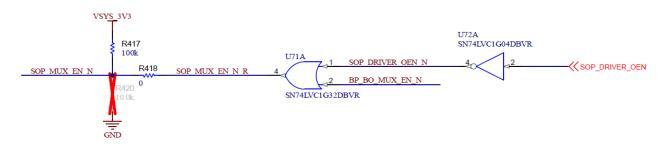

On the AM261x ZFG/ZEJ/ZNC package devices, additional isolation is required to prevent driving the SOP pins before boot is complete, as the functional mode signals shared with the SOP nets are capable of driving the SOP[3:0] states strong enough to disrupt the boot mode setting. This is accomplished on the AM261x LaunchPad by implementing a mux with SOP pin functional mode signals as the inputs, and the nets shared with the SOP signals as the outputs. The Output Enable pin on the mux is controlled by an RC delay circuit driven by the device PORz signal. The RC delay circuit holds the mux enable signal low long enough for the SOP[3:0] pins to be driven and the device boot mode to be latched, thus preventing any voltage applied to the functional mode pins from driving the SOP nets. This scheme is detailed in the following figures:

# AM261x SOP[3:0]

| AM261 SOP0    | AM261 SOP0 | R358 | 10.0k |                                                        |

|---------------|------------|------|-------|--------------------------------------------------------|

| AM261_SOPU    | AM261 SOP1 | R359 | 10.0k | AM261_PR1_PRU1_GPI011<br>AM261_PR1_PRU1_GPI012         |

| AM261_SOP1    | AM261 SOP2 | R328 | 10.0k | AM261_PR1_PR01_GPI012<br>AM261_SPI0_CLK/PR1_PRU0_GPI09 |

| AM261_SOP2    | AM261 SOP3 | R120 | 10.0k | AM261 SPI0 D0 R                                        |

| AW201_30F3 // |            | ***  |       | V AIVI201_3FIU_DU_K                                    |

Figure 5-5. LP-AM261 SOP Isolation Mux

### PORZ SOP Driver RC Delay

# **SOP State Driver**

Figure 5-7. LP-AM261 SOP State Driver

Figure 5-8. LP-AM261 SOP Isolation Mux Output Enable Generation

Figure 5-9. LP-AM261 SOP Isolation - Layout

The LP-AM261 implementation is likely more complex than necessary for a typical AM261x system due to the wide range of functions the EVM is required to support. For a simpler implementation, tying the delayed PORz signal to the isolation mux enable is sufficient. The key requirement is that there must be sufficient time for the SOP signals to latch the boot mode before any applied voltage is exposed to the shared functional signals.

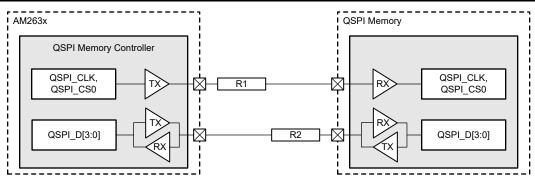

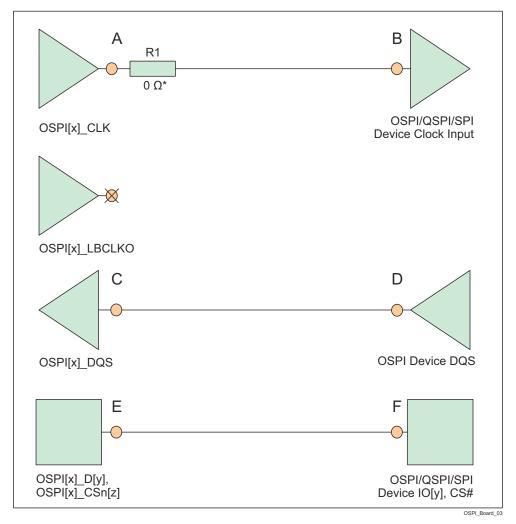

# **6 OSPI and QSPI Memory Implementation**

The OSPI Flash memory interface is the primary bootloader memory location for the AM263Px and AM261x MCUs, and the QSPI Flash memory interface is the primary bootloader memory location for the AM263x MCU. For a full description of boot ROM execution, including OSPI and QSPI boot information, see the device specific AM26x Technical Reference Manual. The correct OSPI and QSPI pins configured by the AM26x boot ROM are connected to the flash memory device if the intention is to boot from the flash.. Refer to Section 6.1 for additional details

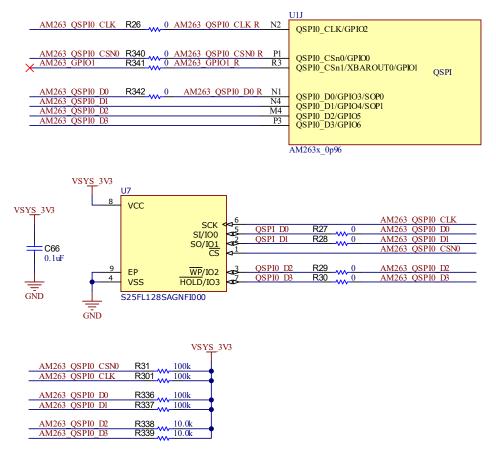

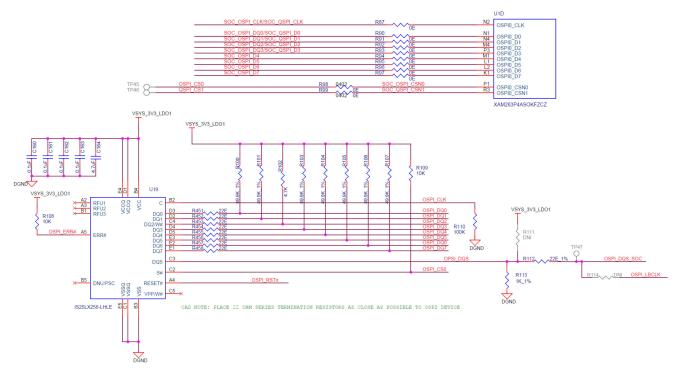

The excerpt from Figure 6-1 shows the implementation of the QSPI NOR flash interface from the LP-AM263 design.

Figure 6-1. Example AM263x QSPI Controller and NOR Flash Memory Schematic

The excerpt from Figure 6-2 shows the implementation of the OSPI NOR flash interface on the TMDSCNCD263P AM263Px controlCARD design.

Figure 6-2. Example AM263Px OSPI Controller and NOR Flash Memory Schematic

### **Series Termination Resistors**