# Using DMA with Framework Components for 'C64x+

Murat Karaorman, Gunjan Dang, Ezell Young

Software Development Organization

#### **ABSTRACT**

This application note describes the standard DMA software abstractions and interfaces for TMS320 DSP Algorithm Standard (xDAIS) compliant algorithms designed for the 'C64x+EDMA3 controller using DMA Framework Components utilities. The DMA Framework Component utilities described in this document include a standard DMA resource specification and negotiation protocol (IDMA3), a DMA Resource Manager (DMAN3), and a functional DMA interface and library (ACPY3) compliant with IDMA3. This document provides both reference information and guidelines for producers and consumers of IDMA3-compliant algorithms and components.

#### Contents

| 1 | Intro | oductio                                      | on                                                              |    |

|---|-------|----------------------------------------------|-----------------------------------------------------------------|----|

| 2 | Fun   | undamental Framework Components DMA Concepts |                                                                 |    |

|   | 2.1   | Logica                                       | al DMA Channels & DMA Handles                                   |    |

|   |       |                                              | h vs. Persistent DMA Resources                                  |    |

|   | 2.3   | DMA F                                        | Resource Management using DMAN3                                 |    |

|   | 2.4   | DMA <sup>-</sup>                             | Fransfer Submission and Synchronization using ACPY3             | 8  |

|   |       | 2.4.1                                        | FIFO Ordering of DMA Transfers and Linked DMA Transfers         | 8  |

|   |       | 2.4.2                                        | Channel Privacy and Synchronization                             |    |

|   |       |                                              | DMA Transfer Configuration Settings                             |    |

| 3 | IDM   |                                              | andard Interface for Negotiating DMA Resources                  |    |

|   | 3.1   | IDMA3                                        | 3 versus IDMA2                                                  | 1  |

|   | 3.2   | IDMA3                                        | 3 Interface Definition                                          | 12 |

|   |       | 3.2.1                                        | DMA Channel Descriptor: IDMA3_ChannelRec                        | 13 |

|   |       | 3.2.2                                        | IDMA3 Functions: IDMA3_Fxns                                     |    |

|   |       | 3.2.3                                        | IDMA3 Object and Handle Structures: IDMA3_Obj                   | 15 |

|   |       | 3.2.4                                        | IDMA3 Protocol Object for Channel Environment Memory Management | 18 |

|   |       | 3.2.5                                        | IDMA3 Enumeration Type Documentation                            | 19 |

| 4 | DM/   | AN3: 'C                                      | C64x+ DMA Resource Manager                                      | 20 |

|   |       |                                              | DMAN3 for Algorithm Integration                                 |    |

|   | 4.2   | DMAN                                         | I3 Configuration                                                | 2  |

|   |       | 4.2.1                                        | Introduction to Configuration Options                           | 2  |

|   |       | 4.2.2                                        | Configuration Parameters                                        |    |

|   |       | 4.2.3                                        | DMAN3 Configuration Examples                                    |    |

|   |       | 4.2.4                                        | Configuring DMAN3 Without Using RTSC                            |    |

|   |       | 4.2.5                                        | Configuring DMAN3 Using RTSC Tooling                            |    |

|   | 4.3   | DMAN                                         | l3 Functions                                                    |    |

|   |       | 4.3.1                                        | DMAN3_grantDmaChannels                                          |    |

|   |       | 4.3.2                                        | DMAN3_exit                                                      |    |

|   |       | 4.3.3                                        | DMAN3_init                                                      |    |

|   |       | 4.3.4                                        | DMAN3_releaseDmaChannels                                        |    |

|   |       | 4.3.5                                        | DMAN3_createChannels                                            |    |

|   |       | 4.3.6                                        | DMAN3 freeChannels                                              | 33 |

| 5    |       |          | nctional DMA Abstraction Layer                                 |    |

|------|-------|----------|----------------------------------------------------------------|----|

|      |       |          | 3 Functions and Comparison to ACPY2                            |    |

|      | 5.2   |          | 3 Interface                                                    |    |

|      |       |          | Logical Channel Configuration Parameters                       |    |

|      |       | 5.2.2    | ACPY3_configure                                                | 36 |

|      |       | 5.2.3    | ACPY3_fastConfigure16b                                         | 37 |

|      |       | 5.2.4    | ACPY3_fastConfigure32b                                         | 38 |

|      |       | 5.2.5    | ACPY3_start                                                    | 39 |

|      |       | 5.2.6    | ACPY3_wait                                                     | 39 |

|      |       | 5.2.7    | ACPY3_waitLinked                                               | 40 |

|      |       |          | ACPY3_complete                                                 |    |

|      |       | 5.2.9    | ACPY3_completeLinked                                           | 41 |

|      |       | 5.2.10   | ACPY3_activate                                                 | 41 |

|      |       | 5.2.11   | ACPY3_deactivate                                               | 42 |

|      |       | 5.2.12   | ACPY3_init                                                     | 42 |

|      |       | 5.2.13   | ACPY3_exit                                                     | 42 |

|      |       | 5.2.14   | ACPY3_setFinal                                                 | 43 |

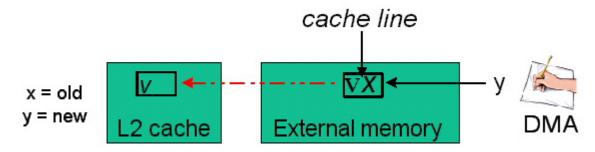

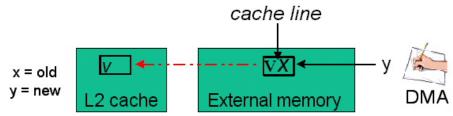

| 6    | Cac   | he Coh   | erency Issues for Algorithm Consumers                          | 44 |

| 7    | For   | Algorit  | hm Producers: Creating Algorithms that Use DMA                 | 45 |

|      | 7.1   | IDMA3    | and ACPY3 Related Changes that affect the Algorithm Developers | 46 |

|      | 7.2   | Rules a  | and Guidelines Summary                                         | 46 |

|      | 7.3   | Implem   | nenting the IDMA3 Interface                                    | 47 |

|      | 7.4   | Configu  | uring Logical Channels and DMA Transfers                       | 49 |

|      |       |          | Performance Considerations                                     |    |

|      | 7.5   | Schedu   | uling Asynchronous DMA Transfers on Logical Channels           | 50 |

|      |       |          | Alignment Issues Using ACPY3_start                             |    |

|      | 7.6   | Synchr   | onizing and Serializing DMA Transfers                          | 51 |

|      | 7.7   | Cache    | Coherency Issues for Algorithm Producers                       | 51 |

| 8    |       |          | opy (FCPY) Algorithm Example                                   |    |

|      |       |          | _Interface Functions                                           |    |

|      |       |          | Instance Heap Memory Requirements                              |    |

|      |       |          | The Use of IDMA3 and ACPY3 Interfaces                          |    |

| 9    | The   |          | oytest Example                                                 |    |

| 10   |       |          |                                                                |    |

| App  |       |          | de for the fastcopytest Example                                |    |

| App  | endi  | x B: Co  | de for FCPY_TI Algorithm                                       | 65 |

| • •  |       |          |                                                                |    |

|      | fcpy  | _ti.h    |                                                                | 66 |

|      | fcpy  | ti priv. | h                                                              | 67 |

|      |       |          | C                                                              |    |

|      | fcpy  | ti idma  | a3.c                                                           | 71 |

|      |       |          | avt.c                                                          |    |

|      |       |          | /.C                                                            |    |

|      |       | ,        | c                                                              |    |

|      |       |          | Figures                                                        |    |

| Figu | ire 1 | . Clie   | ent Application and Algorithm Interaction with DMA Resources   | 4  |

| _    | ıre 2 |          | A Transfer Block                                               |    |

|      | ıra 3 |          | IA3 Function Calling Sequence                                  | 12 |

| Figure 4.  | Algorithm Implementing IALG and IDMA3 Interfaces and Application Using |    |  |  |

|------------|------------------------------------------------------------------------|----|--|--|

| · ·        | Framework Components                                                   | 13 |  |  |

| Figure 5.  | IDMA3 Logical Channels                                                 |    |  |  |

| Figure 6.  | DMA Read Access Coherency Problem                                      |    |  |  |

| Figure 7.  | DMA Write Access Coherency Problem                                     |    |  |  |

| Figure 8.  | Cache Line Boundaries and the L2 Cache                                 |    |  |  |

| Figure 9.  | Cache Line Boundaries and the L2 Cache                                 | 51 |  |  |

| Figure 10. | Illustration of FCPY doCopy operation                                  | 52 |  |  |

| Figure 11. |                                                                        |    |  |  |

|            |                                                                        |    |  |  |

|            | Tables                                                                 |    |  |  |

| Table 1.   | IDMA3 Functions                                                        | 4  |  |  |

| Table 2.   | IDMA3 Channel Request Descriptor (IDMA3_ChannelRec)                    | 5  |  |  |

| Table 3.   | IDMA3 Channel (IDMA3_Obj)                                              |    |  |  |

| Table 4.   | IDMA3 Protocol Object (IDMA3_ProtocolObj)                              | 5  |  |  |

| Table 5.   | DMAN3 Functions                                                        | 6  |  |  |

| Table 6.   | ACPY3 Functions                                                        | 6  |  |  |

| Table 7.   | ACPY3 Params Structure Fields                                          | 6  |  |  |

#### 1 Introduction

The direct memory access (DMA) controller performs asynchronously scheduled data transfers between memory regions without the intervention of the CPU. The parallel operation of the DMA with the execution of the CPU relieves the CPU of the burden of these data transfers. This allows a system to achieve greater throughput.

Algorithms and client applications may want to take advantage of the DMA to overlap data movement with CPU processing. However, the TMS320 DSP Algorithm Standard (also known as xDAIS) does not allow compliant algorithms to directly access or control any hardware peripherals, including the DMA. All system DMA resources must be controlled by the client application.

The new Framework Components DMA utilities allow xDAIS algorithms and client applications to utilize DMA resources by providing standard DMA software abstractions and interfaces. Framework Components now includes the following DMA modules and interfaces:

- IDMA3. This is the standard interface to algorithms for DMA resource specification and negotiation protocols. This interface allows the client application to guery and provide the algorithm its requested DMA resources.

- **DMAN3.** This is the DMA resource manager. It is responsible for managing and granting DMA resources to algorithms and applications based on the IDMA3 interface.

- ACPY3. This is the functional DMA interface and library. The ACPY3 interface describes a comprehensive list of DMA operations that an algorithm can perform on the logical DMA channels acquired through the IDMA3 protocol. These functions are implemented as part of the client application and are called by the algorithm.

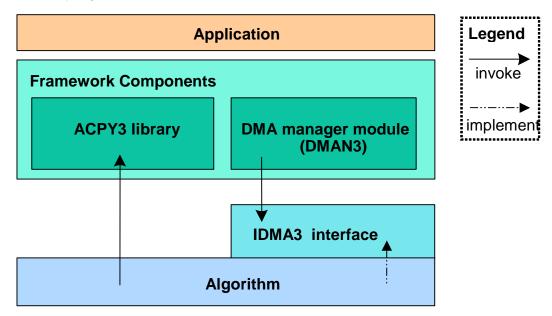

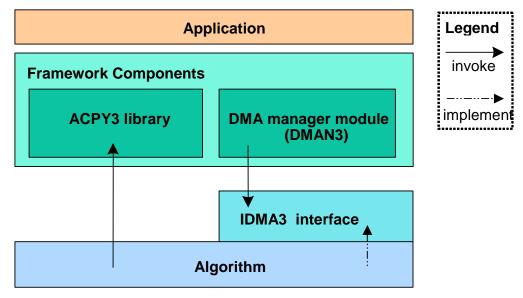

Figure 1 shows which modules are implemented by client application frameworks and which are implemented by algorithms or components. Arrows indicate which modules use other modules.

Figure 1. Client Application and Algorithm Interaction with DMA Resources

Client applications use the algorithm's IDMA3 interface to query the algorithm's DMA resource requirements and grant the algorithm logical DMA resources via handles. Each granted handle provides the algorithm a uniform, private logical DMA channel abstraction. Algorithms, upon getting provisioned by the framework with their DMA resource needs, may call ACPY3 functions to schedule DMA transfers on the logical DMA channels. Alternatively, algorithms may provide their own DMA functions to program the physical DMA resources acquired through the IDMA3 protocol.

The basic ideas and objectives described in the "Use of the DMA Resource" chapter of *TMS320 DSP Algorithm Standard Rules and Guidelines* (SPRU352) apply to the design, implementation and use of the ACPY3 and IDMA3 interfaces. Collectively, IDMA3, DMAN3, and ACPY3 provide a flexible and efficient model that greatly simplifies the management of system DMA resources and services by the client application. They also provide a simple and powerful mechanism for algorithms to configure and access DMA services.

The following tables summarize the API functions and structures used by the IDMA3, ACPY3, and DMAN3 interfaces.

| Functions           | Description                                                                                                                                   |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| dmaChangeChannels() | Called by an application whenever logical channels are moved at run-time.                                                                     |  |

| dmaGetChannelCnt()  | Called by an application to query an algorithm about its number of logical DMA channel requests.                                              |  |

| dmaGetChannels()    | Called by an application to query an algorithm about its DMA channel requests at initialization time, or to get the current channel holdings. |  |

| dmaInit()           | Called by an application to grant DMA handle(s) to the algorithm at initialization.                                                           |  |

Table 1. IDMA3 Functions

#### Table 2. IDMA3 Channel Request Descriptor (IDMA3\_ChannelRec)

| Structure Fields | Description                                                                                                                                                                      |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Handle           | Handle to logical DMA channel                                                                                                                                                    |  |

| numTransfers     | Number of DMA transfers that are submitted using this logical channel handle.                                                                                                    |  |

|                  | Single (==1) or Linked ( >= 2)                                                                                                                                                   |  |

| numWaits         | Number of individual transfers that can be waited in a linked start.                                                                                                             |  |

|                  | (1 for single transfers or to wait for all transfers to complete)                                                                                                                |  |

| priority         | Relative priority recommendation {Urgent, High, Medium, Low}                                                                                                                     |  |

| protocol         | Optional protocol handle for allocating channel environment ("env") memory and calling custom channel initialization function.                                                   |  |

| persistent       | When persistent is set to TRUE, the granted physical EDMA resources (PaRAMs and TCCs) are for exclusive use by this channel. They cannot be shared with any other IDMA3 channel. |  |

#### IDMA3 Channel (IDMA3\_Obj) Table 3.

| Structure Fields | Description                                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| numTccs          | The number of TCCs allocated to this channel.                                                                                                                                                                        |

| numPaRams        | The number of PaRAM entries allocated to this channel.                                                                                                                                                               |

| tccTable         | Array of TCCs assigned to this channel                                                                                                                                                                               |

| paRamAddr        | PaRAMs assigned to channel                                                                                                                                                                                           |

| qdmaChan         | Physical QDMA Channel assigned to handle                                                                                                                                                                             |

| transferPending  | Run-time channel state that must be maintained by channel owner.  Must be set to true when a new transfer is started on this channel.  Must be set to false when a wait/sync operation is performed on this channel. |

| env              | When the channel IDMA3_Protocol requires it, "env" points to the private channel memory allocated for the channel by the framework DMA resource manager.                                                             |

| protocol         | The IDMA3_Protocol handle used by the DMA manager to determine memory requirements for the "env".                                                                                                                    |

| persistent       | Indicates if the channel has been allocated with persistent property.                                                                                                                                                |

#### IDMA3 Protocol Object (IDMA3\_ProtocolObj) Table 4.

| Structure Fields | Description                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| name             | The name of the optional custom protocol that will be used by the algorithm requesting the IDMA3 channel resources.                                                      |

|                  | This object contains function pointers to be used when determining channel "env" memory requirements and for custom channel initialization and finalization.             |

| getEnvMemRec     | When not NULL, points to the function called by the DMA manager to query the IDMA3 protocol's memory requirements for the IDMA3 channel's environment ("env") pointer.   |

| initHandle       | When not NULL, points to the function to be called by DMA manager after allocation of the "env" memory to perform custom IDMA3 protocol initialization of channel state. |

| deInitHandle     | When not NULL, points to the function to be called by DMA manager when a channel is freed to perform any custom IDMA3 protocol de-initialization.                        |

# Table 5. DMAN3 Functions

| Functions                | Description                                                                                  |

|--------------------------|----------------------------------------------------------------------------------------------|

| DMAN3_grantDmaChannels   | Grant logical channel resources to one of more algorithm instances sharing a common groupId. |

| DMAN_exit ()             | Finalization method of the DMAN module.                                                      |

| DMAN3_init ()            | Initialize the DMAN3 module.                                                                 |

| DMAN3_releaseDmaChannels | Remove logical channel resources from one or more algorithm instances.                       |

| DMAN3_createChannels     | Allocate DMA resources and initialize memory for one or more logical DMA channels.           |

| DMAN3_freeChannels       | Free DMA resources and memory allocated to one or more logical DMA channel.                  |

# Table 6. ACPY3 Functions

| Functions              | Description                                                                                                                                       |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ACPY3_activate         | Activates given channel. Take over shared resources prior to use.                                                                                 |  |

| ACPY3_deactivate       | Deactivates given channel. Give back shared resources at the end of use.                                                                          |  |

| ACPY3_complete         | Check if the data transfers on a specific logical channel have completed                                                                          |  |

| ACPY3_completeLinked   | Check if an individual transfer on a specific logical channel have completed                                                                      |  |

| ACPY3_configure        | Configure a logical channel                                                                                                                       |  |

| ACPY3_exit             | Free resources used by the ACPY3 module [FRAMEWORK API]                                                                                           |  |

| ACPY3_setFinal         | Dynamically change the number of transfers in a sequence of linked transfers. Sets given transferNo as the last in a sequence of linked transfers |  |

| ACPY3_init             | Initialize the ACPY3 module [FRAMEWORK API]                                                                                                       |  |

| ACPY3_fastConfigure16b | Modify a single (16-bit) parameter of the logical DMA Channel                                                                                     |  |

| ACPY3_fastConfigure32b | Modify a single (32-bit) parameter of the logical DMA Channel                                                                                     |  |

| ACPY3_start            | Issue a request for a data transfer using current channel settings                                                                                |  |

| ACPY3_wait             | Wait for all data transfers to complete on a specific logical channel                                                                             |  |

| ACPY3_waitLinked       | Wait for an individual data transfer to complete on the logical channel                                                                           |  |

# Table 7. ACPY3\_Params Structure Fields

| Structure Fields | Description                                                                        |

|------------------|------------------------------------------------------------------------------------|

| transferType     | Transfer type: ACPY3_1D1D, ACPY3_1D2D, ACPY3_2D1D or ACPY3_2D2D                    |

| srcAddr          | Source Address of the DMA transfer                                                 |

| dstAddr          | Destination Address of the DMA transfer                                            |

| elementSize      | Number of consecutive bytes in each 1D transfer vector (ACNT)                      |

| numElements      | Number of 1D vectors in 2D transfers (BCNT)                                        |

| numFrames        | Number of 2D frames in 3D transfers (CCNT)                                         |

| srcElementIndex  | Offset in number of bytes from beginning of each 1D vector to the beginning of the |

|                  | next 1D vector. (SBIDX)                                                            |

| dstElementIndex  | Offset in number of bytes from beginning of each 1D vector to the beginning of the |

|                  | next 1D vector. (DBIDX)                                                            |

| srcFrameIndex    | Offset in number of bytes from beginning of the first 1D vector of source frame to |

|                  | the beginning of the first element in the next frame.                              |

|                  | (SCIDX): signed value between -32768 and 32767.                                    |

| dstFrameIndex    | Offset in number of bytes from beginning 1D vector of first element in destination |

|                  | frame to the beginning of the first element in next frame                          |

|                  | (DCIDX): signed value between -32768 and32767.                                     |

| waitId | For a linked transfer entry:                                                                                                                           | waitld |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|        | -1 : no individual wait on this transfer                                                                                                               |        |

|        | 0 <= waitId < numWaits : this transfer can be waited on or polled for completion.                                                                      |        |

|        | Ignored for single-transfers and for the last transfer in a sequence of linked transfers, which are always synchronized with waitId == (numWaits - 1). |        |

#### 2 **Fundamental Framework Components DMA Concepts**

The following subsections highlight the fundamental concepts and features supported by the Framework Components associated with DMA resources and services.

#### 2.1 **Logical DMA Channels & DMA Handles**

The logical DMA channel is the fundamental software abstraction for characterizing hardware DMA resources and services. Each logical DMA channel represents a private hardware DMA resource and a private state identified by and accessed through a DMA handle. Applications are in charge of the physical DMA resources and grant IDMA3 channel handles to algorithms that request them using the IDMA3 interface.

#### 2.2 Scratch vs. Persistent DMA Resources

The physical EDMA3 resources associated with each logical DMA channel can be can be requested as scratch or persistent, borrowing the concepts from xDAIS/IALG as it applies to memory. Application frameworks or resource managers such as DMAN3 can optimize resource allocation of scarce physical resources by arranging a group of algorithms to share the same physical resources when the channels have been requested as "scratch" (persistent=false).

When more than one processing thread shares a scratch resource (memory or IDMA3 channel), the application framework must ensure that at any given time only one of the processing threads is active. Upon activation, the processing thread may use the scratch resources without interference from other sharing threads. However they must assume that the state of the resource upon activation is undefined and perform necessary initialization. Additionally, at the point of deactivation, they must be completely finished with their use of the scratch resources (for example, by not leave any outstanding DMA transfers or unchecked transfer completion codes) and save any context information they may need for the next activation, as covered under xDAIS DMA Rule 1. For xDAIS-compliant algorithms, the activation and deactivation events correspond to the instance IALG::algActivate and IALG::algDeactivate calls.

#### 2.3 **DMA Resource Management using DMAN3**

The IDMA3 interface does not specify or mandate the use of a particular framework DMA Resource manager. However, the TI Framework Components package provides DMAN3 as a fully-supported and configurable DMA Resource manager in charge of managing the EDMA3.0 physical resources that the application framework has given exclusively to DMAN3.

In a typical Framework Component based application, DMAN3 grants each algorithm the DMA resources it requests via the IDMA3 interface. The algorithm subsequently may call ACPY3 functions to configure logical channel settings, to request DMA transfers, or to synchronize with on-going transfers.

DMAN3 can be configured using a runtime C interface or statically using XDC tooling. The configuration provides DMAN3 with the physical EDMA3 resources: PaRAMs, TCCs, QDMA channels. DMAN3 configuration dictates how it allocates and manages the memory supplied to each logical DMA channel. DMAN3 additionally supports sharing of physical EDMA3 resources among algorithms created with the same scratch groupld whenever it is possible. It is the responsibility of the application framework to ensure that algorithms created using the same DMAN3 scratch grouplds do not pre-empt each other. See Section 4.2.3, "DMAN3 Configuration Examples" for some common allocation scenarios and tips.

# 2.4 DMA Transfer Submission and Synchronization using ACPY3

Algorithms or applications can use the physical DMA resources obtained through the IDMA3 interface directly or using any custom DMA library. However, the TI Framework Components package provides a high performance library, ACPY3, which may be used to perform a rich set of DMA operations using the logical DMA channels acquired through the IDMA3 protocol.

The ACPY3 API introduces several DMA transfer-related abstractions highlighted in the following subsections.

# 2.4.1 FIFO Ordering of DMA Transfers and Linked DMA Transfers

Several outstanding DMA transfer requests may be submitted asynchronously to run concurrently on separate logical DMA channels. Only transfer requests started on the same logical channel are guaranteed to start and complete in a strictly first-in first-out (FIFO) ordering.

In order to start multiple DMA transfers simultaneously but in a strict FIFO order, the IDMA3 interface introduces the notion of logical channels with more than 1 configurable transfer. Each ACPY3\_start issued on a logical DMA channel, in effect, issues these as linked DMA transfers, similar to the mechanism provided by the EDMA3.0 hardware. In addition to the enforced FIFO ordering, the ACPY3 library submits linked transfers more efficiently, so their use is encouraged even if FIFO ordering is not strictly required.

ACPY3 additionally allows synchronizing with one or more intermediate transfers within a linked channel. The number of intermediate waits must be indicated in the "numWaits" field when requesting an IDMA3 channel that will be used to wait on intermediate transfers.

# 2.4.2 Channel Privacy and Synchronization

Algorithms have exclusive ownership of each received logical channel and can operate safely without fear of external components (such as other algorithms or other system code) accessing the channel and issuing transfer requests or changing channel configuration settings. They must, however, follow the ACPY3 API to activate and deactivate each IDMA3 channel during instance activation and deactivation, respectively.

All synchronization calls are issued on a per channel basis, as opposed to a per transfer basis. An algorithm can issue either a blocking wait, or a non-blocking query call to synchronize with a logical channel's completion status.

# 2.4.3 DMA Transfer Configuration Settings

The purpose of acquiring logical channel handles is to submit DMA transfer requests. Each submitted DMA transfer request specifies a source and destination memory region. A background DMA activity asynchronously carries out the copying of the contents of the source memory region to the destination.

The configuration setting of a logical channel is similar to the hardware register settings of the underlying EDMA3.0 hardware DMA device. However, each logical channel retains its configured DMA transfer settings. The most recently configured transfer settings at the time the ACPY3 start function is called apply to the asynchronously started DMA transfer.

Two properties of DMA transfers make them desirable and performance critical for algorithms:

- The physical transfer/copy operation takes place in the "background" under the close control of specialized circuitry and controllers. This allows algorithms to issue transfer requests in advance and to perform other useful operations while data is being copied in the background.

- The physical layout of source or destination DMA transfer blocks need not be a single

contiguous chunk of memory. By setting a few channel configuration parameters, algorithms

can specify complex layout patterns. This can lead to significant performance improvements

even if the algorithm cannot take advantage of asynchronous execution and the CPU sits

idle while waiting for the transfer to complete.

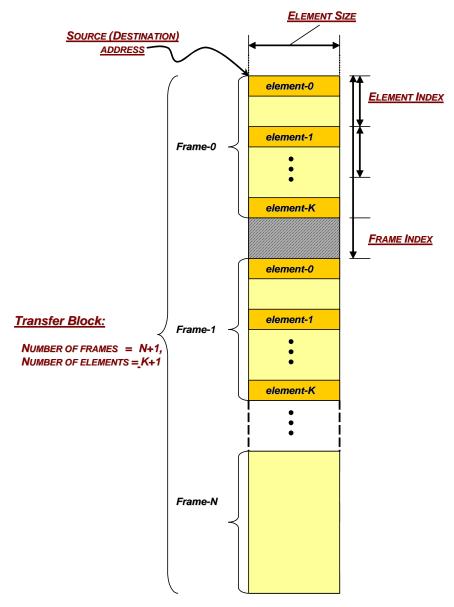

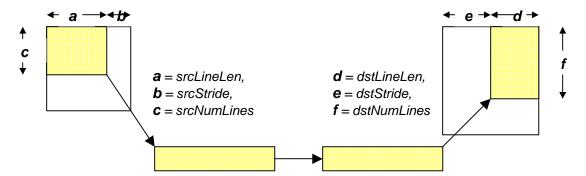

The unit of DMA transfer is a block composed of frames and elements. Each DMA transfer is submitted on a logical channel via the ACPY3\_start function. The *source* and *destination* addresses for the blocks and the *number of elements* in each frame are now part of the channel's configuration settings. The configuration parameters are intrinsic properties of each logical channel and are set exclusively when the algorithm calls ACPY3 configuration functions. The previously configured properties of each logical channel at the time of an ACPY3\_start request determine the actual memory copied from source to destination. Each DMA transfer is characterized by the following list configurable attributes. (Figure 2 illustrates the memory layout of a DMA transfer block characterized by these configuration parameters). Note that the element and frame index parameters can be configured independently for both source and destination.

- transferType. 1D-to-1D, 1D-to-2D, 2D-to-1D or 2D-to-2D

- **elementSize.** The number of 8-bit bytes per element. The element size for ACPY3 transfers can be a variable number, 1 ≤ number ≤ 65535, whereas the IDMA2/ACPY2 specification required this to be either 1,2, or 4.

- numFrames <sup>1</sup>. The number of frames in a block, 1 ≤ number ≤ 65535

- SrcElementIndex and DstElementIndex. The offset in 8-bit bytes between the start addresses of two consecutive elements in a frame. Element indexes must be specified only when the source or destination is a 2D transfer. They are ignored for 1D transfers. Element indexes can be signed (i.e. negative) values in the range: -32767 ≤ number ≤ 32768

Using DMA with Framework Components for 'C64x+ 9

<sup>&</sup>lt;sup>1</sup> The current implementation of ACPY3 does not support the use of numFrames or frame indexes due to QDMA-based hardware implementation restrictions. These may be supported in future releases using an EDMA-based implementation.

- SrcFrameIndex and DstFrameIndex <sup>1</sup>. The offset in 8-bit bytes between the start addresses of the first elements of two consecutive frames. (NOTE: This corresponds to the AB-synched SRC/DST CIDX settings in the EDMA3.0 DMA parameters.) Frame indexes must be specified only when the number of frames > 1, otherwise they are ignored. Frame indexes can be signed (negative or positive) values in the range: -32767 ≤ number ≤ 32768

- numElements. The number of elements per frame, 1 ≤ number ≤ 65535

- srcAddr and dstAddr. 8-bit byte-addresses

Figure 2. DMA Transfer Block

# **IDMA3: Standard Interface for Negotiating DMA Resources**

TMS320 DSP Algorithm Standard (xDAIS) compliant algorithms designed for the 'C64x+ EDMA3 controller must implement the IDMA3 interface to publish and acquire DMA resources they will use. The application framework DMA Resource Manager (DMAN3 is one reference implementation provided by the Framework Components) calls IDMA3 interface functions to query and subsequently allocate and grant the requested DMA resources. The IDMA3 interface is similar to the xDAIS IDMA2 interface in terms of its definition and role. IDMA3 introduces the notion of a logical DMA channels abstraction via a handle similar to that used in IDMA2.

#### 3.1 **IDMA3 versus IDMA2**

The following key changes have been introduced as compared to the IDMA2/ACPY2 interfaces:

- IDMA3 is no longer a pure hardware abstraction of generic DMA resources. Logical channels obtained through the IDMA3 interface expose some physical EDMA3 resources: Parameter RAM Sets (PaRAMs), Transfer Completion Codes (TCCs), and QDMA Channel ids.

- IDMA3 introduces the notion of scratch vs. persistent resources for the physical EDMA3 resources assigned to each IDMA3 channel. This approach is similar to the IALG scratch memory concept, which allows frameworks to efficiently share/overlay algorithm instance scratch buffers using instance activation and deactivation. This approach in IDMA3 allows sharing of TCCs and PaRAM entries and nicely hooks with IALG activate/deactivate events.

- Channels that cannot be used in a shared context must be requested with "Persistent=TRUE", otherwise the resource manager is free to arrange the sharing of granted physical DMA resources.

- Each IDMA3 channel can be optionally associated with a custom IDMA3 protocol. When a non-null "protocol" object is provided, the DMA resource manager uses IDMA3\_Protocol functions to perform additional memory allocation for the logical DMA channel's environment ("env") field or to call protocol-specific handle initialization and de-initialization functions. This feature allows frameworks to support custom DMA service function libraries (ACPY3 is just one such library) with custom initialization and finalization functions.

- Each logical DMA channel can be assigned a relative channel priority.

For performance reasons, support was added for the following EDMA3.0-centric DMA concepts:

- Hardware linked transfers that can be quickly started through QDMA.

- Waiting on an intermediate transfer's completion in the case of linked transfers.

Finally, based on existing algorithm use cases, the following changes were made to allow ACPY3 to have a more streamlined and high-performance design:

- The queue IDs defined in IDMA2 are no longer needed. This means there is no requirement to enforce inter-channel FIFO ordering of submitted DMA transfers. When FIFO ordering is needed, you must use linked transfers.

- FIFO completion of DMA transfers is supported only on individual logical DMA channels and linked transfers.

- Support has been added for intermediate synchronization points associated with "wait-ids" for individual transfers within a linked transfer chain.

#### 3.2 IDMA3 Interface Definition

The IDMA3 interface is implemented by algorithms that need EDMA3 resources. The application framework DMA Resource Manager calls the algorithm's IDMA3 interface functions to query and subsequently allocate and grant the requested DMA resources. (DMAN3 is a reference implementation of a DMA Resource Manager provided by the Framework Components.) If required, the framework calls IDMA3 channel-specific IDMA3\_Protocol functions to allocate, initialize, and free additional channel environment memory, which is part of the logical DMA channel state.

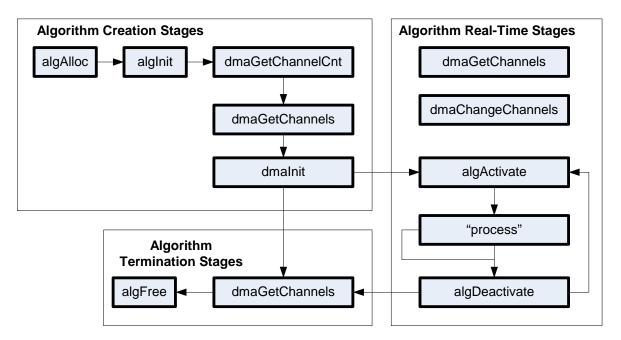

The algorithm implements the IDMA3 interface by defining and initializing a global structure of type IDMA3\_Fxns. Every function defined in this structure must be implemented and assigned to the appropriate field in this structure. Figure 3 illustrates the calling sequence for IDMA3 functions and how these functions relate to the IALG functions performed during algorithm instance creation and real-time operation.

Figure 3. IDMA3 Function Calling Sequence

The dmaChangeChannels() and dmaGetChannels() functions can be called at any time in the algorithm's real-time stages. The algMoved() and algNumAlloc() functions were omitted from this figure for simplicity.

The dmaGetChannels() and dmaInit() functions must be called after algInit() and before algActivate(). The dmaGetChannelCnt() function can be called before the algorithm instance object is created if the framework wants to query the algorithm about its DMA resource requirements before creating the instance object.

**Note:** Framework Components provides a DMA resource manager, DMAN3, which provides functions to perform the IDMA3 operations to create algorithms that implement the IDMA3 interface. This is discussed in Section 4.

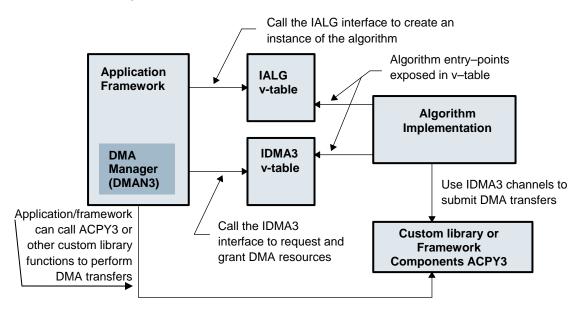

Figure 4 illustrates a typical system with an algorithm implementing the IALG and IDMA3 interfaces and the application with a DMA manager. Notice that the algorithm calls the ACPY3 run-time functions, which are implemented by the Framework Components. The ACPY3 interface provides a comprehensive list of DMA functions that an algorithm can call using the IDMA3 handles to program the logical DMA channels obtained through the IDMA3 interface. These functions allow the algorithm to:

- Configure each logical channel's DMA transfer settings

- Submit asynchronous DMA transfer requests

- Synchronize with the completion status of submitted transfers (both blocking and nonblockina).

Figure 4. Algorithm Implementing IALG and IDMA3 Interfaces and Application Using **Framework Components**

# 3.2.1 DMA Channel Descriptor: IDMA3 ChannelRec

The IDMA3 interface functions use the IDMA3 ChannelRec structure definition to characterize the properties of each logical DMA channel to be granted to the requesting algorithm or module. The DMA Manager utilizes the information passed in a channel descriptor and responds by constructing a logical IDMA3 channel containing the physical DMA resources that are assigned to the channel, and passes the handle of the DMA channel using the same channel descriptor.

This structure has the following data fields:

| IDMA3_Handle         | handle       |

|----------------------|--------------|

| Int                  | numTransfers |

| Int                  | numWaits     |

| IDMA3_Priority       | priority     |

| IDMA3_ProtocolHandle | protocol     |

| Bool                 | persistent   |

The following list describes these fields:

#### • IDMA3 Handle IDMA3 ChannelRec::handle

The handle to a logical DMA channel.

# • Int IDMA3\_ChannelRec::numTransfers

The maximum number of linked DMA transfers that will be submitted using this logical channel handle. Single (==1) or Linked (>= 2).

#### • Int IDMA3 ChannelRec::numWaits

The maximum number of transfers that can be independently waited upon. This includes intermediate transfers of a linked DMA transfer. A wait, with a waitld of (numWaits – 1) is configured to indicate the end of the linked or single transfer on a particular channel. Hence, while requesting a handle with a configured number of numWaits, always count the default wait required to indicate the end of transfer. For example, if only 1 intermediate transfer is to be tracked, IDMA3\_ChannelRec::numWaits should be 2. Use a waitld of 0 to track the intermediate transfer and a waitld of 1 (numWaits – 1) to track the end of the entire transfer.

### • IDMA3 Priority IDMA3 ChannelRec::priority

The relative priority recommendation for transfers submitted on this channel: High, Medium, or Low. See Section 3.2.5 for constants to use for priorities.

## IDMA3\_ProtocolHandle IDMA3\_ChannelRec::protocol

When non-null, the protocol object provides an interface for querying and initializing logical DMA channel for use by the given protocol. The protocol can be IDMA3\_PROTOCOL\_NULL; in this case no "env" is allocated. For example, when requesting a logical channel to be used with ACPY3 functions, the protocol needs to be set to &ACPY3\_PROTOCOL.

# • Bool IDMA3\_ChannelRec::persistent

When persistent is set to TRUE, the PaRAMs and TCCs are allocated exclusively for this channel. They cannot be shared with any other IDMA3 channel.

# 3.2.2 IDMA3 Functions: IDMA3\_Fxns

The application framework calls the following functions to query and grant DMA resources requested by the algorithm at initialization time, and to make changes to these resources at runtime. These IDMA3 functions must be implemented by all algorithms that need to access physical DMA resources of the EDMA3 controller.

Void \*implementationId Void (\*dmaChangeChannels )(IALG\_Handle, IDMA3\_ChannelRec \*) Uns (\*dmaGetChannelCnt )(Void) Uns (\*dmaGetChannels )(IALG Handle, IDMA3 ChannelRec \*) Int (\*dmalnit)(IALG\_Handle, IDMA3\_ChannelRec \*)

- **implementationId** This holds a unique value that identifies the module implementing this interface. This same value must be used in all interfaces implemented by the module. Since all compliant algorithms must implement the IALG interface, it is sufficient for these algorithms to set this field to the address of the module's declared IALG Fxns structure.

- dmaChangeChannels() The application framework's DMA resource manager calls this function whenever a logical channel is moved at run-time.

- dmaGetChannelCnt() The application framework's DMA resource manager calls this function to query an algorithm about the maximum number of logical DMA channels requested.

- dmaGetChannels() The application framework's DMA resource manager calls this function to query an algorithm about its DMA channel requests at initialization time, or to get the current channel holdings.

- dmalnit() The application framework's DMA resource manager calls this function to grant DMA handle(s) to the algorithm at initialization time. The algorithm uses this function to complete the initialization of its instance object.

# 3.2.3 IDMA3 Object and Handle Structures: IDMA3\_Obj

The IDMA3 channel object holds the private state associated with each logical DMA channel. The application framework DMA manager creates and initializes the logical channel provisioned with the physical EDMA3 resources that are exposed in this structure definition, and passes its handle to the requesting algorithm using the IDMA3 interface.

The holder of a handle to an IDMA3 channel may directly access the physical resources assigned to the channel or use a standard (ACPY3) or custom DMA functional library that recognizes IDMA3 channel handles.

When the channel is created with its persistent field set to "false", the physical DMA resources assigned to the channel are be considered to be "scratch" memory, as the definition applies to IALG memory attributes. Algorithms must perform initialization of the resource state each time they are put in an "active" state (via an algActivate call) and must save any necessary channel context when they are deactivated (via algDeactivate). When using ACPY3, calling ACPY3\_activate and ACPY3\_deactivate during instance activation and deactivation, respectively, performs this required context initialization and deinitialization.

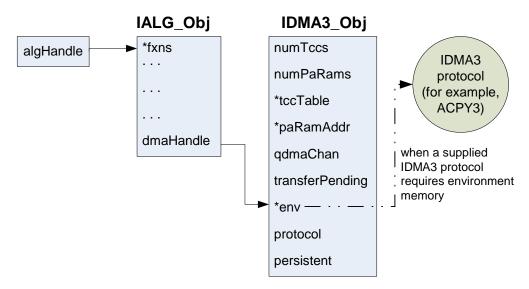

Figure 5 shows how the algHandle points to an IALG\_Obj object, which in turn points to an IDMA3 Obj object.

Figure 5. IDMA3 Logical Channels

The IDMA3\_Handle data type is a pointer to the IDMA\_Obj structure. The IDMA3\_Obj structure has the following data fields:

| MdUns                | numTccs         |

|----------------------|-----------------|

| MdUns                | numPaRams       |

| SmUns *              | tccTable        |

| Uns *                | paRamAddr       |

| MdUns                | qdmaChan        |

| Bool                 | transferPending |

| Void *               | env             |

| IDMA3_ProtocolHandle | protocol        |

| Bool                 | persistent      |

The following list describes these fields:

## MdUns IDMA3 Obj::numTccs

The number of TCCs allocated to this channel.

## MdUns IDMA3 Obj::numPaRams

The number of contiguous EDMA3 Parameter RAM (PaRAM Set) register sets allocated to this channel.

### SmUns\* IDMA3\_Obj::tccTable

The address of the array containing TCCs assigned to this channel.

## Uns\* IDMA3 Obj::paRamAddr

The physical address of the first PaRAM assigned to this channel.

## MdUns IDMA3 Obj::gdmaChan

The index of the physical QDMA channel assigned to the handle.

## Bool IDMA3\_Obj::transferPending

The channel state. This must be maintained by the channel handle owner. The transferPending state must be set to true each time a new DMA transfer is physically submitted using this DMA channel. The state must be cleared to false before a new physical transfer can be submitted using this channel.

#### Void\* IDMA3 Obj::env

An optional "environment" memory that may be allocated as a private extension of the channel state. Memory for the "env" must be supplied by the framework prior to calling the IDMA3\_Fxns::dmaInit function only if the IDMA3 channel descriptor requires it by providing a non-null "protocol" handle and a non-null getEnvMemRec() function pointer.

The IDMA3 Protocol object's getEnvMemRec() function characterizes the size, alignment and space attributes of the "env" memory needed for the channel. The framework is responsible for allocating and reclaiming the "env" memory.

During channel creation, the "env" pointer must always be created as private and persistent memory assigned to the IDMA3 channel object. However, the framework/resource manager is also allowed to allocate the requested internal "env" memory as "scratch" memory that can only be used when the channel is in an active state.

In the scratch allocation case, the framework/resource manager must still allocate the "env" as a "persistent" shadow memory, possibly in "external memory", and then pass the address of the scratch "internal" "env" memory in the first word of the returned IDMA3 Obj's "env" pointer. If a channel's "env" memory is created as "persistent" with no "scratch" shadow, then the first word of the env memory must be set to null.

# IDMA3\_ProtocolHandle IDMA3\_Obj::protocol

When non-null, this points to the channel protocol function table used by the DMA manager to interrogate and provision memory for the channel's "env" area.

Bool IDMA3\_Obj::persistent

This flag indicates whether the channel was allocated with the persistent property.

# 3.2.4 IDMA3 Protocol Object for Channel Environment Memory Management

The IDMA3 protocol object (the "protocol" field of the channel descriptor) is used only when the requestor of the IDMA3 channel requires:

- additional environment memory (assigned to the channel's "env" pointer) to be allocated by the framework as part of the channel object, or

- custom initialization or de-initialization functions to be called by the framework upon channel creation and deletion.

If these requirements do not apply, you may request the IDMA3 channel with a null "protocol" field and skip the details of this section.

Algorithms or framework libraries (such as ACPY3) may need some additional persistent and private "environment" memory to be associated with each IDMA3 channel in order to manage channel state or to create shadow copies of registers, data structures, etc. The IDMA3 interface defines a protocol, via the IDMA3\_ProtocolObj specification, that can be implemented and used by individual algorithms or functional DMA libraries to request and receive channel environment memory from the resource management framework during channel creation.

Custom DMA libraries may take advantage of this feature and require that IDMA3 channels are requested and created using specific IDMA3 Protocol Objects. An example of this is the ACPY3 library, which supplies its own protocol object, ACPY3\_PROTOCOL. Algorithms or applications that will use ACPY3 to submit DMA transfers are simply required to set the "protocol" field to the address of ACPY3\_PROTOCOL when they request an IDMA3 channel for ACPY3 use.

When the IDMA3 channel descriptor (IDMA3\_ChannelRec) contains a non-null IDMA3\_ProtocolObj reference, the provided functions are called to determine channel environment memory requirements and to perform initialization and de-initialization of the channel object. If the IDMA3 protocol does not require the functionality associated with any particular function, it may be set to null. The application framework and DMA resource manager are responsible for calling the IDMA3\_Protocol functions.

The IDMA3 ProtocolObj contains the following fields:

#### String name

Void (\*getEnvMemRec )(IDMA3\_ChannelRec \*, IDMA3\_MemRec \*)

Bool (\*initHandle )(IDMA3\_Handle)

Bool (\*deInitHandle )(IDMA3\_Handle)

The following list describes these fields:

# String IDMA3 ProtocolObj::name

The name of the protocol.

# Void(\*IDMA3 ProtocolObj::getEnvMemRec)(IDMA3 ChannelRec \*, IDMA3 MemRec \*)

The function is called by the application framework/DMA manager to obtain the IDMA3 protocol's memory requirements (IDMA3\_MemRec) for its environment for the given IDMA3 channel descriptor. This is usually done when creating a logical DMA channel.

# Bool(\* IDMA3\_ProtocolObj::initHandle)(IDMA3\_Handle)

This function is called after allocation. It allows the IDMA3 protocol to do any initialization of its environment. It initializes the "env" memory passed in the IDMA3 channel handle and any other channel state. Returns TRUE on success. FALSE otherwise. If FALSE is returned channel creation fails.

If the framework/resource manager allocates the requested internal "env" memory as "scratch", the "env" pointer passed in the IDMA3\_Handle points to a persistent and private shadow memory (possibly in "external memory"), which contains the address of the "scratch" allocated "internal" "env" memory in the first word of the "persistent" "env" pointer.

If the first word of the env memory is NULL, then no separate "scratch" memory has been allocated and the "env" memory itself is "persistent".

# Bool(\* IDMA3\_ProtocolObj::delnitHandle)(IDMA3\_Handle)

This function is called when a channel is freed. It deinitializes a channel before assigned resources and memory are freed by the DMA manager. It is called so that the IDMA3 protocol can do any required de-initialization or freeing any memory that may have been allocated in initHandle().

# 3.2.5 IDMA3 Enumeration Type Documentation

The following enumerated types are defined for use by the IDMA3 API:

### enum IDMA3\_MemType

| Constant       | Memory Type          |

|----------------|----------------------|

| IDMA3_INTERNAL | Internal data memory |

| IDMA3_EXTERNAL | External data memory |

#### enum IDMA3\_Priority

| Constant              | IDMA3 Priority Level |

|-----------------------|----------------------|

| IDMA3_PRIORITY_URGENT | Urgent               |

| IDMA3_PRIORITY_HIGH   | High                 |

| IDMA3_PRIORITY_MEDIUM | Medium               |

| IDMA3_PRIORITY_LOW    | Low                  |

# 4 DMAN3: 'C64x+ DMA Resource Manager

DMAN3 is the DMA Resource Manager responsible for granting and reclaiming physical DMA resources such as EDMA3.0 PaRAM Register sets and transfer completion codes (TCCs). DMAN3 creates logical DMA channels based on the IDMA3 interface specification and grants these to requesting algorithms or other software components.

The application framework configures DMAN3 during system start-up (prior to its first use) with a dedicated set of EDMA3.0 physical DMA resources: PaRAM Sets, TCCs, and QDMA channels. Algorithms receive DMA handles from DMAN3 and use them to call ACPY3 functions to configure logical channel settings, to request DMA transfers or to synchronize with on-going transfers.

DMAN3 functions are intended to provide application frameworks a convenient and easy-to-use layer to integrate algorithms that request DMA resources.

# 4.1 Using DMAN3 for Algorithm Integration

The following steps provide a generic and convenient set of instructions for using the DMAN3 module to instantiate algorithm instances that request DMA resources. The code examples are from the fastcopytest.c example provided with this application note.

1. Include the DMAN3 and ACPY3 modules in the application. You can use the DMAN3 module as provided or make changes to it as needed by your application.

```

#include <ti/sdo/fc/dman3/dman3.h>

#include <ti/sdo/fc/acpy3/acpy3.h>

```

2. Create an algorithm instance using the IALG interface and set values for fields in the algorithm-specific params structure, which is declared in i<mod>.h. Use the standard IALG interface to allocate and grant the memory buffers requested by the algorithm and initialize the instance object.

```

FCPY_Params fcpyParams;

FCPY_Handle alg;

IDMA3_Fxns *dmaFxns[NUMALGS];

IALG_Handle alg[NUMALGS];

...

FCPY_init();

fcpyParams = FCPY_PARAMS; /* use the default creation parameters */

if ((alg = FCPY_create(&FCPY_IALG, &fcpyParams)) == NULL) {

SYS_abort("Could not create algorithm instance");

}

```

3. Call the DMAN3 and ACPY3 module initialization functions.

```

/* Assign internal and external Heaps to DMAN3 module. */

DMAN3_PARAMS.heapInternal = L1DHEAP;

DMAN3_PARAMS.heapExternal = EXTERNALHEAP;

/* Initialize DMA manager & ACPY3 lib for xDAIS algs and grant DMA resources */

DMAN3_init();

ACPY3_init();

```

4. Define a scratch sharing context by associating a group-id to use for DMA resource allocation using DMAN3 module. All subsequent DMAN3 calls using the same group-id will share underlying physical DMA resources.

```

Int groupId = 1;

Int numAlgs = 1;

```

5. Use the DMAN3 module to grant the DMA resources requested by the algorithm.

```

= (IALG_Handle)fcpyAlg;

alg[0]

dmaFxns[0] = &FCPY_IDMA3;

if (DMAN3_grantDmaChannels(groupId, alg, dmaFxns, numAlgs) != DMAN3_SOK) {

SYS_abort("Problem adding algorithm's dma resources");

```

#### 4.2 **DMAN3 Configuration**

The DMAN3 module manages physical and logical DMA resources for DSP algorithms and drivers. Allocation of following physical EDMA/QDMA resources is needed to ensure interoperability:

- TCCs (Transfer Completion Codes)

- PaRAM entries (Parameter RAM)

- QDMA channels

The DMAN3 functions manage system EDMA/QDMA resources that are pre-allocated to it by initializing the global DMAN3 configuration parameter DMAN3\_PARAMS during the initial system configuration. The DMAN3 init() function uses the initial system DMAN3 configuration settings and assumes that it exclusively owns and manages these resources. For example, the system integrator could identify and allocate 48 PaRAM entries to DMAN3. The rest could be distributed between the drivers, power managers on the chip, and possibly other frameworks that have access to the shared DMA resource.

# 4.2.1 Introduction to Configuration Options

The following section describes the configuration parameters of the DMA Manager module, DMAN3. Each configuration option can be set at design time by the system integrator to ensure optimal sharing of DMA resources for the execution environment.

There are two ways to configure DMAN3 parameters.

- You can use a low-level C language based approach to directly modify an interface-defined global configuration structure, DMAN3 PARAM, as defined in the DMAN3 API specification. The DMAN3 Params structure defines the configurable parameters of the DMAN3 module.

- Alternately, you can use XDC tooling to configure the RTSC module, DMAN3.

The XDC tooling approach results in the generation of the same low-level C based global configuration structures, so the type of configuration technology used does not matter to the underlying DMAN3 library implementation.

# 4.2.2 Configuration Parameters

The following is a list of the configurable DMAN3 parameters and a description of each.

Two names are given for each configuration parameter in this section. First, the DMAN3 parameters named in the DMAN3\_Params struct in the dman3.h header file are listed as DMAN3\_Params::<a tribute name>. The DMAN3 parameters are also configurable via the RTSC DMAN3 package interface; these names are specified in DMAN3.xdc and are listed in this section as DMAN3.<a tribute name>.

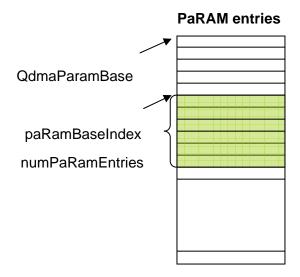

# Uns\* DMAN3\_Params::qdmaPaRamBase UInt DMAN3.qdmaPaRamBase

This identifies the physical base address of PARAM0 in the EDMA3/QDMA hardware whose resources are being managed by DMAN3. Set this to the actual base address of the PaRAM entries for the particular device on which DMAN3 is being configured.

# Uns DMAN3\_Params::maxPaRamEntries Ulnt DMAN3.maxPaRamEntries

The total number of PaRAM entries on the target hardware. Set this to the actual number of PaRAM entries available on the particular device on which DMAN3 is being configured.

# Uns DMAN3\_Params::paRamBaseIndex UInt DMAN3.paRamBaseIndex

(0>value>255) This represents the first PaRAM table entry number that is assigned by configuration for exclusive DMAN3 allocation. Contiguous PaRAM entries will be allocated exclusively for DMAN starting from this index.

# Uns DMAN3\_Params::numPaRamEntries Ulnt DMAN3.numPaRamEntries

The number of PaRAM table entries starting at DMAN3\_PARAM\_BASE\_INDEX assigned by configuration for exclusive DMAN3 allocation.

Uns DMAN3\_Params::maxQdmaChannels

UInt DMAN3.maxQdmaChannels

The total number of physical QDMA channels available on the target hardware. Set this to the actual number of QDMA channels that are available on the device for which DMAN3 is being configured.

# Uns DMAN3 Params::numQdmaChannels UInt DMAN3.numQdmaChannels

The number of physical QDMA channels that are assigned to DMAN3 via configuration. This number is assigned to DMAN3\_NUM\_QDMA\_CHANNELS.

# **Uns\* DMAN3\_Params::qdmaChannels** UInt DMAN3.gdmaChannels[DMAN3 NUM QDMA CHANNELS]

An array of size DMAN3 NUM QDMA CHANNELS that contains the channel numbers of the physical QDMA channels assigned to DMAN3 via configuration. DMAN3 exclusively owns these QDMA channels and assumes that they will not be used by any other resource. These channels need not be contiguous.

# Uns DMAN3 Params::tccAllocationMaskH UInt DMAN3.tccAllocationMaskH

A 32-bit bitmask representing a configuration-provided list of TCCs for exclusive DMAN3 allocation in the range 32-63. For example, for TCCs in the range 32-63 the High Mask (tccAllocationMaskH) is configured so that a "1" in bit position "i" indicates the TCC: (32 + i) is assigned to DMAN3.

## Uns DMAN3 Params::tccAllocationMaskL UInt DMAN3.tccAllocationMaskL

A 32-bit bitmask representing a configuration-provided list of TCCs for exclusive DMAN3 allocation in the range 0-31. For example, for TCCs in the range 0-31 the Low Mask (tccAllocationMaskL) is configured so that a "1" in bit position "i" indicates the TCC: "i" is assigned to DMAN3.

# SmUns DMAN3\_Params::numTccGroup[DMAN3\_MAXGROUPS] Int DMAN3.numTccGroup[DMAN3 MAXGROUPS]

An array containing the number of TCCs to be assigned to groups for sharing.

Algorithms in a particular scratch group (with the same group ID), share the same shared scratch pool. DMA channels requested by a given group use TCCs allocated for that group. The numTccGroup array indicates, for each group ID, the number of TCCs allocated to it.

Depending on the calls you make to create DMA channels in the same scratch group, you may or may not share the same TCCs.

# MdUns DMAN3\_Params::numPaRamGroup[DMAN3\_MAXGROUPS] Int DMAN3.numPaRamGroup[DMAN3\_MAXGROUPS]

Arrays containing the list of PaRAM entries that will be assigned to groups for sharing.

Algorithms in a particular scratch group (with the same group ID), share the same shared scratch pool. DMA channels requested by a given group use TCCs allocated for that group. The numPaRamGroup array indicates, for each group ID, the number of PaRAMs allocated to it.

Depending on the calls you make to create DMA channels in the same scratch group, you may or may not share the same PaRAMs

## Bool DMAN3\_Params::idma3Internal Bool DMAN3.idma3Internal

Use the internal memory heap to dynamically allocate IDMA3 objects. If this value is "false", IDMA3 objects are allocated in the heap specified by heapExternal. If the value of idma3Internal is "true", IDMA3 objects are allocated in the heap specified by heapInternal.

# Int DMAN3\_Params::heapInternal String DMAN3.heapInternal

The Memory Heap ID for dynamic allocation of DMAN3 objects that must be allocated in L1D Internal RAM. The internal heap could be used for allocation of memory for IDMA3 objects if indicated by the idma3Internal flag.

A value of -1 for heapInternal indicates that the heap is NOT DEFINED. If heapInternal is not defined, then any IDMA3 protocol call that requests IDMA3 objects to be created in the internal memory, will fail. When using RTSC module configuration you are required to provide a valid DSP/BIOS heap label.

# Int DMAN3\_Params::heapExternal String DMAN3.heapExternal

The Memory Heap ID for dynamic allocation of private DMAN3 data structures that can be allocated in external memory. The heapExternal memory space is used by DMAN3 to allocate memory for holding DMA channel descriptors that point to logical DMA channels. This space could also be used to hold IDMA3 objects if the flag idma3Internal is set to false.

A value of -1 indicates that the heap is NOT DEFINED. If heapExternal is not defined then DMAN3 attempts to use heapInternal. As a consequence, at least one of them must be defined. When using RTSC module configuration you are required to provide a valid DSP/BIOS heap label.

# DMAN3\_ScratchAllocFxn DMAN3\_Params::scratchAllocFxn String DMAN3.scratchAllocFxn

Algorithms, while requesting IDMA3 channels from DMAN3, might specify a particular IDMA3 protocol that provides custom DMA services. This protocol might require additional memory allocation for the channel's environment ("env" field). The scratchAllocFxn is a function call that when non-null is used to allocate the protocol's environment memory. If scratchAllocFxn is null, this additional memory is allocated in the internal heap specified by the heapInternal parameter.

If the scratchAllocFxn is provided, but fails to allocate the memory, DMAN3 attempts to allocate the memory dynamically using its heapInternal.

Note: The Framework Component DSKT2 provides a scratchAllocFxn implementation that can be used to allocate, when possible, the IDMA3 protocol handle's environment memory in the shared scratch area, provided that DSKT2 was also used to create the actual algorithm instance using the same scratch group ID.

# DMAN3\_ScratchFreeFxn DMAN3\_Params::scratchFreeFxn String DMAN3.scratchFreeFxn

The scratchFreeFxn is a function call that is used to free memory allocated using the scratchAllocFxn by DMAN3.

Note: The Framework Component DSKT2 provides a scratchFreeFxn implementation that must be called if memory has been allocated using DSKT2's scratchAllocFxn

# Uns DMAN3 Params::nullPaRamIndex **UInt DMAN3.nullPaRamIndex**

The index of the PaRAM entry to be reserved as a "NULL" PaRAM. Any QDMA channel that is inactive is mapped to the nullPaRamIndex entry by setting up the QCHMAP register accordingly. This PaRAM index must not be used by the application domain for scheduling EDMA3 transfers.

Note: This index is not counted against the numPaRAMEntries configuration setting.

# bool DMAN3.debug

A value of true for the debug parameter enables the debug profile of the DMAN3 library. This results in a larger and slower version of the library being linked in. It provides extra parameter checking and causes debug trace statements to be generated in the DSP/BIOS SYS trace buffer.

# 4.2.3 DMAN3 Configuration Examples

In the following subsections we discuss some common DMAN3 configuration scenarios.

# 4.2.3.1 Configuring DMAN3 for Optimal Sharing of Physical DMA Resources

DMAN3 attempts to maintain a separate sharable pool of physical EDMA3 resources such as PaRAMs and TCCs for each scratch group, identified by the groupId. The groupId argument passed to a DMAN3 function is used to determine the shared scratch resource pool to satisfy the allocation request. However, the shared resource pool for a particular groupId does not get created until the first DMAN3 allocation call using that groupId. The initial size of the shared scratch PaRAM or TCC pool is determined by the "greater" of:

- The size of the resource needed to satisfy the current allocation request.

- The DMAN3 configuration setting for DMAN3::numPaRamGroup[groupId] for the PaRAM pool.

- The DMAN3 configuration setting for DMAN3::numPaRamGroup[groupId] for the TCC pool.

Therefore it may be important to configure the DMAN3 numPaRamGroup and numPaRamGroup properties for optimal allocation to ensure that all allocation requests can be satisfied using the same shared resource pool for that groupId.

For example, if algorithm instances A and B, assigned to the same groupId, i, require 10 PaRAMs for A's channel requirements and 20 PaRAMs for B, then setting:

```

DMAN3::numPaRamGroup[i] = 20

```

ensures that, irrespective of the order in which the A and B instances are created, they can be assigned PaRAMs from the same shared PaRAM pool assigned to group:i.

For the same example, suppose you used a different DMAN3 setting such as:

```

DMAN3::numPaRamGroup[i] = 5

```

If A is created first and then B, then 10 PaRAMs are created for A, and the shared PaRAM pool has size=10 for group:i. This results in not being able to satisfy B's PaRAM allocation from group:i's shared pool. DMAN3 would still try to satisfy B's request by privately allocating 20 PaRAMs to B, in a non-sharable manner, if at the time of the call DMAN3 has enough PaRAMs available for non-shared allocation. If there are not enough such PaRAMs available, B's allocation returns failure, indicating not enough PaRAMs.

With the latter setting, if B is created first, the initial shared PaRAM pool allocation of 20 PaRAMs for group:i would be able to satisfy the subsequent allocation request for A from the shared pool. But, in this scenario, the optimal allocation imposes an order of creation constraint (B first, then A) for the application.

A similar argument applies when configuring the DMAN3 numTccGroup setting.

## 4.2.3.2 DMA Channel Memory Allocation

The DMAN3 configuration settings, .heapInternal and .heapExternal are used for allocation of IDMA3 channel objects and internal data structures. These heaps can be used to control memory allocation by DMAN3 in conjunction with the DMAN3 Config parameter .idma3Internal (the default is true).

A value of "false" means the IDMA3 objects are allocated in the heap specified by DMAN3\_PARAMS.heapExternal. If the value of .idma3Internal is "true", IDMA3 objects are allocated in the heap specified by DMAN3\_PARAMS.heapInternal.

## 4.2.3.3 IDMA3 Protocol Environment Memory Allocation

In addition to the memory allocated for the IDMA3 channel handle, if the IDMA3 channel is requested with an IDMA3 Protocol, such as ACPY3\_PROTOCOL, there may be additional memory allocation for the channel's environment memory (assigned to "env".) The IDMA3\_Protocol may additionally require the environment memory to be allocated in "internal" memory with some size and alignment constraints, as is the case for ACPY3. In this case, the following DMAN3 configuration settings become important:

```

.scratchAllocFxn (default = null)

.scratchFreeFxn (default = null)

```

When .scratchAllocFxn and .scratchFreeFxn are null, DMAN3 uses .heapInternal to dynamically allocate and free IDMA3 channel env memory. However when not-null, it calls these functions instead to allocate and free the "env" memory.

While there is no dependency between DMAN3 and DSKT2, it is possible to configure DMAN3 by plugging these functions with the specialized DSKT2 APIs DSKT2\_allocScratch() and DSKT2\_freeScratch() for the DMAN3 config params scratchAllocFxn and scratchFreeFxn respectively. Doing this causes the internal memory requests for the IDMA3\_Protocol requested channel "env" memory to be allocated from the DSKT2 managed scratch memory pool for the algorithm instance, when shared scratch DSKT2 memory is available.

# 4.2.4 Configuring DMAN3 Without Using RTSC

The non-RTSC way to configure the DMAN3 configuration parameters is quite straightforward. To modify the DMAN3 configuration parameters, include the *dman.h* header file in your C file, and override each of the parameters with the modified values. See the code snippet below as an example of how to modify the heapInternal and heapExternal parameters:

# 4.2.5 Configuring DMAN3 Using RTSC Tooling

In the program configuration file, define the DSP/BIOS heaps that will be assigned to DMAN3 heaps. For example, the following code snippet from the dman3/example/fastcopytest.tcf DSP/BIOS configuration file creates two DSP/BIOS heaps with appropriate attributes and heap labels: EXTERNALHEAP and L1DHEAP:

```

utils.loadPlatform("ti.platforms.evmDM6446");

DDR = prog.module("MEM").instance("DDR2");

* Create external memory segment for this (simulated) board

* Enable heaps in it and define the label for heap usage.

* /

= 0x83F00000;

DDR.base

DDR.len

= 0x0FFE00; // may be much bigger -- this is sim

DDR.space

DDR.space = "code/data"; // code/data so we can place code in it

DDR.createHeap = true;

DDR.enableHeapLabel = true;

DDR["heapLabel"] = prog.extern("EXTERNALHEAP");

DDR.heapSize

= 0x8000;

DDR.comment

= "DDR";

* Enable heaps in the L1DSRAM (internal L1 cache ram, fixed size)

and define the label for heap usage.

bios.L1DSRAM.createHeap

= true;

bios.L1DSRAM.enableHeapLabel = true;

bios.L1DSRAM["heapLabel"] = prog.extern("L1DHEAP");

bios.L1DSRAM.heapSize = 0x800;

```

The RTSC module configuration of the application uses and configures the DMAN3 module to make changes to the default DMAN3 configuration settings. For example, the following code snippet from dman3/examples/fastcopytest.cfg assigns the application-defined DSP/BIOS heap "L1DHEAP" to DMAN3.heapInternal, which is defined as the DSP/BIOS heap. It assigns "EXTERNALHEAP" to DMAN3.heapExternal. Then, it assigns the EDMA3 PaRAMs 78 through 125 and TCCs 32 through 63 to the DMAN3 module. It assigns 6 of the 8 available QDMA channels {0, 1, 4, 5, 6, and 7} to DMAN3.

It also sets 16 PaRAMs and 16 TCCs for scratch group 0 and sets 32 PaRAMs and 16 TCCs for scratch group 1.

```