# AN-2292 Designing an Isolated Buck (Fly-Buck) Converter

Vijay Choudhary

#### **ABSTRACT**

In many applications, one or more low-cost, simple to use, isolated power supplies working from input voltages up to 100 V are needed. Traditional solutions use flyback converters to generate this bias supply. Flyback designs typically utilize asymmetric transformers turns ratios for primary and secondary power windings, with an optocoupler and reference, or an auxiliary winding for feedback regulation. Additionally, flyback converters need an elaborate compensation design for stability. This results in a tedious design process, bulky solution, with a higher component count and cost.

An isolated buck converter (Fly-Buck) uses a synchronous buck converter with coupled inductor windings to create isolated outputs. Isolated converters utilizing Fly-Buck topology use a smaller transformer for an equivalent power transfer as the transformer primary and secondary turns ratios are better matched. There is no need for an optocoupler or auxiliary winding as the secondary output closely tracks the primary output voltage, resulting in smaller solution size and cost.

This article presents the basic operating principle of an isolated buck converter. The operating current and voltage waveforms are explained and design equations are derived. The design example shows a step-by-step procedure for designing a practical two-output 3 W isolated buck converter.

|   | Contents                                                                                                            |    |

|---|---------------------------------------------------------------------------------------------------------------------|----|

| 1 | Fly-Buck Converter                                                                                                  | 1  |

| 2 | Maximum Output Current Equations                                                                                    | 4  |

| 3 | Design Example                                                                                                      | 5  |

| 4 | Conclusions                                                                                                         |    |

| 5 | References                                                                                                          | 10 |

|   | List of Figures                                                                                                     |    |

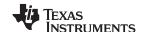

| 1 | Complete Schematic for an LM5017–Based Isolated Converter                                                           | 9  |

| 2 | Efficiency at 750 kHz, V <sub>OUT1</sub> = 10 V                                                                     | 9  |

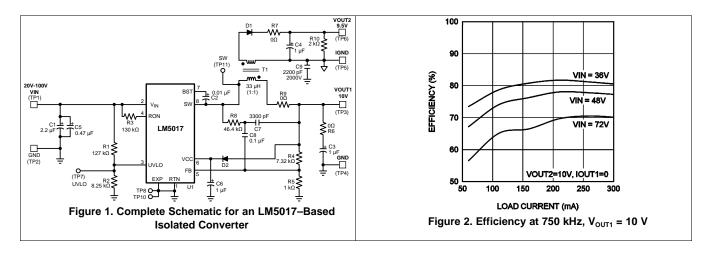

| 3 | Steady State Waveform (V <sub>IN</sub> = 48 V, I <sub>OUT1</sub> = 100 mA, I <sub>OUT2</sub> = 200 mA)              | 9  |

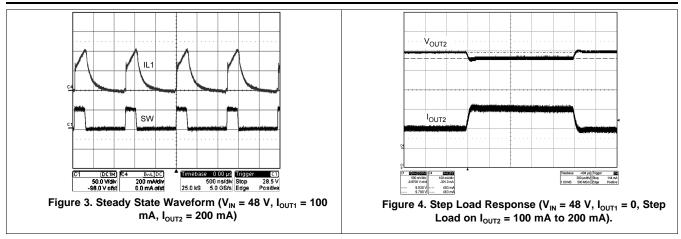

| 4 | Step Load Response ( $V_{IN} = 48 \text{ V}$ , $I_{OUT1} = 0$ , Step Load on $I_{OUT2} = 100 \text{ mA}$ to 200 mA) | 9  |

|   | List of Tables                                                                                                      |    |

| 1 | Isolated Buck Regulator Design Equations                                                                            | 5  |

| 2 | Component Calculation/Selection Steps for a Two-Output Isolated Buck                                                | 6  |

#### 1 Fly-Buck Converter

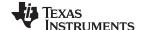

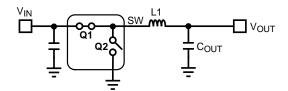

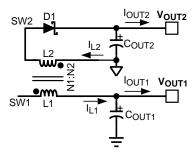

An isolated buck converter, also known as Fly-Buck converter, is created by replacing the output filter inductor (L1) in a synchronous buck converter with a coupled inductor (X1) or flyback-type transformer, and rectifying the secondary winding voltage using a diode (D1) and a capacitor ( $C_{OUT2}$ ). The topology can be extended to any number of isolated secondary outputs. It also can be used to generate one or more inverting outputs.

All trademarks are the property of their respective owners.

Fly-Buck Converter www.ti.com

## 1a) A Synchronous Buck Converter

1b) An Isolated Buck Converter (Fly-buck)

## Creating an Isolated Buck Converter by Modifying a Synchronous Buck Converter

The primary output voltage equation is identical to a buck converter and is given by Equation 1:

$$V_{OUT1} = \frac{T_{ON}}{T_{ON} + T_{OFF}} V_{IN} = D \times V_{IN}$$

(1)

and the secondary output voltage is given by Equation 2:

$$V_{OUT2} = \frac{N2}{N1} V_{OUT1} - V_F$$

(2)

where VF is the forward voltage drop of the secondary rectifier diode, and N1, N2 are the number of turns in the primary and secondary windings, respectively. The secondary output  $(V_{OUT2})$  closely tracks the primary output voltage  $(V_{OUT1})$  without the need for additional transformer winding or an optocoupler for feedback across the isolation boundary.

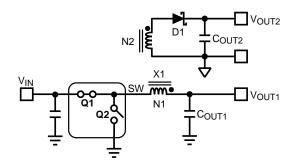

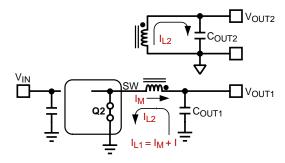

Isolated Buck Converter Switching Sub-Intervals shows the operating modes in an isolated configuration during TON, when the high-side buck switch is on; and TOFF, when the low-side switch is on. Current in the two windings is also shown. During TON, the current in the secondary winding is zero as the secondary diode is reverse biased by a voltage equal to

$$V_{IN} \times \frac{N2}{N1}$$

(3)

The current in the primary winding is the same as the magnetizing current (similar to a buck converter inductor).

www.ti.com Fly-Buck Converter

### Creating an Isolated Buck Converter by Modifying a Synchronous Buck Converter (continued)

2a) TON (Q1: ON, Q2: OFF)

2b) TOFF (Q1: OFF, Q2: ON)

#### **Isolated Buck Converter Switching Sub-Intervals**

During TOFF, the current in the secondary winding is decided by the resonant tank formed by  $C_{\text{OUT1}}$ , the leakage inductance of the coupled inductor, and  $C_{\text{OUT2}}$ . The current in the primary winding is the sum of the magnetizing current (similar to a buck converter inductor current), and the reflected current from the secondary winding. These operating waveforms are shown in Isolated Buck Operating Waveforms.

**Isolated Buck Operating Waveforms**

### **Isolated Buck Operating Waveforms (continued)**

## 2 Maximum Output Current Equations

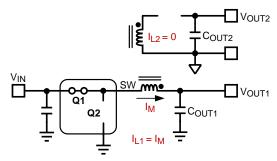

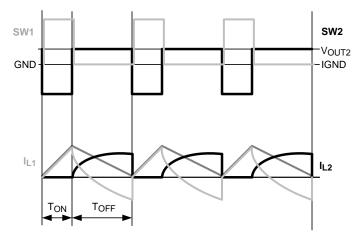

On a cycle-by-cycle average basis, the winding and output currents have the following relationship Isolated Buck Output Stage with Coupled Inductor.

$$I_{L1} = I_{OUT1} \tag{4}$$

and

$$I_{L2} = I_{OUT2} \tag{5}$$

#### **Isolated Buck Output Stage with Coupled Inductor**

The combined inductor current waveform  $(i_{L1} + i_{L2})$ , which is equal to the magnetizing current, is identical to a buck converter. The peak inductor and switch current during on-time is given by Equation 6:

$$i_{\text{sw(peak)}} = i_{\text{L1(peak)}} = I_{\text{L1}} + I_{\text{L2}} + \frac{\Delta I_{\text{L1}} + \Delta I_{\text{L2}}}{2} = I_{\text{OUT1}} + I_{\text{OUT2}} + \frac{\Delta I_{\text{L1}}}{2}$$

(6)

where we make use of the fact that during on-time (TON) there is no current in secondary winding. Therefore, the maximum total load current is given by Equation 7:

$$I_{OUT1} + I_{OUT2} = I_{LIM (MIN)} - \frac{\Delta I_{L1}}{2}$$

(7)

where the total load current is defined as the sum of the load currents at the two outputs. For turn-ratios (N2/N1) not equal to unity,  $I_{OUT2}$  should be multiplied by the turn-ratio in Equation 7, shown here in Equation 8:

$$I_{OUT1} + I_{OUT2} \frac{N2}{N1} = I_{LIM (MIN)} - \frac{\Delta I_{L1}}{2}$$

(8)

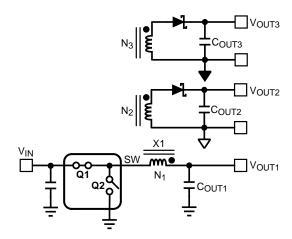

The maximum peak-to-peak current ripple in the primary winding is given by Isolated Buck Regulator with Three Outputs:

$$\Delta I_{L1} = \frac{\left(V_{\text{IN (MAX)}} - V_{\text{OUT}}\right)}{L1 \times f_{\text{SW}}} \frac{V_{\text{OUT}}}{V_{\text{IN (MAX)}}}$$

(9)

www.ti.com Design Example

### Isolated Buck Output Stage with Coupled Inductor (continued)

**Isolated Buck Regulator with Three Outputs**

Table 1 presents equations for non-equal turn-ratios and three windings (Isolated Buck Regulator with Three Outputs). The generalization to any number of windings is straightforward.

Table 1. Isolated Buck Regulator Design Equations

| Description                                 | Equations                                                                                                          |      |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|

| Output Voltages                             | $V_{OUT1} = \frac{T_{ON}}{T_{ON} + T_{OFF}} V_{IN} = D \times V_{IN}$                                              | (10) |

|                                             | $V_{OUT2} = \frac{N2}{N1} V_{OUT1} - V_F$                                                                          | (11) |

|                                             | $V_{OUT3} = \frac{N3}{N1} V_{OUT1} - V_F$                                                                          | (12) |

| Cycle-by-Cycle Average Quantities           | $I_{L1} = I_{OUT1}$                                                                                                | (13) |

|                                             | $I_{L2} = I_{OUT2}$                                                                                                | (14) |

|                                             | $I_{L3} = I_{OUT3}$                                                                                                | (15) |

| Peak Currents in HS FET and Primary Winding | $i_{sw(peak)} = i_{L1(peak)} = I_{OUT1} + \frac{N2}{N1}I_{OUT2} + \frac{N3}{N1}I_{OUT3} + \frac{\Delta I_{L1}}{2}$ | (16) |

| Primary Winding Peak-to-Peak Current Ripple | $\Delta I_{L1} = \frac{\left(V_{IN\;(MAX)} - V_{OUT}\right)}{L1 \; x \; f_{SW}} \frac{V_{OUT}}{V_{IN\;(MAX)}}$     |      |

|                                             | L1 x f <sub>SW</sub> V <sub>IN (MAX)</sub>                                                                         | (17) |

## 3 Design Example

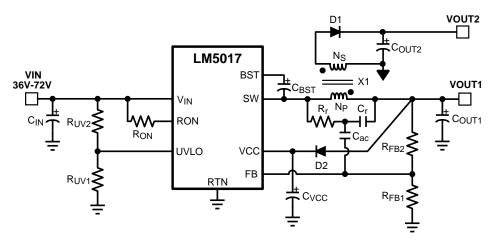

The design example illustrated in Two Output Isolated Buck Reference Schematic details the design procedure for a two-output isolated buck converter.

| Design Specifications                         |             |  |

|-----------------------------------------------|-------------|--|

| Input Voltage Range (V <sub>IN</sub> )        | 36 V - 72 V |  |

| Primary Output Voltage (V <sub>OUT1</sub> )   | 10 V        |  |

| Secondary Output Voltage (V <sub>OUT2</sub> ) | 10 V        |  |

| Primary Load Current (I <sub>OUT1</sub> )     | 100 mA      |  |

| Secondary Load Current (I <sub>OUT2</sub> )   | 200 mA      |  |

| Switching Frequency (fsw)                     | 750kHz      |  |

Design Example www.ti.com

Two Output Isolated Buck Reference Schematic

In this example, we start with a standard two-output circuit using TI's 100 V synchronous buck regulator, LM5017, and calculate the component values. We begin with buck converter component calculations and qualify some of the steps for the isolated configuration. The calculation steps are listed in Table 2.

Table 2. Component Calculation/Selection Steps for a Two-Output Isolated Buck

| Component Name                      | Calculation Steps                                                                                                                                                                                                                               | Selected Value/Rating |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| R <sub>FB1</sub> , R <sub>FB2</sub> | This parameter is selected by the user. Choose RFB1=1k $\Omega$                                                                                                                                                                                 | 1kΩ, 7.16kΩ           |

|                                     | $V_{OUT1} = 1.225 V \times \left(1 + \frac{R_{FB2}}{R_{FB1}}\right)$ (13)                                                                                                                                                                       | 3)                    |

|                                     | $\rightarrow$ R <sub>FB2</sub> = $\left(\frac{V_{OUT1}}{1.225} - 1\right)$ x R <sub>FB1</sub> = 7.16 kΩ (15)                                                                                                                                    | 9)                    |

| C <sub>vcc</sub>                    | Select a 1µF capacitor of 16 V or higher rating as recommended in the LM5017 datasheet.                                                                                                                                                         | e 1μF, 16 V           |

| C <sub>BST</sub>                    | Select a 0.01µF capacitor of 16 V or higher rating, as recommended in the datasheet.                                                                                                                                                            | n 0.01μF, 16 V        |

| C <sub>IN</sub>                     | Input capacitor should be large enough to limit the input voltage ripple                                                                                                                                                                        | 0.47μF + 2.2μF, 100 V |

|                                     | $C_{IN} \ge \frac{I_{OUT (MAX)}}{4 x f x \Delta V_{IN}}$                                                                                                                                                                                        |                       |

|                                     | (2)                                                                                                                                                                                                                                             | 0)                    |

|                                     | Choosing a $\Delta V_{IN}$ =0.5 V gives a minimum $C_{IN}$ =0.2 $\mu$ F A standard value of 0.47 $\mu$ F is selected. A larger bulk capacitor is usually needed to suppress inductive spikes in the input voltage. A 2.2 $\mu$ F bulk capacitor | is                    |

|                                     | selected in this case. Input capacitor should be rated for the maximum input voltage under all conditions.                                                                                                                                      |                       |

| R <sub>ON</sub>                     | From datasheet,                                                                                                                                                                                                                                 | 130kΩ                 |

|                                     | $f_{SW} = \frac{V_{OUT1}}{K \times R_{ON}} $ (2)                                                                                                                                                                                                | 1)                    |

|                                     | Where K = 1 x $10^{-10} \rightarrow R_{ON} = 133 \text{ k}\Omega$                                                                                                                                                                               |                       |

| $R_{\text{UV1}},  R_{\text{UV2}}$   | UVLO resistors RFB1 and RFB2 set the UVLO threshold and hysteresis according to the following relationship:                                                                                                                                     | 4.42kΩ, 125kΩ         |

|                                     | $V_{IN (HYS)} = I_{HYS} \times R_{UV2} $ (2)                                                                                                                                                                                                    | 2)                    |

|                                     | and                                                                                                                                                                                                                                             |                       |

|                                     | $V_{IN}(UVLO, rising) = 1.225V \times \left(\frac{R_{UV2}}{R_{UV1}} + 1\right)$ (23)                                                                                                                                                            | 3)                    |

|                                     | where $I_{HYS}\!\!=\!\!20\mu A.$ Setting UVLO hysteresis of 2.5 V and UVLO rising threshold of 36 V results in $R_{UV1}\!\!=\!\!4.42k\Omega;$ and $R_{UV2}\!\!=\!\!125k\Omega$                                                                  |                       |

www.ti.com Design Example

Table 2. Component Calculation/Selection Steps for a Two-Output Isolated Buck (continued)

| Component Name | Calculation Steps                                                                                                                                                                                                                                                                                                                                                                                                         | Selected Value/Rating     |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| X1             | A coupled inductor or a flyback type transformer is required for this topology. Energy is transferred from primary to secondary when the synchronous switch of the buck is ON.  Using Equation 16 for the peak inductor current equation in Table 1, the maximum inductor current ripple that can be tolerated is given by: $\Delta I_{L1} = \left(0.7 - I_{OUT1} - I_{OUT2} \times \frac{N2}{N4}\right) \times 2 = 0.8A$ | L1=33 μH, 1:1 turns ratio |

|                | Using Equation 17 for the peak-to-peak inductor current ripple equation, the minimum inductor value is given by:  (24)                                                                                                                                                                                                                                                                                                    |                           |

|                | $L1 = \frac{\left(V_{\text{IN (MAX)}} - V_{\text{OUT}}\right)}{\Delta I_{\text{L1}} \times f_{\text{SW}}} \frac{V_{\text{OUT}}}{V_{\text{IN (MAX)}}} = 14.4 \ \mu\text{H} $ (25)                                                                                                                                                                                                                                          |                           |

|                | A higher value such as 22 µH or 33 µH for primary inductance can be selected to keep the primary winding and high-side switch current below the minimum peak current limit. For our design, a 33 µH value is selected for primary inductance. For this chosen primary inductance, in the primary inductor current ripple during TON is Equation 26                                                                        |                           |

|                | $\Delta I_{L1} = \frac{\left(V_{\text{IN (MAX)}} - V_{\text{OUT}}\right)}{L1 \text{ x } f_{\text{SW}}} \frac{V_{\text{OUT}}}{V_{\text{IN (MAX)}}} $ (26)                                                                                                                                                                                                                                                                  |                           |

|                | A 1:1 turns ratio is selected, resulting in Equation 27 $V_{OUT2} = \frac{N2}{N1} V_{OUT1} - V_F \approx 9.3V \tag{27}$                                                                                                                                                                                                                                                                                                   |                           |

| D1             | The voltage across D1 when the high side buck switch is on is $V_{D1} = \frac{N2}{N1} V_{IN} \eqno(28)$                                                                                                                                                                                                                                                                                                                   | 100 V, 1A<br>DLFS1100–7   |

|                | For a V <sub>IN_MAX</sub> =72 V, a 100 V Schottky is selected.                                                                                                                                                                                                                                                                                                                                                            |                           |

Design Example www.ti.com

Table 2. Component Calculation/Selection Steps for a Two-Output Isolated Buck (continued)

| Component Name    | Calculation Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Selected Value/Rating |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| C <sub>OUT1</sub> | In a buck converter, $\Delta V_{OUT} = \frac{\Delta I_{L1}}{8 \text{ x f x C}_{OUT1}} $ (29)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 μF, 25 V, X7R       |

|                   | and therefore for an output voltage ripple of ~50 mV gives, $C_{\text{OUT1}} = 1.16~\mu\text{F}$ . Selecting a standard value of 1 $\mu\text{F}$ results in $\Delta V_{\text{OUT}} = 60~\text{mV}$ at $V_{\text{IN}} = 72~\text{V}$ and $\Delta V_{\text{OUT}} = 50~\text{mV}$ at $V_{\text{IN}} = 36~\text{V}$ . The figure below shows the primary winding current waveform (IL1). The reflected secondary winding current adds to the primary winding current. Because of this the output voltage ripple is not the same as in a non-isolated buck converter. The output capacitor value calculated in Equation 29 should be used as the starting point. Actual optimization of output capacitor over the whole line/load range must be done experimentally. A better approximation of the primary output capacitor voltage ripple is given by Equation 30: |                       |

|                   | $\Delta V_{OUT1} = \frac{\left(I_{OUT2} \times \frac{N2}{N1}\right) \times T_{ON \text{ (MAX)}}}{C_{OUT1}} \approx 75 \text{ mV}$ $T_{ON \text{(MAX)}} \times I_{OUT2} \times N2/N1$ (30)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |

|                   | I <sub>L1</sub> I <sub>L2</sub> I <sub>OUT2</sub> I <sub>OUT2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

|                   | Current Waveforms for C <sub>OUT1</sub> Ripple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |

|                   | Calculation (31)  As can be seen from the primary inductor current waveform in the above figure, in case of low leakage, the primary winding current reverses immediately when the secondary winding starts conducting. Therefore, the reflected secondary winding current induced primary output ripple voltage is not phase-lagged with respect to the switch node waveform. Therefore, the reflected load current induced voltage ripple does not need to be compensated for with the ripple injection circuit.  If lower output voltage ripple is required, a higher value should be                                                                                                                                                                                                                                                                       |                       |

| ^                 | selected for C <sub>OUT1</sub> and/or C <sub>OUT2</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 uE 25 V V7D         |

| C <sub>OUT2</sub> | A simplified waveform for secondary output current (I <sub>OUT2</sub> ) and the current in the secondary winding is shown in the figure below.  I <sub>OUT2</sub> T <sub>ON(MAX)</sub> × I <sub>OUT2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 μF, 25 V, X7R       |

|                   | Secondary Current Waveforms for C <sub>OUT2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |

|                   | Ripple Calculation (32)  The secondary output current (I <sub>OUT2</sub> ) is sourced by C <sub>OUT2</sub> during one time TON. Ignoring the current transitions time in the secondary winding, the secondary output capacitor ripple voltage can be calculated using Equation 33:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |

|                   | $\Delta V_{\text{OUT2}} = \frac{I_{\text{OUT2}} \times T_{\text{ON (MAX)}}}{C_{\text{OUT2}}} $ (33)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

|                   | For a 1:1 transformer turns ratio the primary and secondary voltage ripple equations are identical. Therefore, $C_{\text{OUT2}}$ is chosen to be equal to $C_{\text{OUT1}}$ (1 µF) to get comparable ripples on primary and secondary outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |

|                   | If lower output voltage ripple is required, a higher value should be selected for $C_{\text{OUT}_1}$ and/or $C_{\text{OUT}_2}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

www.ti.com Design Example

Table 2. Component Calculation/Selection Steps for a Two-Output Isolated Buck (continued)

| <b>Component Name</b> | Calculation Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Selected Value/Rating              |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46kΩ, 0805, 1000 pF, 0.1 μF (25 V) |

|                       | Type II Ripple Circuit (34)   Using type III ripple circuit equations, the target ripple should be greater than the capacitive ripple generated at the primary output. $C_r = 1000 \text{ pF}$ $C_{ac} = 0.1 \mu\text{F}$ $R_r C_r \leq \frac{\left(V_{\text{IN }(\text{MIN)}} - V_{\text{OUT}}\right) \times T_{\text{ON}}}{50 \text{ mV}}$ (35)   Resulting in Rr= 180k $\Omega$ . This is the borderline case of stable ripple.   Half to a fourth of this resistance should be selected for sufficient margin for variations in TON, $C_{\text{OUT1}}$ , and other components. For this design Rr = 46.4k $\Omega$ ; is selected for robust operation. |                                    |

| D2 (optional)         | D2 is an optional diode connected between $V_{OUT1}$ and $V_{CC}$ regulator output. When $V_{OUT1}$ is > $V_{CC}$ the $V_{CC}$ supplied from $V_{OUT1}$ . This results in reduced losses in $V_{CC}$ regulator inside the IC.                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 V, 50 mA                        |

The final schematic for the isolated power supply is shown in Figure 1. The experimental results for this circuit are presented in Figure 2, Figure 3, and Figure 4.

Conclusions www.ti.com

#### 4 Conclusions

An isolated buck converter (or Fly-Buck) converter was presented that does not require any additional winding or optocoupler for regulating an isolated output. The operating principle of the topology was also presented along with operating current and voltage waveforms. The relationship between the primary and the isolated output voltages and output currents were presented. We also developed design equations for estimating the peak primary switch current for specified load currents. The equations in this design can also be used to determine the maximum load current that the converter can provide for a given peak current limit. Simplified approximations for output voltage ripples were also presented. A detailed design procedure was presented for a 3W two-output isolated buck converter with a primary output and an isolated output using a 100 V synchronous buck regulator IC.

An isolated buck converter can be used to replace a flyback converter for low-power isolated regulator applications with potential savings in complexity, number of components, and cost. Learn more about flyback converters on the Power Management website at <a href="https://www.ti.com">www.ti.com</a>.

### 5 References

LM5017: 100 V,600 mA Constant On-Time Synchronous Buck Data Sheet (SNVS783) LM5160 Wide Input 65 V, 1.5A Synchronous Step-Down DC-DC Converter (SNVSA03)

www.ti.com Revision History

## **Revision History**

|   | Changes from B Revision (May 2013) to C Revision |          |  |

|---|--------------------------------------------------|----------|--|

|   | Changed 8 to 4                                   |          |  |

|   | Changed value from 1.24 to 0.2                   |          |  |

| • | Added two sentences                              | ······ 6 |  |

|   | Added 0.47 +                                     |          |  |

| • | Added reference                                  | 10       |  |

|   |                                                  |          |  |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products | Applications |

|----------|--------------|

| Products | Applications |

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic Security www.ti.com/security logic.ti.com

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity