# Reducing System Complexity With Self-Latching Comparators

Ho Siu

#### Introduction

For voltage and current fault signals, it is often advantageous to latch the detection signal into the fault state until the system controller takes action to fix the faults. Latching maintains that the fault condition is acknowledged and addressed by the system controller before the latch is deliberately released. The latching functionality of comparators is typically implemented with a comparator and other discrete components. Designing and controlling a discrete latching comparator takes up board space, as well as introduces complexity to the design. This application brief explains the advantages of using TI's self-latching comparator family over discrete latching comparators.

## **Discrete Latching Comparator**

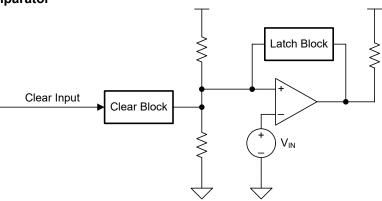

Figure 1. Block Diagram Implementation of a Latching Comparator

A discrete latching comparator is implemented with two functional blocks: a latch block and a clear block. The latch block serves to latch the output of the comparator after a fault condition is detected. The clear block serves to clear the latch to put the comparator back into an armed state for the next detection of the fault. Below is an example of a discrete implementation for an inverting comparator that latches low.

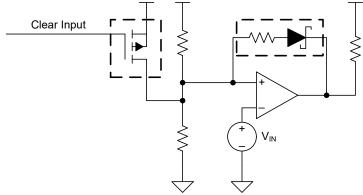

Figure 2. Example Discrete Implementation of a Latching Comparator

The latch block is implemented by a Schottky diode and a resistor. During output low, the diode is forward biased and conducts to pull the non-inverting input of the comparator low. This action latches the comparator, as the non-inverting input is now a low voltage such that the inverting input can no longer cross the non-inverting input to cause an output high state. The clear function is implemented with an enhancement-mode PMOS that clears the latch on active low. The PMOS pulls the non-inverting input of the comparator up to the supply voltage to assert an output high to clear the latch.

Discrete implementations of a latching comparator add complexity to the system. Designer must account for the electrical characteristics of the latch block and the clear block. When using discrete components, such as the series resistor and Schottky diode in Figure 2, there are additional considerations to take into account to establish functionality. For example, the designer must select an appropriate resistor and Schottky diode to effectively pull the non-inverting input to a lower voltage than the input voltage at the inverting terminal. Additionally, the designer must choose and drive the pull-up PMOS to overcome the series resistor and Schottky diode to release the latch. The addition of the discrete components also affects the power dissipation of the circuit and the amount of board space the design occupies.

#### **Integrated Self-Latching Comparator**

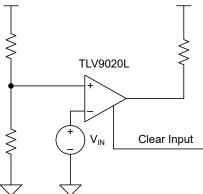

TI's TLV902xL family offers integrated self-latching comparators. The latching and clear functionality are integrated into the device, so the comparator does not need discrete components to implement latch and clear blocks. The discrete implementation above can be substituted with TLV9020L without the need for the discrete PMOS, Schottky diode, and extra resistor.

Figure 3. Self-latching Comparator Implementation Using TLV9020L

TLV9020L is an open-drain, self-latching comparator that latches low. The output of the comparator stays latched low on the first high-to-low transition until the device is manually cleared by a negative edge clear signal.

www.ti.com Trademarks

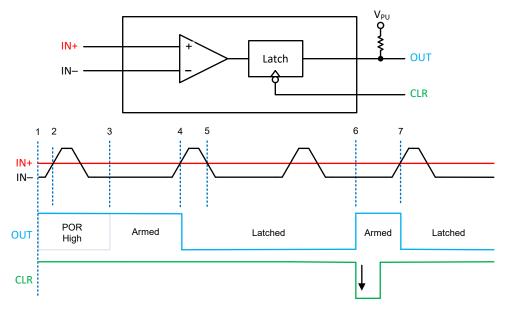

Figure 4. Timing Diagram for TLV9020L

TLV9020L integration of the latch and clear functions simplify the design and control of the latching comparator. The lack of additional discrete components reduces the overall board space this circuit occupies. There are fewer considerations for the latch and clear, as the latch is handled internally to the TLV9020L, and the clear is a digital signal with an input low level of 0.6V and an input high level 1.2V. TLV9020L has an edge-triggered clear that offers advantages over level-triggered clears. Fault conditions can cause the clear signal to short to ground or the supply voltage, inadvertently causing the comparators to constantly be in a clear state and fail to detect fault conditions. This failure is mitigated by the TLV9020L negative edge-triggered clear signal. Overall, the TL902xL family offers improvement in functionality and design simplicity when compared to discrete latching comparators.

The TLV902xL and TLV903xL family have several power-on options differentiated by *L1* and *L2* options, depending on whether the user wants the self-latching comparator to power on in a latched or unlatched state.

**Output State During Output State After Armed Output Device Output Type Output Latch POR** POR Latches On Condition TLV902xL1 Open-Drain High Armed  $H \rightarrow L$ Low TLV902xL1-Q1 TLV902xL2 Open-Drain Low Latched Low  $\mathsf{H} \to \mathsf{L}$ Low TLV902xL2-Q1 TLV903xL1 Push-Pull Hi-Z Armed  $I \rightarrow H$ High TLV903xL1-Q1 TLV903xL2 Push-Pull High Latched High  $L \rightarrow H$ High TLV903xL2-Q1

**Table 1. Power-On Options**

## **Trademarks**

All trademarks are the property of their respective owners.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated