Gerome Cacho

### ABSTRACT

Fiber transmission, otherwise known as 1000BASE-X or 100BASE-FX depending on speed, is a type of communication interface that connects between two Ethernet PHYs. As opposed to traditional copper communication, fiber transmission has advantages such as faster linkup times as well as less signal integrity issues that can otherwise come from a long copper wire.

# **Table of Contents**

| 1 What is Fiber?            | 2 |

|-----------------------------|---|

| 1.1 Pins Used               |   |

| 1.2 Hardware Configurations |   |

| 1.3 Useful Registers        | 4 |

| 2 Common Use Cases          | 5 |

| 3 Summary                   | 6 |

| 3 Summary<br>4 References   | 6 |

| <b>_</b>                    |   |

### Trademarks

All trademarks are the property of their respective owners.

1

# 1 What is Fiber?

Fiber is a type of communication interface that is supported on DP83822 and DP83869. While DP83869HM has a single variant, DP83822 supports fiber in the -IF and -HF variants.

### 1.1 Pins Used

For each device, there are fives pins used for fiber communication. However, as best practice, make sure that the PHY is bootstrapped into the respective modes for fiber operation.

| Pin Name (Number) | Functionality                                                                                                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TD_P (12)         | Transmitting Pins. Output of the PHY.                                                                                                                                                           |

| TD_M (11)         |                                                                                                                                                                                                 |

| RD_P (10)         | Receiving Pins. Input of the PHY.                                                                                                                                                               |

| RD_M (9)          |                                                                                                                                                                                                 |

| LED_1/GPIO1 (24)  | Signal Detect. Typically connected to SFP module which helps determine if communication has been interrupted and relays to PHY to drop link. Use other LED pins for appropriate functionalities |

#### Table 1-1. DP83822 Fiber Pins

| Table 1-2. DP83822 Fiber Bootstrapping |                  |                      |  |

|----------------------------------------|------------------|----------------------|--|

| Pin Name (Number)                      | Strap Mode       | Description          |  |

| COL (29)                               | 2 or 3           | Enables FX_EN        |  |

| LED_0 (17)                             | 1                | Half Duplex          |  |

|                                        | 4 (Default)      | Full Duplex          |  |

| RX_ER (28)                             | 3 or 4 (Default) | Signal Detect Enable |  |

#### Table 1-3. DP83869 Fiber Pins

| Pin Name (Number) | Functionality                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| SOP (15)          | Transmitting Pins. Output of the PHY.                                                                                                        |

| SON (14)          |                                                                                                                                              |

| SIP (16)          | Receiving Pins. Input of the PHY.                                                                                                            |

| SIN (17)          |                                                                                                                                              |

| JTAG_TDI/SD (24)  | Signal Detect. Typically connected to SFP module which helps determine if communication has been interrupted and relays to PHY to drop link. |

## Table 1-4. DP83869 Fiber Bootstrapping

| Pin Name (Number)    | Strap Name | OPMODE[2] | OPMODE[1] | OPMODE[0] | Functional Mode                                      |

|----------------------|------------|-----------|-----------|-----------|------------------------------------------------------|

| RX_D2 (35)           | OPMODE[2]  | 0         | 0         | 1         | RGMII to 1000BASE-X                                  |

| RX_D3 (36)           | OPMODE[1]  | 0         | 1         | 0         | RGMII to 100BASE-FX                                  |

| JTAG_TDO/GPIO_1 (22) | OPMODE[0]  | 1         | 0         | 0         | Media Convertor (1000BASE-T to 1000BASE-X): 1000Mbps |

|                      |            | 1         | 0         | 1         | Media Convertor (100BASE-Tx to 100BASE-Fx): 100Mbps  |

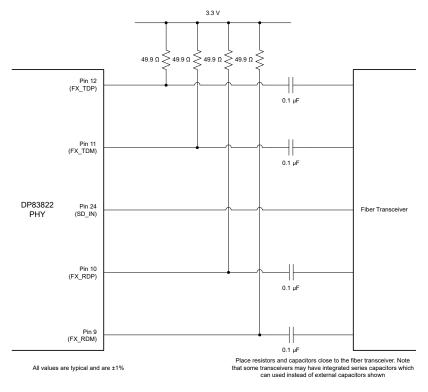

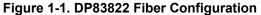

## **1.2 Hardware Configurations**

The following are configurations for connections between the PHY and fiber module. Between fiber modules, there are typically two cables; one for transmitting, and one for receiving. A cable needs to be connected between one module's transmit port and another module's receive port.

# **1.3 Useful Registers**

#### Table 1-5. DP83822 Fiber Registers

| Register Address | Bitfield | Description/Usefulness                                                      |

|------------------|----------|-----------------------------------------------------------------------------|

| 0x1              | 2        | Link                                                                        |

| 0xA              | 14       | 100BASE-FX Enable                                                           |

| 0x16             | 4        | Reverse Loopback Enable                                                     |

| 0x40             | 6:5      | [6] = Far End Fault Generator Disable<br>[5] = Far End Fault Detect Disable |

| 0x403            | 11:8     | Adjusts Transmitter Swing                                                   |

| 0x465            | 0        | Signal Detect Polarity (Default Active High for good signal)                |

| 0x467            | 15:0     | Bootstrapping Status                                                        |

| 0x468            | 15:0     |                                                                             |

| Register Address | Table 1-6. DP83869 Fib<br>Bitfield | Description/Usefulness                                                                                                                                                                      |  |

|------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x11             | 15:11, 9:8                         | Copper Link Supplimental Status (Useful for<br>Media Converter only)                                                                                                                        |  |

| 0x1DF            | 2:0                                | Operation Mode:<br>0x1 for RGMII to 1000BASE-X<br>0x2 for RGMII to 100BASE-FX<br>0x4 for 1G Media Converter<br>0x5 for 100M Media Converter                                                 |  |

| 0xC00            | 15:12, 10:8, 6                     | Fiber Control Register<br>[15] = Fiber Reset<br>[14] = MAC Loopback<br>[6,13] = Speed<br>[12] = Enable Auto-Negotiation<br>[10] = Isolate<br>[9] = Restart Auto-Negotiation<br>[8] = Duplex |  |

| 0xC01            | 2                                  | Link                                                                                                                                                                                        |  |

| 0xC10            | 15:14, 9                           | <ul> <li>[15] = Far End Fault Generator Disable</li> <li>[14] = Far End Fault Detect Disable</li> <li>[9] = Signal Detect Disable</li> </ul>                                                |  |

| 0xC19            | 9                                  | FEF Interrupt Status                                                                                                                                                                        |  |

| 0xC1A            | 5                                  | Fiber Reverse Loopback Enable                                                                                                                                                               |  |

| 0xC30            | 2                                  | Signal Detect Polarity Configuration (Default<br>Active Low for good signal)                                                                                                                |  |

| 0x6E             | 15:0                               | Bootstrapping Status                                                                                                                                                                        |  |

(1) Program Reg 0xC2A[15] = '1' in addition to Reg 0xC10[14] = '1' for FEF detection disable

# 2 Common Use Cases

The following are common occurrences when using the PHY in Fiber mode and potential descriptions of events which can occur if the occurrence happened.

| Event                                                                            | Results                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Opposing or local SFP modules are disconnected from board                        | Both PHYs lose link                                                                                                                                                                                                                                                                                                                      |

| Both fiber cables disconnected (TX and RX)                                       |                                                                                                                                                                                                                                                                                                                                          |

| Single fiber cable is disconnected                                               | Both PHYs lose link due to Far-End Fault (FEF), a functionality where if DUT senses that link has been lost, the DUT can send a FEF signal over the transmitting line so the link partner can also drop link. While FEF is enabled by default, the FEF can have the detection and/or generation functionality disabled through register. |

|                                                                                  | 1. If FEF generation is disabled on DUT, when DUT RX cable is unplugged, PHY does not send FEF to link partner through DUT TX cable. This can cause a scenario where DUT PHY indicates no link, but link partner PHY does indicate link.                                                                                                 |

|                                                                                  | 2. If FEF detection is disabled on DUT, when DUT TX cable is unplugged, link partner PHY can send FEF to DUT. However, DUT does not detect FEF and thus not drop link. This can create a scenario where DUT indicates link and link partner indicates no link.                                                                           |

| Inverted Signal Detect                                                           | This can create false-negative or false-positive linkup status. Please confirm polarity of pin, detect prior to plugging in to avoid damage to device or module. If polarity needs to be switched, a register write needs to be written prior to plugging in module.                                                                     |

| Mismatching SFP Modules on<br>optical connection (100BASE-FX<br>with 1000BASE-X) | PHYs do not link up                                                                                                                                                                                                                                                                                                                      |

| Mismatching SFP and PHY speed (822)                                              | If given a 1G SFP with a matching 1G SFP from link partner side, DP83822 can link up and think the DUT has a fiber link at 100Mbps. Packet throughput was tested successfully. However, if module speeds mismatch, PHYs do not link per above case.                                                                                      |

| Mismatching SFP and PHY speed<br>(869)                                           | If given a 100Mbps SFP when in 1G Fiber (1000Base-X or 1000M Media Converter), and connected to another DP83869 in same mode, PHY does not link up.<br>If given a 1000Mbps SFP when in 100M Fiber (100Base-FX or 100M Media Converter) PHYs can link up and have shown valid throughput.                                                 |

Table 2-1. Common Occurrences Using PHY in Fiber Mode

5

# 3 Summary

This application note provides consolidated information on the fiber functionality available in DP83822 and DP83869. The document includes characterizations for the interface and exclusive register information for debugging fiber.

## **4** References

- Texas Instruments, *DP83822 Robust, Low Power 10/100 Mbps Ethernet Physical Layer Transceiver* data sheet.

- Texas Instruments, DP83869HM High Immunity 10/100/1000 Ethernet Physical Layer Transceiver With Copper and Fiber Interface data sheet.

- Texas Instruments, *DP83822IF: Fiber Link Status*, E2E™ Design Support Forum.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated