## How to Design a FPD-Link III System Using DS90UB953-Q1 and DS90UB954-Q1

Cole Macias and Mandeep Singh

#### ABSTRACT

FPD-Link III devices such as the DS90UB95x-Q1 can support cameras in Advanced Driver Assist Systems (ADAS) in the automotive industry. There are complications that can occur in system implementation due to the complexity of the technology, so it is important to ensure proper design. The purpose of this document is to systematically design a SERDES system using the DS90UB953-Q1 and DS90UB954-Q1.

| Contents |

|----------|

|----------|

| 1 | Overvi | ew                                                         | 3  |

|---|--------|------------------------------------------------------------|----|

|   | 1.1    | System Level Functionality                                 | 3  |

| 2 | Basic  | Design Rules                                               | 4  |

|   | 2.1    | IDX and MODE Pin Verification                              |    |

|   | 2.2    | Successful I <sup>2</sup> C Communication With 953 and 954 | 10 |

|   | 2.3    | I2C Passthrough Verification                               | 12 |

|   | 2.4    | Basic Diagnostic and Error Registers                       | 12 |

| 3 | Desigr | ning the Link Between SER and DES                          | 14 |

|   | 3.1    | Back Channel Configuration                                 | 15 |

|   | 3.2    | BIST                                                       | 16 |

|   | 3.3    | AEQ                                                        | 20 |

|   | 3.4    | CML Out                                                    | 21 |

| 4 | Desigr | ning Link Between SER and Image Sensor                     | 21 |

|   | 4.1    | Sensor Initialization Using SER GPIOs                      | 21 |

|   | 4.2    | CLKOUT                                                     | 23 |

| 5 | Desigr | ning Link Between DES and ISP                              |    |

|   | 5.1    | Frame Sync                                                 | 24 |

|   | 5.2    | Port Forwarding                                            | 29 |

|   | 5.3    | Pattern Generation                                         | 29 |

| 6 | Hardw  | are Design                                                 | 31 |

|   | 6.1    | Basic I2C Connectors                                       |    |

|   | 6.2    | AC Capacitor on FPD3 Link                                  | 32 |

|   | 6.3    | Capacitance Used in Loop Filter                            |    |

|   | 6.4    | Critical Signal Routing                                    |    |

|   | 6.5    | Time Domain Reflection                                     |    |

|   | 6.6    | Return Loss and Insertion Loss                             | 33 |

|   | 6.7    | Power-over-Coax (PoC)                                      | 33 |

|   | 6.8    | Voltage and Temperature Sensing                            |    |

| 7 | Appen  | dix                                                        |    |

|   | 7.1    | Scripts                                                    |    |

|   | 7.2    | Acknowledgments                                            |    |

|   |        |                                                            |    |

#### List of Figures

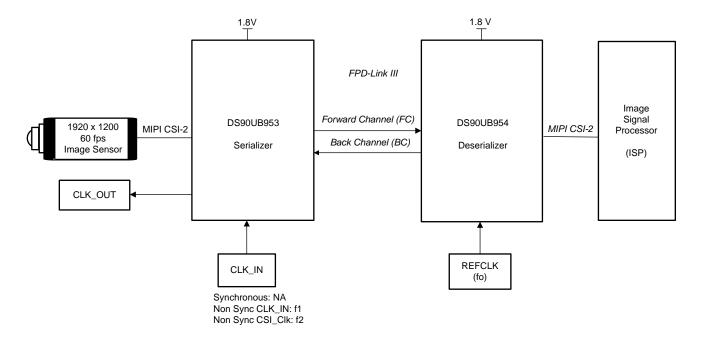

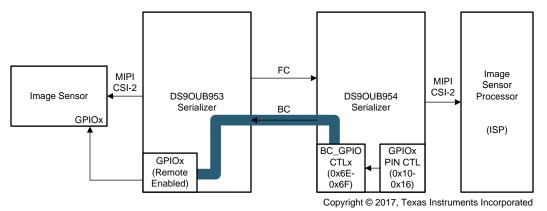

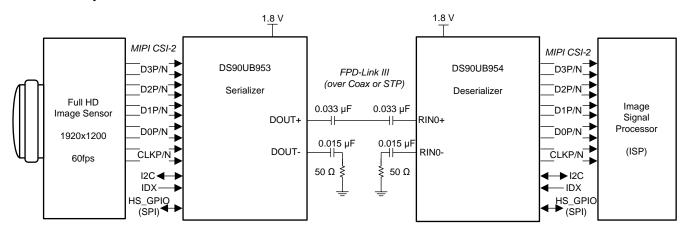

| 1 | Simplified Block Diagram of DS90UB953/DS90UB954-Q1 System | 3 |

|---|-----------------------------------------------------------|---|

| 2 | Basic Design Rules Flowchart                              | 4 |

| Clocking System Diagram                                         | 6                                                             |

|-----------------------------------------------------------------|---------------------------------------------------------------|

| Illustration of Synchronous Clocking                            |                                                               |

| Illustration of Non-Synchronous Mode With External Oscillator   | . 8                                                           |

| Illustration of Non-Synchronous Mode With Always on Clock (AON) | . 8                                                           |

| Illustration of Two Ports                                       | 11                                                            |

| Flowchart for SER and DES Link                                  | 15                                                            |

| BIST Script Flowchart                                           | 17                                                            |

| Image Sensor and SER Link Design                                | 21                                                            |

| Flowchart for Initializing the Image Sensor Using GPIO's        | 22                                                            |

| Clocking System Diagram                                         | 23                                                            |

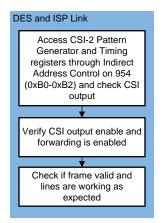

| DES and ISP Link Flowchart                                      | 24                                                            |

| Steps for Controlling SER GPIOs Remotely and Locally            | 24                                                            |

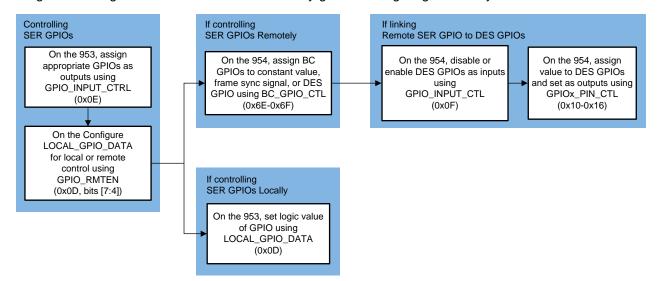

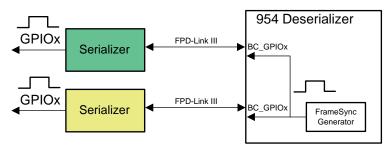

| Block Diagram of Controlling SER GPIOs Over BC                  | 25                                                            |

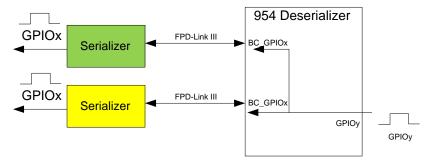

| Block Diagram of Controlling SER GPIOs Remotely                 | 26                                                            |

| Block Diagram of Internally Generated Frame Sync                | 27                                                            |

| Block Diagram of Externally Generated Frame Sync                | 28                                                            |

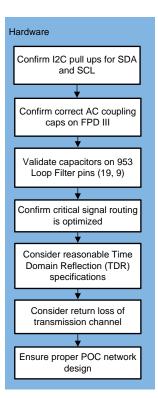

| Hardware Design Flowchart                                       | 31                                                            |

| Simplified Block Diagram of DS90UB953-Q1/DS90UB954-Q1 System    | 32                                                            |

|                                                                 | Illustration of Non-Synchronous Mode With External Oscillator |

#### List of Tables

| 1  | Serial Control Bus Addresses for IDX on the 953                            | 5  |

|----|----------------------------------------------------------------------------|----|

| 2  | Serial Control Bus Addresses for IDX on the 954                            | 5  |

| 3  | DS90UB953-Q1 Strap Configuration Mode Select                               | 6  |

| 4  | DS90UB954-Q1 Strap Configuration Mode Select                               | 6  |

| 5  | Mode Clock Calculation Table                                               | 9  |

| 6  | Mode Clock Settings With Descriptions of fo and f1                         | 9  |

| 7  | Bit Description of SER_ALIAS_ID Register With Example                      | 11 |

| 8  | Bit Description of FPD3_PORT_SEL Register 0x4C                             | 12 |

| 9  | Communication of I2C Devices Using Various Passthrough Settings            | 12 |

| 10 | DS90UB954-Q1 Registers Used for Diagnostics and Checking Errors            | 13 |

| 11 | DS90UB953-Q1 Registers Used for Diagnostics and Checking Errors            | 14 |

| 12 | Settings for Bidirectional Configuration (BCC_CONFIG) Register 0x58 on 954 | 16 |

| 13 | RESET_CTL Register Description on 953                                      | 17 |

| 14 | DEVICE_STS Register Description on 954                                     | 18 |

| 15 | GENERAL_STATUS Register Description for Lock on 953                        | 18 |

| 16 | DS90UB954-Q1 Registers Used in BIST Script                                 | 19 |

| 17 | DS90UB953-Q1 Registers Used in BIST Script                                 | 20 |

| 18 | Channel Monitor Loop-Through Output Configuration of the 954               | 21 |

| 19 | Bit Description of GPIO_INPUT_CTRL Register 0x0E                           | 22 |

| 20 | Bit Description of LOCAL_GPIO_DATA Register 0x0D                           | 22 |

| 21 | Example Using GPIO_INPUT_CTRL Register 0x0E for Local SER GPIO Control     | 25 |

| 22 | Example Using LOCAL_GPIO_DATA Register 0x0D for Local SER GPIO Control     | 25 |

| 23 | Example Using LOCAL_GPIO_DATA Register 0x0D for Local SER GPIO Control     | 26 |

| 24 | BC_GPIO_CTL0 Registers From the 954 Data Sheet                             | 26 |

| 25 | Example using BC_GPIO_CTL0 Register 0x6E for Remote SER GPIO Control       | 27 |

| 26 | Registers Used When Configuring GPIOS and Frame Sync on the 953 and 954    | 28 |

## Trademarks

All trademarks are the property of their respective owners.

## 1 Overview

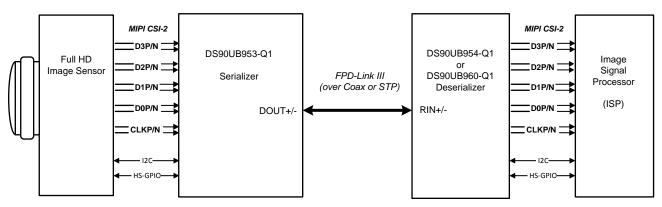

## 1.1 System Level Functionality

The DS90UB954-Q1 FPD-Link III deserializer, in conjunction with an ADAS FPD-Link III serializer, supports the video transport needs with an ultra-high-speed forward channel and an embedded bidirectional control channel. After the DS90UB954-Q1 receives the data, the device outputs the data from a configurable MIPI CSI-2 port. The CSI-2 port may be configured as either a single CSI-2 output with four lanes up to 1.662 Gbps per lane, or as two 2-lane CSI-2 outputs that can send replicated data on both ports. The engineer can use a second differential clock for the second replicated output when the device is configured for dual CSI-2 outputs that can support one clock lane and one or two data lanes each. The DS90UB954-Q1 can support multiple data formats and different resolutions as provided by the sensor. Conversion between different data formats is not supported. The CSI-2 Tx module accommodates both image data and non-image data (including synchronization or embedded data packets).

The DS90UB953-Q1 serializes data from high-resolution image sensors or other sensors using the MIPI CSI-2 interface. The DS90UB953-Q1 serializer is optimized to interface with the DS90UB954-Q1 deserializer (dual hub) or the DS90UB960-Q1 deserializer (quad hub) as well as potential future deserializers. The interconnect between the serializer and the deserializer can be either a coaxial or shielded twisted-pair (STP) cable. The DS90UB953-Q1 was designed to support multi-sensor systems such as surround view, and as such has the ability to synchronize sensors through the DS90UB954-Q1 and DS90UB960-Q1 hub.

Due to the complexity of this system, there are a variety of issues that can be avoided by proper design. The purpose of this guide is the help the user systematically design a system using the 953 and 954. The following chapters show the typical concepts and tests and how to implement them. This guide lists basic design rules as a checklist that should be followed to ensure proper initialization of the system. The items described in the suggested checklist are the building blocks of the system. Without them, the system will not work as expected.

Following the completion of the basic design rules section, this guide provides analysis of the three important links in the ADAS System using DS90UB953-Q1 and DS90UB954-Q1:

- 1. The link between the serializer (SER) and deserializer (DES)

- 2. The link between the serializer and imager sensor

- 3. The link between the deserializer and Image Signal Processor (ISP)

Important procedures and design considerations are highlighted and explained in the form of script examples, general steps, and flow charts.

At the end of this guide is a set of hardware design topics that are commonly discussed when designing a SERDES system.

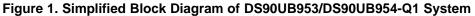

### 2 Basic Design Rules

This chapter describes a list of key items that are fundamental when powering on the system. These items define the functionality of the entire system. To get the system up and running quickly, TI recommends to check these items before moving forward.

Figure 2. Basic Design Rules Flowchart

### 2.1 IDX and MODE Pin Verification

Each IDX and Mode pin contains a voltage divider to the respective IDX and Mode pins on the 953 and 954. The IDX and Mode pins read the voltage on the pin, and the internal comparators decide which IDX or Mode is assigned to each device. As a result, the required voltage supply and the ratio of the resistor divider are used to set the IDX and Mode pins.

### 1. Ensure commands refer to correct I<sup>2</sup>C addresses by checking the IDX pin.

- a. The IDX pin configures the control interface to one of many possible device addresses used in I2C communication. Usually for 1.8-V or 3.3-V referenced I2C I/O voltage, a pullup resistor and a pulldown resistor is used to set the appropriate voltage on the IDX input pin of both devices.

- b. The IDX resistor divider must be referred to Pin #25 on the 953 and Pin #35 on the 954. Tables that hold appropriate resistor values for setting IDX are shown below.

- c. For example the 953 can have an open pullup resistor, a 40.2-k $\Omega$  pulldown resistor, and an I2C supply of 1.8 V to achieve a device ID of 0x30. This is shown in Table 1.

| www.ti.com | ۱ |

|------------|---|

|------------|---|

| IDX | V <sub>TARGET</sub> VOLTAGE RANGE |              |              | V <sub>IDX</sub><br>TARGET<br>VOLTAGE | SUGGESTE<br>RESISTORS  |                       | I2C 8-BIT<br>ADDRESS | 12C 7-BIT<br>ADDRESS | I2C I/O<br>VOLTAGE |

|-----|-----------------------------------|--------------|--------------|---------------------------------------|------------------------|-----------------------|----------------------|----------------------|--------------------|

|     | RATIO<br>MIN                      | RATIO<br>TYP | RATIO<br>MAX | V <sub>VDD</sub> = 1.8 V              | R <sub>HIGH</sub> (kΩ) | R <sub>Low</sub> (kΩ) | ADDRESS              | ADDRE33              | VOLTAGE            |

| 1   | 0.000                             | 0.00         | 0.131        | 0.000                                 | Open                   | 40.2                  | 0x30                 | 0x18                 | 1.8 V              |

| 2   | 0.178                             | 0.214        | 0.256        | 0.385                                 | 180                    | 47.5                  | 0x32                 | 0x19                 | 1.8 V              |

| 3   | 0.537                             | 0.564        | 0.591        | 1.015                                 | 82.5                   | 102                   | 0x30                 | 0x18                 | 3.3 V              |

| 4   | 0.652                             | 0.679        | 0.706        | 1.223                                 | 68.1                   | 137                   | 0x32                 | 0x19                 | 3.3 V              |

Table 1. Serial Control Bus Addresses for IDX on the 953

## Table 2. Serial Control Bus Addresses for IDX on the 954

| NO. | VIDX VOLTAGE RANGE              |                                 |                                 | V <sub>IDX</sub> TARGET<br>VOLTAGE | SUGGESTED STRAP<br>RESISTORS (1% TOL) |                       | PRIMARY ASSIGNED I <sup>2</sup> C<br>ADDRESS |       |

|-----|---------------------------------|---------------------------------|---------------------------------|------------------------------------|---------------------------------------|-----------------------|----------------------------------------------|-------|

|     | V <sub>MIN</sub>                | V <sub>TYP</sub>                | V <sub>MAX</sub>                | (V); VDD1P8 = 1.8<br>V             | R <sub>HIGH</sub> (ΚΩ)                | R <sub>LOW</sub> (ΚΩ) | 7-BIT                                        | 8-BIT |

| 0   | 0                               | 0                               | 0.131 ×<br>V <sub>(VDD18)</sub> | 0                                  | OPEN                                  | 10.0                  | 0x30                                         | 0x30  |

| 1   | 0.179 ×<br>V <sub>(VDD18)</sub> | 0.213 ×<br>V <sub>(VDD18)</sub> | 0.247 ×<br>V <sub>(VDD18)</sub> | 0.374                              | 88.7                                  | 23.2                  | 0x32                                         | 0x32  |

| 2   | 0.296 ×<br>V <sub>(VDD18)</sub> | 0.330 ×<br>V <sub>(VDD18)</sub> | 0.362 ×<br>V <sub>(VDD18)</sub> | 0.582                              | 75.0                                  | 35.7                  | 0x34                                         | 0x34  |

| 3   | 0.412 ×<br>V <sub>(VDD18)</sub> | 0.443 ×<br>V <sub>(VDD18)</sub> | 0.474 ×<br>V <sub>(VDD18)</sub> | 0.792                              | 71.5                                  | 56.2                  | 0x36                                         | 0x36  |

| 4   | 0.525 ×<br>V <sub>(VDD18)</sub> | 0.559 ×<br>V <sub>(VDD18)</sub> | 0.592 ×<br>V <sub>(VDD18)</sub> | 0.995                              | 78.7                                  | 97.6                  | 0x38                                         | 0x38  |

| 5   | 0.642 ×<br>V <sub>(VDD18)</sub> | 0.673 ×<br>V <sub>(VDD18)</sub> | 0.704 ×<br>V <sub>(VDD18)</sub> | 1.202                              | 39.2                                  | 78.7                  | 0x3A                                         | 0x3A  |

| 6   | 0.761 ×<br>V <sub>(VDD18)</sub> | 0.792 ×<br>V <sub>(VDD18)</sub> | 0.823 ×<br>V <sub>(VDD18)</sub> | 1.420                              | 25.5                                  | 95.3                  | 0x3C                                         | 0x3C  |

| 7   | 0.876 ×<br>V <sub>(VDD18)</sub> | V <sub>(VDD18)</sub>            | V <sub>(VDD18)</sub>            | 1.8                                | 10.0                                  | OPEN                  | 0x3D                                         | 0x3D  |

### 2. Ensure devices are in correct mode by checking the MODE.

- a. As shown in Table 3, the DS90UB953-Q1 can operate in one of many different modes that define the clocking the 953. The default mode is selected by the bias voltage applied to the MODE pin (21) during power up. To set this voltage, a potential divider between VDD and GND is used to apply the appropriate bias. TI recommends that this potential divider should be referenced to the potential on the VDDD pin (25). After power up, the MODE can be read or changed through register access. On the 953, register 0x03 controls MODE\_SEL.

- b. As shown in Table 4, the DS90UB954-Q1 can operate in many different modes that define the expected imager data format. Mode is defined on power up through a voltage divider to the Mode pin (37). While the 954 can be placed in different modes, the only compatible mode with the 953 is the CSI-2 Mode. After power up, the mode can be controlled by the first 2 bits of the PORT\_CONFIG register with address of 0x6D.

- c. The most common deserializer mode configuration for a 954 and 953 system is to use a CSI-2 port and a coaxial cable between the devices. As a result, a pullup resistor of 78.7 k $\Omega$ , a pulldown resistor of 97.6 k $\Omega$ , and 1.8 V for VDD are used.

Basic Design Rules

| MODE<br>NO. | V <sub>TAF</sub>           | RGET VOLTAGE RAI           | NGE                        | V <sub>TARGET</sub> STRAP<br>VOLTAGE | SUGGESTED ST<br>(1%    |                       |                                                                                                                                              |

|-------------|----------------------------|----------------------------|----------------------------|--------------------------------------|------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|             | RATIO MIN                  | RATIO TYP                  | RATIO MAX                  | (V); V <sub>(VDD)</sub> = 1.8<br>V   | R <sub>HIGH</sub> (kΩ) | R <sub>LOW</sub> (kΩ) | DESCRIPTION                                                                                                                                  |

| 1           | 0.000                      | 0.000                      | 0.133                      | 0.000                                | OPEN                   | 10                    | CSI-2<br>Synchronous<br>mode – FPD-<br>Link III Clock<br>reference<br>derived from<br>deserializer 2                                         |

| 2           | 0.288 × V <sub>(VDD)</sub> | 0.325 × V <sub>(VDD)</sub> | 0.367 × V <sub>(VDD)</sub> | 0.586                                | 75                     | 35.7                  | CSI-2 Non-<br>synchronous<br>CLK_IN – FPD-<br>Link III Clock<br>reference<br>derived from<br>external clock<br>reference input<br>CLK_IN pin |

| 3           | 0.412 × V <sub>(VDD)</sub> | 0.443 × V <sub>(VDD)</sub> | 0.474 × V <sub>(VDD)</sub> | 0.792                                | 71.5                   | 56.2                  | CSI-2 Non-<br>synchronous<br>AON – FPD-<br>Link III Clock<br>reference<br>derived from<br>internal AON<br>clock.                             |

## Table 3. DS90UB953-Q1 Strap Configuration Mode Select

## Table 4. DS90UB954-Q1 Strap Configuration Mode Select

| MODE<br>NO. | V <sub>TAR</sub> | GET VOLTAGE RA                                            | NGE           | V <sub>TARGET</sub> STRAP<br>VOLTAGE | SUGGESTED STF<br>(1% T |                       | RX MODE |

|-------------|------------------|-----------------------------------------------------------|---------------|--------------------------------------|------------------------|-----------------------|---------|

|             | V <sub>MIN</sub> | V <sub>MIN</sub> V <sub>TYP</sub> TARGET V <sub>MAX</sub> |               | (V); VDD1P8 =<br>1.8 V               | R <sub>HIGH</sub> (kΩ) | R <sub>LOW</sub> (kΩ) |         |

| 0           | 0                | 0                                                         | 0.131 × VDD18 | 0                                    | OPEN                   | 10                    | CSI     |

| 1           | 0.525 × VDD18    | 0.559 × VDD18                                             | 0.592 × VDD18 | 0.995                                | 78.7                   | 97.6                  | CSI     |

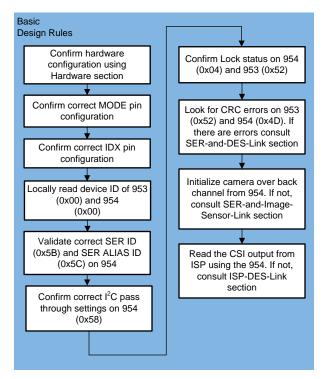

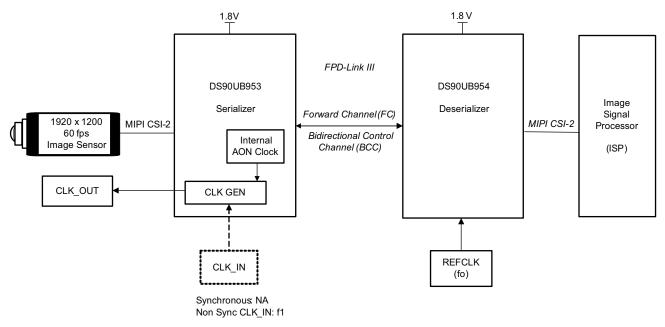

## 2.1.1 REF Clock, CLK IN, AON and Frequency Selection

## Figure 3. Clocking System Diagram

The DS90UB953-Q1 supports two different clocking schemes controlled by the MODE pin and MODE\_SEL register, 0x03. They are the synchronous and non-synchronous CLK\_IN.

## 2.1.1.1 Synchronous Mode

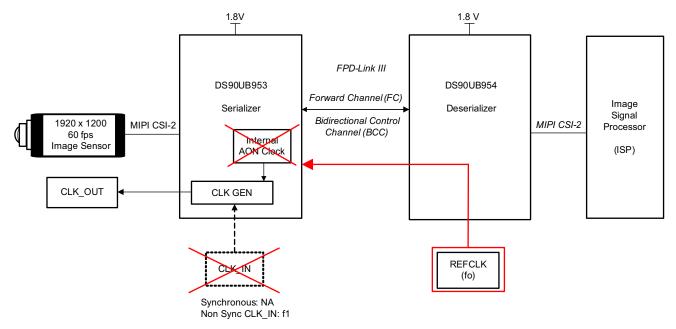

### Figure 4. Illustration of Synchronous Clocking

The first mode, synchronous, is an internally generated clock. This clock reference is extracted from back channel on the bidirectional communications link, and the internal PLLs take the extracted signal to generate the required clocks. This allows multiple cameras within a system to operate in the same clock domain and allows more space on the PCB. As shown in Figure 4, REFCLK (f0) is input signal on the deserializer that is required for precise frequency operation. Refer to the REFCLK section in the 954 data sheet for more information. The RECLK specifications for the 953 states that REFCLK must range from 24 to 26 MHz, and this signal sends *two bits* across the back channel: high and low. As a result, multiply the REFCLK frequency by two when calculating the BC and FC rate. This is summarized in Table 5.

#### Basic Design Rules

www.ti.com

## 2.1.1.2 Non-Synchronous CLK\_IN Mode

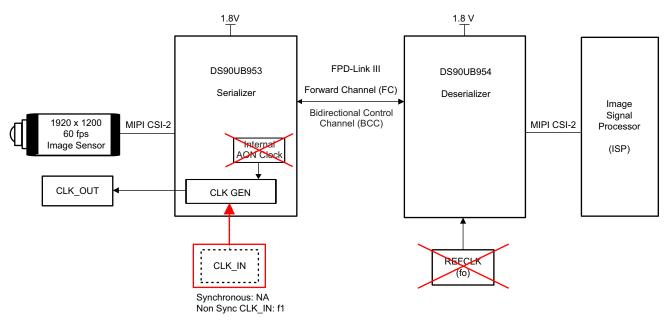

## Figure 5. Illustration of Non-Synchronous Mode With External Oscillator

The second mode, non-synchronous CLK\_IN, uses an external oscillator as a reference and generates the required clock for the FPD forward channel for that reference. Referring to Figure 5, the external clock must be fed into the CLK\_IN pin (20) on the 953, running at a constant rate (f1) proportional to the REFCLK (f0), and a BC rate is then programmed to be less than or equal to 10 Mbps. Register 0x05, GENERAL\_CFG, on the 953 holds parameters for the PLL clock control. Bits [6:4] of this register control the CLKIN divider. The CLKIN Divider can be divided by 1 or 2 by assigning these bits to 0b000 or 0b001, respectively. This division must be accounted for when calculating the FC rate which is shown in Table 5.

## 2.1.1.3 Non-Synchronous AON Mode

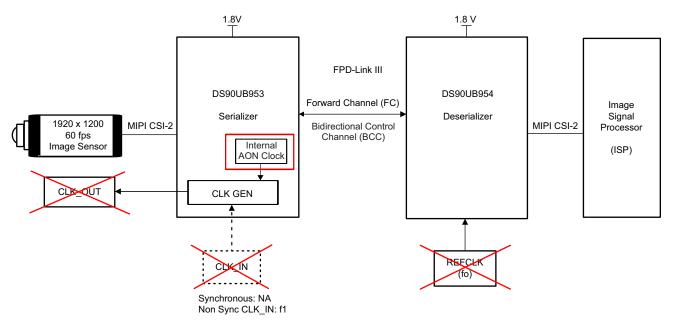

## Figure 6. Illustration of Non-Synchronous Mode With Always on Clock (AON)

The third mode, non-synchronous internal clocking mode, the serializer uses the internal Always on Clock (AON) as the reference clock for the forward channel. The OSCCLK\_SEL select must be asserted 0x05[3]=1 to enable maximum data rate when using internal clock mode, and the CLK\_OUT function is disabled. A separate reference is provided to the image sensor or ISP. When in CSI-2 mode, the CSI-2 interface may be synchronous to this clock. The CSI-2 rate must be lower than the line rate. For example, with the internal clock of 24.2 MHz the FPD-Link III forward channel rate is 3.872 Gbps, the CSI-2 throughput must be  $\leq$  3.1 Gbps (See Table 5).

## 2.1.1.4 CSI Throughput

When calculating CSI throughput, it is important to account for the extra 8 bits in the 40-bit forward channel payload that are used for redundancy, parity, check sum, DC balancing, embedded clock, control, and error checking. A normal CSI payload is 32 bits, and adding these 8 bits will reduce the actual amount of data that is transferred. This is why 4.16 Gbps of data transfer is actually a maximum of 3.32 Gbps of CSI throughput.

Because there are four data lanes available, the maximum value of CSI throughput per lane is calculated as 832 Mbps after dividing the maximum possible CSI throughput by 4. Even if two lanes in use, the maximum throughput is still divided 4. As a result, the maximum CSI throughput is 832 Mbps, regardless of how many lanes are used. Note that this is a limitation of the serializer and not the deserializer. This information is found in Table 5.

## 2.1.1.5 Clocking and Frequency Selection Example

Using the correct resistor divider values at the MODE pin, the device will power up in synchronous mode. REFCLK (f0) is 25 MHz, which is the recommended value. Use Table 5 for reference. To calculate the CLK\_OUT, see Section 4.2.

### 954 Back Channel Bit Rate:

| BC Rate = $2(f_0) = 2(25M) = 50$ Mbps | (1) |

|---------------------------------------|-----|

| 953 Forward Channel Bit Rate:         |     |

FC Rate =  $2 \times 80(f_0) = 160(25M) = 4$  Gbps

(2)

## 953 CSI Throughput:

| CSI Throughput = $2 \times 80(f_0) \times (32/40) = 160(25M) \times (32/40) = 3.2$ Gbps | (3) |

|-----------------------------------------------------------------------------------------|-----|

|-----------------------------------------------------------------------------------------|-----|

### CSI Throughput per Lane:

$$\frac{\text{CSI Throughput}}{\text{Lane}} = \frac{2 \times 80(f_0) \times (32/40)}{4} = \frac{160(25\text{M}) \times (32/40)}{4} = 800 \text{Mbps}$$

(4)

| MODE               | 953 CLK_IN<br>(MHz) | 954<br>REFCL<br>K (MHz) | 954 BC<br>RATE<br>(Mbps) | 953 FORWARD<br>(FC) RATE<br>(Mbps) | 953 CSI<br>THROUGHPUT            | MAX CSI<br>THROUGHPUT | MAX<br>CSI/LANE | CLK_OUT                     |

|--------------------|---------------------|-------------------------|--------------------------|------------------------------------|----------------------------------|-----------------------|-----------------|-----------------------------|

| Synchronous        | NA                  | fo                      | 2 × fo                   | fo × 160                           | ≤ fo × 160 ×<br>32/40            | 3.32 Gbps             | 832 Mbps        | FC / HS_CLK_DIV) ×<br>(M/N) |

| Non Sync<br>CLK_IN | f1 /<br>CLKIN_DIV   | – NA 10 M               | 10 Mbps                  | f1 × 80                            | ≤ f1 × 80 × 32/40                | 3.32 Gbps             | 832 Mbps        | FC / HS_CLK_DIV) ×<br>(M/N) |

|                    | f2 /<br>CLKIN_DIV   |                         |                          | f2 × 40                            | $\leq f2 \times 40 \times 32/40$ | 3.32 Gbps             | 832 Mbps        | FC / HS_CLK_DIV) ×<br>(M/N) |

| Non Sync<br>AON    | NA                  | NA                      | 10 Mbps                  | f3 × 80                            | ≤ f3 × 80 × 32/40                | 3.32 Gbps             | 832 Mbps        | N/A                         |

### Table 5. Mode Clock Calculation Table

### Table 6. Mode Clock Settings With Descriptions of fo and f1

|    | POSSIBLE RANGE (MHz) | DIVIDE            |

|----|----------------------|-------------------|

| fo | 24 to 26             | N/A               |

| f1 | 25 to 52             | for CLKIN_DIV = 1 |

| Table 6. Mode Clock Settings with Descriptions of to and 11 (continued) |                      |                                      |  |  |

|-------------------------------------------------------------------------|----------------------|--------------------------------------|--|--|

|                                                                         | POSSIBLE RANGE (MHz) | DIVIDE                               |  |  |

| f2                                                                      | 50 to 104            | for CLKIN_DIV = 2                    |  |  |

| f3                                                                      | 48.4 to 51           | for CLKIN_DIV = 1, OSCCLK_SEL<br>= 1 |  |  |

## Table C. Made Cleak Cattings With Descriptions of to and fd (captings)

#### 2.2 Successful PC Communication With 953 and 954

## 1. Read Device ID of derserializer and serializer locally.

- On both the 953 and 954, register 0x00 contains the I2C\_DEVICE\_ID that is necessary for I<sup>2</sup>C communication. Communicating locally does not require transactions across the bidirectional control channel (BCC), which means I<sup>2</sup>C commands are made directly to the device.

- Using the device ID that is established by the IDX pin, use a read command to access the value in . register 0x00. If the correct value is returned then communication to the device was received. If the value returned was different than expected, see Section 2.1 about verifying the IDX pin. If the value returned was zero, then communication to the device may not be functioning properly.

- The Python code used in Analog Launch Pad (ALP) for this operation is represented below where the 954\_ID is the 8-bit address assigned by the IDX pin, 0x00 is the address where the read will occur, and 1 is number of bytes returned after the read command occurs:

board.Readl2C(954\_ID,0x00,1)

## 2. Verify that the deserializer and serializer are locked.

The LOCK status serves the purpose of validating the link integrity of the connection between the SER and DES. When the LOCK status is high, the PLL in the DES is locked and validates the data and clock recovered from the serial input.

Note that the deserializer and serilaizer may not be locked in the beginning stages of bringing up the system. As a result, continue to check the basic design rules and verify that they are correct.

On the 954, the DEVICE STS can be found in register 0x04. Bit [2] holds the lock status of the device. In addition to the lock status, the device status holds many status flags regarding the reference clock, pass, power-up initialization, and check sum configuration. A healthy link between the SER and DES is indicated by the value 0xCF.

### 3. Read the Device ID of serializer using the deserializer.

- After using  $I^2C$  locally and verifying a lock between devices, the next step is to send a transaction over the BCC and verify that it works. A basic way to do this is to read the SER ID using the DES which is found in register 0x5C on the 954.

- To read the device ID of the SER from the DES, the Alias ID must be used for I<sup>2</sup>C transactions. Simply reading register 0x00 of the SER Alias ID should return the value set by the IDX pin. For more information about aliasing, see Section 2.2.1.

#### 2.2.1 Aliasing

Device Alias ID refers to the alternate 7-bit address assigned to either the serializer, deserializer, or remote slave. The Device Alias can help differentiate devices that have the same Device ID or physical I<sup>2</sup>C address. TI recommends that the I<sup>2</sup>C master always use the device alias to communicate with a remote I<sup>2</sup>C slave.

For example, the DS90UB954-Q1 can support two serializers like the DS90UB953-Q1. If both serializers are 953s that house the same camera, the device IDs and default alias IDs for the corresponding devices will be the same. As a result, the best practice is to write a unique alias ID to each device. Note that these conventions only apply when the I<sup>2</sup>C passthrough is enabled. Refer to Section 2.3 on I<sup>2</sup>C passthrough for more information.

I<sup>2</sup>C addresses are always 7 bits (binary). The majority of the registers on the DS90UB95x-Q1 associated with I<sup>2</sup>C addresses uses bits [7:1] for the address, and bit 0 is either reserved or used for some other purpose. Therefore, while loading an address value to a specific register, it is always left-shifted by 1 bit. For example, 0x50 (101 0000) left-shifted by 1 bit is 0xA0 (1010 0000). This operation can be represented as, 0x50<<1 which is equal to 0xA0.

#### Table 7. Bit Description of SER\_ALIAS\_ID Register With Example

| ADDR. | 0x5C[7:1]           | 0x5C[0]                                      |

|-------|---------------------|----------------------------------------------|

| Bits  | 101 0000            | 0                                            |

| Dec.  | Remote SER Alias ID | Automatically Acknowledges I2C writes to SER |

If a defined alias ID does not follow this convention, problems can arise. For example, register 0x5C on the 954 holds the SER\_ALIAS\_ID. If bit [0] of the 8-bit address is set to 1, transactions using this alias ID will be automatically acknowledged. As a result, the controller (or master) sends the slave address and does not listen for a response from the slave when communicating with the serializer on the bus. All writes are attempted regardless of the forward channel lock state or status of the remote Serializer Acknowledge. This can be problematic when validating the link between the SER and DES.

## 2.2.2 Port Selection on 954

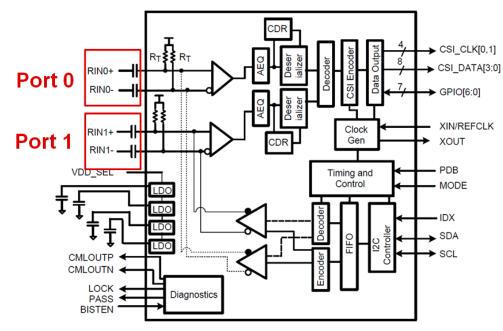

Figure 7. Illustration of Two Ports

The DS90UB954-Q1 has two ports (Port 0 and Port 1) that allow the user to interface two serializers—and subsequently, two image sensors—with one 954. As a result, the entire register space for Port 0 is similar but independent to Port 1. Therefore, the port must be accounted for when doing read or write commands to registers on the 954.

The FPD3\_PORT\_SEL register, with address of 0x4C, has the ability to control which port is read and which port has permission to write. Specifically, bit [4] controls which port is read where 0 indicates that read commands access port 0 and 1 indicates that read commands access port 1. Finally, bits [1] and [0] control write permissions for port 1 and port 0, respectively. Any combination of RX port registers can be written simultaneously. This is summarized in Table 8.

Broadcast mode refers to writing both to the port 0 and port 1 serializers simultaneously. This can achieved by defining both alias IDs to be the same and enabling writes to both ports.

Basic Design Rules

www.ti.com

| ADDR. | 0x4C[7:5]                                       | 0x4C[4]                        | 0x4C[3:2] | 0x4C[1:0]                               |

|-------|-------------------------------------------------|--------------------------------|-----------|-----------------------------------------|

| Bits  | 0X0                                             | Х                              | 00        | XX                                      |

| Desc. | Holds physical port number<br>and reserved bits | Determines which port is read. | Reserved  | Enables writes for Port 1<br>and Port 0 |

## 2.3 I2C Passthrough Verification

The Bidirectional Control Channel Configuration register is located on the 954 and holds I2C passthrough and back channel controls. Respectively, bits [6] and [7] enable I2C passthrough and I2C passthrough all. I2C passthrough controls the way that I2C commands are mapped through the BCC. The BCC\_CONFIG register has the address of 0x58.

I2C passthrough, bit [6] of 0x58, allows communication to slaves (SER) and remote slaves (image sensor) using their alias ID. As a result, it is not possible to communicate to the SER using its device ID defined by the IDX pin. See Section 2.2.1 for more information.

**NOTE:** TI recommends enabling this bit for normal operation of the 953 and 954 system.

I2C passthrough all, bit [7] of 0x58, allows communication to slave devices using their alias ID or device ID.

**NOTE:** Communication with remote slaves is not ensured while this bit is enabled. This setting should not be used except for debugging purposes or for certain situations where data must be sent in a critical timing window and an acknowledgment (ACK) is not required during the I2C communication.

A summary of these settings are shown in Section 3.2.3.

| I2C                            |                                    | COMMUNICATE WITH             | ENSURED                   |                                                                 |

|--------------------------------|------------------------------------|------------------------------|---------------------------|-----------------------------------------------------------------|

| PASSTHROU<br>GH BIT<br>0x58[6] | I2C PASSTHROUGH ALL BIT<br>0x58[7] | WITHOUT SER ALIAS<br>DEFINED | WITH SER ALIAS<br>DEFINED | COMMUNICATION WITH<br>REMOTE SLAVE WITH<br>ALIAS AND ID DEFINED |

| 1                              | 0                                  | No                           | Yes                       | Yes                                                             |

| 1                              | 1                                  | Yes                          | Yes                       | No                                                              |

| 0                              | 1                                  | Yes                          | Yes                       | No                                                              |

| 0                              | 0                                  | No                           | No                        | No                                                              |

## 2.4 Basic Diagnostic and Error Registers

This section discusses the various errors and registers used in 953 and 954 systems. Various errors will be presented and discussed using basic definitions. The various registers pertaining to the errors are found in the tables below. More information regarding these registers can be found in the data sheet.

**Parity Errors:** Parity errors refer to errors that occur over the forward channel. These errors are caused by irregular changes to data, as it is recorded when it is entered in memory. Note that these errors only have to do with the link between the SER and DES (found in Section 3), which means they are independent of CSI errors. Check addresses 0x55, 0x56, and 0x4D on the 954.

**Cyclic Redundancy Check (CRC) Errors:** CRC errors refer to errors that occur over the back channel. These errors are caused by accidental changes to the data. The redundancy in the transmitted data is checked and flagged. Note that these errors only have to do with the link between the SER and DES (found in Section 3), which means they are independent of CSI errors. Check addresses 0x4D on the 954 and 0x55 and 0x56 on the 953.

**BIST CRC Errors:** BIST CRC Errors refer to errors generated during the Built-In Self Test (BIST) between the 954 and 953. Note that these errors only have to do with the link between the SER and DES (found in Section 3), which means they are independent of CSI errors. For more information about BIST, refer to Section 3.2. Check addresses.

**CSI Errors:** CSI errors refer to errors in CSI data packets. These can be Checksum, Length, or ECC errors. CSI errors can occur across any of the links, however, they usually occur when designing the link between the DES and ISP (found in Section 5) is designed.

**CSI Checksum Errors:** CSI Checksum errors refer to an error detected in the packet data portion of the CSI packet.

**CSI Length Errors:** CSI length errors refer to an error detected in expected packet length. Packet length errors occur if the data length field in the packet header does not match the actual data length for the packet.

**CSI Error Correcting Code (ECC) Errors:** CSI ECC errors refer to errors in CSI data packets that are 1 or 2 bits off from their correct value. Errors that are 1 bit, are automatically corrected while errors that are 2 bits are detected but not corrected.

**FPD III Encoder Error:** FPD III Encoder error refers to errors in the FPD-Link III encoding that has been detected by the receiver. These are also tied to the Link error count and Link error threshold.

Buffer Error: Buffer errors refer to the overflow condition that has occurred on the packet buffer FIFO.

| DEVICE | REGISTER NUMBER | REGISTER NAME    | REGISTER DESCRIPTION                                                                                                                                                                               |

|--------|-----------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 954    | 0x04            | DEVICE_STS       | General flags of device status and<br>communication between DES and SER:<br>check sum config, power up<br>initialization, refclk valid, pass, lock                                                 |

| 954    | 0x05            | PAR_ERR_THOLD_HI | Parity error threshold high byte that<br>provides 8 most bits of threshold value.<br>Flagged in RX_PORT_STS1                                                                                       |

| 954    | 0x06            | PAR_ERR_THOLD_LO | Parity error threshold low byte that<br>provides 8 most bits of threshold value.<br>Flagged in RX_PORT_STS1                                                                                        |

| 954    | 0x4D            | RX_PORT_STS1     | Flags for various detected errors: BCC<br>CRC error, Lock status Change, BCC<br>sequencing error, Parity Error, Pass,<br>and Lock                                                                  |

| 954    | 0x4E            | RX_PORT_STS2     | Flags for various detected errors: Line<br>Length Unstable, Line Length changed,<br>FPD3 Encoder error, packet buffer error,<br>CSI Error, frequency stable, FPD3 CLK<br>detect, Line count change |

| 954    | 0x55            | RX_PAR_ERR_HI    | 8 MSBs of FPD3 Parity Errors                                                                                                                                                                       |

| 954    | 0x56            | RX_PAR_ERR_LO    | 8 LSBs of FPD3 Parity Errors                                                                                                                                                                       |

| 954    | 0x57            | BIST_ERR_COUNT   | Returns BIST error count                                                                                                                                                                           |

| 954    | 0x7A            | CSI_RX_STS       | Has general flags for CSI errors: Packet length, check sum, 2-bit ECC, 1-bit ECC                                                                                                                   |

| 954    | 0x7B            | CSI_ERR_COUNTER  | Returns counts number of CSI packets received with errors                                                                                                                                          |

| 954    | 0xB9            | LINK_ERROR_COUNT | Enables serial link data integrity error<br>count, link error count threshold, and<br>waiting for SFLITER to stabilize                                                                             |

| 954    | 0xD0            | PORT_DEBUG       | Indicates SER is in BIST mode. If not<br>SER is not in BIST and bit [5] is high,<br>could indicate error                                                                                           |

| 954    | 0x24            | INTERRUPT_STS    | If interrupt enabled, flags when and<br>where interrupts occurred: global<br>interrupt, CSI Transmit port 0, RX port 1<br>and port 0                                                               |

Table 10. DS90UB954-Q1 Registers Used for Diagnostics and Checking Errors

| Table 10. DS90UB954-Q1 Registers Used for Diagnostics and Checking Errors (continued) |

|---------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------|

| DEVICE | REGISTER NUMBER | REGISTER NAME                                                | REGISTER DESCRIPTION                                                                           |

|--------|-----------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 954    | 0x36-0x37       | CSI_TX_ICR, CSI_TX_ISR                                       | Detects CSI RX errors and enables<br>interrupts if necessary                                   |

| 954    | 0xD8-0xDB       | PORT_ICR_LO, PORT_ICR_HI,<br>PORT_ISR_HI, and<br>PORT_ISR_LO | Interrupts on various errors: see the 954<br>data sheet register table for more<br>information |

## Table 11. DS90UB953-Q1 Registers Used for Diagnostics and Checking Errors

| DEVICE | REGISTER NUMBER | REGISTER NAME    | REGISTER DESCRIPTION                                                                                                        |

|--------|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 953    | 0x49            | BC_CTRL          | Back channel control used for clearing<br>CRC and BIST errors and TX-RX link<br>detect timer value                          |

| 953    | 0x52            | GENERAL_STS      | General flags that indicate status of<br>errors (BCC, BIST CRC, CRC, Link<br>Lost) and communication between<br>DES and SER |

| 953    | 0x54            | BIST_ERR_CN1     | 8 bits that count the CRC errors in<br>BIST mode                                                                            |

| 953    | 0x55            | CRC_ERR_CNT1     | CRC Error count (LSB)                                                                                                       |

| 953    | 0x56            | CRC_ERR_CNT2     | CRC Error count (MSB)                                                                                                       |

| 953    | 0x5C            | CSI_ERR_CNT      | Counts number of CSI packets<br>received with errors since the last read<br>of the counter                                  |

| 953    | 0x5D            | CSI_ERR_STATUS   | Shows Line Length mismatch, Check<br>sum error, ECC 2-bit error detected,<br>ECC 1-bit Error Detect                         |

| 953    | 0x5E            | CSI_ERR_DLANE01  | Shows errors for lanes 0 and 1: single<br>bit error in sync, multi error in sync,<br>control error in HS request Mode       |

| 953    | 0x5F            | CSI_ERR_DLANE23  | Shows errors for lanes 2 and 3: single<br>bit error in sync, multi error in sync,<br>control error in HS request Mode       |

| 953    | 0x60            | CSI_ERR_CLK_LANE | CLK Lane: control error in HS request<br>mode, Invalid LP state detected                                                    |

| 953    | 0x79            | BCC_STATUS       | Error flags over BCC: master timeout,<br>slave error, slave time out, and SER<br>Response                                   |

| 953    | 0x77            | ECC_ERR_SEL      | Choose to force many different ECC<br>errors                                                                                |

## 3 Designing the Link Between SER and DES

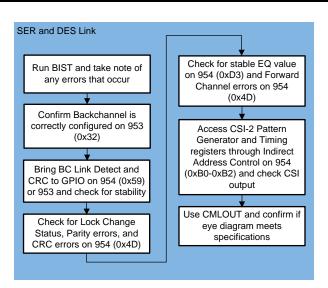

The link between the 953 and 954 is a core link that ensures proper communication between devices. Considering back channel configuration, BIST, AEQ, CML, and internal pattern generation will ensure that the link between the SER and DES is functional.

Figure 8. Flowchart for SER and DES Link

## 3.1 Back Channel Configuration

As shown in Section 2.1.1, the 953 is compatible with certain back channel frequencies. Furthermore, the 954 has the ability to adjust the back channel frequency to be compatible with the connected device. The process for changing the back channel configuration is shown below:

- 1. On the 954, configure the back channel frequency select for 953 compatibility using the BCC Configuration register.

- The BCC\_CONFIG register can be found at the 0x58 address. This register has the settings for I2C passthrough, which is explained in Section 2.3, as well as the BC frequency selector. By setting bits [2:0] to 0b110, the back channel will be set to the 953 default rate of 50 Mbps.

- Note that DS90UB913A-Q1 and DS90UB933-Q1 have different defaults for back channel rates. As a result, they can be adjusted accordingly. See the 954 data sheet in the BCC\_CONFIG register description for more information.

#### Designing the Link Between SER and DES

www.ti.com

| PAGE | ADDR<br>(HEX) | REGISTER NAME | BIT(S) | FIELD                             | TYPE            | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                |

|------|---------------|---------------|--------|-----------------------------------|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |               |               | 7      | I2C<br>PASSTH<br>ROUGH<br>ALL     | RW              | 0       | I2C Passthrough All Transactions<br>0: Disabled<br>1: Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                |

|      |               |               | 6      | I2C<br>PASSTH<br>ROUGH            | RW              | 0       | I2C Passthrough to serializer if decode<br>matches<br>0: Passthrough Disabled<br>1: Passthrough Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                |

|      |               |               |        | 5                                 | AUTO<br>ACK ALL | RW      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Automatically Acknowledge all I2C writes<br>independent of the forward channel lock<br>state or status of the remote<br>Acknowledge<br>0: Disable<br>1: Enable |

|      |               |               | 4      | BC_ALW<br>AYS_ON                  | RW              | 1       | Back channel enable<br>0: Back channel enable requires setting<br>of either I2C_PASS_THROUGH and<br>I2C_PASS_THROUGH_ALL. This bit<br>may only be written through a local I <sup>2</sup> C<br>master.<br>1: Back channel is always enabled<br>independent of I2C_PASS_THROUGH<br>and I2C_PASS_THROUGH_ALL                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                |

| RX   | 0x58          | BCC_CONFIG    | 3      | BC CRC<br>GENERA<br>TOR<br>ENABLE | RW              | 1       | Back Channel CRC Generator Enable<br>0: Disable<br>1: Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                |

|      |               | BCC_CONFIG    | 2:0    | BC FREQ<br>SELECT                 | RW, S           | 0x0     | Back Channel Frequency Select. Default<br>value set by strap condition upon<br>asserting PDB = HIGH.<br>000: 2.5 Mbps (default for DS90UB933-<br>Q1 or DS90UB913A-Q1 compatibility)<br>001- 011: Reserved<br>100: 10 Mbps (default for CSI<br>Asynchronous back channel<br>compatibility)<br>101: 25 Mbps<br>110: 50 Mbps (default for DS90UB953-<br>Q1 CSI Synchronous back channel<br>compatibility)<br>111: 100 Mbps<br>Note that changing this setting will result<br>in some errors on the back channel for a<br>short period of time. If set over the<br>control channel, the deserializer should<br>first be programmed to Auto-Ack<br>operation to avoid a control channel time-<br>out due to lack of response from the<br>serializer. |                                                                                                                                                                |

## Table 12. Settings for Bidirectional Configuration (BCC\_CONFIG) Register 0x58 on 954

## 3.2 BIST

An optional At-Speed Built-In Self Test (BIST) feature supports testing of the high-speed serial link and the back channel without external data connections. This is useful in the prototype stage, equipment production, in-system test, and system diagnostics.

## 3.2.1 BIST Configuration and Status

The BIST mode is enabled by BIST configuration register 0xB3. The test may select either an external PCLK or the internal oscillator clock (OSC) frequency in the Serializer. In the absence of PCLK, the user can select the internal OSC frequency at the deserializer through the BIST configuration register.

When BIST is activated at the deserializer, a BIST enable signal is sent to the serializer through the Back Channel. The serializer outputs a continuous stream of a pseudo-random sequence and drives the link at speed. The deserializer detects the test pattern and monitors it for errors. The serializer also tracks errors indicated by the CRC fields in each back channel frame. While the lock indications are required to identify the beginning of proper data reception, for any link failures or data corruption, the best indication is the contents of the error counter in the BIST\_ERR\_COUNT register 0x57 for each RX port.

## 3.2.2 BIST Procedure

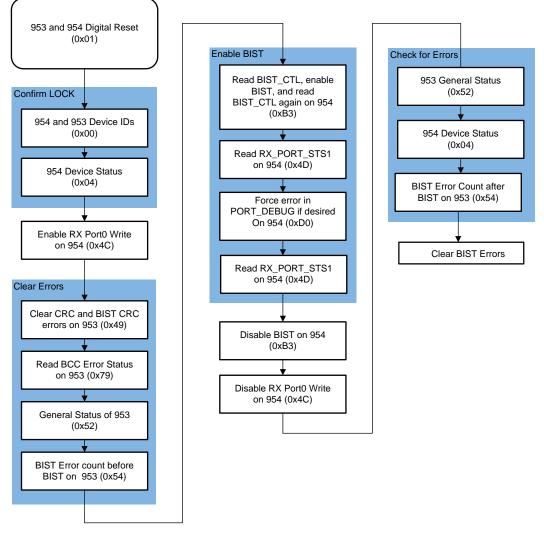

Figure 9. BIST Script Flowchart

The following steps will explain how BIST is conducted between the DS90UB953-Q1 and DS90UB954-Q1. After basic rules have been followed, BIST will determine the health of the link between the SER and DES only. Example code is listed in Section 7.1.1 and a list of registers used in the code is shown in Table 16 and Table 17.

| ADDR. | 0x01[7:3] | 0x01[2]               | 0x01[1]                           | 0x01[0]                        |

|-------|-----------|-----------------------|-----------------------------------|--------------------------------|

| Bits  | XXX       | Х                     | 0                                 | 1                              |

| Desc. | Reserved  | Restart ROM Auto-Load | Digital reset including registers | Digital reset except registers |

## Table 13. RESET\_CTL Register Description on 953

How to Design a FPD-Link III System Using DS90UB953-Q1 and DS90UB954-Q1

# 1. Use the reset register to reset the entire digital block and set the serializer (SER) and deserializer (DES) to a known state.

- Register 0x01 is the RESET\_CTL register on both the 953 and 954.

- Note that bit [0] in REST\_CTL does not reset the registers. Bit [1] controls the digital reset responsible for clearing registers. Generally, it is better to conduct a digital reset without clearing the registers to save time initial troubleshooting steps.

| ADDR. | 0x04[7]                             | 0x04[7]                                | 0x04[7]  | 0x04[7]      | 0x04[7]     | 0x04[7]     | 0x04[1:0] |

|-------|-------------------------------------|----------------------------------------|----------|--------------|-------------|-------------|-----------|

| Bits  | Х                                   | Х                                      | Х        | Х            | 1           | 1           | XX        |

| Desc. | Configuration<br>Checksum<br>Passed | Power-up<br>Initialization<br>Complete | Reserved | REFCLK Valid | PASS Status | LOCK Status | Reserved  |

## Table 14. DEVICE\_STS Register Description on 954

| Table 15 GENERAL | STATUS Register Description for Lock on 953 |  |

|------------------|---------------------------------------------|--|

|                  | OTATOO REGISTER DESCRIPTION TO LOCK ON 555  |  |

| ADDR. | 0x52[7]  | 0x52[6]        | 0x52[5]  | 0x52[4]      | 0x52[3]                | 0x52[2]                            | 0x52[1]              | 0x52[0]             |

|-------|----------|----------------|----------|--------------|------------------------|------------------------------------|----------------------|---------------------|

| Bits  | X        | 1              | Х        | Х            | Х                      | 1                                  | Х                    | 1                   |

| Desc. | Reserved | LOCK<br>Status | Reserved | BC Link lost | BIST Error<br>detected | FC High-<br>speed lock<br>detected | BC error<br>detected | BC Link<br>detected |

# 2. Confirm that SER and DES are locked by accessing the respective devices IDs and DES device status.

- As mentioned before, verifying the correct SER and DES device IDs indicates that the correct DES device ID and SER alias ID is used when making I2C commands. The DEVICE\_ID for both devices can be found in register 0x00 while the SER\_ALIAS\_ID can be found on the deserializer in register 0x5C.

- The DES device status will indicate if the LOCK status is high. As mentioned before, the LOCK status serves the purpose of validating the link integrity of the connection between the SER and DES. When the LOCK status is high, the PLL in the DES is locked and validates the data and clock recovered from the serial input. As a result, the value should be 0xCF. DEVICE\_STS on the 954 can be found in register 0x04.

## 3. Enable the write permission for RX Port0.

- On the DES, this bit allows data to be written to RX port 0 registers. Any combination of RX port

registers can be written simultaneously. This applies to all paged FPD3 Receiver port registers.

Remember, configuring parameters that pertain to RX port 0 registers require a write command. If

permission to write RX port 0 is not given, then register values will not be changed even with

correct write commands. The FPD3\_PORT\_SEL can be found in register 0x4C.

- 4. On the SER, clear any previous errors in the system before enabling BIST by clearing the CRC errors and BIST CRC errors in addition to reading the BCC status and SER general status.

- BIST CRC errors and CRC errors are cleared to ensure that the next BIST test only includes errors from the specified test. These errors are housed in the BC\_CTRL register located at 0x49 on the 953. Value 0x28 selects the self-clearing bits to clear the BIST CRC and CRC errors.

- Reading the bidirectional control channel (BCC) status has two functions. First, if there are any errors that occurred over the BCC, they may be flagged and categorized in this register. Second, reading this register may clear a flag that is raised in the SER general status register that can only be cleared when the BCC status register is read. The BCC\_STATUS register is located at 0x79 on the 953.

- The general status of the SER holds indicators for many different types of errors, including BIST CRC ERR and the RX LOCK DETECT. Verifying its value before BIST will show the changes that occur after BIST. A typical general status will indicate the value 0x45 showing that RX Lock Detect, HS PLL Lock, and Link Detect flags are high. GENERAL\_STS can be found at register 0x52 on the 953.

#### 5. Read the BIST error counter before BIST.

- In addition to checking the indicator if an error occurred, it is important to read the number errors before the test. If one error is forced, we expect this value to be 0x01 after the BIST has completed. The BIST\_ERR\_CNT can be found in register 0x54 of the 953.

- 6. On the DES, read the BIST control register, enable the BIST, force the singular, multiple, or no errors, and read the RX port status after the BIST starts and before the BIST ends.

- The BIST control register enables the BIST as well as various parameters important for BIST. Bit

[0] of the BIST control represents BIST\_EN. Reading it before and then after enabling BIST helps

show that BIST has been enabled. By using the sleep command, BIST can run as long as the user

desires. BIST\_CTL can be located in register 0xB3 of the 954.

- The RX port status, like the general status and BCC status on the 954, houses many useful error flags. These flags include: the BCC CRC error, lock status change, BCC sequence error, parity error, receiver pass indication, lock status, and locked to recovered clock status. Consider bit [4] which indicates the LOCK\_STS\_CHG. By reading this value right after the BIST is enabled, and right before the BIST is disabled, the user is able to tell if the lock status changed during BIST. It is important to read this register after BIST is started because enabling and disabling the BIST forces the devices to relock. RX\_PORT\_STS1 can be found in register 0x4D.

- The port debug register is used for debugging various functions by enabling build in errors or tests. Bit [0] is self-clearing and controls the FORCE\_ONE\_BC\_ERROR function. Bit [1], by comparison, controls FORCE\_BC\_ERRORS and must be cleared. This is helpful for testing the error detection of the system. The PORT\_DEBUG register can be found at 0xD0 of the 954.

#### 7. Disable the BIST and write permissions of RX Port0.

- Disabling the BIST is done through the BIST control register, 0xB3, on the DES. BIST uses all functionality of the BCC and disabling the BIST reestablishes communication between the SER and DES.

- This bit allows data to be written to RX port 0 registers. Any combination of RX port registers can be written simultaneously. This applies to all paged FPD3 Receiver port registers. Because only reads are required at this stage the BIST, it is good practice to disable the write permission. The FPD3\_PORT\_SEL can be found in register 0x4C.

### 8. Check for errors on the SER general status, DES device status, and BIST error count.

- The general status of the 953, with register value 0x52, that was checked before BIST gave a value of 0x45. With the introduction of an error, a value of 0x4D is read from the register. This value indicates that the RX Lock Detect, HS PLL Lock, Link Detect, and BIST CRC Error flags are high.

- The device status of the 954 was checked before BIST. Despite forcing an error in the system, the status should read still read 0xCF because the devices should still be LOCKED.

- Before BIST was enabled, all possible BIST CRC errors were cleared and the BIST CRC error count was read. After forcing one error during BIST, one error should be displayed in the BIST\_ERR\_CNT. If the count is 0x01, that means that the devices were LOCKED, any errors that occurred were only produced during the BIST test, the error detection system is working as intended, and the link between the SER and DES is not producing any errors.

The LOCK and PASS statuses ensure that the serializer and deserializer are communicating effectively. By using the built-in self test (BIST), the LOCK between devices can be accurately evaluated. As a result, this is a fundamental step to ensure proper design of the board.

### 3.2.3 List of Registers Used in BIST Script

| DEVICE | REGISTER NUMBER | REGISTER NAME | REGISTER DESCRIPTION                                                  |

|--------|-----------------|---------------|-----------------------------------------------------------------------|

| 954    | 0x00            | DEVICE_ID     | I <sup>2</sup> C device ID for DES. Used in I <sup>2</sup> C commands |

| 954    | 0x01            | RESET_CTL     | Responsible for digital resets and analog power down                  |

#### Table 16. DS90UB954-Q1 Registers Used in BIST Script

| ······································ |                 |                |                                                                                          |  |  |

|----------------------------------------|-----------------|----------------|------------------------------------------------------------------------------------------|--|--|

| DEVICE                                 | REGISTER NUMBER | REGISTER NAME  | REGISTER DESCRIPTION                                                                     |  |  |

| 954                                    | 0x5C            | SER_ALIAS_ID   | I <sup>2</sup> C alias ID that is used to communicate to SER from DES                    |  |  |

| 954                                    | 0x04            | DEVICE_STS     | General flags that indicate status of device<br>and communication between DES and<br>SER |  |  |

| 954                                    | 0x4C            | FPD3_PORT_SEL  | RX port register                                                                         |  |  |

| 954                                    | 0xB3            | BIST_CTL       | Various parameters important for control<br>of BIST                                      |  |  |

| 954                                    | 0x4D            | RX_PORT_STS1   | General flags that indicate various errors                                               |  |  |

| 954                                    | 0xD0            | PORT_DEBUG     | Port used for debugging various functions of DES                                         |  |  |

| 954                                    | 0x55            | RX_PAR_ERR_HI  | Shows 8 most significant bits of errors that occur on the forward channel                |  |  |

| 954                                    | 0x56            | RX_PAR_ERR_LOW | Shows 8 least significant bits of errors that occur on forward channel                   |  |  |

## Table 16. DS90UB954-Q1 Registers Used in BIST Script (continued)

## Table 17. DS90UB953-Q1 Registers Used in BIST Script

| DEVICE | REGISTER NUMBER | REGISTER NAME | REGISTER DESCRIPTION                                                                     |

|--------|-----------------|---------------|------------------------------------------------------------------------------------------|

| 953    | 0x00            | DEVICE_ID     | I <sup>2</sup> C device ID for SER. Used in I <sup>2</sup> C commands                    |

| 953    | 0x01            | RESET_CTL     | Responsible for digital resets and analog power down                                     |

| 953    | 0x49            | BC_CTRL       | Back channel control used for clearing errors and TX-RX link detect timer value          |

| 953    | 0x79            | BCC_STATUS    | Group of error flags that indicate various errors over BCC                               |

| 953    | 0x52            | GENERAL_STS   | General flags that indicate status of errors<br>and communication between DES and<br>SER |

| 953    | 0x54            | BIST_ERR_CNT  | 8 bits that count the CRC errors in BIST mode                                            |

## 3.3 AEQ

On the 954, the receiver inputs provide an adaptive equalization filter to compensate for signal degradation from the interconnect components. To determine the maximum cable reach, consider the factors that affect signal integrity such as jitter, skew, ISI, crosstalk, and so forth. The equalization status and configuration are selected through AEQ registers 0xD2–0xD3. For more in depth AEQ control, see the AEQ register with an address of 0x42.

If these register values are continuously read and the values jump sporadically, then the AEQ is not properly compensating for factors that affect signal integrity. If the deserializer loses Lock, the adaptive equalizer will reset and perform the Lock algorithm again to reacquire the serial data stream being sent by the serializer.

In addition, the AEQ values may settle to a state that is overcompensating for the factors that affect signal integrity. If the AEQ values seem to be higher than expected in the AEQ\_STATUS register (0xD3), set AEQ\_RESTART (0xD2[3]) to 1, and let the AEQ values resettle. If the system continually settles to the wrong value on power up, then reset the 954 before port forwarding is enabled.

## 3.4 CML Out

The DS90UB954-Q1 includes an internal Channel Monitor Loop (CML)-through output on the CMLOUTP/N pins 38 and 39, respectively. A buffered loop-through output driver is provided on the CMLOUTP/N to observe jitter after equalization for each of the two RX receive channels. The CMLOUT monitors the post EQ stage, thus providing the recovered input of the deserializer signal. The measured serial data width on the CMLOUT loop-through is the total jitter including the internal driver, AEQ, back channel echo, and so forth. Each channel also has its own CMLOUT monitor and can be used for debug purposes. This CMLOUT is useful in identifying gross signal conditioning issues. Typically, these pins are routed to test points and not connected. For monitoring CMLOUT, be sure to terminate with  $100-\Omega$  differential load.

For more information regarding CMLOUT, refer to the Channel Monitor Loop-Through Output Driver section in the 594 data sheet. Example code fore enabling CMLOUT FPD3 RX Port 0 is given in Section 7.1.4 while the process is given in Table 18.

|                                  | FPD-Link III RX Port 0                                                                     | FPD-Link III RX Port 1                                               |  |

|----------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|

| ENABLE MAIN LOOP-THROUGH DRIVER  | 0xB0 = 0x14; 0xB1 = 0x00; 0xB2 = 0x80 0xB1 = 0x03; 0xB2 = 0x28<br>0xB1 = 0x04; 0xB2 = 0x28 |                                                                      |  |

| SELECT CHANNEL MUX               | 0xB1 = 0x02; 0xB2 = 0x20                                                                   | 0xB1 = 0x02; 0xB2 = 0xA0                                             |  |

| SELECT RX PORT                   | 0xB0 = 0x04; 0xB1 = 0x0F;<br>0xB2 = 0x01 0xB1 = 0x10;<br>0xB2 = 0x02                       | 0xB0 = 0x08; 0xB1 = 0x0F;<br>0xB2 = 0x01 0xB1 = 0x10;<br>0xB2 = 0x02 |  |

| DISABLE MAIN LOOP-THROUGH DRIVER | 0xB0 = 0x14; 0xB1 = 0x00; 0xB2 = 0x<br>0xB1 = 0x04; 0x                                     |                                                                      |  |

| DESELECT CHANNEL MUX             | 0xB1 = 0x02; 0xB2 = 0x20                                                                   | 0xB1 = 0x02; 0xB2 = 0x20                                             |  |

| DESELECT RX PORT                 | 0xB0 = 0x04; 0xB1 = 0x0F;<br>0xB2 = 0x00 0xB1 = 0x10;<br>0xB2 = 0x00                       | 0xB0 = 0x08; 0xB1 = 0x0F;<br>0xB2 = 0x00 0xB1 = 0x10;<br>0xB2 = 0x00 |  |

## Table 18. Channel Monitor Loop-Through Output Configuration of the 954

## 4 Designing Link Between SER and Image Sensor

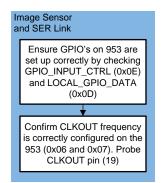

### Figure 10. Image Sensor and SER Link Design

## 4.1 Sensor Initialization Using SER GPIOs

The following steps will generally explain how the initialization of the image sensor occurs from the DS90UB953-Q1. It is important that the link between the SER and DES is working. If the link between the SER and DES is not working, then you will not be able to use the DES to talk to the SER—and subsequently—the image sensor. Example code is listed in Section 7.1.2.

In the example script, the traces on the PCB connect GPIO0 to the imager reset, GPIO1 to the imager power down, GPIO2 to the SER WP, and GPIO3 to frame sync.

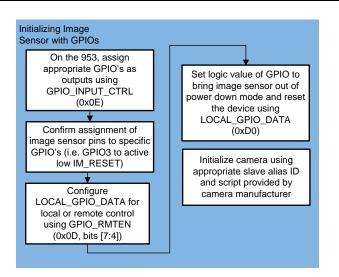

Figure 11. Flowchart for Initializing the Image Sensor Using GPIO's

- 1. On the serializer enable the appropriate General-Purpose Input/Output (GPIO) pins for output mode.

- On the serializer, GPIO\_INPUT\_CTRL controls whether GPIO0-3 are configured as inputs or outputs. The first 4 bits [3:0] control whether they are used as inputs, and the last 4 bits [7:4] are used as outputs. Because all GPIOs in this example refer to settings that can be set, all GPIOs are set to outputs. This register has the value of 0x0E.

- GPIO0 and GPIO1 on the 953 can be used for sensing the voltage applied to its input. See Section 6.8 for more information. As a result, GPIO2 and GPIO3 should be used before assigning other GPIO pins.