# DP83822 Jitter Analysis

## Aniruddha Khadye

#### **ABSTRACT**

This application note explores how clock jitter affects performance of DP83822 10/100 Industrial Ethernet PHY. The methods in this document describe how to set up a jitter measurement test bench and determine acceptable levels of clock jitter for proper operation and compliance.

#### Contents Introduction ..... 2 3 List of Figures 2 3 4 Jitter Tolerance Test Bench 5 5 6

Introduction www.ti.com

## 1 Introduction

The timing variations in signal edges from their ideal values is called Jitter. With the increase in data rates, jitter has become important factor in system design. A clock with high jitter can cause performance degradation in Ethernet subsystem such as compliance failures, high Bit Error Rate etc. Clock jitter can be caused due to factors such as thermal noise, power supply variations, loading conditions, device nosie and interference coupled from other circuit on the subsystem. Jitter can be measured and expressed in multiple ways. Important types of jitter are as follows;

- Period Jitter

- Cycle to Cycle Jitter

- · Long Term Jitter

- · Time Interval Jitter

- Phase Noise

For the purpose of this app note we will be focusing on Phase Noise.

#### 2 Phase Noise

Phase Noise is a method of describing jitter in the frequency domain. Phase noise can be described as a set of noise values at different frequency offsets or as a continuos noise plot over a range of frequencies. When a continuos noise plot is used phase noise is expressed in seconds.

An ideal clock has all the energy located at the carrier frequency. In real-life scenario, energy is leaked out over a range of frequencies on both sides of the carrier frequencies. For expressing Phase Noise it is necessary to define a start and stop frequency offset with respect to the carrier frequency. These frequency offsets are application dependent.

For the scope of this application note, phase noise will be expressed as the integrated noise from 100Hz to 20MHz offset from center frequency of 25MHz. For measuring jitter tolerance of the PHY it is required to inject controlled jitter in the reference clock and observe the effect on PHY Performance. The performance metrics for the PHY will be the 100Base-TX Transmit jitter and an optional measurement of Bit Error Rate.

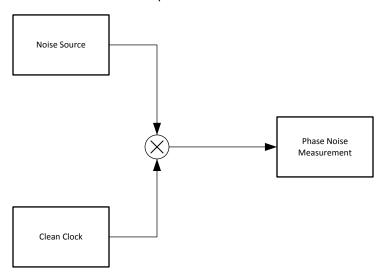

Figure 1 shows the Jitter measurement setup.

Figure 1. Clock Jitter Measurement Setup

www.ti.com Phase Noise

A clean clock is modulated with controlled amount of noise. The output is connected to a signal analyzer in Phase Noise measurement mode. The noise source can be any signal generator which can generate random noise signal. Test setup for this application note used R & S SMB100A as the clock source, Agilent 33250A as the noise source and Agilent E5052A as the phase noise measurement device. The output of 33250A is connected to SMB100A and modulation of clean clock with noise occurs within the SMB100A.

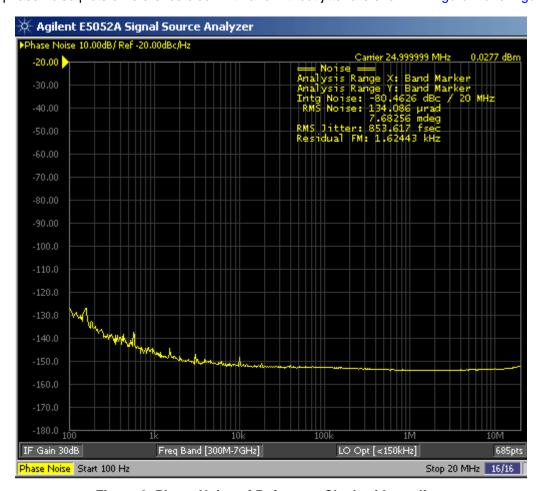

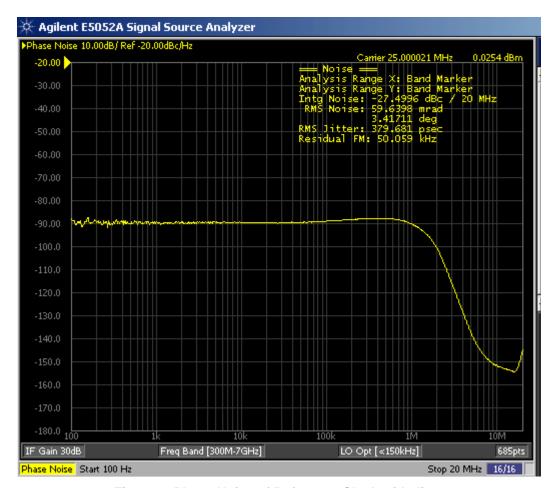

The phase noise plots of reference clock with and without jitter are shown in Figure 2 and Figure 3.

Figure 2. Phase Noise of Reference Clock without Jitter

DP83822 Jitter Tolerance www.ti.com

Figure 3. Phase Noise of Reference Clock with Jitter

## 3 DP83822 Jitter Tolerance

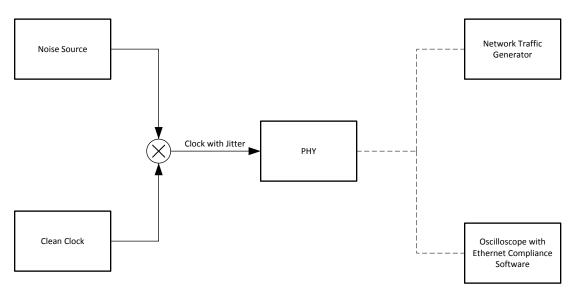

For demonstrating DP83822 jitter tolerance, a DP83822 EVM is used as Equipment Under Test (EUT). The EUT is configured to accept external reference clock (25MHz). For observing performance difference, 100Base-TX Transmit Jitter is measured at output of EUT using the Ethernet Compliance Software on TEK DPO 70804C oscilloscope and TEK P6330 Differential Probe. Bit Error Rate measurements are also conducted using SmartBits 200 chassis with SX-7405 card (Network Traffic Generator). Figure 4 shows the block diagram for Jitter Tolerance measurement.

Please note that these measurements are conducted at room temperature in lab setting on limited samples.

www.ti.com DP83822 Jitter Tolerance

Figure 4. Jitter Tolerance Test Bench

## 3.1 100Base-TX Transmit Jitter

The DP83822 is configured for generating scrambled idles and the transmit jitter is measured on the compliance software. The aim is to check at what jitter level the DP83822 fails IEEE compliance test. The procedure is explained below.

## **Equipment List**

- Agilent 33250A

- R & S AMB100A

- Tek DPO 70804C with Tek P6330 differential probe

- Agilent E5052A

- Ethernet Compliance software

- Ethernet Compliance Test Fixture TF-GBE

- Co-ax cables

#### **Procedure**

- Turn off modulation to get jitter free reference clock.

- Configure DP83822 for scrambled idles.

- Write 0x2100 to Register 0x00. This forces 100M operation.

- Write 0x0021 to Register 0x19. This force MDI mode.

- Use TC2 section of the Ethernet Compliance Test Fixture to probe Channel A of EUT using the differential probe.

- Follow the test guide for running Transmit Jitter Measurement. This test should be a pass since there

is no jitter on the clock

- Turn modulation on and repeat the measurement. Increase the amplitude of noise wave untill Transmit jitter test results in failure.

- Disconnect the Clock from the EUT and connect it to Agilent E5052A via DC Block. Record the RMS Jitter with Averaging turned on.

DP83822 Jitter Tolerance www.ti.com

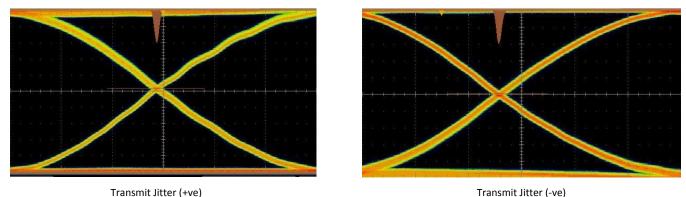

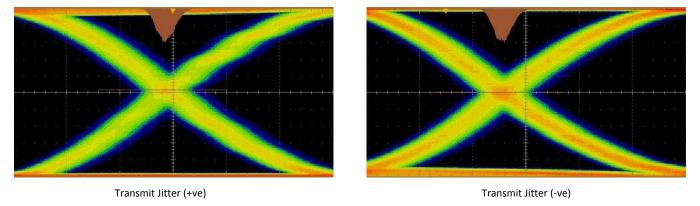

Figure 5. 100Base-TX Transmit Jitter with Clean Clock

Figure 6. 100Base-TX Transmit Jitter with Bad Clock

The DP83822 can tolerate approximately 375ps of RMS jitter on the clock. The RMS jitter was measured from 100Hz offset to 20MHz offset from the center frequency.

www.ti.com DP83822 Jitter Tolerance

### 3.2 Bit Error Rate

This test is optional. A network traffic generator is used for transmitting packets to the DP83822. The DP83822 is configured in reverse loopback. The network traffic generator receives the packet and checks for transmit errors. The input clock jitter for EUT is increased untill Packet errors are observed at the network traffic generator. For this experiment, SMB200 chassis with SX-7405 card is used as the traffic generator. SMB200 has its own SmartWindows software for configuring and controlling the cards.

## **Equipment List**

- Agilent 33250A

- R & S AMB100A

- Tek DPO 70804C with Tek P6330 differential probe

- Agilent E5052A

- SMB200 Chassis with SX-7405 10/100 card

- · Windows XP computer with SmartWindows Software

- Co-ax cables

#### **Procedure**

- Power on SMB200 and EUT. Configure EUT for reverse loopback by writing 0x0110 in register 0x16.

- Connect SX-7405 card with EUT using a Cat5 cable.

- Configure SX-7405 to transmit ethernet packets. The packets should be 1518bytes and channel utilization should be 100%.

- Slowly increase Noise Amplitude on Agilent 33250A till errors are observed on received ethernet packets.

- Connect the clock to the Phase Noise measurement setup as shown in Figure 1 and measure RMS jitter with Averaging turned on.

DP83822 can tolerate approximately 445ps of input clock jitter.

## 4 Conclusion

This app note explains the effect of reference clock jitter on the performance of DP83822 and the procedure to test the jitter performance. Jitter tolerance numbers are provided at the end of each test. These numbers are derived from limited sample set of DP83822 devices tested in lab setting.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products | Applications |

|----------|--------------|

| Tiouucis | Applications |

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic Security www.ti.com/security logic.ti.com

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity