# **Correcting cross-wire faults in modern e-metering networks**

# **By Thomas Kugelstadt**

#### Senior Systems Engineer

Electricity metering (e-metering) for commercial and residential applications relies heavily on long-haul, differential data-transmission networks based on the TIA/EIA-485 standard, commonly referred to as RS-485. In order to overcome the large ground-potential differences often encountered between remotely located bus nodes, each node is galvanically isolated, with regards to signal and supply lines, from the local e-metering circuitry.

The e-metering network is a typical master/slave system in which a host processor in the master node (located in a control center) sequentially addresses multiple slave nodes (located in the individual end customer's premises) along the bus.

With a single network comprising up to 60 nodes typically, the potential for unintentionally cross-wiring the two conductors of the twisted-pair bus cable can be rather high, if neither preventive measures during network installation nor corrective measures during network operation are applied.

The e-metering companies in the United States and Europe rely heavily on trained installation personnel and visually distinctive, color-coded cabling as preventive measures. This approach allows for the use of standard transceivers and cabling, such as isolated RS-485 transceivers and CAT-5 cable.

To further reduce the risk of wiring faults, recent network designs have been implementing a so-called training sequence that causes the slave nodes to adjust to the signal polarity of the master. During this sequence, the master broadcasts a unique bit pattern to all slaves. The same bit pattern, initially stored in each slave processor during power-up, is then compared with the pattern sent by the master. If the patterns match, the slave maintains its signal polarity. In the case of a mismatch, the slave processor inverts the signal polarity of both the incoming receive data and the outgoing transmit data. This inverting process is typically accomplished through an Exclusive-OR function within the slave processor and does not require any changes in hardware design. Thus, the proper operation of standard transceivers is still maintained.

In contrast to this approach, Asian e-metering companies push for more cost savings in network designs by using:

- Personnel inexperienced in network installation

- Low-cost, non-color-coded lamp wire instead of twistedpair cable

- Dedicated transceivers with integrated signal-polarity correction

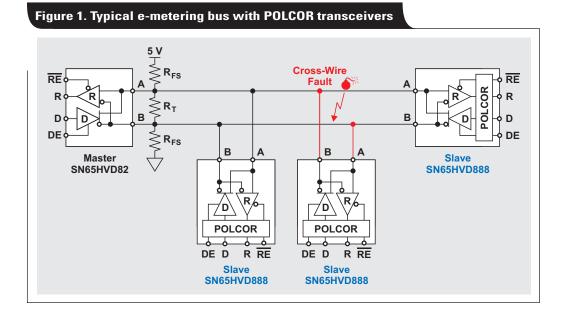

Figure 1 shows a typical e-metering network with SN65HVD888 polarity-correction (POLCOR) transceivers from Texas Instruments (TI). The master node contains a failsafe-biasing resistor network ( $R_{FS}$  and  $R_{T}$ ) that determines the signal polarity on the bus. Both master and slave nodes require integrated polarity-correction logic in

#### Figure 2. Polarity-correction timing after power-up

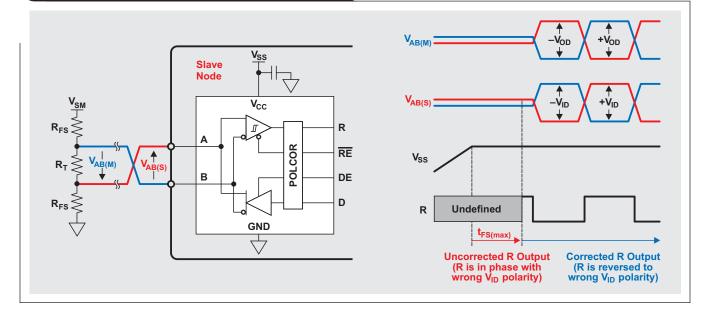

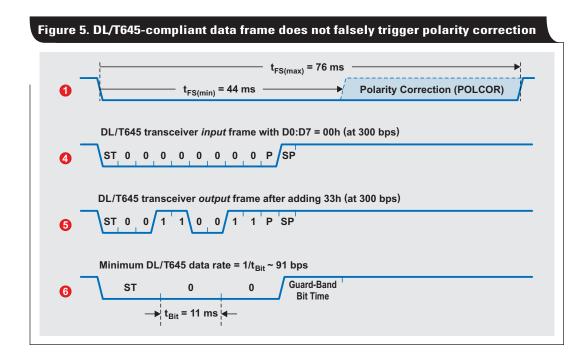

order to match the bus's signal polarity during bus idling. This correction logic consists of a debounce filter whose debounce time distinguishes between long data strings of the same signal polarity and actual bus-idle time. Due to the wide temperature range, across which the SN65HVD888 must be able to operate, the debounce time can vary between a lower limit of  $t_{FS(min)} = 44$  ms and an upper limit of  $t_{FS(max)} = 78$  ms.

This means that a polarity correction might be initiated by a constant bus voltage that is present for as little as 44 ms. Therefore, a data string of consecutive 0 bits must be shorter than 44 ms to avoid causing polarity correction. Alternatively, an intended polarity correction, typically required after powering up the network or after the installation of a new bus node, requires a bus-idle voltage to be present for longer than 78 ms to ensure that the polarity correction is completed.

During power-up, the receiver output (R) is undefined. Once the slave-node supply  $(V_{SS})$  is stable, the bus must idle for at least  $t_{FS(max)}$  to ensure that the polarity correction is completed. Because of the cross-wire fault, the positive bus voltage at the master's failsafe network  $(V_{AB(M)})$  appears negative at the transceiver input. Thus, after completion of  $t_{FS(max)}\!,$  the transceiver's internal polarity is switched to invert receive and transmit data. Hence, the negative input voltage  $(V_{AB(S)})$  is converted into a positive output voltage.

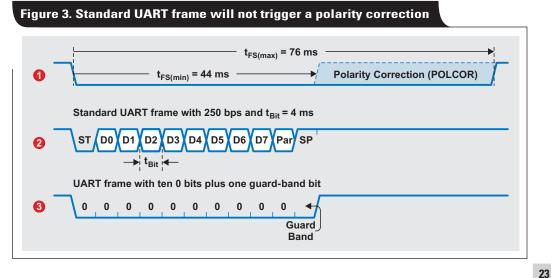

The minimum debounce time of  $t_{FS(min)} = 44$  ms allows for the transmission of a 250-bps UART frame with eleven 0 bits without triggering the POLCOR logic. The bit rate of 250 bps was chosen to be lower than the minimum 300 bps used in e-metering. The structure of the UART frame with its start, data, parity, and stop bits is shown in Figure 3.

Hence, constant bus signals shorter than 44 ms are considered valid data. Those exceeding 78 ms are considered bus-idle states. Only idle states with differential voltages more negative than the negative receiver input threshold  $(V_{IT})$  cause the correction logic to invert signal polarity. Otherwise, a transceiver maintains its polarity status. Figure 2 gives an example of the polarity correction after a power-up sequence.

# Polarity correction with DL/T645 protocol

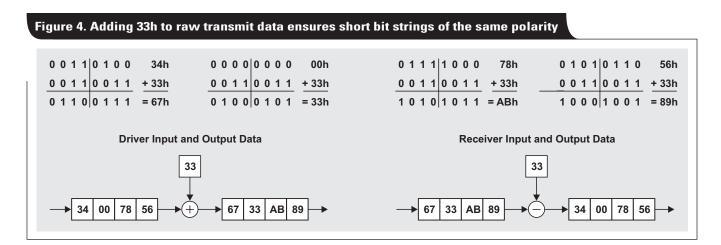

The e-metering protocol standard DL/T645 has further provisions to distinguish between long data strings of the same polarity and bus-idle states. Figure 4 shows how an example power value of 340078.56 W is processed within slave and master nodes.

The DL/T645 protocol calls for the measured decimal value in the driving slave node to be divided into groups of two digits. Each two-digit pair is converted into hexadecimal format (indicated by "h"). When these hex values arrive at the driver input, a 33h value is added. The resulting sum pattern is then transmitted through the driver output across the bus towards the master.

At the receiving master input, 33h is subtracted from the incoming sum pattern, thus yielding the original raw transmit data. Further, data processing converts the hex values back into decimal format. Figure 5 shows a DL/T645-compliant data frame operating at the minimum rate of 300 bps and compares it to the minimum debounce time of 44 ms. Here the DL/T645 protocol requires a string of ten 0 bits (eight data bits plus the start and parity bits) to be converted into a bit sequence with a maximum of two consecutive 1 or 0 bits. However, because the start bit is always 0, a maximum of three consecutive 0 bits can occur at the beginning of a frame. Their combined duration of 10 ms, however, is far too short to cause an unintentional polarity correction.

Based on the three 0 bits at the frame start, it can be determined how far the data rate can be safely reduced when one bit is added as a guard band. If the four bits are spread across the 44-ms time window, the bit interval becomes 11 ms. This results in a minimum data rate of  $1/11 \text{ ms} \sim 91 \text{ bps}$ . Therefore it is safe to say that the SN65HVD888 transceiver supports DL/T645-compliant data rates down to 100 bps.

24

**High-Performance Analog Products**

#### Figure 6. Simplified data link

## **Bus loading**

To determine the maximum number of slave nodes the master can drive, two load conditions are evaluated— dynamic or AC loading, and static or DC loading.

#### **AC** loading

AC loading exists during data transmission when the master commands a slave to send data and the slave responds to this request. During this normal operation, signal transients occur on the bus that are affected by the capacitances of the bus cable, node connectors, transceiver inputs, and power supplies. To minimize the effect of capacitive reactance on the signal, e-metering networks operate at low data rates of 300 bps to 20 kbps. Therefore, the following discussion considers only resistive loads.

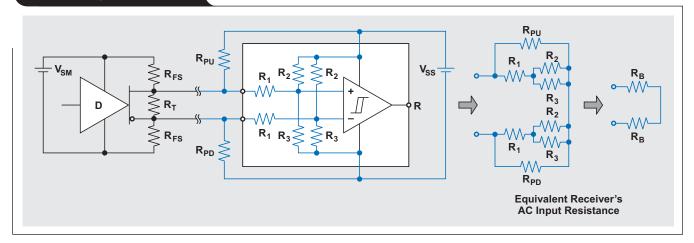

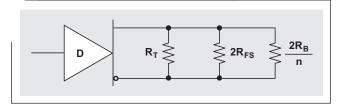

Figure 6 shows a simplified data link between a master, its failsafe-biasing network, and a remotely located slave receiver. Due to their large capacitance, the voltage supplies of the master ( $V_{SM}$ ) and the slave ( $V_{SS}$ ) can be seen as short circuits for AC signals. Hence, for the master node, the two failsafe resistors ( $R_{FS}$ ) are connected in series and lie parallel to the termination resistor ( $R_T$ ). The slave nodes are connected in a similar way. Here the internal DC-bias resistors ( $R_2$  and  $R_3$ ) are in parallel to one another, and their combined resistance is in series to a typical high-impedance  $R_1$ . Occasionally external pull-up/ pull-down resistors ( $R_{PU}$  and  $R_{PD}$ , respectively) are used to further bias the node input. These resistors do nothing but load the bus because they lie in parallel to the internal resistance network of the receiver.

Note that when  $\mathrm{R}_{FS}$  is kept between 1 and 2 k $\Omega,$  it is sufficient to bias the entire bus with a low-impedance biasing network at the master without further biasing at the slave nodes.

The resulting equivalent AC circuit is shown in Figure 7. Here  $2R_B/n$  represents the input resistance of multiple (n) transceivers. Because the EIA-485 standard specifies a maximum differential driver load of  $R_L = 54 \Omega$ , the parallel

#### Figure 7. Equivalent AC network

combination of all resistances on the bus must not exceed this value. This requirement is expressed in Equation 1:

$$\frac{1}{R_{\rm L}} = \frac{1}{R_{\rm T}} + \frac{1}{2R_{\rm FS}} + \frac{n}{2R_{\rm B}}$$

(1)

Solving for n yields Equation 2, which gives the maximum number of bus nodes that should be used under an AC-loading condition:

$$n = 2R_{B} \times \left(\frac{1}{R_{L}} - \frac{1}{R_{T}} - \frac{1}{2R_{FS}}\right)$$

(2)

Two commonly applied network designs are as follows:

1. The master uses a failsafe network with  $\rm R_{T}$  =120  $\Omega$  and  $\rm R_{FS}$  = 1 k $\Omega$ , while each slave is biased with external pull-up/pull-down resistors of  $\rm R_{PU}$  =  $\rm R_{PD}$  = 20 k $\Omega$ , so that  $\rm R_{B} \sim 18$  k $\Omega$ . Under these conditions, the maximum number of potential nodes on the bus is limited to

$$n = 2 \times 18 \text{ k}\Omega \times \left(\frac{1}{54 \Omega} - \frac{1}{120 \Omega} - \frac{1}{2 \text{ k}\Omega}\right)$$

$$= 348 \text{ nodes.}$$

(3)

2. The other scenario uses no termination resistor and rather high-impedance failsafe resistors of 10 k $\Omega$ . Also, the slave nodes operate without external biasing (R<sub>PU</sub> = R<sub>PD</sub> =  $\infty$ ). In this case, R<sub>B</sub> consists of only the receiver's internal resistance, which for the SN65HVD888 is 184 k $\Omega$

25

per input. Due to this high-impedance loading, the theoretical number of bus nodes increases drastically to

n = 2×184 k

$$\Omega$$

×  $\left(\frac{1}{54 \Omega} - \frac{1}{40 k\Omega}\right)$  = 6805 nodes. (4)

These two examples yield rather high numbers of bus nodes in comparison to the average e-metering network comprising only 40 to 60 nodes. The next section, "DC loading," shows that the AC-loading evaluation is misleading, as it does not consider the bus's leakage currents caused by the bus-node supplies.

#### **DC** loading

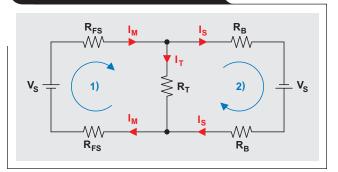

DC loading occurs during bus idling when no transceiver is actively driving the bus. In this state, the supply of the master ( $V_{SM}$ ) drives current through the nearby failsafe network to establish a positive bus failsafe voltage ( $V_{FS}$ ). This voltage determines the signal polarity for all slave nodes. Like the master supply, the slave supply ( $V_{SS}$ ) drives current through its internal resistor network. Part of this current leaks through the input resistance ( $R_1$ ) into the bus. The remaining current then flows through  $R_T$  and returns through  $R_1$  of the opposite terminal (Figure 6).

Correctly wired nodes drive currents through  $R_T$  in the same direction as the master supply. However, cross-wired nodes drive current in the opposite direction through  $R_T$ . This reduces the combined current through  $R_T$ , and with it the failsafe voltage ( $V_{FS}$ ). At a certain number of cross-wired nodes,  $V_{FS}$  can become so small that it falls within the receiver's input sensitivity, causing all bus nodes to assume indeterminate output states. To avoid this condition, the failsafe network at the master must be dimensioned so that even if all slaves are cross-wired, a positive  $V_{FS}$  is still maintained.

Figure 8 illustrates this scenario for only one slave node in order to simplify the mathematical derivations of the voltage and current relations within the network. Because  $V_{SM}$  equals  $V_{SS}$ , both supplies are simplified to  $V_S$ .

Equations 5 and 6 describe the two existing voltage loops, while Equation 7 expresses the current in the upper summing node:

$$-V_{\rm S} + I_{\rm M} \times 2R_{\rm FS} + I_{\rm T} \times R_{\rm T} = 0$$

<sup>(5)</sup>

$$-V_{\rm S} + I_{\rm S} \times 2R_{\rm B} - I_{\rm T} \times R_{\rm T} = 0$$

(6)

#### Figure 8. Equivalent DC network

$$I_{\rm T} = I_{\rm M} - n \times I_{\rm S} \tag{7}$$

Note that in Equation 7, the slave current  $(I_S)$  is multiplied by a factor n, indicating multiple slave nodes.

The master and slave currents are determined by solving Equation 5 for  $I_M$  and Equation 6 for  $I_S$ , yielding Equations 8 and 9, respectively:

$$I_{\rm M} = \frac{V_{\rm S} - I_{\rm T} \times R_{\rm T}}{2R_{\rm FS}}$$

(8)

$$I_{\rm S} = \frac{V_{\rm S} + I_{\rm T} \times R_{\rm T}}{2R_{\rm B}}$$

(9)

Inserting the equations for  $I_M$  and  $I_S$  into Equation 7 and substituting  $I_T$  with  $V_{FS}/R_T$  gives

$$\frac{V_{FS}}{R_T} = \frac{V_S \times (R_B - R_{FS} \times n)}{R_B \times (2R_{FS} + R_T) + R_{FS} \times R_T \times n}.$$

(10)

Solving Equation 10 for  $R_{FS}$  provides the failsafe resistor value necessary to keep  $V_{FS}$  positive:

$$R_{FS} = \frac{V_{S} - V_{FS}}{2V_{FS}/R_{T} + n \times (V_{S} + V_{FS})/R_{B}}.$$

(11)

For applications without a termination resistor ( $R_T = \infty$ ), Equation 11 simplifies to

$$R_{FS} = \frac{R_B \times (V_S - V_{FS})}{n \times (V_S + V_{FS})}.$$

(12)

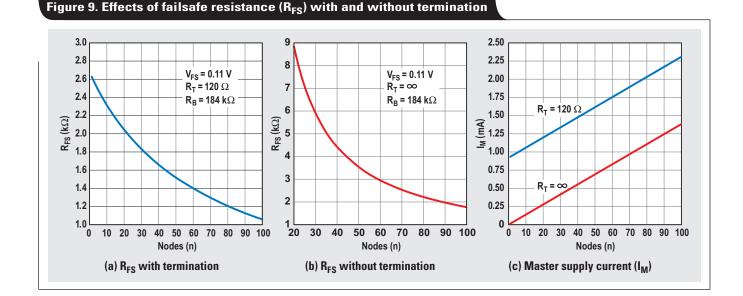

Figure 9 shows the values of  $R_{FS}$  and the master supply current ( $I_M$ ) as functions of bus-node count. Figure 9a was created by using Equation 11, assuming a termination resistor of 120  $\Omega$ . Figure 9b was created by using Equation 12, assuming no termination. Both figures were created for a failsafe voltage of 110 mV.

Figure 9c shows the master supply current  $(I_M)$  for both cases. Despite the low-impedance load of 120  $\Omega,~I_M$  in the failsafe network with termination is merely 1 mA larger than  $I_M$  in the network without termination.

### Conclusion

The SN65HVD888 POLCOR transceiver provides polarity correction for cross-wired bus cables by means of debounce filtering. The filter's minimum debounce time  $(t_{\rm FS(min)})$  determines the maximum duration of consecutive bits of equal polarity, while its maximum debounce time  $(t_{\rm FS(max)})$  determines the minimum bus-idle time for a complete signal-polarity correction.

The SN65HVD888 requires polarity correction only after a power-up sequence. Once completed, the polarity status is stored within the transceiver and consistently applied to both receive and transmit data. Switching the transceiver between transmit and receive mode does not alter the polarity status.

The transceiver supports DL/T645 data rates well below 300 bps. The recommended failsafe-biasing network uses a 120- $\Omega$  termination resistor and two 1.1-k $\Omega$  failsafe-biasing resistors.

#### References

1. "Bus-polarity correcting RS-485 transceiver with IEC-ESD protection," SN65HVD888 Datasheet. Available: www.ti.com/sllseh3-aaj

- 2. *DL/T 645-1997 multi-function watt-hour meter communication protocol*, People's Republic of China, Ministry of Electricity.

- 3. "Interface circuits for TIA/EIA-485 (RS-485)," Application Report. Available: www.ti.com/slla036-aaj

- 4. "RS-422 and RS-485 standards overview and system configurations," Application Report. Available: www.ti.com/slla070-aaj

- TIA/EIA-485-A, Electrical characteristics of generators and receivers for use in balanced digital multipoint systems, Telecommunications Industry Assoc., 2003. Available: www.tiaonline.org

- 6. *TIA/EIA-TSB 89: Application guidelines for TIA/EIA-485-A*, Telecommunications Industries Assoc., Jan. 1, 2006. Available: www.techstreet.com/products/1525598

- 7. ISO/IEC 8482: 1993 Information technology— Telecommunications and information exchange between systems—Twisted pair multipoint interconnections, International Standards Organization, 1993. Available: www.iso.org

## **Related Web sites**

Interface: www.ti.com/interface-aaj

www.ti.com/sn65hvd82-aaj www.ti.com/sn65hvd888-aaj

Subscribe to the AAJ: www.ti.com/subscribe-aaj

# **Internet**

**TI Semiconductor Product Information Center Home Page** support.ti.com

# TI E2E<sup>™</sup> Community Home Page

e2e.ti.com

# **Product Information Centers**

| Americas | Phone           | +1(512) 434-1560                                       |

|----------|-----------------|--------------------------------------------------------|

| Brazil   | Phone           | 0800-891-2616                                          |

| Mexico   | Phone           | 0800-670-7544                                          |

| Interne  | Fax<br>et/Email | +1(972) 927-6377<br>support.ti.com/sc/pic/americas.htm |

# Europe, Middle East, and Africa

Phone

| European Free Call | 00800-ASK-TEXAS<br>(00800 275 83927) |  |

|--------------------|--------------------------------------|--|

| International      | +49 (0) 8161 80 2121                 |  |

| Russian Support    | +7 (4) 95 98 10 701                  |  |

**Note:** The European Free Call (Toll Free) number is not active in all countries. If you have technical difficulty calling the free call number, please use the international number above.

| Fax          | +(49) (0) 8161 80 2045 |

|--------------|------------------------|

| Internet     | www.ti.com/asktexas    |

| Direct Email | asktexas@ti.com        |

#### Japan

| Phone          | Domestic      | 0120-92-3326                    |

|----------------|---------------|---------------------------------|

| Fax            | International | +81-3-3344-5317                 |

|                | Domestic      | 0120-81-0036                    |

| Internet/Email | International | support.ti.com/sc/pic/japan.htm |

|                | Domestic      | www.tij.co.jp/pic               |

# Asia

| Phone                                                        |                                  |                   |  |  |

|--------------------------------------------------------------|----------------------------------|-------------------|--|--|

| International                                                |                                  | +91-80-41381665   |  |  |

| Domestic                                                     |                                  | Toll-Free Number  |  |  |

| Note: Toll-free numbers do not support mobile and IP phones. |                                  |                   |  |  |

| Australia                                                    |                                  | 1-800-999-084     |  |  |

| China                                                        |                                  | 800-820-8682      |  |  |

| Hong Kong                                                    |                                  | 800-96-5941       |  |  |

| India                                                        |                                  | 1-800-425-7888    |  |  |

| Indonesia                                                    |                                  | 001-803-8861-1006 |  |  |

| Korea                                                        |                                  | 080-551-2804      |  |  |

| Malaysia                                                     |                                  | 1-800-80-3973     |  |  |

| New Zealand                                                  |                                  | 0800-446-934      |  |  |

| Philippines                                                  |                                  | 1-800-765-7404    |  |  |

| Singapore                                                    |                                  | 800-886-1028      |  |  |

| Taiwan                                                       |                                  | 0800-006800       |  |  |

| Thailand                                                     |                                  | 001-800-886-0010  |  |  |

| Fax                                                          | +8621-230                        | 73686             |  |  |

| Email                                                        | tiasia@ti.com or ti-china@ti.com |                   |  |  |

| Internet                                                     | support.ti.com/sc/pic/asia.htm   |                   |  |  |

Important Notice: The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval, warranty or endorsement thereof.

A090712

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated