## TPS769xx SOT-23 LDO Linear Regulator Evaluation Module

# User's Guide

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

#### Related Documentation From Texas Instruments

■ TPS76901, TPS76912, TPS76915, TPS76918, TPS76925, TPS76927, TPS76928, TPS76930, TPS76933, TPS76950 Ultra Low-Power 100-mA Low-Dropout Linear Regulators (TI Literature Number SLVS203) provides detailed information on the TPS769xx family of devices.

#### FCC Warning

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### **Trademarks**

TI is a trademark of Texas Instruments Incorporated.

iii

### **Contents**

| 1 In<br>1.<br>1.<br>1. | Output Voltages Greater Than V <sub>REF</sub>             |

|------------------------|-----------------------------------------------------------|

| 2 B<br>2.<br>2.        | ,                                                         |

| 3 Te<br>3.<br>3.       | · · · · · · · · · · · · · · · · · · ·                     |

| _                      | Figures                                                   |

| 4 4                    | 0.1 (TD070004FVM 407 V 4 4 V)                             |

| 1–1<br>1–2             | Schematic Diagram (TPS76901EVM-127, V <sub>O</sub> = 1 V) |

| 1–2<br>2–1             | Fixed Voltage Version of the TPS769xxEVM–127              |

| 2–2                    | Top Silk Screen                                           |

| 2–3                    | Bottom Layer (Top View)                                   |

| 2–4                    | Bottom Silk Screen (Top View)                             |

| 2–5                    | Drill Drawing and Drill Table                             |

| 2–6                    | Top Assembly                                              |

| 2–7                    | Bottom Assembly (Bottom View)                             |

| 3–1                    | Load Regulation                                           |

| 3–2                    | Quiescent Current vs Output Current                       |

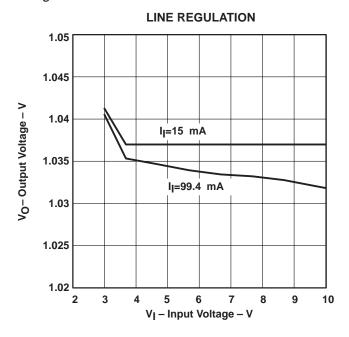

| 3–3                    | Line Regulation                                           |

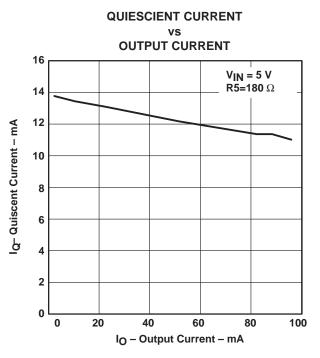

| 3–4                    | Quiescent Current vs Output Current                       |

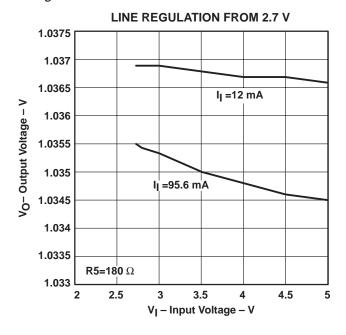

| 3–5                    | Line Regulation from 2.7 V                                |

|                        | Tables                                                    |

| 1–1<br>3–1             | Resistor Values                                           |

### **Chapter 1**

### Introduction

The TPS76901EVM–127, the TPS76918EVM-127, and the TPS76933EVM-127 LDO regulator modules provide the user with cost-effective solutions for providing power to various low-voltage options. These EVMs are pin-compatible with standard 3-terminal type regulators. The EVMs are set up as 1-V, 1.8-V, and 3.3-V output at 100 mA. Various options can be implemented with the board to give a range of output voltages from 0 to 5.5 V.

| Topi | Page                                              |

|------|---------------------------------------------------|

| 1.1  | Introduction1–2                                   |

| 1.2  | Output Voltages Greater Than V <sub>REF</sub> 1–3 |

| 1.3  | Output Voltages Less Than V <sub>REF</sub> 1–4    |

| 1.4  | Fixed Voltage Options1–5                          |

#### 1.1 Introduction

Low cost and simplicity of design make LDO regulators popular solutions in low-power step-down applications where lack of isolation from the input source is not a concern.

Applications of the EVM include single DSP C5400 device, digital camera, medical test equipment, cell phones, consumer audio equipment, and battery backup electronics.

Figure 1–1 shows the schematic of the TPS76901EVM-127 configured for a 1-V output. The TPS76933EVM–127 (3.3 V) schematic is shown in Figure 1–2. The LDO utilizes a PMOS pass element, which reduces the device quiescient current to 28  $\mu A$  (max). Other features of the PMOS LDO is the low dropout voltage of 71 mV (typ), thermal protection, over current limit, and 2  $\mu A$  shutdown quiescient current.

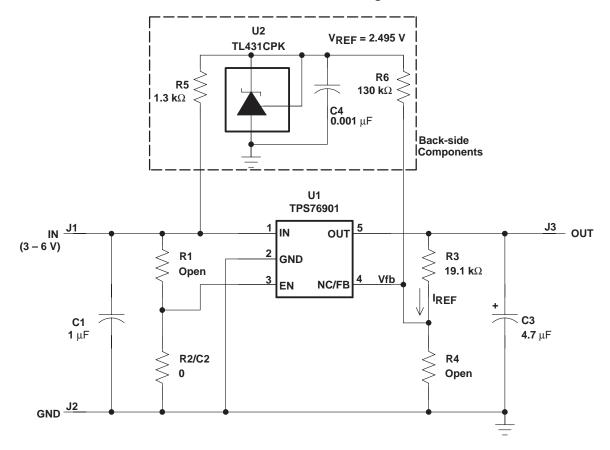

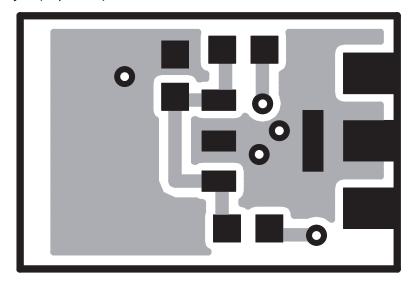

Figure 1–1. Schematic Diagram (TPS76901EVM-127,  $V_O = 1 \text{ V}$ )

The basic functionality of the EVM is to provide output voltages of 0 V to 5.5 V.

By means of external resistors and a voltage reference (R1–R6 and U1), the output voltage is adjusted to provide an output voltage that is either above or below the TPS76901 nominal, internal reference voltage of 1.224 V ( $V_{FB}$ ).

1-2 Introduction

#### 1.2 Output Voltages Greater Than V<sub>REF</sub>

Then

For applications requiring an output voltage greater than the internal reference voltage (VFR) of 1.224 V, a standard linear regulator circuit with an external voltage divider is all that is necessary. The lower section of Figure 1 shows a generic linear regulator circuit with an input capacitor (C1), output capacitor (C3), external voltage divider (R3/R4), and the enable circuit with either a pullup resistor (R1) or pulldown resistor (R2) as required. None of the backside components are required for this application. If a delayed enabled is desired, the R1 and R2/C2 component pads can be used for an RC circuit. When using the TPS76918EVM-127 or the TPS76933EVM-127, the external divider is not required and R3 is a  $0-\Omega$  resistor used to connect the sense terminal to  $V_{\Omega}$ . When using the TPS76901EVM-127 (adjustable output voltage), it is recommended that the divider current ( $I_{REF}$ ) be set to 7  $\mu$ A. Choosing R4 to be 169 k $\Omega$  and calculating R3 for V $\Omega$  accomplishes this.

$$R3 = \left(\frac{V_O}{V_{FB}} - 1\right) \times R4 \tag{1}$$

Where:

$$V_{FB} = 1.224 \text{ V}$$

$$R4 = 169 \text{ k}\Omega$$

Then

$$R3 = \left(138.07 \times V_O\right) - 169 \text{ k}\Omega$$

Lower value resistors can be used but are not as power efficient. Higher value resistors should be avoided due to leakage currents at FB increasing the output voltage error. Table 1–1 shows various voltage options and the suggested resistor values.

Table 1–1. Resistor Values

| OUTPUT VOLTAGE<br>(V) | DIVIDER RESISTANCE $(\mathbf{k}\Omega)$ |     |

|-----------------------|-----------------------------------------|-----|

| ( <b>v</b> )          | R3                                      | R4  |

| 2.5                   | 174                                     | 169 |

| 3.3                   | 287                                     | 169 |

| 3.6                   | 324                                     | 169 |

| 4.0                   | 383                                     | 169 |

| 5.0                   | 523                                     | 169 |

#### 1.3 Output Voltages Less Than V<sub>REF</sub>

Applications requiring a lower output voltage than the internal reference voltage needs additional circuitry. The backside components shown in the upper section of figure 1 along with the deletion of R4 will implement this option. The backside components function as a second (but fixed) voltage source to artificially increase the voltage at the feedback terminal, thus requiring less output voltage to satisfy the error amplifier. The two voltage sources are summed at the error amplifier input node and compared to the internal reference voltage of 1.224 V. The contribution of the TL431 reference is:

$$V_A = \frac{R3}{R3 + R6} \times V_{REF} = \frac{R3}{R3 + R6} \times 2.495 \text{ V}$$

The contribution of the output voltage is:

$$V_{B} = \frac{R6}{R3 + R6} \times V_{O}$$

The total feedback voltage at V<sub>FB</sub> then is the sum of the two previous equations:

$$V_{FB} = V_A + V_B = \left(\frac{R3}{R3 + R6} \times 2.495\right) + \left(\frac{R6}{R3 + R6} \times V_O\right)$$

Selecting R6 = 130 k $\Omega$  and solving for R3 yields:

$$R3 = \frac{\left(V_{FB} - V_{O}\right)}{\left(V_{REF} - V_{FB}\right)} \times R6 = 125.19 - \left(102.28 \times V_{O}\right) k\Omega$$

This circuit can only work down to 0 V due to the lack of a negative supply voltage. The accuracy of the output voltage is determined by the accuracy of both regulators, but since the load for the TL431 portion of the circuit is constant, only its line regulation and drift are important to the output voltage accuracy.

Additional features include a delayed enable by placing a capacitor for C2 and calculating R1 and C2 for an RC circuit. If no delayed enable is needed, then place a zero ohm resistor for R2 since the enable pin is active low. (note that C2 and R2 share the same component location).

1-4 Introduction

#### 1.4 Fixed Voltage Options

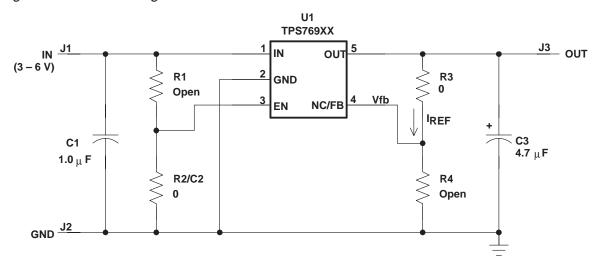

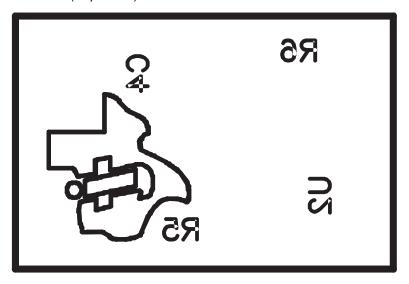

The TPS76918EVM-127 (Vout = 1.8 V) and the TPS76933EVM-127 (Vout = 3.3 V) fixed voltage options are also available. Both of these EVMs use only 4 components (see Figure 1-2) and can be used as a three terminal regulator.

Figure 1–2. Fixed Voltage Version of the TPS769xxEVM–127

Refer to SLVA071 application brief and TPS76901 datasheet for additional information.

1-6 Introduction

### Chapter 2

## **Board Layers and Assembly Drawings**

This chapter shows the board layers and assembly drawings of the TPS769xx EVM.

| Topic |     |                   | age |

|-------|-----|-------------------|-----|

|       | 2.1 | Board Layers      | 2–2 |

|       | 2.2 | Assembly Drawings | 2–5 |

#### 2.1 Board Layers

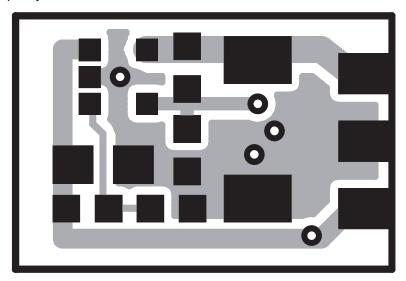

Figure 2–1. Top Layer

Figure 2-2. Top Silk Screen

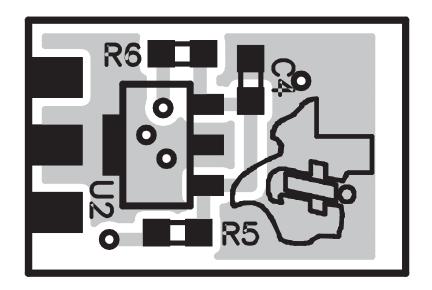

Figure 2–3. Bottom Layer (Top View)

Figure 2-4. Bottom Silk Screen (Top View)

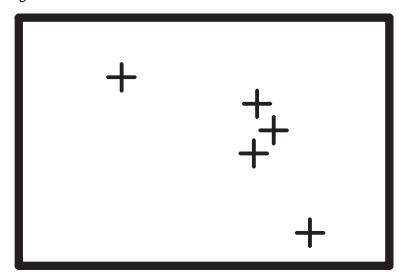

Figure 2–5. Drill Drawing and Drill Table

| Drill Table     |        |          |        |

|-----------------|--------|----------|--------|

| Hole Dia (inch) | Symbol | Quantity | Plated |

| 0.012           | +      | 5        | Yes    |

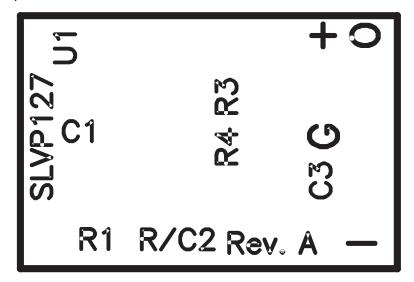

#### 2.2 Assembly Drawings

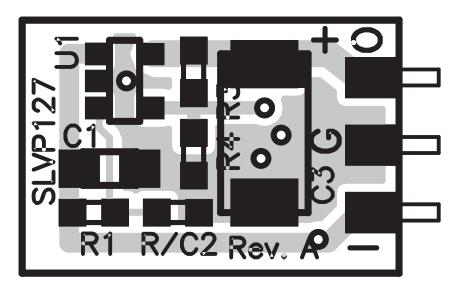

Figure 2–6. Top Assembly

Figure 2–7. Bottom Assembly (Bottom View)

## Chapter 3

# Testing

This chapter provides details on testing the TPS76901–EVM–127

| Topi | c       | Page |

|------|---------|------|

| 3.1  | Testing | 3-2  |

#### 3.1 Testing

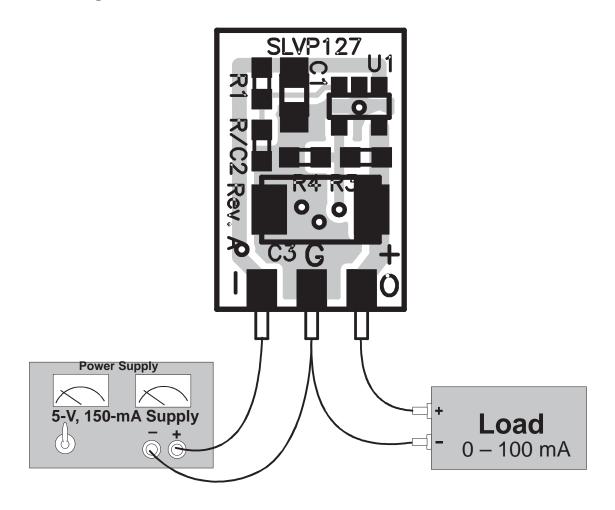

#### 3.2 Test Setup

Test Procedure (for TPS76901EVM-127,  $V_0 = 1 \text{ V}$ )

- 1) Connect test setup as shown in the previous illustration. Set load to zero current. Set input voltage to 5 V and apply.

- 2) Verify output voltage is 1.00 V  $\pm$ 50 mV.

- 3) Adjust load for 100 mA and again verify output voltage is 1.00 V  $\pm 50$  mV.

3-2 Testing

Table 3–1. Bill Of Materials

| REF DES  | QTY | PART NUMBER      | DESCRIPTION                                           | MFG           | SIZE    |

|----------|-----|------------------|-------------------------------------------------------|---------------|---------|

| C1       | 1   | ECJ-2VF1C105Z    | Capacitor, ceramic, 1 μF, 16 V, +80%–20%, Y5V         | Panasonic     | 805     |

| C2       |     |                  | Not used                                              |               | 603     |

| C3       | 1   | TPSC475K035R0600 | Capacitor, tantalum, 4.7 μF, 35 V, 20%                | AVX           | С       |

| C3 (Alt) |     | ECST1AC226R      | Capacitor, tantalum, 22 μF, 10 V, 20%                 | Panasonic     | С       |

| C4       | 1   | GRM39X7R102K050A | Capacitor, ceramic, 1000 pF, 50 V, 10%, X7R           | muRata        | 603     |

| J1       | 3   | CA26DA-D36K-0FA  | Clip, surface-mount, 0.040" board, 0.090" stand-off   | NAS Interplex | 0.1"    |

| J2       |     | CA26DA-D36K-0FA  | Clip, surface-mount, 0.040" board, 0.090" stand-off   | NAS Interplex | 0.1"    |

| J3       |     | CA26DA-D36K-0FA  | Clip, Surface-mount, 0.040" board, 0.090" stand-off   | NAS Interplex | 0.1"    |

| R1       |     |                  | Not used                                              |               | 603     |

| R2       | 1   | Std              | Resistor, chip, 0 Ω, 1/16W, 5%                        |               | 603     |

| R3       | 1   | Std              | Resistor, chip, 19.1 kΩ, 1/16W, 1%                    |               | 603     |

| R4       |     |                  | Not used                                              |               | 603     |

| R5       | 1   | Std              | Resistor, chip, 1.3 kΩ, 1/16W, 5%                     |               | 603     |

| R6       | 1   | Std              | Resistor, chip, 130 kΩ, 1/16W, 1%                     |               | 603     |

| U1       | 1   | TPS76901DBV      | IC, LDO                                               | TI            | SOT23-5 |

| U2       | 1   | TL431CPK         | IC, shunt regulator, 2.5 V, 2%                        | TI            | SOT-89A |

|          | 1   | SLVP127          | PCB, 2 layer, 1 oz, 0.55" × 0.37" × 0.040" (Finished) |               |         |

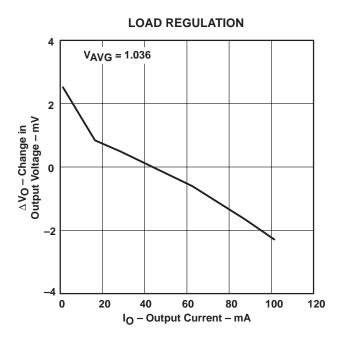

Figure 3–1. Load Regulation

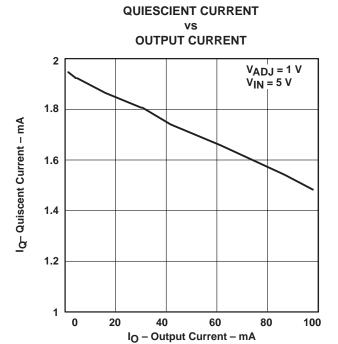

Figure 3–2. Quiescent Current vs Output Current

Figure 3–3. Line Regulation

3-4 Testing

Operation of the 1-V EVM with input voltages from 2.7 V to 3 V requires increasing the bias current for the TL431. Changing R5 to 180  $\Omega$  accomplishes this at the expense of higher quiescent currents. Figures 3–4 and 3–5 show the results of this modification.

Figure 3-4. Quiescent Current vs Output Current

Figure 3-5. Line Regulation from 2.7 V

3-6 Testing