TPS7H2201-SP, TPS7H2201-SEP SLVSD00F SEPTEMBER 2018 - REVISED MARCH 2024

# TPS7H2201-SP and TPS7H2201-SEP Radiation Hardened 1.5V to 7V, 6A eFuse

## 1 Features

TEXAS

INSTRUMENTS

- Standard micro circuit available, SMD 5962R17220

- Vendor item drawing available, VID V62/23608

- Radiation performance:

- Radiation hardness assurance (RHA) up to TID \_ 100krad(Si)

- Single event latchup (SEL), single event burnout (SEB), and single event gate rupture (SEGR) immune to LET = 75MeV-cm<sup>2</sup>/mg

- SEFI/SET characterized to LET = 75MeV-cm<sup>2</sup>/mg

- Integrated single channel eFuse

- Input voltage range: 1.5V to 7V

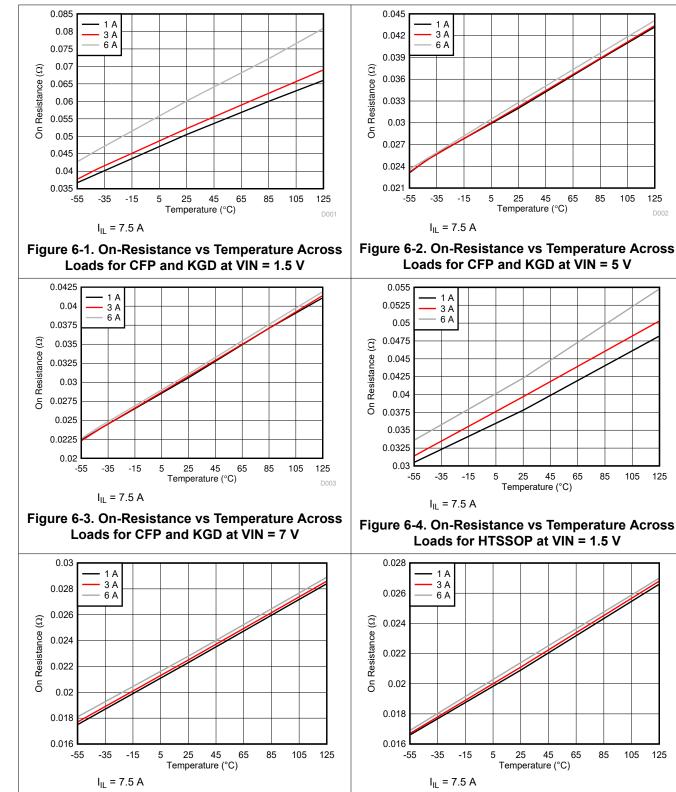

- Low on-resistance (R<sub>ON</sub>) of :

- 35mΩ maximum at 25°C and VIN = 5V for CFP and KGD

- $23m\Omega$  maximum at  $25^{\circ}$ C and VIN = 5V for **HTSSOP**

- 6-A maximum continuous switch current

- Low control input threshold enables use of 1.2, 1.8, 2.5, and 3.3V logic

- Configurable rise time (soft start)

- Reverse current protection

- Programmable and internal current limiting • (fast-trip)

- Programmable fault timer (current limit and • retry modes)

- Thermal shutdown

- Ceramic and plastic package with thermal pad

## 2 Applications

- Space satellite power management and distribution

- Radiation hardened and tolerant power tree applications

- Available in military (-55°C to 125°C) temperature range

## **3 Description**

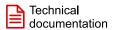

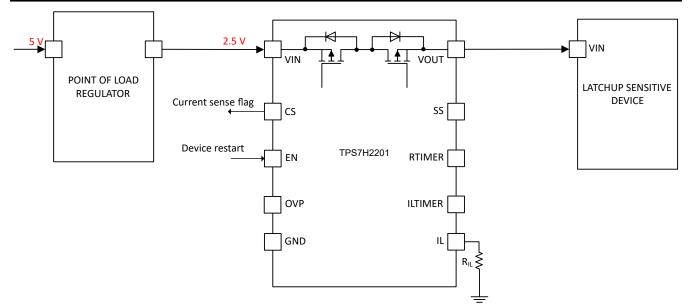

The TPS7H2201 is a single channel eFuse that provides configurable rise time to minimize inrush current and reverse current protection. The device contains a P-channel MOSFET that can operate over an input voltage range of 1.5V to 7V and can support a maximum continuous current of 6A. The switch is controlled by an on and off input (EN), which is capable of interfacing directly with low-voltage control signals.

The TPS7H2201 is available in a ceramic and plastic package with integrated thermal pad allowing for high power dissipation. The device is characterized for operation over the free-air temperature range of -55°C to 125°C.

# **Device Information**

| PART NUMBER <sup>(1)</sup> | GRADE                                 | PACKAGE                                                          |  |  |  |  |  |

|----------------------------|---------------------------------------|------------------------------------------------------------------|--|--|--|--|--|

| 5962R1722001VXC            | Flight grade RHA<br>100krad(Si)       | 16-pin CDFP                                                      |  |  |  |  |  |

| 5962-1722001VXC            | Flight grade QMLV                     | 11.00 × 9.60mm                                                   |  |  |  |  |  |

| TPS7H2201HKR/EM            | Engineering<br>samples <sup>(2)</sup> | Weight: 1.56g <sup>(3)</sup>                                     |  |  |  |  |  |

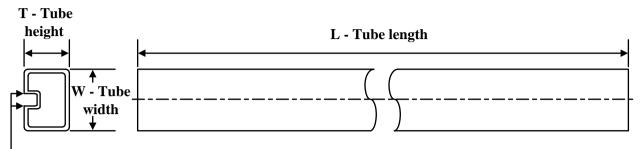

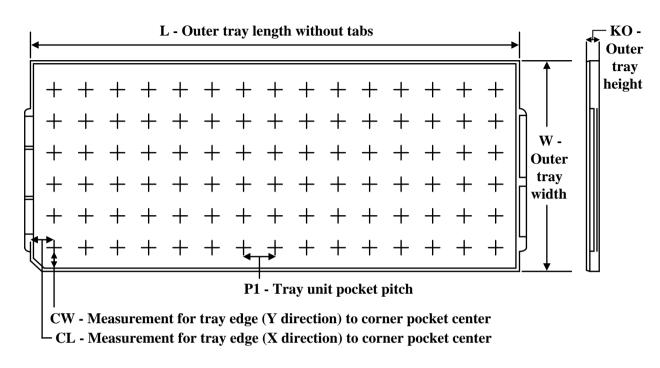

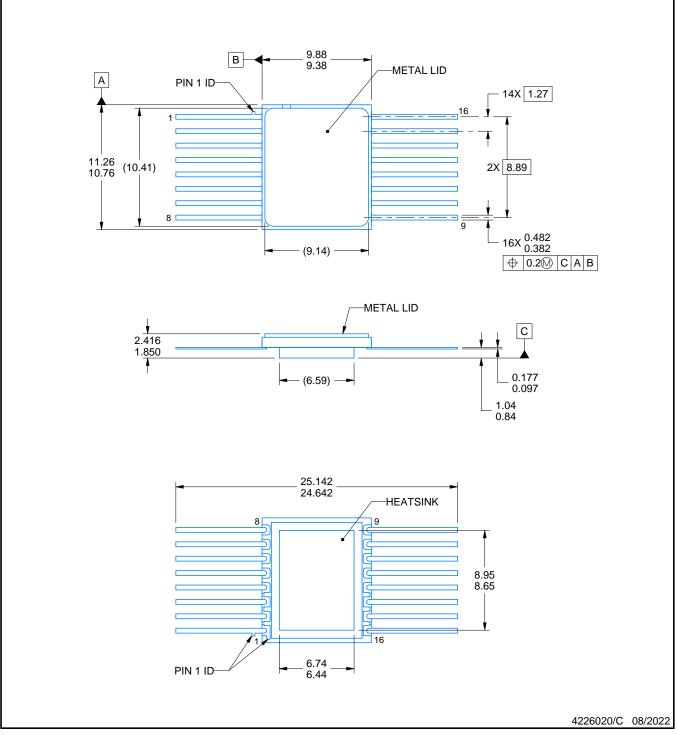

| TPS7H2201MDAPTSEP          | SEP                                   | 32-pin HTSSOP<br>6.10 × 11.00mm<br>Weight: 0.191g <sup>(3)</sup> |  |  |  |  |  |

| TPS7H2201EVM-CVAL          | Ceramic evaluation board              | EVM                                                              |  |  |  |  |  |

- For all available packages, see the orderable addendum at (1) the end of the data sheet. Also refer to Device Options.

- These units are intended for engineering evaluation only. (2) They are processed to a noncompliant flow. These units are not suitable for qualification, production, radiation testing or flight use. Parts are not warranted for performance over the full MIL specified temperature range of -55°C to 125°C or operating life.

- (3) Dimension and mass values are nominal.

Simplified Schematic

# **Table of Contents**

| 1 Features1                                            |

|--------------------------------------------------------|

| 2 Applications1                                        |

| 3 Description1                                         |

| 4 Device Options                                       |

| 5 Pin Configuration and Functions4                     |

| 6 Specifications                                       |

| 6.1 Absolute Maximum Ratings8                          |

| 6.2 ESD Ratings                                        |

| 6.3 Recommended Operating Conditions8                  |

| 6.4 Thermal Information9                               |

| 6.5 Electrical Characteristics: All Devices9           |

| 6.6 Electrical Characteristics: CFP and KGD Options 11 |

| 6.7 Electrical Characteristics: HTSSOP Option12        |

| 6.8 Switching Characteristics (All Devices)13          |

| 6.9 Quality Conformance Inspection13                   |

| 6.10 Typical Characteristics14                         |

| 7 Parameter Measurement Information                    |

| 8 Detailed Description                                 |

| 8.1 Overview20                                         |

| 8.2 Functional Block Diagram                          | .20  |

|-------------------------------------------------------|------|

| 8.3 Feature Description                               |      |

| 8.4 Device Functional Modes                           |      |

| 9 Application and Implementation                      |      |

| 9.1 Application Information                           | . 31 |

| 9.2 Typical Applications                              |      |

| 9.3 Power Supply Recommendations                      | 36   |

| 9.4 Layout                                            | . 36 |

| 10 Device and Documentation Support                   |      |

| 10.1 Documentation Support                            | . 37 |

| 10.2 Receiving Notification of Documentation Updates. |      |

| 10.3 Support Resources                                | . 37 |

| 10.4 Trademarks                                       | .37  |

| 10.5 Electrostatic Discharge Caution                  | 37   |

| 10.6 Glossary                                         | 37   |

| 11 Revision History                                   | . 38 |

| 12 Mechanical, Packaging, and Orderable               |      |

| Information                                           | . 38 |

|                                                       |      |

Copyright © 2024 Texas Instruments Incorporated

## **4 Device Options**

| GENERIC PART<br>NUMBER | RADIATION RATING <sup>(1)</sup>                                         | GRADE <sup>(2)</sup>             | PACKAGE           | ORDERABLE PART<br>NUMBER |

|------------------------|-------------------------------------------------------------------------|----------------------------------|-------------------|--------------------------|

|                        | TID of 100 krad(Si) RLAT,                                               | QMLV-RHA                         | 16-pin HKR CFP    | 5962R1722001VXC          |

|                        | DSEE free to 75 MeV-                                                    | QMLP-RHA                         | 32-pin DAP HTSSOP | 5962R1722002PYE          |

| TPS7H2201-SP           | cm <sup>2</sup> /mg                                                     | KGD (QMLV-RHA)                   | Die               | 5962R1722001V9A          |

|                        | Nana                                                                    | Engineering Medel (3)            | 16-pin HKR CFP    | PTS7H2201HKR/EM          |

|                        | None                                                                    | Engineering Model <sup>(3)</sup> | Die               | TPS7H2201Y/EM            |

| TPS7H2201-SEP          | TID of 50 krad(Si) RLAT,<br>DSEE free to 43 MeV-<br>cm <sup>2</sup> /mg | Space Enhanced<br>Plastic        | 32-pin DAP HTSSOP | TPS7H2201MDAPTSEP        |

(1) TID is total ionizing dose and DSEE is destructive single event effects. Additional information is available in the associated TID reports and SEE reports for each product.

(2) For additional information about part grade, view SLYB235.

(3) These units are intended for engineering evaluation only. They are processed to a non-compliant flow (such as no burn-in and only 25°C testing). These units are not suitable for qualification, production, radiation testing, or flight use. Parts are not warranted as to performance over temperature or operating life.

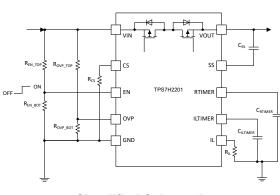

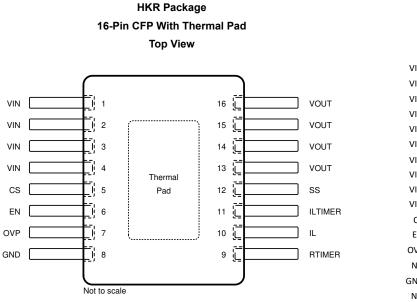

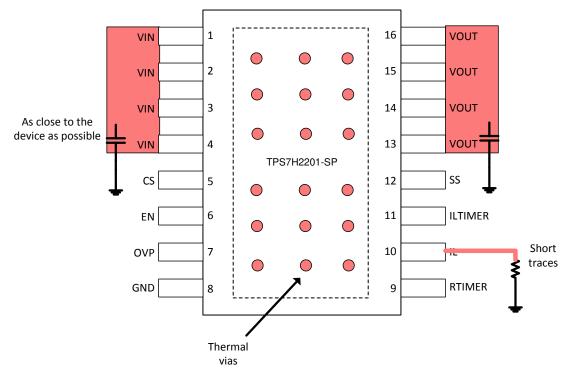

## **5** Pin Configuration and Functions

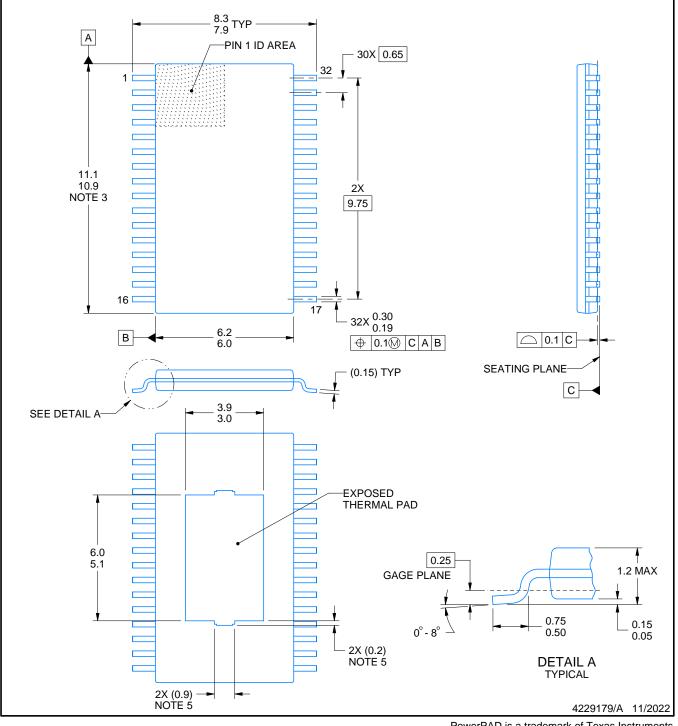

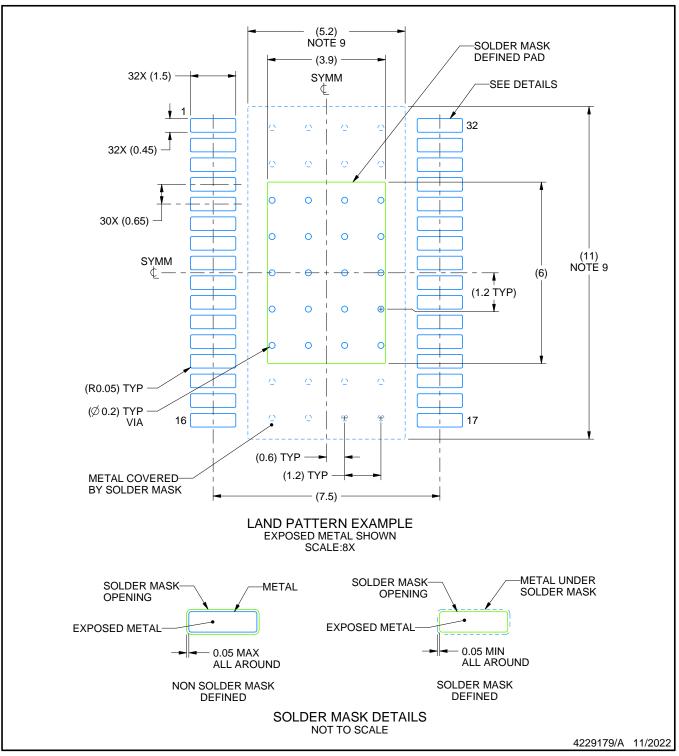

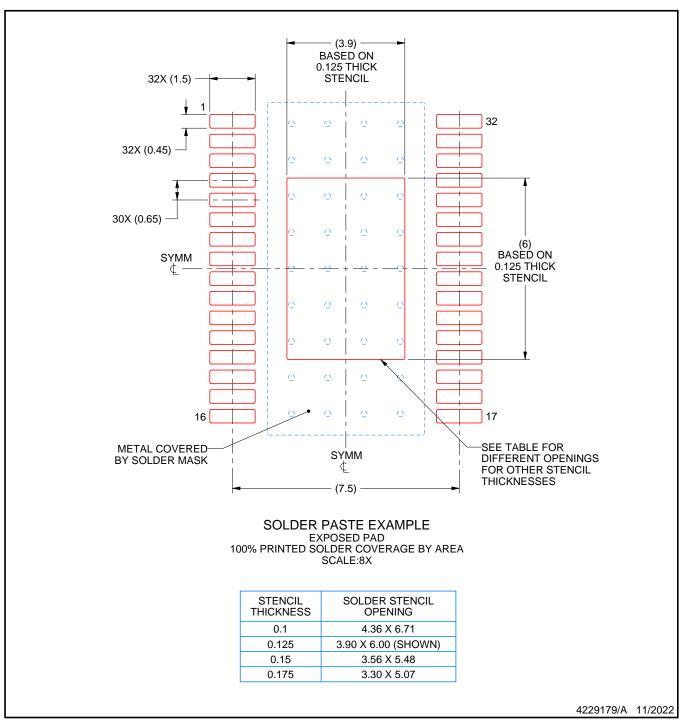

**DAP Package**

#### Table 5-1. Pin Functions

| PIN             |             |                |                    |                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----------------|-------------|----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| HKR (16)<br>NO. | PW (32) NO. | NAME           | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 1-4             | 1-10        | VIN            | I                  | Switch input. Input bypass capacitor recommended for minimizing $V_{IN}$ dip.                                                                                                                                                                                                                                                                                                                                        |  |  |

| 5               | 11          | CS             | 0                  | Current sense pin proportional to output current. Connect a resistor to GND.                                                                                                                                                                                                                                                                                                                                         |  |  |

| 6               | 12          | EN             | I                  | Active high switch control input. Do not leave floating.                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 7               | 13          | OVP            | I                  | Overvoltage protection. Programmable using an external resistor divider. If no OVP is desired, this pin should be connected to GND.                                                                                                                                                                                                                                                                                  |  |  |

| 8               | 15          | GND            |                    | Device ground. <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 9               | 18          | RTIMER         | I/O                | I/O Capacitor programmed fault timer control during disabled and retry mode.<br>Connecting this pin to GND holds the switch disabled until the EN pin is cycled.<br>Do not float this pin or connect it to VIN.                                                                                                                                                                                                      |  |  |

| 10              | 20          | IL             | I/O                | Current limiter control. Programmable using an external resistor to GND. Do not                                                                                                                                                                                                                                                                                                                                      |  |  |

| 11              | 21          | ILTIMER        | I                  | Capacitor programmed fault timer control during current limiting mode. Connecting this pin to VIN uses the internal current limit timer and connecting this pin to GND disables the internal timer functionality for the ILTIMER as well as retry mode. In this case, the device will remain at programmed current limit indefinitely in the event of a short without going intro retry mode. Do not float this pin. |  |  |

| 12              | 22          | SS             | I/O                | Switch slew rate control. See the Section 8.3.2 section for more information.                                                                                                                                                                                                                                                                                                                                        |  |  |

| 13-16           | 23-32       | VOUT           | 0                  | Switch output. A minimum 10-µF output capacitor is recommended.                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                 | 14,16,17,19 | NC             | _                  | No connect. This pin is not internally connected. It is recommended to connect these pins to GND to prevent charge buildup; however, these pins can also be left open or tied to any voltage between GND and VIN.                                                                                                                                                                                                    |  |  |

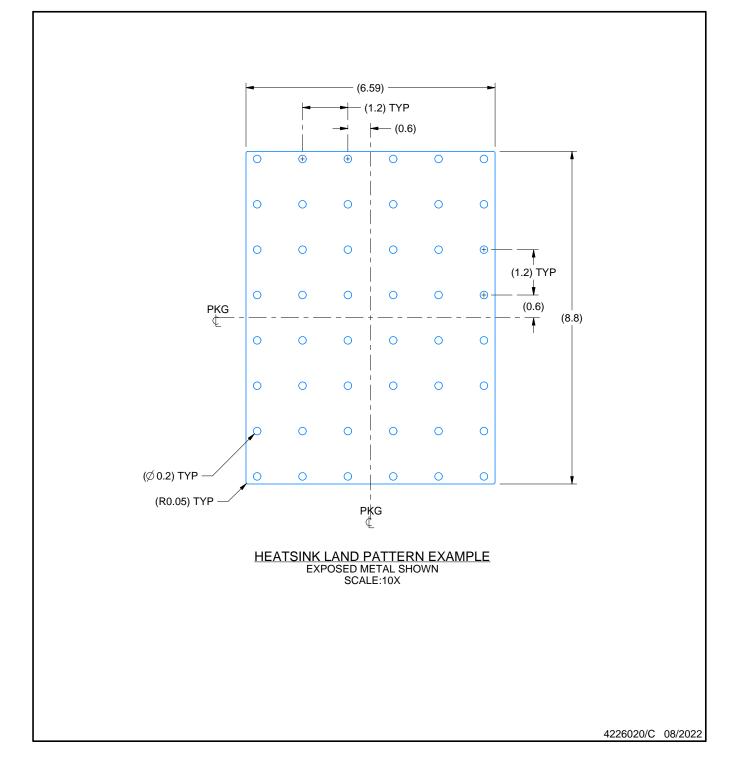

|                 | _           | Thermal<br>Pad | _                  | Thermal pad (exposed center pad) for heat dissipation purposes. Thermal pad is internally connected to seal ring and GND.                                                                                                                                                                                                                                                                                            |  |  |

(1) I = Input, O = Output, I/O = Input or Output, — = Other

(2) Thermal pad is internally connected to the seal ring and GND for HKR option.

|               |             |        |                | Table 5-2. Bare Di    | e Information             |                                                       |        |               |

|---------------|-------------|--------|----------------|-----------------------|---------------------------|-------------------------------------------------------|--------|---------------|

| DIE THICKNESS | В           | ACK    | SIDE FINISH    | BACKSIDE<br>POTENTIAL | BOND PAD META<br>COMPOSIT |                                                       | BOND I | PAD THICKNESS |

| 15 mils       | Sil         | icon v | vith backgrind | Ground                | ALCU                      |                                                       |        | 1050 nm       |

|               |             |        |                |                       |                           |                                                       |        |               |

|               |             |        |                | 1<br>4<br>6<br>8      |                           | 47 4                                                  | 8      |               |

|               |             |        | 11 1<br>13 1   | 0<br>2<br>4<br>6      |                           | 43     4       41     4       39     3       37     3 | 0      |               |

| 5746-         | - 2670 -    |        | 17 1<br>19 2   | 8<br>0                |                           | 35 3.<br>33 3:                                        | 4      |               |

|               |             |        | 21<br>22<br>23 |                       |                           |                                                       | 31     |               |

|               |             |        | 24             |                       |                           |                                                       | 30     |               |

|               |             |        | 25             |                       |                           |                                                       | 29     |               |

|               | 38          | 0—     | 26 2           | 7                     |                           | 28                                                    |        |               |

| <u>*</u>      | ~~ <b>\</b> | Ó      |                |                       | 510                       |                                                       |        |               |

|               |             | 76     | -              |                       | 662                       |                                                       |        | •             |

- 1. All dimensions in microns (µm).

- 2. The inner rectangle is the die and the outer rectangle is the die plus scribe lines.

#### TPS7H2201-SP, TPS7H2201-SEP SLVSDO0F – SEPTEMBER 2018 – REVISED MARCH 2024

| Table 5-3. Bond Pad Coordinates in Microns |            |         |         |         |         |  |

|--------------------------------------------|------------|---------|---------|---------|---------|--|

| DESCRIPTION                                | PAD NUMBER | X MIN   | Y MIN   | X MAX   | Y MAX   |  |

| VIN                                        | 1          | 611.78  | 4976.1  | 751.73  | 5116.05 |  |

| VIN                                        | 2          | 258.17  | 4976.1  | 398.12  | 5116.05 |  |

| VIN                                        | 3          | 258.17  | 4809.15 | 398.12  | 4949.1  |  |

| VIN                                        | 4          | 611.78  | 4809.15 | 751.73  | 4949.1  |  |

| VIN                                        | 5          | 258.17  | 4641.39 | 398.12  | 4781.34 |  |

| VIN                                        | 6          | 611.78  | 4641.39 | 751.73  | 4781.34 |  |

| VIN                                        | 7          | 258.17  | 4473.59 | 398.12  | 4613.54 |  |

| VIN                                        | 8          | 611.78  | 4473.59 | 751.73  | 4613.54 |  |

| VIN                                        | 9          | 258.17  | 3647.7  | 398.12  | 3787.65 |  |

| VIN                                        | 10         | 611.78  | 3647.7  | 751.73  | 3787.65 |  |

| VIN                                        | 11         | 258.17  | 3480.75 | 398.12  | 3620.7  |  |

| VIN                                        | 12         | 611.78  | 3480.75 | 751.73  | 3620.7  |  |

| VIN                                        | 13         | 258.17  | 3312.99 | 398.12  | 3452.94 |  |

| VIN                                        | 14         | 611.78  | 3312.99 | 751.73  | 3452.94 |  |

| VIN                                        | 15         | 258.17  | 3145.19 | 398.12  | 3285.14 |  |

| VIN                                        | 16         | 611.78  | 3145.19 | 751.73  | 3285.14 |  |

| VIN                                        | 17         | 258.17  | 2315.57 | 398.12  | 2455.52 |  |

| VIN                                        | 18         | 611.78  | 2315.57 | 751.73  | 2455.52 |  |

| VIN                                        | 19         | 258.17  | 2146.37 | 398.12  | 2286.32 |  |

| VIN                                        | 20         | 611.78  | 2146.37 | 751.73  | 2286.36 |  |

| AVDD                                       | 21         | 54.99   | 1842.03 | 194.94  | 1981.98 |  |

| AVDD                                       | 22         | 54.99   | 1671.48 | 194.94  | 1811.43 |  |

| CS                                         | 23         | 54.99   | 1480.77 | 194.94  | 1620.72 |  |

| EN                                         | 24         | 54.99   | 972.68  | 194.94  | 1112.63 |  |

| OVP                                        | 25         | 54.99   | 406.26  | 194.94  | 546.21  |  |

| GND                                        | 26         | 407.21  | 54.99   | 547.16  | 194.94  |  |

| GND                                        | 27         | 577.76  | 54.99   | 717.71  | 194.94  |  |

| RTIMER                                     | 28         | 2792.88 | 54.99   | 2932.83 | 194.94  |  |

| IL                                         | 29         | 3315.06 | 587.43  | 3455.01 | 727.38  |  |

| ILTIMER                                    | 30         | 3315.06 | 1099.26 | 3455.01 | 1239.21 |  |

| SS                                         | 31         | 3315.06 | 1544.09 | 3455.01 | 1684.04 |  |

| VOUT                                       | 32         | 3111.66 | 2146.37 | 3251.61 | 2286.32 |  |

| VOUT                                       | 33         | 2758.05 | 2146.37 | 2898    | 2286.32 |  |

| VOUT                                       | 34         | 3111.66 | 2315.57 | 3251.61 | 2455.52 |  |

| VOUT                                       | 35         | 2758.05 | 2315.57 | 2898    | 2455.52 |  |

| VOUT                                       | 36         | 3111.66 | 3145.19 | 3251.61 | 3285.14 |  |

| VOUT                                       | 37         | 2758.05 | 3145.19 | 2898    | 3285.14 |  |

| VOUT                                       | 38         | 3111.66 | 3312.99 | 3251.61 | 3452.94 |  |

| VOUT                                       | 39         | 2758.05 | 3312.99 | 2898    | 3452.94 |  |

| VOUT                                       | 40         | 3111.66 | 3480.75 | 3251.61 | 3620.7  |  |

| VOUT                                       | 41         | 2758.05 | 3480.75 | 2898    | 3620.7  |  |

| VOUT                                       | 42         | 3111.66 | 3647.7  | 3251.61 | 3787.65 |  |

| VOUT                                       | 43         | 2758.05 | 3647.7  | 2898    | 3787.65 |  |

| VOUT                                       | 44         | 3111.66 | 4473.59 | 3251.61 | 4613.54 |  |

| VOUT                                       | 45         | 2758.05 | 4473.59 | 2898    | 4613.54 |  |

Copyright © 2024 Texas Instruments Incorporated

| Table 5-3. Bond Pad Coordinates in Microns (continued) |            |         |         |         |         |  |  |

|--------------------------------------------------------|------------|---------|---------|---------|---------|--|--|

| DESCRIPTION                                            | PAD NUMBER | X MIN   | Y MIN   | X MAX   | Y MAX   |  |  |

| VOUT                                                   | 46         | 3111.66 | 4641.39 | 3251.61 | 4781.34 |  |  |

| VOUT                                                   | 47         | 2758.05 | 4641.39 | 2898    | 4781.34 |  |  |

| VOUT                                                   | 48         | 3111.66 | 4809.15 | 3251.61 | 4949.1  |  |  |

| VOUT                                                   | 49         | 2758.05 | 4809.15 | 2898    | 4949.1  |  |  |

| VOUT                                                   | 50         | 3111.66 | 4976.1  | 3251.61 | 5116.05 |  |  |

| VOUT                                                   | 51         | 2758.05 | 4976.1  | 2898    | 5116.05 |  |  |

Copyright © 2024 Texas Instruments Incorporated

7

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup> (2)

|                             |                                                                                    | MIN  | MAX       | UNIT |

|-----------------------------|------------------------------------------------------------------------------------|------|-----------|------|

| VIN                         | Input voltage                                                                      | -0.3 | 7.5       | V    |

| VOUT                        | Output voltage                                                                     | -0.3 | 7.5       | V    |

| EN, OVP                     | Enable and over voltage protection pins                                            | -0.3 | 7.5       | V    |

| CS, ILTIMER, RTIMER, IL, SS | Current sense, current limit timer, retry timer, current limit and soft start pins | -0.3 | VIN + 0.3 | V    |

| I <sub>MAX</sub>            | Maximum continuous switch current                                                  |      | 9         | А    |

| I <sub>PLS</sub>            | Maximum pulsed switch current (t≤5µs)                                              |      | 45        | А    |

| TJ                          | Maximum junction temperature                                                       | -55  | 150       | °C   |

| T <sub>stg</sub>            | Storage temperature                                                                | -65  | 150       | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground pin.

## 6.2 ESD Ratings

|                                            |                         |                                                                                | VALUE | UNIT |

|--------------------------------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                                          | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±4000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                   |                                               | MIN | MAX   | UNIT |

|-------------------|-----------------------------------------------|-----|-------|------|

| VIN               | Input voltage                                 | 1.5 | 7     | V    |

| SR <sub>VIN</sub> | Input voltage slew rate                       |     | 0.01  | V/µs |

| VOUT              | Output voltage                                | 0   | 7 (1) | V    |

| I <sub>MAX</sub>  | Maximum continuous switch current             |     | 6     | А    |

| TJ                | Operating junction temperature <sup>(2)</sup> | -55 | 125   | °C   |

(1) This maximum VOUT voltage is only applicable when the device is disabled (EN = Low). When the device is enabled (EN = High), the maximum VOUT voltage is the input voltage, VIN.

(2) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $[T_{A(max)}]$  is dependent on the maximum operating junction temperature  $[T_{J(max)}]$ , the maximum power dissipation of the device in the application  $[P_{D(max)}]$ , and the junction-to-ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the equation:  $T_{A(max)} = T_{J(max)} - (\theta_{JA} \times P_{D(max)})$ .

#### 6.4 Thermal Information

|                       |                                              | TPS7H2201-SP | TPS7H2201-SEP |      |

|-----------------------|----------------------------------------------|--------------|---------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | HKR (CFP)    | DAP (HTSSOP)  | UNIT |

|                       |                                              | 16 PINS      | 32 PINS       |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 72.3         | 23.5          |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 96.1         | 11.2          |      |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 42.1         | 5.4           | °C/W |

| Ψյт                   | Junction-to-top characterization parameter   | 3.3          | 0.1           | C/W  |

| Ψјв                   | Junction-to-board characterization parameter | 42.5         | 5.4           |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.6          | 0.5           |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics: All Devices

over operating free-air temperature range (unless otherwise noted)

|                              | PARAMETER                                | TEST CONDITION                                              | ONS                                                 | SUBGROUP<br>(1) | MIN  | ТҮР  | МАХ  | UNIT  |

|------------------------------|------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------|-----------------|------|------|------|-------|

| POWER SU                     | PPLIES AND CURRENTS                      |                                                             |                                                     | I               |      |      |      |       |

| VIN <sub>HUVLO</sub>         | Internal VIN UVLO voltage, rising        |                                                             |                                                     |                 |      | 1.32 |      | V     |

| VIN <sub>LUVLO</sub>         | Internal VIN UVLO voltage, falling       |                                                             |                                                     |                 |      | 1.23 |      | v     |

| HYST <sub>VIN-</sub><br>UVLO | Internal VIN UVLO hysteresis             |                                                             |                                                     |                 |      | 92   |      | mV    |

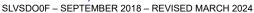

| Ι <sub>Q</sub>               | Quiescent current                        | $I_{OUT} = 0$ mA,<br>$V_{IN} = EN = 5$ V, CS resistor of 20 | ) kΩ to GND                                         | 1, 2, 3         |      | 2.4  | 6.5  | mA    |

|                              |                                          |                                                             | 1.5 V ≤ VIN ≤ 7 V                                   | 1, 2, 3         |      |      | 250  |       |

|                              |                                          |                                                             | VIN =1.5 V                                          | 1, 2, 3         |      | 3.27 |      | 1     |

|                              | VIN to VOUT forward leakage              | EN = VOUT = GND, measured                                   | VIN = 1.8 V                                         | 1, 2, 3         |      | 3.35 |      | - μΑ  |

| IF                           | current VO                               | VOUT current                                                | VIN= 3.3 V                                          | 1, 2, 3         |      | 3.62 |      |       |

|                              |                                          |                                                             | VIN = 5 V                                           | 1, 2, 3         |      | 4.11 |      |       |

|                              |                                          |                                                             | VIN = 7 V                                           | 1, 2, 3         |      | 6.82 |      |       |

|                              |                                          | EN = GND,<br>I <sub>OUT</sub> = 0 mA, measured VIN          | VIN = 5 V                                           | 1, 2, 3         |      | 0.4  | 3    | -     |

|                              |                                          |                                                             | VIN = 3.3 V                                         | 1, 2, 3         |      | 0.3  | 3    |       |

| I <sub>SD</sub> VIN          |                                          |                                                             | VIN = 1.8 V                                         | 1, 2, 3         |      | 0.2  | 3    |       |

|                              |                                          |                                                             | After TID = 100<br>krad, VIN = 1.8,<br>3.3, and 5 V | 1               |      |      | 3.1  |       |

| SOFT STAR                    | rt                                       | 1                                                           |                                                     | 1               |      |      |      |       |

| I <sub>SS</sub>              | Soft start charge current                | 1 V on SS pin                                               |                                                     | 1, 2, 3         |      | 65   | 83   | μA    |

| SR <sub>SS</sub>             | Soft start slew rate                     | SS pin floating, COUT = 10 µF                               |                                                     |                 |      | 295  |      | mV/μs |

| ENABLE A                     | ND UNDERVOLTAGE LOCKOUT (I               | EN/UVLO) INPUT                                              |                                                     |                 |      |      |      |       |

| V <sub>IHEN</sub>            | EN/UVLO threshold voltage, rising        |                                                             |                                                     | 1, 2, 3         | 0.56 | 0.61 | 0.65 | v     |

| V <sub>ILEN</sub>            | EN/UVLO threshold voltage, falling       |                                                             |                                                     | 1, 2, 3         | 0.47 | 0.51 | 0.55 | v     |

| HYST <sub>EN</sub>           | EN/UVLO hysteresis voltage               |                                                             |                                                     | 1, 2, 3         |      | 93   | 124  | mV    |

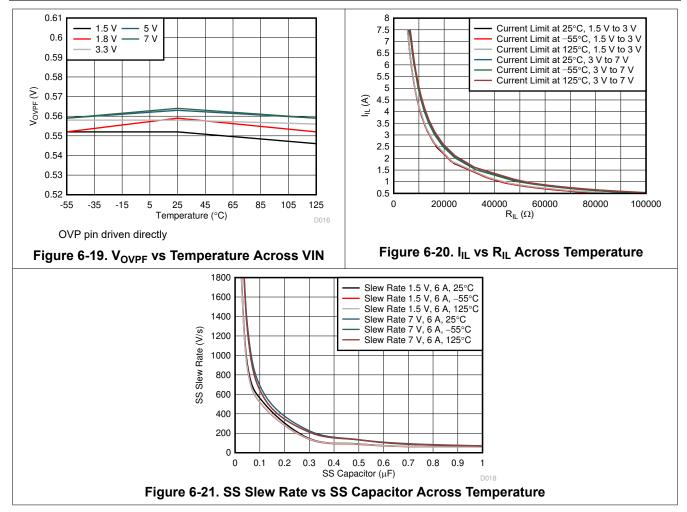

| t <sub>LOW</sub>             | EN signal low time during cycling        | RTIMER = GND, IL = 1 A, I <sub>VOUT</sub><br>= 2 A          | See Figure 7-1                                      | 9, 10, 11       | 20   |      |      | μs    |

| VIN <sub>EN</sub>            | VIN percentage for enable <sup>(2)</sup> |                                                             | -1-                                                 | 4, 5, 6         | 75%  |      |      |       |

| I <sub>EN</sub>              | EN pin input leakage current             | EN = VIN = 5 V                                              |                                                     | 1, 2, 3         |      |      | 12   | nA    |

## 6.5 Electrical Characteristics: All Devices (continued)

over operating free-air temperature range (unless otherwise noted)

|                                        | PARAMETER                             | TEST CONDITIONS                                                 | SUBGROUP<br>(1) | MIN                        | ТҮР  | МАХ       | UNIT |

|----------------------------------------|---------------------------------------|-----------------------------------------------------------------|-----------------|----------------------------|------|-----------|------|

| OVERVOLT                               | AGE PROTECTION (OVP)                  | 1                                                               |                 |                            |      |           |      |

| V <sub>OVPR</sub>                      | OVPR thresold voltage, rising         |                                                                 | 1, 2, 3         | 0.52                       | 0.57 | 0.63      | V    |

| V <sub>OVPF</sub>                      | OVPF threshold voltage, falling       |                                                                 | 1, 2, 3         | 0.5                        | 0.55 | 0.59      | V    |

| HYST <sub>OVP</sub>                    | OVP hysteresis voltage                | 1.6 V < VIN < 7 V                                               | 1, 2, 3         |                            | 20   | 55        | mV   |

| I <sub>OVP</sub>                       | OVP pin input leakage current         |                                                                 | 1, 2, 3         |                            |      | 15        | nA   |

| CURRENT L                              | IMIT AND CURRENT SENSE                |                                                                 | 1               |                            |      |           |      |

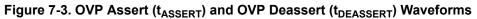

| t <sub>CSEN</sub>                      | Time for valid CS output after enable | C <sub>SS</sub> = 120 nF                                        | 9, 10, 11       |                            |      | 5         | ms   |

| Minimum VC                             | OUT current for valid CS output       |                                                                 | 1, 2, 3         | 750                        |      |           | mA   |

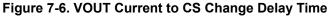

| VOUT currer                            | nt change to CS change delay time     | 0.5-A rising step, 100 mA/ $\mu$ s, 1.5 V $\leq$ VIN $\leq$ 7 V | 9, 10, 11       |                            | 16   | 74        | μs   |

| VOUT currer                            | nt change to CS change delay time     | 0.5-A falling step, 100 mA/ $\mu$ s, 1.5 V ≤ VIN ≤ 7 V          | 9, 10, 11       |                            | 16   | 73        | μs   |

| CS pin accur                           | асу                                   | 0.75 A ≤ I <sub>VOUT</sub> ≤ 7.5 A                              | 4, 5, 6         | -10%                       |      | 10%       |      |

| CS pin volta                           | ge                                    | $0.75 \text{ A} \le I_{\text{VOUT}} \le 7.5 \text{ A}$ , no OCP | 1, 2, 3         |                            | Ň    | √IN – 0.4 | V    |

|                                        |                                       | I <sub>VOUT</sub> ≤1A                                           | 1, 2, 3         | I <sub>VOUT</sub> +<br>0.5 |      |           |      |

| Current limit setting, I <sub>IL</sub> |                                       | 1A < I <sub>VOUT</sub> ≤ 3 A                                    | 1, 2, 3         | I <sub>VOUT</sub> + 1      |      |           | A    |

|                                        |                                       | I <sub>VOUT</sub> > 3 A                                         | 1, 2, 3         | I <sub>VOUT</sub> +<br>1.5 |      |           |      |

| Programmat                             | le current limit accuracy             | 1.5 V ≤ VIN ≤ 7 V                                               | 4, 5, 6         | -20%                       |      | 20%       |      |

| Fast trip off o                        | current limit                         | VIN = 5 V, 10-mΩ short in 10 µs                                 |                 |                            | 22   |           | А    |

| TIMERS                                 |                                       |                                                                 | 1               |                            |      |           |      |

| IILTIMER                               | ILTIMER charge current                |                                                                 | 1, 2, 3         | 0.7                        | 1    | 1.38      | μA   |

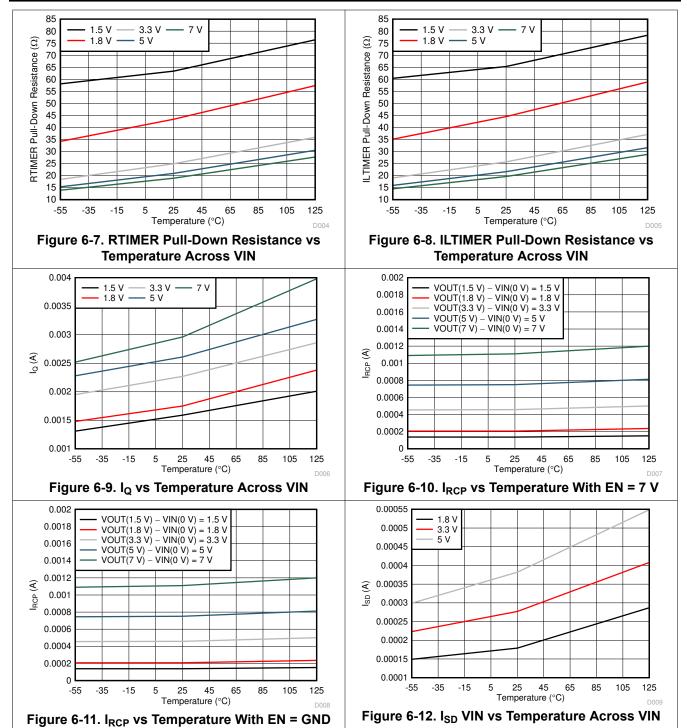

| PD <sub>ILTIMER</sub>                  | ILTIMER internal pull-down resistance | 40 mV on ILTIMER pin                                            | 1, 2, 3         |                            | 38   | 153       | Ω    |

| IRTIMER                                | RTIMER charge current                 |                                                                 | 1, 2, 3         | 0.7                        | 1    | 1.38      | μA   |

| PD <sub>RTIMER</sub>                   | RTIMER internal pull-down resistance  | 40 mV on RTIMER pin                                             | 1, 2, 3         |                            | 38   | 153       | Ω    |

| THERMAL S                              | HUTDOWN                               | ·                                                               |                 |                            |      | J. J. J.  |      |

| Thermal shu                            | tdown                                 | VIN = 5 V                                                       |                 |                            | 175  |           | °C   |

| Thermal shu                            | tdown hysteresis                      | VIN = 5 V                                                       |                 |                            | 20   |           | °C   |

(1) For subgroup definitions, see Quality Conformance Inspection table.

(2) VIN must be  $\geq$  75% of its final value before EN is asserted only if VIN<sub>SR</sub> > VOUT<sub>SR</sub>.

## 6.6 Electrical Characteristics: CFP and KGD Options

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                                    | TEST COND                                                                 | TIONS             | SUBGROUP <sup>(1)</sup> | MIN | TYP  | MAX | UNIT                                           |

|------------------|----------------------------------------------|---------------------------------------------------------------------------|-------------------|-------------------------|-----|------|-----|------------------------------------------------|

| POWER            | SUPPLIES AND CURRENTS                        |                                                                           |                   |                         |     |      |     |                                                |

| I <sub>RCP</sub> | Reverse current protection leakage current   | EN = 0 V, VIN = 0 to 7 V, VO<br>VOUT > VIN<br>EN = 7 V, VIN = 0 V, VOUT = |                   | 1, 2, 3                 |     | 0.45 | 2.5 | mA                                             |

|                  | NT LIMIT AND CURRENT SENSE                   | LIN = 7 V, VIN = 0 V, VOOT =                                              |                   |                         |     |      |     |                                                |

|                  | off off-time <sup>(2)</sup>                  | VIN = 5 V, C <sub>SS</sub> = 2.7 nF                                       |                   | 9, 10, 11               |     | 61   | 158 |                                                |

|                  | current limit timer (fast trip off current   | VIN = 5 V, $I_{VOUT}$ = 3 A, IL = 6<br>10-mΩ short in 10 µs               | A, ILTIMER = VIN, | 9, 10, 11               |     | 15   | 35  | μs                                             |

| RESIST           | ANCE CHARACTERISTICS                         |                                                                           |                   |                         |     |      |     |                                                |

|                  |                                              | –55°C                                                                     |                   |                         |     | 24   |     |                                                |

|                  |                                              |                                                                           | -40°C             | -                       |     |      | 26  | I                                              |

|                  |                                              | VIN = 7 V, I <sub>IL</sub> = 7.5 A                                        | 25°C              | 1, 2, 3                 |     | 31   | 34  | 1                                              |

|                  |                                              |                                                                           | 85°C              |                         | i   | 37   | 40  |                                                |

|                  |                                              |                                                                           | 125°C             |                         |     | 41   | 45  |                                                |

|                  |                                              | VIN = 5 V, I <sub>IL</sub> = 7.5 A                                        | –55°C             | 1, 2, 3                 |     |      | 26  | 1                                              |

|                  |                                              |                                                                           | -40°C             |                         |     |      | 27  | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- |

|                  |                                              |                                                                           | 25°C              |                         |     | 32   | 35  |                                                |

|                  |                                              |                                                                           | 85°C              |                         |     | 39   | 42  |                                                |

|                  |                                              |                                                                           | 125°C             |                         |     | 43   | 47  |                                                |

|                  |                                              | <sup>1</sup> VIN = 3.3 V, I <sub>IL</sub> = 7.5 A                         | –55°C             | 1, 2, 3                 |     |      | 28  |                                                |

|                  |                                              |                                                                           | -40°C             |                         |     |      | 30  |                                                |

| R <sub>ON</sub>  | ON-state resistance, lead length<br>= 2.5 mm |                                                                           | 25°C              |                         |     | 35   | 38  |                                                |

|                  |                                              |                                                                           | 85°C              |                         |     | 42   | 46  |                                                |

|                  |                                              |                                                                           | 125°C             |                         |     | 47   | 52  |                                                |

|                  |                                              |                                                                           | –55°C             | 1, 2, 3                 |     |      | 36  |                                                |

|                  |                                              |                                                                           | -40°C             |                         |     |      | 39  |                                                |

|                  |                                              | VIN = 1.8 V, I <sub>IL</sub> = 7.5 A                                      | 25°C              |                         |     | 45   | 51  |                                                |

|                  |                                              |                                                                           | 85°C              |                         |     | 55   | 62  |                                                |

|                  |                                              |                                                                           | 125°C             |                         |     | 61   | 70  |                                                |

|                  |                                              |                                                                           | –55°C             |                         |     |      | 44  | 1                                              |

|                  |                                              |                                                                           | -40°C             |                         |     |      | 48  | 1                                              |

|                  |                                              | VIN = 1.5 V, I <sub>IL</sub> = 7.5 A                                      | 25°C              | 1, 2, 3                 |     | 52   | 63  | -                                              |

|                  |                                              |                                                                           | 85°C              | 1  -                    |     | 63   | 77  |                                                |

|                  |                                              |                                                                           | 125°C             |                         |     | 70   | 87  | I                                              |

(1) For subgroup definitions, see Quality Conformance Inspection table.

(2) Bench verified; not tested in production

## 6.7 Electrical Characteristics: HTSSOP Option

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                  | TEST CONDITION                                                                 | IS                            | SUBGROUP <sup>(1)</sup> | MIN | TYP  | MAX | UNIT                                           |

|----------------------|--------------------------------------------|--------------------------------------------------------------------------------|-------------------------------|-------------------------|-----|------|-----|------------------------------------------------|

| POWER                | SUPPLIES AND CURRENTS                      |                                                                                |                               |                         |     |      |     |                                                |

|                      |                                            |                                                                                | SEP                           |                         |     | 0.45 | 0.5 |                                                |

|                      |                                            | EN = 0 V, VIN = 0 to 7 V, VOUT =                                               | QMLP pre TID                  |                         |     | 0.45 | 2.5 |                                                |

|                      | Reverse current protection                 | 0 to 7 V for VOUT > VIN                                                        | QMLP, after<br>TID = 100 krad |                         |     | 0.45 | 20  |                                                |

| I <sub>RCP</sub>     | leakage current                            |                                                                                | SEP                           | - 1, 2, 3               |     | 0.45 | 25  | mA                                             |

|                      |                                            | EN = 7 V, VIN = 0 V, VOUT = 0 to                                               | QMLP pre TID                  |                         |     | 0.45 | 2.5 |                                                |

|                      |                                            | 7 V                                                                            | QMLP, after<br>TID = 100 krad |                         |     | 0.45 | 20  |                                                |

| CURREI               | NT LIMIT AND CURRENT SENSE                 | 1                                                                              |                               | њ                       |     |      |     |                                                |

| Fast trip            | off off-time                               | VIN = 5 V, C <sub>SS</sub> = 2.7 nF                                            |                               | 9, 10, 11               |     | 61   |     |                                                |

| Internal (<br>limit) | current limit timer (fast trip off current | VIN = 5 V, $I_{VOUT}$ = 3 A, IL = 6 A, IL<br>10-m $\Omega$ short in 10 $\mu$ s | TIMER = VIN,                  | 9, 10, 11               |     | 15   |     | μs                                             |

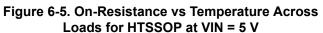

| RESIST               | ANCE CHARACTERISTICS                       |                                                                                |                               | 1                       |     |      |     |                                                |

|                      |                                            |                                                                                | –55°C                         |                         |     | 15.9 | 17  |                                                |

|                      |                                            |                                                                                | -40°C                         |                         |     | 16.9 |     | -                                              |

|                      |                                            |                                                                                | 25°C                          | 1, 2, 3                 |     | 19.9 | 21  |                                                |

|                      |                                            |                                                                                | 85°C                          |                         |     | 22.9 |     |                                                |

|                      |                                            |                                                                                | 125°C                         |                         |     | 25   | 27  |                                                |

|                      |                                            | VIN = 5 V, I <sub>IL</sub> = 7.5 A                                             | –55°C                         |                         |     | 17   | 18  | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- |

|                      |                                            |                                                                                | -40°C                         |                         |     | 18   |     |                                                |

|                      |                                            |                                                                                | 25°C                          | 1, 2, 3                 |     | 21.4 | 23  |                                                |

|                      |                                            |                                                                                | 85°C                          |                         |     | 24.8 |     |                                                |

|                      |                                            |                                                                                | 125°C                         |                         |     | 27   | 29  |                                                |

|                      |                                            | VIN = 3.3 V, I <sub>IL</sub> = 7.5 A                                           | –55°C                         | 1, 2, 3                 |     | 19.2 | 21  |                                                |

|                      |                                            |                                                                                | -40°C                         |                         |     | 20.4 |     |                                                |

| R <sub>ON</sub>      | ON-state resistance                        |                                                                                | 25°C                          |                         |     | 24.5 | 26  |                                                |

|                      |                                            |                                                                                | 85°C                          |                         |     | 28.5 |     |                                                |

|                      |                                            |                                                                                | 125°C                         | 1                       |     | 31.2 | 33  |                                                |

|                      |                                            |                                                                                | –55°C                         |                         |     | 27.1 | 29  |                                                |

|                      |                                            |                                                                                | -40°C                         |                         |     | 28.7 |     |                                                |

|                      |                                            | VIN = 1.8 V, I <sub>IL</sub> = 7.5 A                                           | 25°C                          | 1, 2, 3                 |     | 34.9 | 37  |                                                |

|                      |                                            |                                                                                | 85°C                          |                         |     | 41   |     |                                                |

|                      |                                            |                                                                                | 125°C                         | 1                       |     | 44.9 | 48  |                                                |

|                      |                                            |                                                                                | –55°C                         |                         |     | 33   | 36  |                                                |

|                      |                                            |                                                                                | -40°C                         | 1                       |     | 35   |     | -                                              |

|                      |                                            | VIN = 1.5 V, I <sub>IL</sub> = 7.5 A                                           | 25°C                          | 1, 2, 3                 |     | 42.7 | 46  |                                                |

|                      |                                            |                                                                                | 85°C                          | 1                       |     | 46.2 |     |                                                |

|                      |                                            |                                                                                | 125°C                         | 1                       |     | 55   | 59  |                                                |

(1) For subgroup definitions, see Quality Conformance Inspection table.

## 6.8 Switching Characteristics (All Devices)

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                      | TEST CONDITIONS                                 | MIN | ТҮР  | MAX | UNIT |

|-----------------------|----------------------------------------------------------------|-------------------------------------------------|-----|------|-----|------|

| VIN = EN =            | /IN = EN = 5 V, T <sub>A</sub> = 25°C (unless otherwise noted) |                                                 |     |      |     |      |

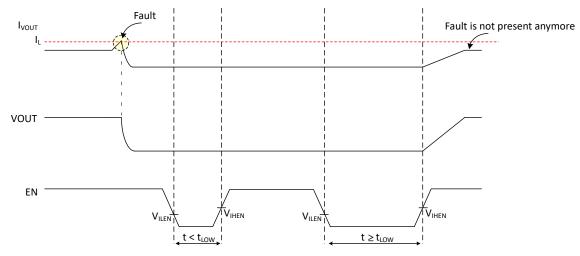

| t <sub>ON</sub>       | Turn-on time                                                   | $R_L$ = 10 Ω, $C_L$ = 10 μF, $C_{SS}$ = 1000 pF |     | 208  |     | μs   |

| t <sub>OFF</sub>      | Turn-off time                                                  | $R_L$ = 10 Ω, $C_L$ = 10 µF, $C_{SS}$ = 1000 pF |     | 60   |     | μs   |

| t <sub>F</sub>        | VOUT fall time                                                 | $R_L$ = 10 Ω, $C_L$ = 10 µF, $C_{SS}$ = 1000 pF |     | 90   |     | μs   |

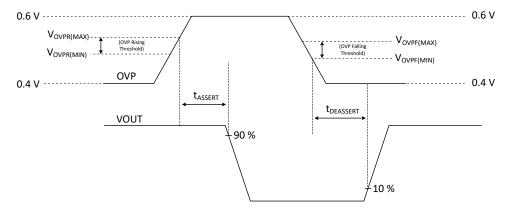

| t <sub>ASSERT</sub>   | OVP assert time                                                | $R_L$ = 10 Ω, $C_L$ = 10 µF, $C_{SS}$ = 1000 pF |     | 4.5  |     | μs   |

| t <sub>DEASSERT</sub> | OVP deassert time                                              | $R_L$ = 10 Ω, $C_L$ = 10 µF, $C_{SS}$ = 1000 pF |     | 9.6  |     | μs   |

| VIN = EN =            | 1.5 V, T <sub>A</sub> = 25°C (unless otherw                    | ise noted)                                      |     |      | ·   |      |

| t <sub>ON</sub>       | Turn-on time                                                   | $R_L$ = 10 Ω, $C_L$ = 10 μF, $C_{SS}$ = 1000 pF |     | 173  |     | μs   |

| t <sub>OFF</sub>      | Turn-off time                                                  | $R_L$ = 10 Ω, $C_L$ = 10 µF, $C_{SS}$ = 1000 pF |     | 64   |     | μs   |

| t <sub>F</sub>        | VOUT fall time                                                 | $R_L$ = 10 Ω, $C_L$ = 10 µF, $C_{SS}$ = 1000 pF |     | 70   |     | μs   |

| t <sub>ASSERT</sub>   | OVP assert time                                                | $R_L$ = 10 Ω, $C_L$ = 10 µF, $C_{SS}$ = 1000 pF |     | 2.65 |     | μs   |

| t <sub>DEASSERT</sub> | OVP deassert time                                              | $R_L$ = 10 Ω, $C_L$ = 10 µF, $C_{SS}$ = 1000 pF |     | 6.56 |     | μs   |

## 6.9 Quality Conformance Inspection

MIL-STD-883, Method 5005 - Group A

| SUBGROUP | DESCRIPTION         | TEMP (°C) |

|----------|---------------------|-----------|

| 1        | Static tests at     | 25        |

| 2        | Static tests at     | 125       |

| 3        | Static tests at     | -55       |

| 4        | Dynamic tests at    | 25        |

| 5        | Dynamic tests at    | 125       |

| 6        | Dynamic tests at    | -55       |

| 7        | Functional tests at | 25        |

| 8A       | Functional tests at | 125       |

| 8B       | Functional tests at | -55       |

| 9        | Switching tests at  | 25        |

| 10       | Switching tests at  | 125       |

| 11       | Switching tests at  | -55       |

105

85

105

125

125

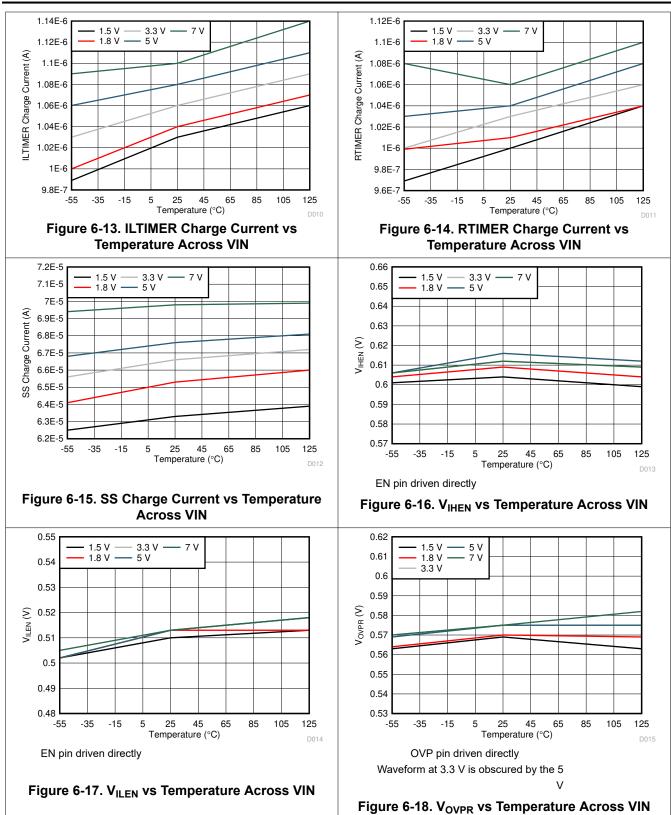

### 6.10 Typical Characteristics

Copyright © 2024 Texas Instruments Incorporated

Figure 6-6. On-Resistance vs Temperature Across

Loads for HTSSOP at VIN = 7 V

85

105

125

14

## 7 Parameter Measurement Information

Figure 7-1. EN Signal Low Time to Restart Device (t<sub>LOW</sub>)

Figure 7-2. Turn-On (t<sub>ON</sub>), Turn-Off (t<sub>OFF</sub>) and VOUT Fall Time (t<sub>F</sub>) Waveforms

## 8 Detailed Description

## 8.1 Overview

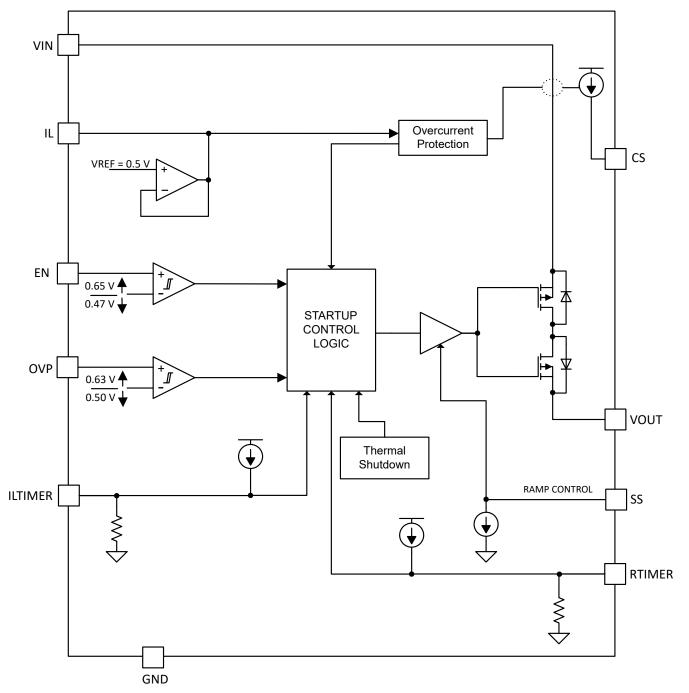

The TPS7H2201 device is a single channel, 6-A eFuse with a programmable slew rate for applications that require specific rise-time as well as programmable current limit for protection purposes. In addition, the TPS7H2201 features a reverse current protection capability for power distribution applications.

### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Enable, Undervoltage, and Overvoltage Protection

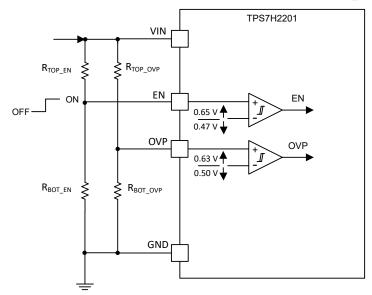

Figure 8-1 shows how resistor dividers from VIN connected to the EN and OVP pins can be used to set the UVLO and OVP trip voltages. The EN pin controls the ON and OFF state of the internal FET. A voltage at this pin greater than  $V_{IHEN}$  turns on the FET and a voltage less than  $V_{ILEN}$  turns it off. The addition of an external resistor divider from VIN allows the EN pin to configure a different enable rising voltage or an undervoltage monitor (UVLO) based on the  $V_{IHEN}$  and  $V_{ILEN}$  specifications respectively. Typically, applications are optimized to either configure the enable rising voltage or the UVLO threshold. As an example, Equation 1 can be used to calculate the UVLO trip point fixing  $R_{TOP EN} = 100 \text{ k}\Omega$ .

In a similar way to the EN pin, the overvoltage protection (OVP) feature of the device can be configured using a resistor divider from VIN connected to the OVP pin. The trip voltage for the OVP has to be less than the absolute maximum VIN voltage. A voltage at the OVP pin greater than  $V_{OVPR}$  will trip the OVP feature and will turn off the FET and a voltage less than  $V_{OVPF}$  will keep the FET on. If this feature is not desired, the OVP pin should be grounded. Equation 2 can be used to calculated the rising OVP trip point fixing  $R_{TOP_OVP} = 100 \text{ k}\Omega$ .

Figure 8-1. UVLO and OVP Thresholds Set by Resistor Dividers

$$R_{BOT\_EN}(k\Omega) \le \frac{47}{V_{UVLO\_TRIP}(V) - 0.47}$$

$$R_{BOT\_OVP}(k\Omega) \ge \frac{63}{V_{OVP\_TRIP}(V) - 0.63}$$

(2)

#### 8.3.2 Adjustable Rise Time

An external capacitor,  $C_{SS}$ , connected between the VOUT and SS pins sets the slew rate. The desired slew rate VOUT<sub>SR</sub> is determined by  $t_r$ , the rise time in seconds, and  $\Delta V$ , the change in VOUT voltage in Volts as shown in Equation 3.

$$VOUT_{SR}(V/s) = \frac{\Delta V_{OUT}(V)}{t_r(s)}$$

(3)

In order to avoid false trips due to the programmable current limit, the desired slew rate must be less than VOUT<sub>SR,MAX</sub> as shown in Equation 4, where  $I_L$  is the programmed current limit,  $I_{VOUT}$  is the normal operation current flowing through the switch, and  $C_{OUT}$  is the output capacitor.

$$VOUT_{SR,MAX} (V/s) < \frac{0.8 \times I_L(A) - 0.95 \times I_{VOUT}(A)}{C_{OUT}(F)}$$

(4)

Once the slew rate has been calculated and meeting the constraint in Equation 4, the  $C_{SS}$  capacitor is then calculated using Equation 5 for VIN < 3-V and IOUT  $\geq$  3-A applications. For all other applications, use Equation 6.

$$C_{SS}(\mu F) = \frac{45}{\text{VOUT}_{SR}(V/s)}$$

(5)

for VIN < 3 V and IOUT  $\ge$  3 A

$$C_{SS}(\mu F) = \frac{65}{\text{VOUT}_{SR}(V/s)}$$

(6)

for all other conditions

#### 8.3.3 Programmable Current Limiting

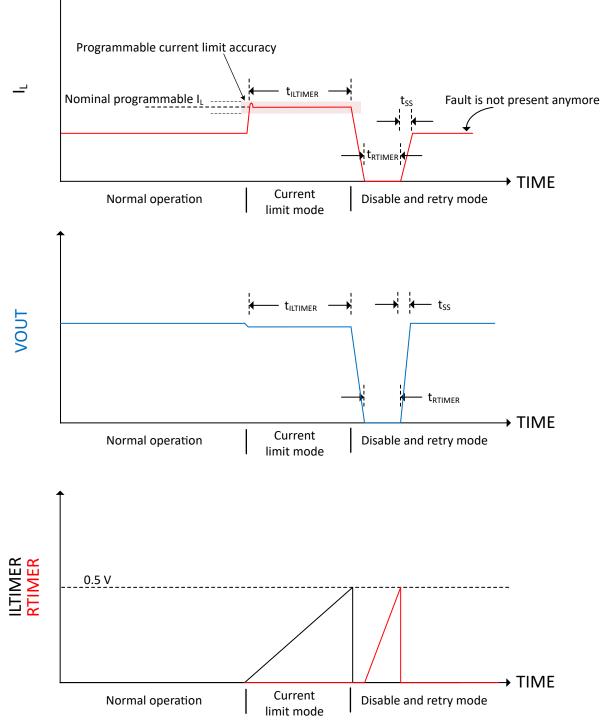

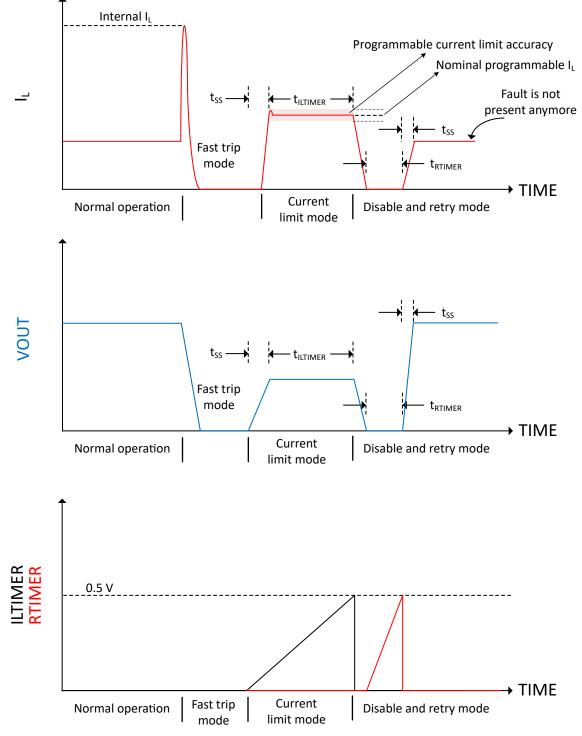

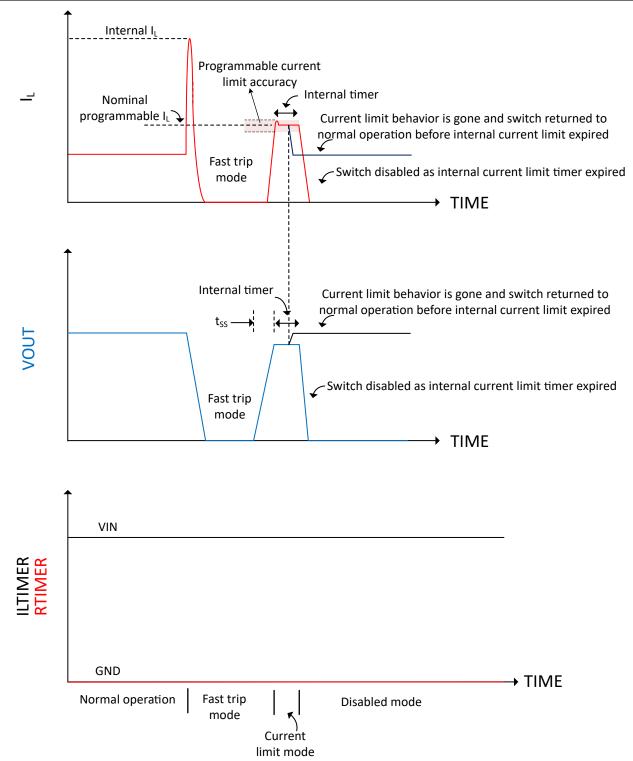

A current limit can be programmed using an external resistor connected from the IL pin to GND. This programmed current limit ( $\pm 20\%$  accurate) refers to the continuous current through the device and therefore, when operated at its maximum current rating (6 A), the programmed current limit needs to be set 20% higher. As shown in Figure 8-2, a current limit event of this nature is defined as a soft short. The resistor value R<sub>IL</sub>, can be calculated using Equation 7 for VIN  $\leq$  3 V, and Equation 8 for VIN > 3 V, where I<sub>L</sub> is the programmed current limit value in amperes. This programmable current limiting feature is different from the internal current limiting activated during fast trip mode as shown in Figure 8-3. A current limit event in this case is defined as a hard short and this current limit (typical of 22 A) cannot be programmed.

$$R_{\rm IL}(\Omega) = \frac{45500}{I_{\rm L}(A)} \tag{7}$$

for VIN  $\leq$  3 V

$$R_{\rm IL}(\Omega) = \frac{49000}{I_{\rm L}(A)}$$

for VIN > 3 V

#### 8.3.4 Programmable Fault Timer

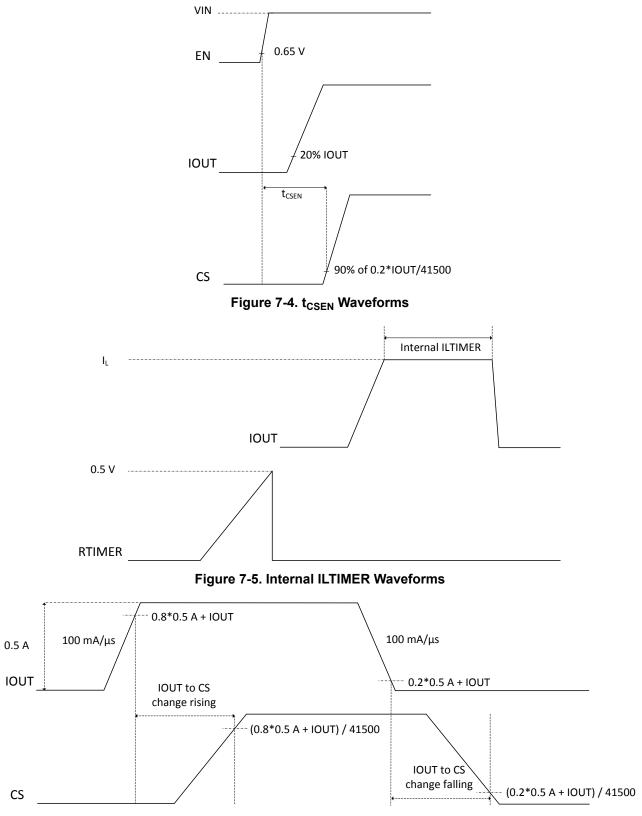

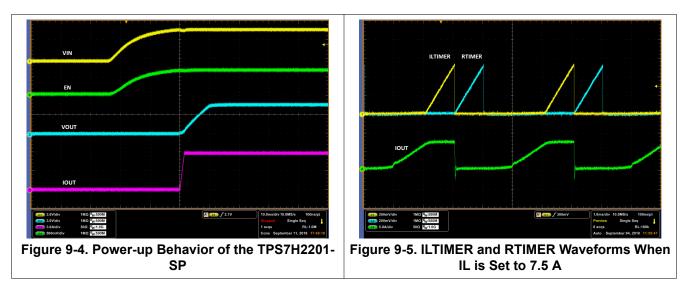

A capacitor connected from the ILTIMER pin to GND determines the programmable current limit fault time duration. The ILTIMER pin will charge the capacitor to 0.5 V during an overload condition and will discharge it otherwise through an internal pull down resistance. The time that the device will be in current limit before turning off is configured by C<sub>ILTIMER</sub> and the time can be calculated using Equation 9. Connecting this pin to VIN will cause the device to be disabled once the internal current limit timer expires as shown in Figure 7-5. However, connecting it to GND will disable the internal timer functionality completely and therefore, in the case of a short, the device will remain at the programmed current limit indefinitely. When using the internal timer, the programmable current limit may not have time to settle to its programmed value. Because of this, the programmable current limit could briefly fall outside of its defined accuracy threshold. The fast trip off current limit, however, will remain valid.

(8)

$$t(\mu s) = \frac{C(pF)}{2}$$

(9)

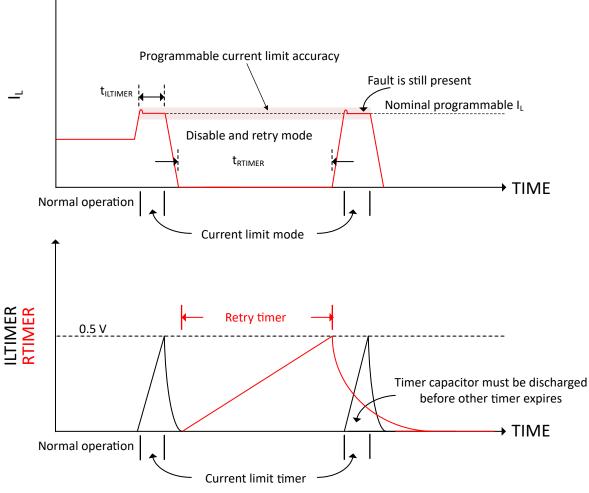

The time that the device remains disabled after the current limit timer expires is configurable through a capacitor connected from the RTIMER pin to GND. The RTIMER pin will charge the capacitor to 0.5 V after the switch is turned off and will discharge it otherwise. The time can be calculated using Equation 9. Connecting this pin to GND will keep the device disabled and it will require the device to be enabled by cycling the EN pin (Refer to EN Signal Low Time to Restart Device  $(t_{LOW})$ ). The behavior of the ILTIMER and RTIMER pins for a soft short, hard short and internal timer conditions are shown in Figure 8-2, Figure 8-3, and Figure 8-4, respectively. Please notice that Figure 8-2 and Figure 8-3 assume the fault is not present after the switch has been disabled and enabled again (retry mode). If the fault is present after the retry mode, the device will go into current limit mode and this cycle will repeat until the fault is no longer present.

Table 8-1 and Table 8-2 summarizes the fault duration time and retry time based on the pin conditions.

| ILTIMER Pin Condition                    | Fault Time Duration During Overload |

|------------------------------------------|-------------------------------------|

| VIN                                      | 15 μs (typ), 35 μs (max)            |

| GND                                      | Indefinitely                        |

| Capacitor to GND (C <sub>ILTIMER</sub> ) | Equation 9                          |

| Float                                    | Not valid (do not float pin)        |

#### Table 8-1. Fault Time Duration for ILTIMER Pin Conditions

#### Table 8-2. Time to Retry During an Overload Condition for RTIMER Pin Conditions

| RTIMER Pin Condition                    | Time to Retry During an Overload                                |  |  |

|-----------------------------------------|-----------------------------------------------------------------|--|--|

| GND                                     | Disabled (switch off) until EN is low for t > $t_{LOW}$ (20 µs) |  |  |

| Capacitor to GND (C <sub>RTIMER</sub> ) | Equation 9                                                      |  |  |

| Float                                   | Not valid (do not float pin)                                    |  |  |

Figure 8-2. Soft Short Programmable Fault Timer Operation Connecting Capacitors to ILTIMER and RTIMER Pins

Figure 8-3. Hard Short Programmable Fault Timer Operation Connecting Capacitors to ILTIMER and RTIMER Pins

# Figure 8-4. Programmable Fault Timer Operation Using the Internal Current Limit Timer and Disabling the Retry Mode

The programmable fault timers, ILTIMER and RTIMER, should be set in such a way that the capacitor for one timer is discharged before the other timer expires to ensure proper operation. In the specific case of using the internal ILTIMER, the RTIMER capacitor should be sized such that it is discharged before the internal ILTIMER expires, assuming the fault is still present. Figure 8-5 shows a situation where this constraint is not

met as the RTIMER is much larger than the ILTIMER and therefore, the  $C_{\text{RTIMER}}$  is not discharged before the  $C_{\text{ILTIMER}}$  reaches 0.5 V, which is when the ILTIMER will expire. In order to avoid this situation, the constraint shown in Equation 10 must be met. Using this equation, once a capacitor for a timer has been selected (C<sub>1</sub> in Equation 10), the maximum value for the capacitor of the second timer can be determined. The internal pull-down resistance for each of the timers can be found in the *Electrical Characteristics: All Devices* table. For the situation shown in Figure 8-5, C<sub>1</sub> and R<sub>PD1</sub> in Equation 10 correspond to the RTIMER.

$$C_1(\mu F) < \frac{C_2(pF)}{8 \times R_{PD1}(\Omega)}$$

(10)

#### 8.3.5 Current Sense

This pin will output a current proportional to the output current of the switch for current sensing applications. A resistor to GND will convert this current to voltage for current sensing purposes. The output current will be the switch current divided by 41,500. The CS pin will have a valid output 5 ms after the device has been enabled. To operate the current sense in the linear region, the voltage at the CS pin at the application maximum load, should not exceed the CS pin voltage sepcification (VIN - 400 mV).

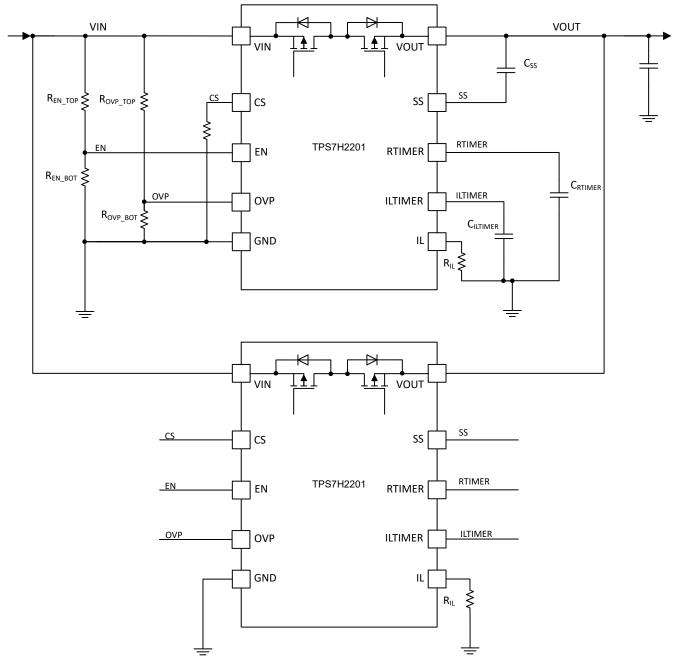

## 8.3.6 Parallel Operation

The TPS7H2201 can be configured in parallel operation either to increase the current capability, up to 12 A, or to reduce the on-state resistance. In this case, all pins are shared as shown in Figure 8-6, except the current limit

Copyright © 2024 Texas Instruments Incorporated

resistor (R<sub>IL</sub>) for proper operation of the internal current limit loop. The current limiting resistors must be sized as described in the *Programmable Current Limiting* section.

Figure 8-6. Parallel Configuration to Reduce Resistance or Increase Current Capability

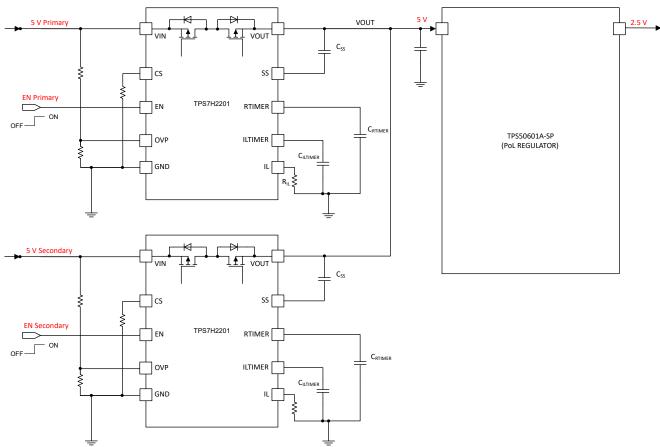

#### 8.3.7 Reverse Current Protection