# Application Report

# Protection for HART I/O in Analog Input and Output Modules with TPS2661x

George Thottan

#### **ABSTRACT**

Industrial equipment such as Programmable Logic Controller (PLC) collects data from sensors, analyze this data, and controls the industrial process through actuators. One way of collecting data from different sensors is through current loops. The current output of sensor is measured by converting the data into a voltage using a burden resistor. PLC also uses a hybrid communication protocol named Highway Addressable Remote Transducer (HART) to transmit diagnostic or calibration information similar to control variables. HART uses a 1.2kHz or 2.2Khz carrier signal to modulate the data bits being transmitted. The advantage of using HART is that it can be used over legacy 4 – 20mA instrumentation current loops, sharing the same pair of wires. This application note describes the use of TPS2661x current loop protector in the protection of analog current loops while supporting the HART protocol.

#### **Table of Contents**

| 1 Overview of a HART Enabled Analog Input Module               | 2 |

|----------------------------------------------------------------|---|

| 2 Protection Provided by TPS2661 to Analog Input Module        |   |

| 2.1 Overload Protection                                        |   |

| 2.2 Output Hot Short and Input Hot Plug                        |   |

| 2.3 Miswiring on Input                                         |   |

| 2.4 Input Under Voltage Protection                             | 3 |

| 3 Protection Provided by TPS2661 to Analog Output Module (AOM) | 4 |

| 3.1 Miswiring on Output                                        | 4 |

| 3.2 Output under voltage protection                            | 4 |

| 4 HART Tests Done on TPS2661x                                  |   |

| 5 Challenges Using Discrete Solution Instead of TPS2661x       | 6 |

| List of Figures                                                |   |

| Figure 1-1. Analog Input Module with HART                      |   |

| Figure 2-1. Protection for Analog Input with TPS2661x          |   |

| Figure 3-1. Analog Output Protection with TPS2661x             |   |

| Figure 4-1. 1.2Khz HART Signal Through TPS2661x                | 5 |

| Figure 4-2. 2.2Khz HART Signal Through TPS2661x                | 5 |

| List of Tables                                                 |   |

| Table 4-1. Ascending Order HART Data                           |   |

| Table 4-2. Descending Order HART Data                          | 6 |

| Trademarks                                                     |   |

All trademarks are the property of their respective owners.

### 1 Overview of a HART Enabled Analog Input Module

A PLC uses a HART enabled analog input module (AIM) to communicate with the field device in real-time. A HART enabled analog input module consists of an ADC and sense resistor to measure the analog current, and a HART modem to modulate and demodulate the HART data. The HART communication protocol is a master/ slave communication scheme. The input module acts as the master and sends requests for data to the slave transmitter or field device. The slave transmitter regulates the loop current and transmits HART as AC coupled 1mApp sinusoidal waveform over the DC current loop that is converted to a voltage signal by the burden resistor and demodulated by the HART modem at the analog input module. When the analog input module transmits HART, it directly couples the voltage signal to the burden resistor, creating a HART voltage waveform that is demodulated by the HART modem in the field device.

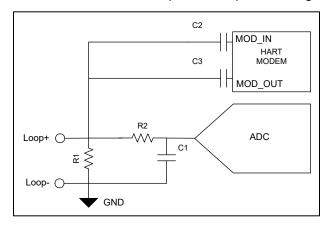

Figure 1-1 shows a simplified circuit diagram of a HART enabled analog input module. When the current flows across the load resistor, R1, a proportional voltage is induced across R1. This voltage is equal to the loop current multiplied by the load resistance. The ADC samples and converts this voltage into a digital value that can be read by a microcontroller. R2 and C1 form a simple low-pass filter to remove out-of band noise present at the ADC input. C2 and C3 isolate the DC from the modem input and output to the high side of the load resistor.

Figure 1-1. Analog Input Module with HART

## 2 Protection Provided by TPS2661 to Analog Input Module

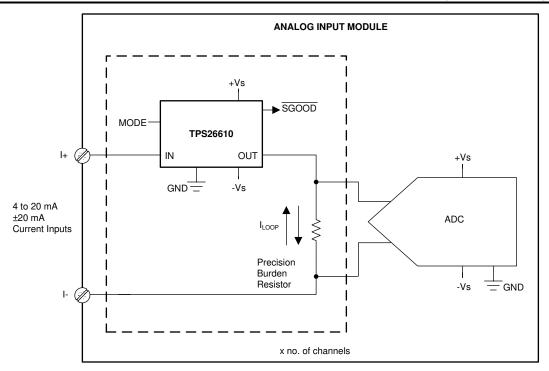

TPS2661x provides Universal Input protection for ±20 mA, 0 to 20 mA, 4-20 mA. Figure 2-1 shows an analog input module with TPS2661x current loop protector. TPS2661x provides the over current, over voltage and surge protection needed for the Analog input modules. This device offers protection up to a voltage of +/- 50V, while supporting operation on lower power supplies because of a low Rds on of 7.50hm. All these protection benefits are offered while still being HART compliant. The low leakage currents from the current loop helps it to maintain the integrity of the data being transmitted in the form of an analog dc current while allowing the modulated ac current on top of it in the form of HART.

Figure 2-1. Protection for Analog Input with TPS2661x

#### 2.1 Overload Protection

The TPS2661x devices feature a fixed bidirectional over current threshold of 32-mA (IOL) typical. It can also allow 2 times the IOL for limited time depending on the mode of operation. If the current tries to exceed the IOL limit, the device regulates the current and eventually reduce the output voltage. The power dissipation across the device during current regulation will be (VIN - VOUT) x IOUT and this could heat up the device and lead to thermal shutdown. The device does auto retry to power up post that and eventually power up if the overload condition passes.

#### 2.2 Output Hot Short and Input Hot Plug

TPS2661x provides protection against hot short preventing excessive current flow and damage to the AIM in the event of a load resistor short or a current loop short. It also provides protection during a hot plug event. In the event of a short or a high voltage hot plug, there is a rapid buildup of load current. Due to limited bandwidth, the current limit amplifier cannot respond quickly to this. The device features a fast trip circuitry. It quickly responds to a rapid increase in load current in the event of short and turns off the internal FET, cutting off the load current. Post FET turn off, the device turns back on slowly, allowing the current-limit loop to regulate the output current to current limit

#### 2.3 Miswiring on Input

In an industrial application, it is possible that a field power supply can be miswired to a current input. During miswiring to field power source, a large voltage can appear across the ADC inputs, burden resistor or current limiting element and burn it. TPS2661x clamps the input voltage to the system power rail and provides current limiting feature to avoid any damages caused by this miswiring.

#### 2.4 Input Under Voltage Protection

The TPS2661x devices provide protection from under-voltage events on IN pin by turning off the internal FETs and cutting off the signal path whenever VIN goes below Undervoltage Protection Threshold Falling. The signal path through TPS2661x is restored again when VIN goes above Undervoltage Protection Threshold Falling – undervoltage Hysteresis

# 3 Protection Provided by TPS2661 to Analog Output Module (AOM)

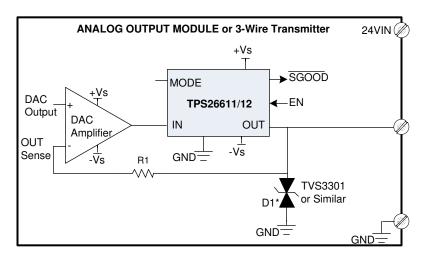

Programmable logic controller (PLC) applications require a full function, flexible, programmable analog output solution. Figure 3-1 shows an analog output module. It hosts a DAC which converts the digital data and control instructions from the PLC MCU to analog data for the downstream actuators or indicators. Most of the AOM's will be HART compatible to communicate with the on-field sensors used for system diagnostics. A HART enabled analog output module consists of a HART modem which will demodulate the ac coupled HART signals.

TPS2661x can be used for protection of analog output module against any high voltage field miswiring. The out-pin voltage is monitored with respect to the +Vs/-Vs supply voltages. If the OUT voltage goes outside the +Vs/-Vs supply rails, the FETs cutoff current conduction path and protects the whole system.

Figure 3-1. Analog Output Protection with TPS2661x

# 3.1 Miswiring on Output

The TPS2661x devices provide protection from over-voltage events on OUT pin by turning off the internal Pass FETs and cutting off the signal path whenever VOUT goes above Overvoltage Protection Threshold, Rising. The signal path through TPS2661x is restored again when VOUT goes below Overvoltage Protection Threshold, Rising – Overvoltage hysteresis

#### 3.2 Output under voltage protection

The TPS2661x devices provide protection from under-voltage events on OUT pin by turning off the internal FETs and cutting off the signal path whenever VOUT goes below Undervoltage Protection Threshold Falling. The signal path through TPS2661x is restored again when VOUT goes above Undervoltage Protection Threshold Falling – undervoltage Hysteresis

# 4 HART Tests Done on TPS2661x

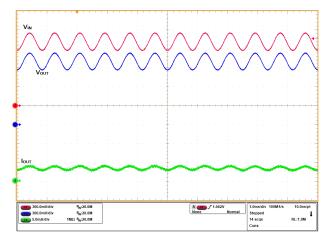

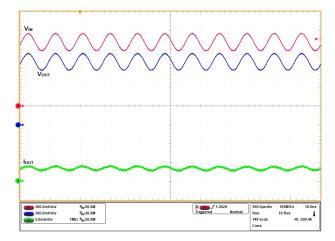

To test the performance of TPS2661x on HART protocol, the approach was to check the impact TPS2661x have on the loop current and the HART communication bits that were being transmitted. To figure the possibility of bit error being introduced by TPS2661x, multiple strategies were adopted in putting together the data set for the test. The data set covered the possibility of bit swap and bit flip errors being introduced by TPS2661x leakage currents. A sample data set is shown in Figure 4-1 and Figure 4-2. The reference data point will be HART transmission between HART transceivers without the Loop current protector. This data would be compared with the data received after adding the TPS2661x current loop protector in the communication loop. Tests were performed with different dc loop current settings.

Data set included the following:

- Single byte transmission

- · Transmission of byte sequence in ascending order from 00 to FF

- Transmission of byte sequence in descending order from FF to 00

Results of the tests proved that, the low leakage current feature helped TPS2661x to provide the required protection without interfering with the analog dc loop current while allowing the HART communication. No bit flip or bit swap errors were also observed on HART communication with TPS2661x inserted in the communication loop. Figure 4-1 and Figure 4-2 show the HART communication through TPS2661x for a 0 and 1 transmission. Table 4-1 and Table 4-2 provide the HART data transmission results with TPS2661x device.

Figure 4-1. 1.2Khz HART Signal Through TPS2661x

Figure 4-2. 2.2Khz HART Signal Through TPS2661x

Table 4-1. Ascending Order HART Data

| Write Byte | Read Byte        | Error Byte | Loop Current  | Write Byte | Read Byte | Error Byte | Loop Current  |  |  |

|------------|------------------|------------|---------------|------------|-----------|------------|---------------|--|--|

|            | Without TPS2661x |            |               |            | With TF   | S2661x     |               |  |  |

| 0          | 0                | No Error   | 4, 2.5, 7.5mA | 0          | 0         | No Error   | 4, 2.5, 7.5mA |  |  |

| 1          | 1                | No Error   | 4, 2.5, 7.5mA | 1          | 1         | No Error   | 4, 2.5, 7.5mA |  |  |

| 2          | 2                | No Error   | 4, 2.5, 7.5mA | 2          | 2         | No Error   | 4, 2.5, 7.5mA |  |  |

| 3          | 3                | No Error   | 4, 2.5, 7.5mA | 3          | 3         | No Error   | 4, 2.5, 7.5mA |  |  |

| 4          | 4                | No Error   | 4, 2.5, 7.5mA | 4          | 4         | No Error   | 4, 2.5, 7.5mA |  |  |

| 5          | 5                | No Error   | 4, 2.5, 7.5mA | 5          | 5         | No Error   | 4, 2.5, 7.5mA |  |  |

| 6          | 6                | No Error   | 4, 2.5, 7.5mA | 6          | 6         | No Error   | 4, 2.5, 7.5mA |  |  |

| 7          | 7                | No Error   | 4, 2.5, 7.5mA | 7          | 7         | No Error   | 4, 2.5, 7.5mA |  |  |

| 8          | 8                | No Error   | 4, 2.5, 7.5mA | 8          | 8         | No Error   | 4, 2.5, 7.5mA |  |  |

| 9          | 9                | No Error   | 4, 2.5, 7.5mA | 9          | 9         | No Error   | 4, 2.5, 7.5mA |  |  |

| Α          | Α                | No Error   | 4, 2.5, 7.5mA | Α          | Α         | No Error   | 4, 2.5, 7.5mA |  |  |

| В          | В                | No Error   | 4, 2.5, 7.5mA | В          | В         | No Error   | 4, 2.5, 7.5mA |  |  |

Table 4-2. Descending Order HART Data

| Table 4 2. Beecenang erael 11/4(1) Bata |                  |            |               |               |           |            |               |  |  |

|-----------------------------------------|------------------|------------|---------------|---------------|-----------|------------|---------------|--|--|

| Write Byte                              | Read Byte        | Error Byte | Loop Current  | Write Byte    | Read Byte | Error Byte | Loop Current  |  |  |

|                                         | Without TPS2661x |            |               | With TPS2661x |           |            |               |  |  |

| FF                                      | FF               | No Error   | 4, 2.5, 7.5mA | FF            | FF        | No Error   | 4, 2.5, 7.5mA |  |  |

| FE                                      | FE               | No Error   | 4, 2.5, 7.5mA | FE            | FE        | No Error   | 4, 2.5, 7.5mA |  |  |

| FD                                      | FD               | No Error   | 4, 2.5, 7.5mA | FD            | FD        | No Error   | 4, 2.5, 7.5mA |  |  |

| FC                                      | FC               | No Error   | 4, 2.5, 7.5mA | FC            | FC        | No Error   | 4, 2.5, 7.5mA |  |  |

| FB                                      | FB               | No Error   | 4, 2.5, 7.5mA | FB            | FB        | No Error   | 4, 2.5, 7.5mA |  |  |

| FA                                      | FA               | No Error   | 4, 2.5, 7.5mA | FA            | FA        | No Error   | 4, 2.5, 7.5mA |  |  |

| F9                                      | F9               | No Error   | 4, 2.5, 7.5mA | F9            | F9        | No Error   | 4, 2.5, 7.5mA |  |  |

| F8                                      | F8               | No Error   | 4, 2.5, 7.5mA | F8            | F8        | No Error   | 4, 2.5, 7.5mA |  |  |

| F7                                      | F7               | No Error   | 4, 2.5, 7.5mA | F7            | F7        | No Error   | 4, 2.5, 7.5mA |  |  |

| F6                                      | F6               | No Error   | 4, 2.5, 7.5mA | F6            | F6        | No Error   | 4, 2.5, 7.5mA |  |  |

| F5                                      | F5               | No Error   | 4, 2.5, 7.5mA | F5            | F5        | No Error   | 4, 2.5, 7.5mA |  |  |

| F4                                      | F4               | No Error   | 4, 2.5, 7.5mA | F4            | F4        | No Error   | 4, 2.5, 7.5mA |  |  |

| F3                                      | F3               | No Error   | 4, 2.5, 7.5mA | F3            | F3        | No Error   | 4, 2.5, 7.5mA |  |  |

|                                         |                  |            |               |               |           |            |               |  |  |

# 5 Challenges Using Discrete Solution Instead of TPS2661x

A circuit providing solution with discrete elements consist of TVS diode, Zener diodes and PTC. During a miswiring event, TVS diode provides protection from surge pulses, PTC is required for over-current protection while Back-to-Back Zener diodes are required for overvoltage protection and limiting the power dissipation in Burden Resistor. For comparison of TPS2661x with discrete solution, see Enabling Smarter, Integrated Protection for 4-20mA Current Loops with eFuses.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated