# Power Switch Fault Glitch Solution During Power Up

Sam Ting and Ziv Zhang

#### **ABSTRACT**

The Fault open-drain output of power switch is usually connected to MCU as an indicator when an over-current or over temperature condition is encountered. However, in some cases, as input of power switch powers up fast, momentary false fault asserts that may lead to the MCU operating incorrectly.

It is suggested to use the software method such as controlling the MCU to avoid the fault glitch. This application report also displays one work around to avoid this false fault signal transferring to MCU. The document is applicable for TPS25221, TPS2065C/D, and TPS2069C/D.

#### **Table of Contents**

| 1 Introduction                                                                                      | .2  |

|-----------------------------------------------------------------------------------------------------|-----|

| 2 Root cause of False Fault Glitch                                                                  | 3   |

| 3 Solution for the Fault Glitch                                                                     |     |

| 3.1 With RC Filter to Eliminate Fault Glitch as Start-Up                                            |     |

| 3.2 Validate the Influence of RC Filter to Normal Operation                                         |     |

| 4 Summary                                                                                           | 5   |

| 5 Revision History                                                                                  | Ę   |

|                                                                                                     |     |

| List of Figures                                                                                     |     |

| Figure 1-1. Bench Set-Up.                                                                           | . 2 |

| Figure 1-2. Fault Glitch as Ramp V <sub>IN</sub> at 6 V/ms                                          | .2  |

| Figure 2-1. Simplified Internal Circuit Between IN Pin and Fault Pin                                | .3  |

| Figure 3-1. Solution for Fault Glitch                                                               | . 3 |

| Figure 3-2. Without RC Filter Waveform, 5 V/ms                                                      | .4  |

| Figure 3-3. With RC Filter Waveform, 5 V/ms                                                         |     |

| Figure 3-4. Fault Signal Behavior as V <sub>in</sub> Power up in Current Limit Condition            | . 4 |

| Figure 3-5. Fault Signal Behavior as Current Limit                                                  | . 4 |

|                                                                                                     |     |

| List of Tables                                                                                      |     |

| Table 1-1. Recommended Operating Condition of Input Voltage in TPS2065C/D and TPS2069C/D Data Sheet | 2   |

| Trademarks                                                                                          |     |

All trademarks are the property of their respective owners.

Introduction Www.ti.com

#### 1 Introduction

The power-distribution switch family is intended for applications such as USB where heavy capacitive loads and short circuits are likely to be encountered. Device features include enable, reverse blocking when disabled, output discharge pulling down, over-current protection, over temperature protection, and de-glitch fault reporting.

The open-drain output fault signal asserts as over current and over temperature conditions encountered with about 9 ms de-glitch time.

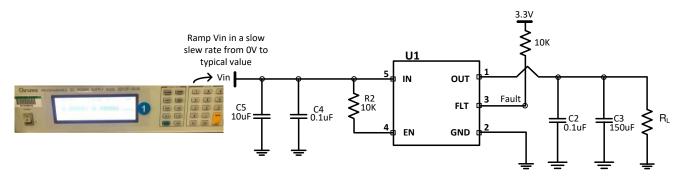

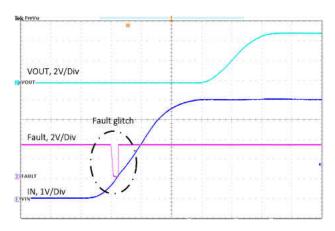

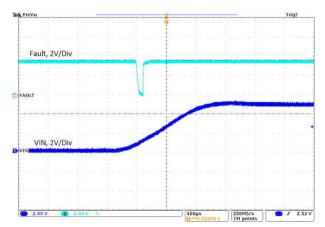

However, as the device is powered up in a fast slew rate, the fault signal falsely asserts that lead to the incorrect operation of the System-on-Chip (SoC). Figure 1-1 shows the set-up of the bench and ramp  $V_{IN}$  at 6 V/ms slew rate. Figure 1-2 shows the fault will have a glitch as  $V_{IN}$  ramp to about 1 V, which is far from the recommended operation range from 4.5 V to 5.5 V. Table 1-1 is the recommended operating condition of  $V_{IN}$ .

Figure 1-1. Bench Set-Up

Figure 1-2. Fault Glitch as Ramp V<sub>IN</sub> at 6 V/ms

Table 1-1. Recommended Operating Condition of Input Voltage in TPS2065C/D and TPS2069C/D Data Sheet

|                       | MIN | MAX | UNIT |

|-----------------------|-----|-----|------|

| VIN Input voltage, IN | 4.5 | 5.5 | V    |

The following section discusses the root cause of this phenomenon and the solve method of this concern.

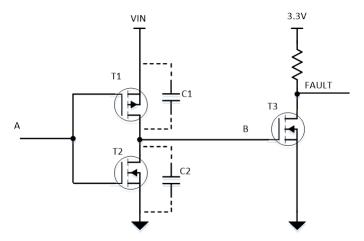

#### 2 Root cause of False Fault Glitch

The following process occurs as V<sub>IN</sub> ramps fast from 0 V to the recommended operation range:

- Before V<sub>IN</sub> reach to UVLO threshold to start reset, the internal circuit status is unknown.

- If V<sub>IN</sub> ramps pretty fast, the voltage on point B maybe coupled through C1.

- If the voltage on point B is larger than the threshold voltage  $V_{th}$ , T3 may pull down the FAULT pin.

- The whole circuit resumes to normal after the internal reset.

Figure 2-1. Simplified Internal Circuit Between IN Pin and Fault Pin

Due to the unknown status of the gate of T3, the Fault pin has the chance to be pulled down to 0 V.

#### 3 Solution for the Fault Glitch

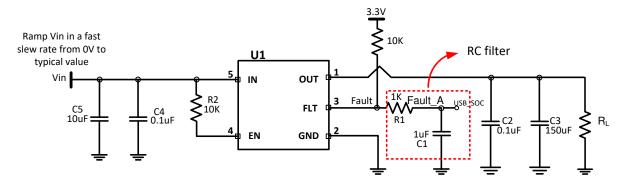

#### 3.1 With RC Filter to Eliminate Fault Glitch as Start-Up

Figure 3-1. Solution for Fault Glitch

Adding the RC filter between the Fault and MCU to eliminate the glitch.

Since point B from Figure 2-1 is in unknown status until  $V_{IN}$  reaches UVLO (4 V, the worst case in TPS2065D or TPS2069D). The worst case for Fault low is from  $V_{in} = V_{th}$  to  $V_{in}$  reach UVLO.

If  $V_{in} = 5 \text{ V}$ , and  $V_{IN}$  ramp =  $V_{ramp}$  V/ms, the worst Fault low period  $T_{FAULT\_L} = (UVLO - V_{th}) / V_{ramp}$ . You need Fault\_A to be >  $V_{FAULT\_H}$  (1.7 V) during  $T_{FAULT\_L}$ .  $V_{FAULT_d\_H}$  according to the customer's definition. Before power on, the initial voltage on C1 is 3.3 V. Before  $V_{in}$  reaches the UVLO voltage threshold, the voltage on C1 discharges through the FLT pin to GND.

Solution for the Fault Glitch www.ti.com

Select RC value to make sure:

$$V_{Fault\_A} = 3.3 V \times e^{\frac{-T_{FAULT\_L}}{RC}} > 1.7 V \tag{1}$$

If  $V_{ramp}$  = 5 V/ms, then  $T_{FAULT\ L}$  = 0.6 ms, select R = 1k $\Omega$ , C=1  $\mu$ F.

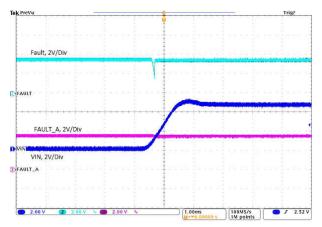

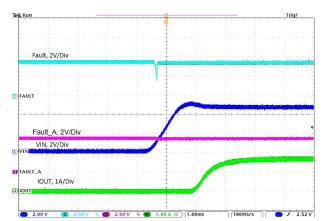

Figure 3-2. Without RC Filter Waveform, 5 V/ms

Figure 3-3. With RC Filter Waveform, 5 V/ms

As seen in Figure 3-2, without the RC filter added, the Fault pin is pulled down to 0 V. The duration time depends on the slew rate of input. Figure 3-3 displays that with the RC filter added, although the Fault pin has a glitch, the terminal Fault\_A that is connected to MCU almost has no glitches, always high level. The method proposed can eliminate the fault glitch concern.

### 3.2 Validate the Influence of RC Filter to Normal Operation

In order to validate whether the method proposed has some impact on the IC's normal operation, the delay time of added RC filter is verified. The following bench has been set up.

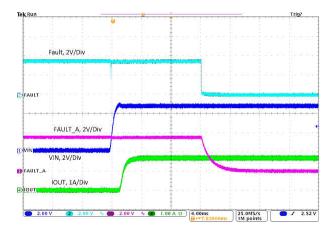

$V_{in}$  = 5 V, slew rate is 5V/ms. With RC filter added, the parameters are R1 =1k $\Omega$  and C1 = 1  $\mu$ F. RLoad = 2.5  $\Omega$ , current limit = 1.55A in TPS2065D. In theory, Fault A from 3.3 V to 0.7 V, the time is 1.55 ms. In general, 0.7 V is regarded as low level of fault signal.

Figure 3-4. Fault Signal Behavior as Vin Power up in Current Limit Condition

Figure 3-5. Fault Signal Behavior as Current Limit

In Figure 3-4, as V<sub>in</sub> ramps fast in the current limit condition, the Fault pin will glitch from 3.3 V to 1.4 V. However, the Fault\_A that is connected to MCU almost has no glitch. Figure 3-5 indicates that in current limit condition, the Fault A can also assert normally, but with a delay time about 1.55 ms. The results are in coincidence with theoretical calculation.

www.ti.com Summary

## 4 Summary

The RC filter workaround can help solve the power switch fault glitch issue during  $V_{in}$  startup. The workaround will cause a delay on normal fault condition. The delay duration depends on the RC value. Comparing with internal fault glitch time, 8-9 ms, the 1.55 ms delay time is relatively less impact and can be compromised.

## **5 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision * (October 2019) to Revision A (July 2021)                               | Page |

|---|-----------------------------------------------------------------------------------------------|------|

| • | Update was made in the Abstract                                                               | 1    |

| • | Updated the numbering format for tables, figures and cross-references throughout the document | 2    |

|   |                                                                                               |      |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated