# Designing a Split-Rail SEPIC With the TPS61175

Jeff Fain

PMP-DC Low-Power DC/DC Converters

### **ABSTRACT**

Often a regulated DC output voltage is needed between the minimum and maximum input voltages of a DC/DC converter, but neither a buck or boost converter in standard configurations is sufficient. However, a boost converter integrated circuit (IC) can be configured to drive a single-ended, primary inductor converter (SEPIC) power stage and provide an output voltage that is between the input voltage extremes. In addition, the user may want to extend the maximum input voltage range of the converter to limits beyond the absolute maximum of the IC.

# 1 Power Stage Design

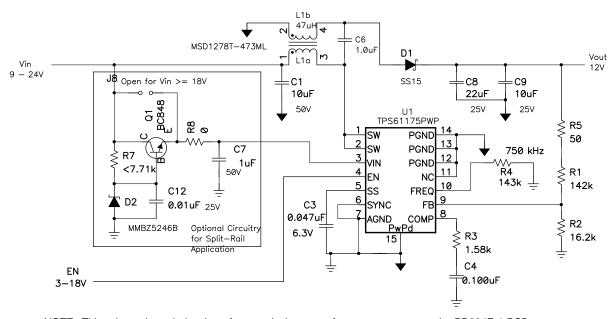

The following design example can help a user design a 12-V power supply from a 9-V to 24-V input power source using the TPS61175 boost converter IC in the SEPIC configuration with split-rail capability. In order to simplify this report, only the SEPIC and discrete linear regulator design equations with minimal explanatory text are included. For more information on the SEPIC topology and its design equations, see application reports <a href="SLVT309">SLVT309</a> and <a href="SLVA337">SLVA337</a>. More information is available on extending the input voltage range of a converter in application report <a href="SLVA338">SLVA338</a>. shows the power supply circuit.

NOTE: This schematic excludes the reference designators of open component on the PR894E-1 PCB.

Figure 1. 12-V Power Supply From 9-V to 24-V Input Power Source

Table 1 gives the performance specifications for the reference design.

Table 1. Performance Specifications for the Reference Design

| Parameter                         | Conditions | Min | Nom | Мас | Unit |

|-----------------------------------|------------|-----|-----|-----|------|

| Input and Ambient Characteristics |            |     |     |     |      |

| V <sub>IN</sub>                   |            | 9   | 15  | 24  | V    |

Power Stage Design www.ti.com

Table 1. Performance Specifications for the Reference Design (continued)

| Parameter           |                           | Conditions                                                     | Min  | Nom | Mac  | Unit                            |

|---------------------|---------------------------|----------------------------------------------------------------|------|-----|------|---------------------------------|

| f <sub>S</sub>      |                           |                                                                |      | 750 |      | MHz                             |

| T <sub>A</sub>      |                           |                                                                |      |     | 55   | °C                              |

| Output C            | Output Characteristics    |                                                                |      |     |      |                                 |

| V <sub>OUT</sub>    | Output voltage            |                                                                | 11.5 | 12  | 12.5 | V                               |

|                     | Load regulation           | $V_{IN} = 9 \text{ V}, 10 \text{ mA} < I_{O} < 800 \text{ mA}$ |      |     | 1%   | DV <sub>O</sub> /I <sub>O</sub> |

| V <sub>RIPPLE</sub> | Output voltage ripple     | I <sub>O</sub> = 800 mA                                        |      |     | 50   | MVP                             |

| Io                  | Output current            |                                                                | 1    |     | 750  | mA                              |

| η                   | Efficiency                |                                                                |      | 90% |      |                                 |

| Transient Response  |                           |                                                                |      |     |      |                                 |

| I <sub>TRAN</sub>   | Load step                 |                                                                |      | 325 |      | mA                              |

| $DV_TRAN$           | V <sub>O</sub> undershoot |                                                                |      | 350 |      | mV                              |

Table 2 summarizes the design considerations for the passive components.

**Table 2. Design Equations for Passive Components**

| SLYT309<br>Equation (Eq)<br>Number              | Design Equation a                                                                                                                      | Selection                                                                   |                      |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------|--|--|

| Eq 1                                            | $D = \frac{V_{OUT} + V_{D}}{V_{IN} + V_{OUT} + V_{D}}$                                                                                 | $D_{\text{max}} = \frac{12 + 0.5}{9 + 12 + 0.5} = 0.58$                     |                      |  |  |

|                                                 |                                                                                                                                        | $D_{\min} = \frac{12 + 0.5}{24 + 12 + 0.5} = 0.34$                          |                      |  |  |

| Eq 2 with η <sub>EST</sub>                      | $I_{\text{IN(DC),MAX}} = \frac{I_{\text{OUT,MAX}}}{\eta_{\text{EST}}} \times \frac{V_{\text{OUT}} + V_{\text{D}}}{V_{\text{N,MIN}}}$   | $= \frac{0.75}{0.9} \times \frac{12 + 0.5}{9} = 1.16 \text{ A}$             |                      |  |  |

| <sup>(1)</sup> Eq 3 where K <sub>IND</sub> =0.2 | $\Delta I_{L} = K_{IND} \times I_{N(DC)MAX} = 0$                                                                                       | MSD1278T-473ML,<br>47μH, I <sub>SAT</sub> =1.45A,<br>DCR=0.180 Ω            |                      |  |  |

| Eq 4                                            |                                                                                                                                        |                                                                             |                      |  |  |

| Eq. 5                                           | $I_{\text{L1a(PEAK)}} = \frac{I_{\text{IN(DC),MAX}}}{\eta} \times \left(1 + \frac{K_{\text{IND}}}{2}\right)$                           | $=\frac{1.16}{0.9} \times \left(1 + \frac{20\%}{2}\right) = 1.42 \text{ A}$ | -                    |  |  |

| Eq. 7                                           | $C_{\text{OUT}} \ge \frac{I_{\text{OUT}} \times D_{\text{(MAX)}}}{\Delta V_{\text{RPL}} \times f_{\text{S}}} = \frac{0}{50 \text{ m}}$ | . <del>75 × 0.581</del><br>Vpp × 750 kHz = 11.62 μF                         | C8=22 μF    C9=10μF, |  |  |

| NA                                              | $C_{OUT} \ge \frac{\Delta I_{TRAN}}{2\pi \times f_{BW} \times \Delta V_{TRAN}} = 2$                                                    | 25-V ceramic capacitors                                                     |                      |  |  |

| DV <sub>Cp-PKPK</sub> < 5%×Vo                   | $V_{Cp,(MAX)} = V_{IN} + \frac{1}{2} \times \Delta V_{Cp,PKPK} = 24$                                                                   |                                                                             |                      |  |  |

| Eq 11                                           | $C_{P} \ge \frac{I_{OUT} \times D_{(MAX)}}{\Delta V_{Cp-PKPK} \times f_{S}} \ge \frac{1}{0}$                                           | $\frac{0.75A \times 0.581}{0.6V \times 750 \text{ kHz}} = 0.97 \mu\text{F}$ | C6 = 1 µF, 50V       |  |  |

<sup>&</sup>lt;sup>(1)</sup> This customer application needed low current ripple and EMI, so a 47-µH inductor was selected.

Because ceramic capacitors with very low ESR and therefore very high RMS current ratings were used, the capacitor ripple current calculations were excluded in the preceding equations. In addition, the additional output voltage ripple caused by the capacitor's ESR was ignored. These calculations must be included if higher ESR capacitors are used.

www.ti.com Power Stage Design

Table 3 summarizes the design considerations for the active components.

**Table 3. Design Equations for Active Components**

| SLYT309<br>Equation (Eq) Number | Design Equation and Computation                                                                                                                                                                                                                                                                                                                                           | Selection                                                                     |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Figure 3                        | $V_{Q1(max)} = V_{IN(max)} + V_{OUT} = 24 V + 12 V = 36V$                                                                                                                                                                                                                                                                                                                 |                                                                               |

| Eq 12                           | $I_{Q1(PEAK)} = I_{IN(DC),MAX} + I_{OUT,MAX} + \Delta I_{L}$<br>= 1.16 A + 0.75 A + 0.23 A = 2.14 A                                                                                                                                                                                                                                                                       |                                                                               |

| Eq 14                           | $I_{Q1(RMS)} = \frac{I_{IN(DC),MAX}}{\sqrt{D_{max}}} = \frac{1.16}{\sqrt{0.58}} = 1.5 \text{ A}$                                                                                                                                                                                                                                                                          | U1 = TPS61175 with 38 V,<br>3-A peak FET and $P_D$ = 0.9 W<br>at $T_A$ = 85°C |

| Eq 13                           | $\begin{aligned}  P_{D\_O1} &= I_{O1(RMS)}^2 \times r_{DS(on)} \times D_{max} + I_{O1(PEAK)} \times (V_{IN,MIN} + V_{OUT} + V_D) \\ &\times \frac{t_{Rise} + t_{Fall}}{2} \times f_{SW} = 1.5^2 \times 0.13 \times 0.581 + 2.14 \text{ A} \times (9 + 12 + 0.5) \\ &\times \frac{10 \text{ ns} + 10 \text{ ns}}{2} \times 750 \text{ kHz} = 0.52 \text{ W} \end{aligned}$ |                                                                               |

| NA                              | $V_{R(DIODE)} = V_{IN(max)} + V_{OUT} = 24 V + 12 V = 36 V$                                                                                                                                                                                                                                                                                                               | D2 = B150B-13, 50 V, 1 A                                                      |

| NA                              | $P_{D(DIODE)} = I_{OUT(MAX)} \times V_D = 0.75 \text{ A} \times 0.5 \text{ V} = 375 \text{ mW}$                                                                                                                                                                                                                                                                           | 52 - 51005 10, 30 V, 1 A                                                      |

If using a converter with integrated FET like TPS61175, use this equation to quickly estimate I<sub>OUTmax</sub>.

$$I_{\text{OUT}(\text{MAX})} = \frac{I_{\text{LIM}}}{\left(\frac{V_{\text{OUT}} + V_{\text{D}}}{V_{\text{IN}(\text{MIN})}}\right) \times \left(\frac{1 + K_{\text{IND}}}{\eta_{\text{EST}}}\right) + 1} = \frac{3A}{\left(\frac{12 + 0.5}{9}\right) \times \left(\frac{1 + 20\%}{0.9}\right) + 1} = 1.05 \text{ A}$$

(1)

**Table 4. Discrete Linear Regulator Passive Components**

| SLVA338<br>Equation (Eq) Number                      | Design Equation and Computation                                                                                                                                                            | Selection                       |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|

| Eq 4                                                 | $V_{Z_{max}} < V_{ICmax} = 18V \text{ and } V_{Z_{min}} > V_{INmin} + V_{BE_{max}} = 2.9 \text{ V} + 0.7 \text{ V}$                                                                        | D2 = MMBZ5246B, 16 V,<br>225 mW |  |

| Eq 5 using Q1=BC848<br>with h <sub>FEmin</sub> = 200 | $R_{1D} < \frac{V_{PWRmax} - V_{Zmax}}{I_{Z} + \frac{I_{Qmax}}{h_{FE}}} = \frac{24 \text{ V} - 0.9 \times 18 \text{ V}}{1 \text{ mA} + \frac{2.3 \text{ mA}}{200}} = 7.71 \text{ k}\Omega$ | R7 = 7.68 kΩ                    |  |

Table 5 explains how the remaining components were chosen.

## **Table 5. Additional Components**

| Component                       | Rationale                                                                  |  |  |

|---------------------------------|----------------------------------------------------------------------------|--|--|

| C1 = 10 µF                      | C <sub>IN(MIN)</sub> per TPS61175 data sheet ( <u>SLVS892</u> )            |  |  |

| C3 = 0.047 µF                   | C <sub>SS(MIN)</sub> per TPS61175 data sheet ( <u>SLVS892</u> )            |  |  |

| R1 = 143 kΩ and R2 = 16.2 kΩ    | Equation 7 per TPS61175 data sheet (SLVS892)                               |  |  |

| R4 = 143 kΩ for $f_S$ = 750 kHz | Figure 13 of TPS61175 data sheet (SLVS892)                                 |  |  |

| Q1 = BC848 30-V                 | Low-cost NPN transistor per (SLVA338)                                      |  |  |

| C7 = 1.0 µF, 25 V               | Minimum recommended input capacitor for split rail operation per (SLVA338) |  |  |

| C12 = 0.1 µF, 25 V              | Minimum recommended base capacitor per (SLVA338)                           |  |  |

## 2 Compensating the Control Loop (R3 and C4)

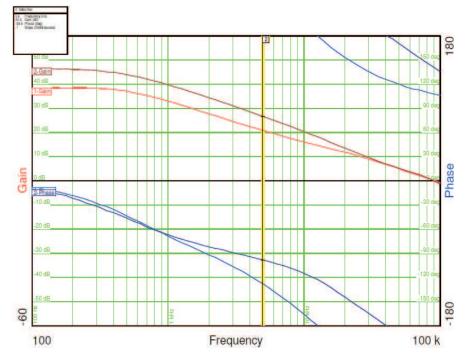

Figure 2 shows the measured results from the power stage transfer function's gain and phase at full load for  $V_{IN(MIN)}$ , in red and royal blue, and  $V_{IN(MAX)}$ , maroon and dark blue, respectively.

Figure 2. Measured Power Stage Gain and Phase with R3 = 1 k $\Omega$  and C4 = 1  $\mu$ F

The lowest frequency right-hand plane zero (RHPZ) occurs at V<sub>IN(MIN)</sub> and is calculated in Equation 2.

$$f_{\text{RHPZ}} = \frac{1}{2\pi \times \frac{L_{1a}}{R_{\text{OUT}}} \times \left(\frac{D}{1-D}\right)^2} = \frac{1}{2\pi \times \frac{47 \,\mu\text{H}}{16 \,\Omega} \times \left(\frac{0.581}{1 - 0.581}\right)^2} = 28.2 \text{ kHz}$$

(2)

The bandwidth typically is set to  $f_{BW} = f_{RHPZ}/10$ ; however, in this case, the RHPZ is fairly low, so  $f_{BW}$  is chosen to be 5 kHz. Therefore, the compensation gain,  $K_{COMP}$ , and power stage gain at the 5-kHz crossover frequency must be 0 dB, or  $K_{COMP}(f_{BW}) + 20log(G_{PW}(f_{BW})) = 0$  dB, so  $K_{COMP}(f_{BW}) = -20log(G_{PW}(f_{BW})) = -20$  dB as illustrated by the yellow line in Figure 2. Using Type II compensation and finding  $G_{EAmax} = 440$  µmho in the data sheet, Equation 3 computes the value of R3 to give  $K_{COMP}(f_{BW}) = -23$  dB, rounded up to the closest standard value.

R3

$$\approx \frac{10^{\frac{K_{COMP} (J_{BW})}{20 \text{ dB}}}}{G_{EA(MAX)} \times \frac{R2}{R2 \times R1}} = \frac{10^{\frac{-23 \text{ dB}}{20 \text{ dB}}}}{440 \text{ } \mu\text{mho} \times \frac{16.2 \text{ } k\Omega}{16.2 \text{ } k\Omega + 143 \text{ } k\Omega}} = 1.58 \text{ } k\Omega$$

(3)

With  $f_Z \approx f_{BW}/5 = 1$  kHz, C4 is solved for in Equation 4.

C4

$$\simeq \frac{1}{2\pi \times R3 \times f_z} = \frac{1}{2\pi \times 1.58 \text{ k}\Omega \times 1 \text{ kHz}} = 100 \text{ nF}$$

(4)

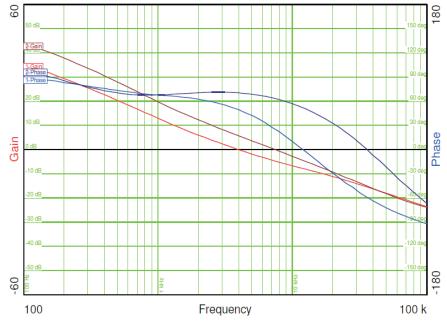

Figure 3 shows the measured loop gain and phase. The measured  $f_{BW}$  is centered around 5 kHz for both  $V_{IN(MIN)}$ , in red and royal blue, and  $V_{IN(MAX)}$ , in maroon and dark blue, and the phase margin is near 60° for both cases.

Figure 3. Measured Total Loop Gain and Phase With R3 = 1.58 k $\Omega$  and C4 = 0.100  $\mu$ F

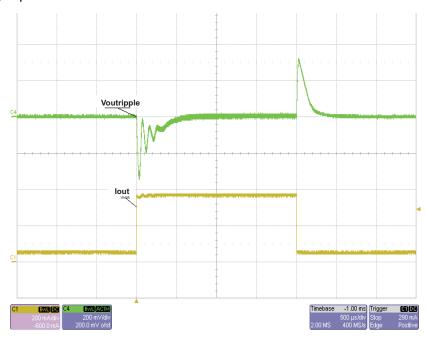

Figure 4 shows the transient response for a 325-mA load step. The DV<sub>TRAN</sub> droop of 350-mV is below the 400-mV design specification.

Figure 4. Load Transient Response With  $V_{IN} = 9 \text{ V}$  and  $I_{OUT} = 50 \text{ mA}$  to 375 mA

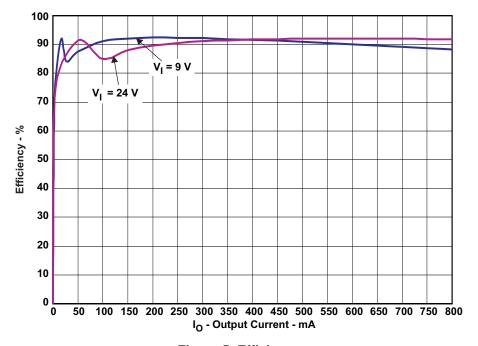

Figure 5 shows the efficiency.

Figure 5. Efficiency

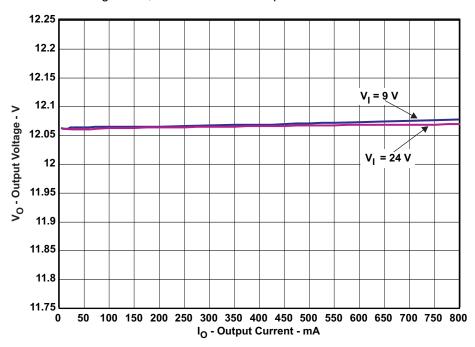

Figure 6 shows the load regulation, well within the 1% specification.

Figure 6. Load Regulation

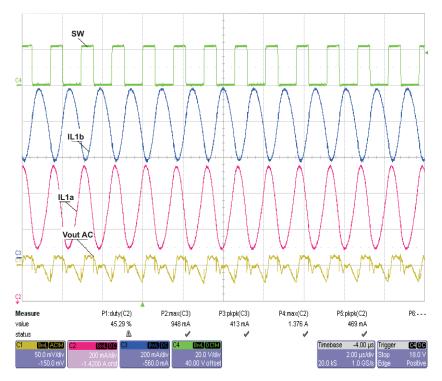

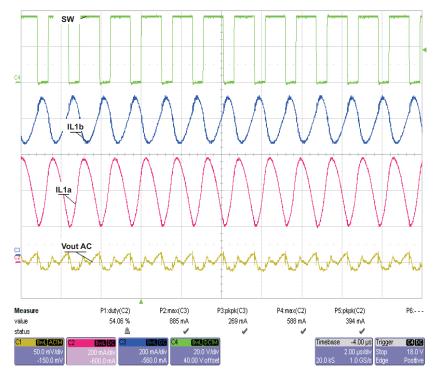

Figure 7 and Figure 8 show the typical operating waveforms.

Figure 7. Operation Including  $V_{RIPPLE}$  at  $V_{IN}$  = 9 V and  $I_{OUT}$  = 750 mA

Figure 8. Operation Including  $V_{RIPPLE}$  at  $V_{IN}$  = 24 V and  $I_{OUT}$  = 750 mA

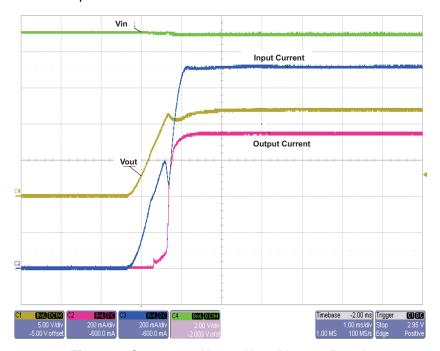

Figure 9 shows the start-up waveform.

Figure 9. Start-up at  $V_{IN} = 9 \text{ V}$  and  $I_{OUT} = 750 \text{ mA}$

In a SEPIC configuration, if the input voltage to the IC and  $V_{\text{ENABLE}}$  is separated from the power stage, careful attention must be paid to the order in which power is applied. If  $V_{\text{IN}}$  and  $V_{\text{ENABLE}}$  are applied to the IC, but no power is flowing to the power stage, the device drives to maximum duty cycle. Once power is supplied to the circuit, switching does not occur and the input current is unregulated. This can lead to device damage if the supply current is not limited.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                 |                                   |

|-----------------------------|------------------------|------------------------------|-----------------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio                        | www.ti.com/audio                  |

| Data Converters             | dataconverter.ti.com   | Automotive                   | www.ti.com/automotive             |

| DLP® Products               | www.dlp.com            | Communications and Telecom   | www.ti.com/communications         |

| DSP                         | <u>dsp.ti.com</u>      | Computers and<br>Peripherals | www.ti.com/computers              |

| Clocks and Timers           | www.ti.com/clocks      | Consumer Electronics         | www.ti.com/consumer-apps          |

| Interface                   | interface.ti.com       | Energy                       | www.ti.com/energy                 |

| Logic                       | logic.ti.com           | Industrial                   | www.ti.com/industrial             |

| Power Mgmt                  | power.ti.com           | Medical                      | www.ti.com/medical                |

| Microcontrollers            | microcontroller.ti.com | Security                     | www.ti.com/security               |

| RFID                        | www.ti-rfid.com        | Space, Avionics & Defense    | www.ti.com/space-avionics-defense |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video and Imaging            | www.ti.com/video                  |

|                             |                        | Wireless                     | www.ti.com/wireless-apps          |