# Optimizing Transient Response of Internally Compensated dc-dc Converters With Feedforward Capacitor

Brian Butterfield PMP - Portable Power

#### **ABSTRACT**

This application report describes how to choose the feedforward capacitor value (Cff) of internally compensated dc-dc power supplies to achieve optimum transient response. The described procedure in this application report provides guidance in optimizing transient response by increasing converter bandwidth while retaining acceptable phase margin. This document is intended for all power supply designers who want to optimize the transient response of a working, internally compensated dc-dc converter.

|    | Contents                                                                                       |

|----|------------------------------------------------------------------------------------------------|

| 1  | Introduction                                                                                   |

| 2  | Feedback Network With and Without the Feedforward Capacitor                                    |

| 3  | Conclusion                                                                                     |

| 4  | References                                                                                     |

|    | List of Figures                                                                                |

| 1  | Feedback Network Consisting of Two Bias Resistors Used to Set Output Voltage                   |

| 2  | Standard Feedback Divider Transfer Function                                                    |

| 3  | Feedback Network With Addition of Feedforward Capacitor                                        |

| 4  | Standard Feedback Divider With Feedfoward Capacitor Transfer Function                          |

| 5  | Internally Compensated Converter Without Feedforward Capacitor                                 |

| 6  | Tip and Barrel Measurement Technique                                                           |

| 7  | Voltage Transient in Response to Load Transient Without Feedforward Capacitor                  |

| 8  | Step Response vs Loop Phase Margin                                                             |

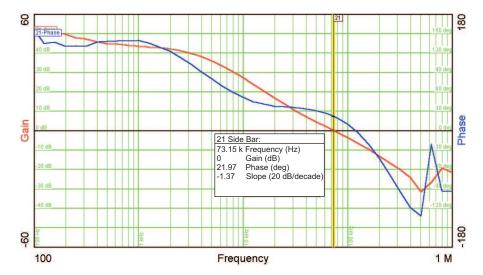

| 9  | Loop Gain and Phase Plot of TPS61081 Circuit Without Feedforward Capacitor                     |

| 10 | Voltage Transient in Response to a Load Transient With 82-pF Feedforward Capacitor             |

| 11 | Loop Gain and Phase Plot of TPS61081 Circuit With 82-pF Feedforward Capacitor                  |

| 12 | Voltage Transient in Response to a 0 to 100% Load Transient With 1000-pF Feedforward Capacitor |

| 13 | Loop Gain and Phase Plot of TPS61081 Circuit With 1000-pF Feedforward Capacitor                |

| 14 | Voltage Transient in Response to Load Transient With 33-pF Feedforward Capacitor               |

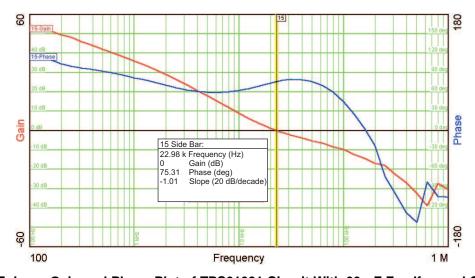

| 15 | Loop Gain and Phase Plot of TPS61081 Circuit With 33-pF Feedforward Capacitor                  |

#### **List of Tables**

Introduction www.ti.com

#### 1 Introduction

Internally compensated dc-dc converters allow designers to save time in the design and in debug processes by minimizing the number of external components that they must select. This simplification inherently narrows a designer's ability to optimize the transient response of the converter. However, with some internally compensated converters, the use of a feedforward capacitor in the feedback network is recommended, but only general guidance is provided for choosing this capacitor value to improve transient response. With measured transient or loop characteristics of a working dc-dc converter, a feedforward capacitor value can be chosen such that the converter bandwidth is significantly improved while still maintaining adequate phase margin. Furthermore, with a better understanding of the feedforward capacitor, the designer can go one step further to optimize either higher bandwidth or greater phase margin to meet specific performance requirements.

#### 2 Feedback Network With and Without the Feedforward Capacitor

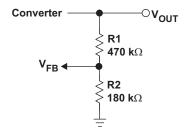

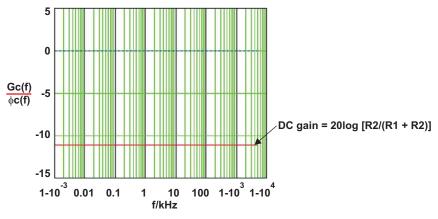

Without a feedforward capacitor, the feedback network of an internally compensated dc-dc converter consists of two feedback resistors used to set the output voltage of the converter, as shown in Figure 1. Figure 2 shows the corresponding gain and phase plot.

Figure 1. Feedback Network Consisting of Two Bias Resistors Used to Set Output Voltage

Figure 2. Standard Feedback Divider Transfer Function

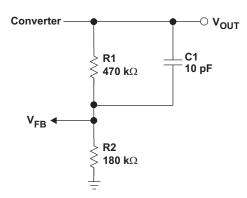

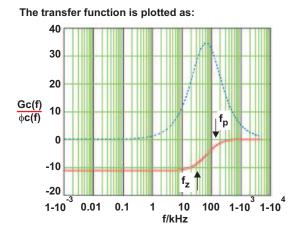

Figure 3 shows the addition of the feedforward capacitor, C1 (Cff), in the feedback network and Figure 4 shows the corresponding gain and phase plot. With the addition of the feedforward capacitor network, the converter can more effectively respond to high-frequency disturbances on the output voltage rail. The bode plots in Figure 2 and Figure 4 show that the responses of each feedback network are identical at lower frequencies. At mid-to-higher frequencies, disturbances on the output rail are attenuated less as the impendence path through C1 decreases and effectively provides a boost in gain and phase. In a working power supply, the increased gain and phase correlates to the converter responding faster to transient loads because the voltage deviation, sensed at the feedback node, is attenuated less at higher frequencies. The converter reacts by adjusting the duty cycle to more quickly correct the output voltage deviation.

Figure 3. Feedback Network With Addition of Feedforward Capacitor

Although Cff introduces a gain boost after its zero frequency, loop phase boost is at a maximum between the zero and pole frequencies; see the following Equation 1 and Equation 2. Increasing the value of Cff shifts the zero and pole in Equation 1 to lower frequencies, and decreasing the value Cff shifts the zero and pole to higher frequencies. The gain at dc is set by R1 and R2. The following equations calculate the pole, zero, and the dc gain of the feedback network as is shown in Figure 4.

$$f_Z = \frac{1}{2\pi \times R1 \times Cff} \tag{1}$$

Equation 1 calculates the zero frequency based on the feedforward capacitor value and the top bias resistor, R1. fz is shown on the plot in Figure 4.

$$f_p = \frac{1}{2\pi \times Cff} \left( \frac{1}{R2} + \frac{1}{R1} \right) \tag{2}$$

Equation 2 calculates the pole frequency based on the feedforward capacitor value and both top and bottom bias resistors, R1 and R2. fp is shown in on the plot in Figure 4.

Figure 4. Standard Feedback Divider With Feedfoward Capacitor Transfer Function

To optimize transient response, a Cff value is chosen such that the gain and phase boost of the feedback increases the bandwidth of the converter, while still maintaining an acceptable phase margin. In general, larger values of Cff provide greater bandwidth improvements. However, if Cff is too large, the feedforward capacitor causes the loop gain to crossover too high in frequency and the Cff phase boost contribution is insufficient, resulting in unacceptable phase margin or instability. Recommended limitations of Cff is discussed later in this document.

# 2.1 Feedforward Capacitor Value Optimization Process

The following process outlines a step-by-step procedure for optimizing the feedforward capacitor.

- Determine the crossover frequency of an internally compensated dc-dc converter with an unpopulated feedforward capacitor (f\_nocff). In certain circumstance, this can be calculated, but for this application report, this optimization procedure is based on measured converter characteristics. You can determine the crossover frequency (converter bandwidth) with transient analysis or by using a network analyzer. Both methods are shown.

- 2. Once the crossover frequency is known, a few equations allow calculation of a feedforward capacitor value which prompts a good compromise between bandwidth improvement and acceptable phase margin. Improvement in transient and loop response is shown with transient analysis and frequency analysis to confirm the design.

- 3. If the designer chooses to optimize for higher bandwidth or increased phase margin (more damping), guidance is provided.

# 2.2 Determining the Crossover Frequency

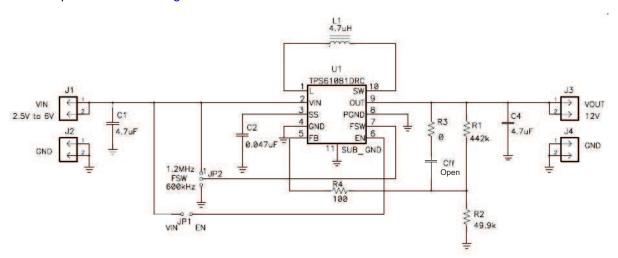

The TPS61081 is used in this example to determine the crossover frequency. This example can be applied to other internally compensated dc-dc converters which recommend external feedforward capacitors in the feedback network.

After using the data sheet guidelines to choose all appropriate external components, remove the feedforward capacitor, and measure the converters crossover frequency by using transient analysis or a network analyzer. Note that to determine the crossover frequency, f\_nocff, the feedforward capacitor must be left open as shown in Figure 5.

Figure 5. Internally Compensated Converter Without Feedforward Capacitor

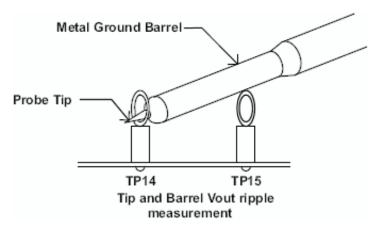

Figure 6 shows the tip and barrel measurement method set up for transient analysis. A transient load is connected to the output of the power supply circuit, while a current probe measures the transient load current, and a tip and barrel voltage probe measures the voltage deviation during transient load conditions on the output.

Figure 6. Tip and Barrel Measurement Technique

The tip and barrel measurement technique in Figure 6 is used to minimize coupling magnetic fields and obtain a more accurate voltage waveform during transient load transitions. TP14 is connected to the measured signal whereas TP15 is connected to ground. TP14 and TP15 are not shown in Figure 5. If the power supply does not include the appropriate test points, the test points can be strategically placed using bus wire. It is recommended that the bus wire test points be tacked onto the converter output capacitor closest to the load. Figure 7 shows the TPS61081 transient response as measured with the tip and barrel technique. The plots are taken using the TPS61081EVM-147 with Vin = 5 V, Vout = 12 V, and a load transient from 0 mA to 160 mA.

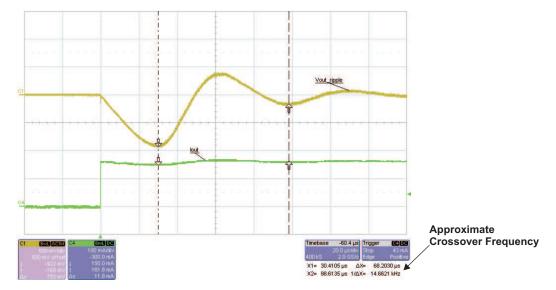

Figure 7. Voltage Transient in Response to Load Transient Without Feedforward Capacitor

About 0.9 V of output voltage deviation from the dc voltage set point is observed. The voltage waveform in Figure 7 provides insight to the converter crossover frequency as described in Evaluation and Performance Optimization of Fully Integrated DC/DC Converters (Topic 7 of the 2006 Portable Power Design Seminar). The frequency of the voltage deviation waveform in response to a load transient is related to the crossover frequency of the converter. Using the oscilloscope's cursors, the crossover frequency is approximated. The frequency of the transient ripple in this example is approximately 15 kHz. Note that the voltage deviation begins to correct 30  $\mu$ s after the transient occurs. As the crossover frequency of the converter is increased, it is confirmed that the converter response is improved as the voltage deviation begins to correct in less time, resulting in less voltage deviation.

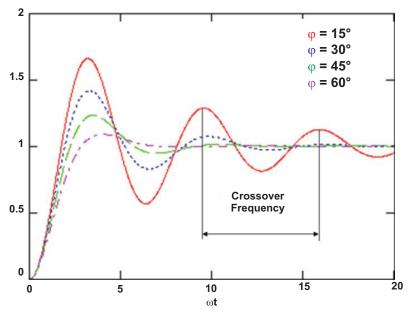

Figure 8. Step Response vs Loop Phase Margin

Using Figure 8 from the 2006 Portable Power Design Seminar topic paper *Evaluation and Performance Optimization of Fully Integrated DC/DC Converters*, the phase margin of the loop can be adequately approximated. Comparing the two plots, the TPS61081 measured the transient response most resembling the number of oscillations of the blue trace with just slightly more oscillation. This means that the measured loop has just slightly less than 30° of phase margin.

# 2.3 Determining the Crossover Frequency Using Frequency Analysis

Because frequency analysis equipment is costly, using such equipment is not always an option. However, when such equipment is available, the crossover frequency can be quickly measured. This method is more accurate than the transient analysis approximation and should be used when possible. Figure 9 shows the frequency analysis of the control loop for the example circuit in Figure 5.

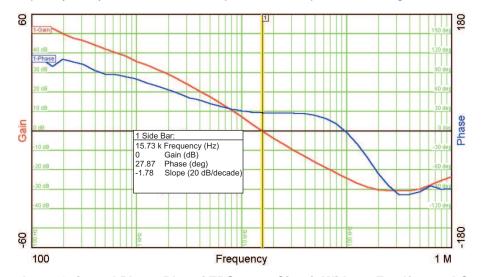

Figure 9. Loop Gain and Phase Plot of TPS61081 Circuit Without Feedforward Capacitor

Once the loop gain and phase plot is obtained with a network analyzer, the crossover frequency is quickly noted. The phase margin is 28° which confirms the transient analysis approximation of being just less than 30°. The crossover frequency also is measured at 16 kHz which is close to the 15-kHz approximation.

# 2.4 Calculating the Feedforward Capacitor for Optimum Loop Response

With the crossover frequency with no Cff identified (f\_nocff), the value of Cff can be calculated for optimum transient response by choosing Cff such that the zero and pole frequency geometrically straddle f nocff.

f\_nocff = 16 kHz Converter crossover frequency with no Cff

$R1 = 442 \text{ k}\Omega$   $R2 = 49.9 \text{ k}\Omega$

R1 and R2 are the feedback bias resistors used to set the output voltage of the converter as shown in Figure 5.

Equation 3 calculates the geometric mean of the feedback network's zero and pole frequencies. The geometric mean frequency equation is used to calculate the frequency where the phase boost from the zero and pole is at a maximum. However, because Cff is currently unknown, equations fz and fp are left in variable form.

$$F_{geometric\_mean} = \sqrt{(f_z \times f_p)}$$

(3)

Equation 4 sets the geometric mean frequency equal to the converter crossover frequency with no Cff.

$$f_{\text{noCff}} = \sqrt{(f_{z} \times f_{p})}$$

(4)

Setting the geometric mean frequency equal to the converter crossover frequency with no Cff positions the maximum phase boost of Cff at f\_nocff. However, because Cff introduces a boost in phase and in gain, the new crossover frequency occurs at a frequency greater than the geometric mean frequency. Therefore, the new converter crossover frequency does not occur at the maximum phase boost frequency due to Cff, but crosses over at a higher frequency facilitating a faster converter response time, while still benefitting from additional phase boost. The following plots confirm that the converter response time does indeed improve, and as a result, less transient voltage deviation is observed.

Substituting Equation 1 and Equation 2 into Equation 4 results in Equation 5, which is now a function of R1, R2, and Cff.

$$f_{\text{_noCff}} = \sqrt{\left(\frac{1}{2\pi \times R1 \times Cff}\right) \left[\frac{1}{2\pi \times Cff} \left(\frac{1}{R2} + \frac{1}{R1}\right)\right]}$$

(5)

Solving for Cff results in a feedforward capacitor value for optimum transient response, Cff\_op.

Cff\_op =

$$\frac{1}{2\pi \times f_{nocff}} \times \sqrt{\frac{1}{R1} \times \left(\frac{1}{R1} + \frac{1}{R2}\right)}$$

$$Cff_op = 7.066 \times 10^{-11}$$

(6)

Where f\_nocff = 16 kHz, R1 = 442 kHz, and R2 = 49.9 kHz. Rounding the calculated Cff value up to the next nearest standard capacitor value, rounds to 82 pF.

Cff std = 82 pF

# 2.5 Improvement

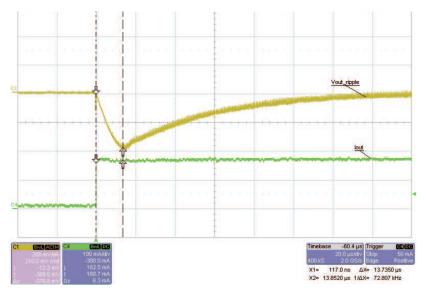

Figure 10 shows the improved transient response with the addition of the 82-pF Cff capacitor. The converter responds in 14  $\mu$ s with Cff = 82 pF compared to 30  $\mu$ s without Cff. The maximum transient voltage deviation is 377 mV with Cff compared to 900 mV without Cff.

Figure 10. Voltage Transient in Response to a Load Transient With 82-pF Feedforward Capacitor

Figure 11. Loop Gain and Phase Plot of TPS61081 Circuit With 82-pF Feedforward Capacitor

Figure 11 shows that the network analyzer also confirms the improved bandwidth with adequate phase margin. For this example, the addition of the Cff capacitor increased the bandwidth by a factor of 3, from 16 kHz to 48 kHz, and increased the phase margin to an acceptable 55°.

For most applications, this is an optimum placement of the feedforward capacitor response. Increasing the feedforward capacitance value pushes both the zero and pole frequencies closer to the origin which increases the crossover frequency but can result in lower overall phase margin. This corresponds to a faster loop at the expense of lower phase margin. Decreasing the Cff value results in the opposite result until a certain point where the feedforward capacitor gain and phase boost contribution diminishes and approaches the response of having no Cff. Having too small a Cff value injects a zero and pole at frequencies too high and effectively too late in loop response, resulting in little or no performance improvement

# 2.6 Optimizing Toward a Faster Loop At the Expense of Less Phase Margin

To reduce transient ripple even more, the feedforward capacitor value can be increased to push the crossover to higher frequencies. Although this can decrease the voltage deviation even more and speed up loop response, more ringing is observed because less phase boost is added from the feedforward capacitor at the new crossover frequency. Larger Cff values provide less phase boost because increasing Cff causes the converter to cross over at higher frequencies while the maximum phase boost moves to lower frequencies. It is recommended to keep the feedforward capacitor value smaller than the value which corresponds to 30° of phase margin, so that a phase margin ≥30° is the minimum phase margin target. This corresponding Cff value limit must be determined empirically, if required. It is generally not recommended to increase Cff significantly greater than the calculated optimized Cff.

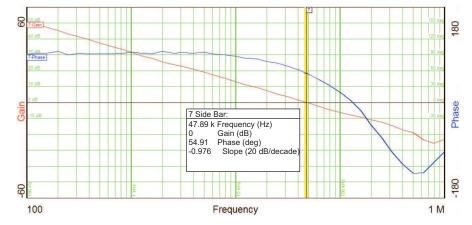

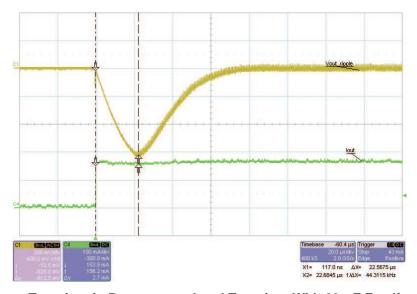

Figure 12 and Figure 13 show the same converter using a 1000-pF feedforward capacitor which is much larger than the initially optimized capacitor value in an attempt to speed up the loop response. It is seen that the converter begins to correct the deviation from dc faster and results in less voltage deviation, at 258 mV. Using the network analyzer, the resulting crossover frequency is improved from 48 kHz to 73 kHz at the expense of lower phase margin, now at 22°, which is lower than that generally recommended. In this transient response, the voltage deviation begins to correct in 9  $\mu$ s as opposed to the optimized 14- $\mu$ s response.

Figure 12. Voltage Transient in Response to a 0 to 100% Load Transient With 1000-pF Feedforward Capacitor

Figure 13. Loop Gain and Phase Plot of TPS61081 Circuit With 1000-pF Feedforward Capacitor

# 2.7 Optimizing Toward Greater Phase Margin for Less Ringing

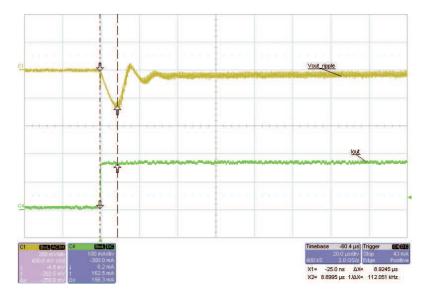

Conversely, if more phase margin is desired, a smaller feedforward capacitor allows the loop to crossover at a lower frequency and position the maximum phase boost from the feedforward capacitor closer to the new crossover frequency, with the tradeoff of lower bandwidth. As the Cff capacitor value is reduced, the bandwidth of the converter approaches the bandwidth of the converter without the feedforward capacitor. Figure 14 and Figure 15 show the transient and loop response of a converter with the 82-pF Cff replaced with a 33-pF Cff. With only 33 pF, the converters response time has increased to 22  $\mu$ s, resulting in a larger transient voltage deviation of 613 mV. This, however, is still better than the 30- $\mu$ s response, 900-mV voltage deviation of the converter without the feedforward capacitor. Also, note that a 0-A to full-load transient is very aggressive testing and was used to show more clearly the optimization throughout this application report.

Figure 14. Voltage Transient in Response to Load Transient With 33-pF Feedforward Capacitor

Figure 15. Loop Gain and Phase Plot of TPS61081 Circuit With 33-pF Feedforward Capacitor

www.ti.com Conclusion

#### 3 Conclusion

The feedforward capacitor used in the feedback network improves the performance of internally compensated dc-dc converters. The respective data sheet describes how to generally size the feedforward capacitor for improved loop response. However, with measured response characteristics of a working design, the feedforward capacitor can be sized to facilitate an improved transient response. The calculated optimal Cff value can be increased or decreased to optimize the converters transient response for minimum voltage deviation or higher phase margin.

#### 4 References

- 1. Evaluation and Performance Optimization of Fully Integrated DC/DC Converters (Topic 7 of 2006 Portable Power Design Seminar)

- 2. Using the TPS40040EVM-001: A 12-V Input, 1.8-V Output, 10-A Synchronous Buck Converter User's Guide (SLUU266)

- 3. TPS6108xEVM-147 User's Guide (SLVU144)

- 4. TPS61080/81, High Voltage DC/DC Boost Converter With 0.5-A/1.3-A Integrated Switch data sheet (SLVS644)

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Page |  |

|------|--|

| 6    |  |

|      |  |

| Page |  |

| 2    |  |

|      |  |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated