# **Using the UCD92xx Digital Point-of-Load Controller**

## **Design Guide**

Literature Number: SLUU490 April 2011

## **Contents**

| _ |       | - 044 O                                                           |    |

|---|-------|-------------------------------------------------------------------|----|

| 1 |       | x-Start Guide                                                     |    |

|   | 1.1   | Procedure                                                         |    |

|   | 1.2   | Summary                                                           |    |

| 2 |       | it Considerations Using the UCD92xx                               |    |

|   | 2.1   | Circuit Board Design                                              |    |

|   |       | 2.1.1 Power Stage Schematics                                      |    |

|   |       | 2.1.2 Differential Sense Lines                                    |    |

|   |       | 2.1.3 3.3-V and 1.8-V Core Voltage Decoupling                     |    |

|   | 2.2   | Temperature Monitoring                                            |    |

|   |       | 2.2.1 Internal Temperature Sense                                  |    |

|   |       | 2.2.2 External Temperature Sense                                  |    |

|   |       | 2.2.3 Thermistor Temperature Sense                                |    |

|   | 2.3   | Current Monitoring                                                |    |

|   |       | 2.3.1 Calculation of the Current Sense Voltage Using Inductor DCR |    |

|   |       | 2.3.2 Calculation of Attenuation Resistor R <sub>ATT</sub>        |    |

|   | 2.4   | Inductor Derating Used by the Fusion GUI                          |    |

|   | 2.5   | Determining IOUT_CAL_GAIN and IOUT_CAL_OFFSET                     |    |

|   | 2.6   | Calibration of IOUT_CAL_GAIN and IOUT_CAL_OFFSET                  |    |

|   | 2.7   | Filtering Requirements on the UCD723x CS Outputs                  |    |

|   | 2.8   | Filtering Requirements on the UCD7242 and UCD74106 CS Outputs     |    |

|   | 2.9   | Calculation of UCD7230A ILIM Voltage                              |    |

|   | 2.10  | Calculation of UCD7231 ILIM Voltage                               | 36 |

| 3 | Volta | ge Regulation                                                     |    |

|   | 3.1   | Loop Compensation                                                 |    |

|   |       | 3.1.1 Total Loop Gain                                             | 38 |

|   | 3.2   | Implementation of the Compensating Filter <i>H</i> (s)            | 39 |

|   |       | 3.2.1 Compensating Filter Architecture                            | 41 |

|   |       | 3.2.2 Fixed-Point Math                                            | 42 |

|   |       | 3.2.3 Cascaded First-Order Filter                                 | 43 |

|   |       | 3.2.4 Type II versus Type III Compensation                        | 43 |

|   | 3.3   | Modeling Delay in the Control Loop                                |    |

|   | 3.4   | Phase Loss as a Result of On-Time and Multiple Power Stages       |    |

|   | 3.5   | Quantization Effects                                              |    |

|   | 3.6   | Anti-Saturation Feature                                           | 46 |

|   | 3.7   | Autotune Operation                                                | 47 |

|   |       | 3.7.1 Determining the Compensating Zeros and Compensating Gain    | 48 |

|   |       | 3.7.1.1 Caveats                                                   | 49 |

|   | 3.8   | How to Tweak the Compensation                                     |    |

|   |       | 3.8.1 Tuning by Pole/Zero Placement                               | 49 |

|   |       | 3.8.2 Tuning by PID Gains                                         |    |

|   | 3.9   | Making Loop Transfer Function Measurements                        | 52 |

|   |       | 3.9.1 Types of Excitation                                         |    |

|   |       | 3.9.2 Generation of Sinewave Excitation                           |    |

|   |       | 3.9.3 Response Measurement Implementation                         | 53 |

|   |       |                                                                   |    |

#### www.ti.com

| 4 | Start | t-Up Sequencing                                               | 55 |

|---|-------|---------------------------------------------------------------|----|

|   | 4.1   | Sequencing                                                    | 56 |

|   | 4.2   | Start Indications                                             | 56 |

|   | 4.3   | TON_DELAY and TON_RISE                                        | 58 |

|   | 4.4   | Group Commands                                                | 59 |

|   | 4.5   | Daisy-Chaining CTRL and PowerGood Pins                        | 60 |

|   | 4.6   | Voltage Tracking                                              | 60 |

|   | 4.7   | GPIO_SEQ_CONFIG                                               | 62 |

|   |       | 4.7.1 Configuration for Sequencing Output                     | 63 |

|   |       | 4.7.2 Configuration for Sequencing Inputs                     | 65 |

|   |       | 4.7.3 Fault Slaves                                            | 66 |

|   |       | 4.7.4 Sequencing Timeout                                      | 68 |

|   | 4.8   | Alternative/Additional PowerGood Outputs                      | 69 |

| 5 | Devi  | ce Operation                                                  | 71 |

|   | 5.1   | AFE Overview                                                  |    |

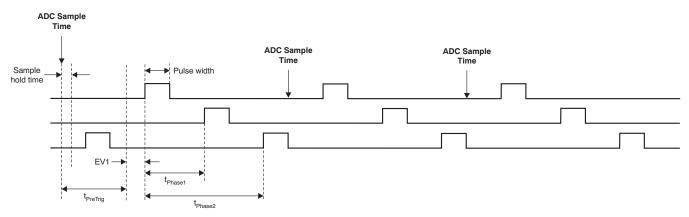

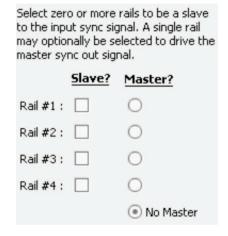

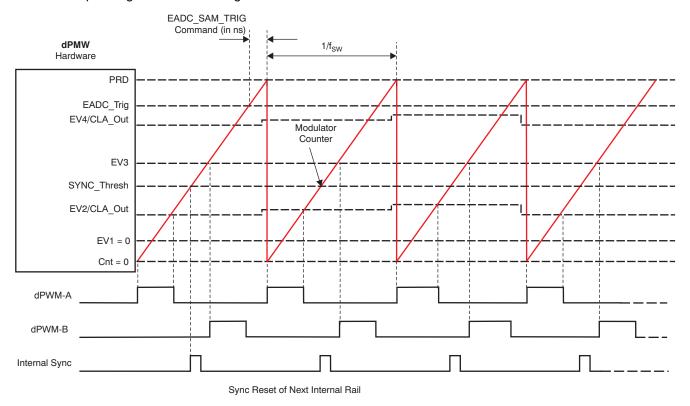

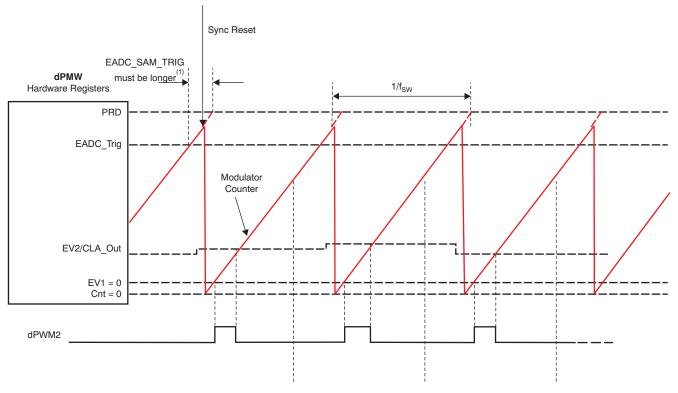

|   | 5.2   | Synchronizing Multiple PWM Signals                            | 73 |

|   |       | 5.2.1 Description of the Digital Demodulator Logic            | 74 |

|   |       | 5.2.2 Effect of EV1                                           | 75 |

|   |       | 5.2.3 Setting EADC_SAMPLE_TRIGGER Value                       | 75 |

|   | 5.3   | The Soft-Start Ramp                                           | 76 |

|   |       | 5.3.1 Starting into a Prebias State                           | 77 |

|   |       | 5.3.2 Effect of a Large DRIVER_MIN_PULSE                      | 78 |

|   | 5.4   | PWM Timing                                                    | 78 |

|   | 5.5   | Inrush Current During Kick-Start                              | 78 |

|   |       | 5.5.1 Inductor Ripple Current                                 |    |

|   | 5.6   | Current Balance                                               | 81 |

|   | 5.7   | Temperature Balance                                           | 84 |

| 6 | Usin  | g the Fusion Designer Software                                | 85 |

|   | 6.1   | Downloading the Project File                                  | 86 |

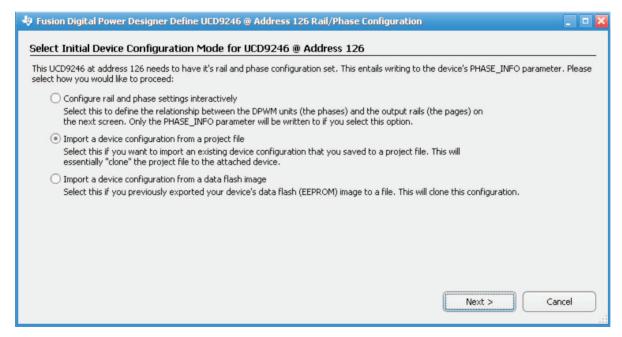

|   |       | 6.1.1 Communicating to a Previously Configured UCD92xx Device | 88 |

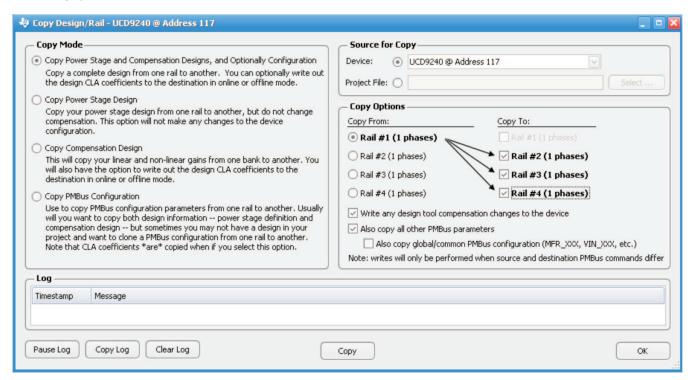

|   | 6.2   | Copying One Design to Another Voltage Rail                    | 88 |

|   |       | 6.2.1 Method 1: Copy Coefficients                             | 89 |

|   |       | 6.2.2 Method 2: Copy a Design                                 | 90 |

|   | 6.3   | Design→Device Synchronization                                 | 90 |

| Α | РМВ   | Bus Communication                                             | 93 |

|   | A.1   | Overview                                                      | 93 |

|   | A.2   | LINEAR11 Format                                               | 94 |

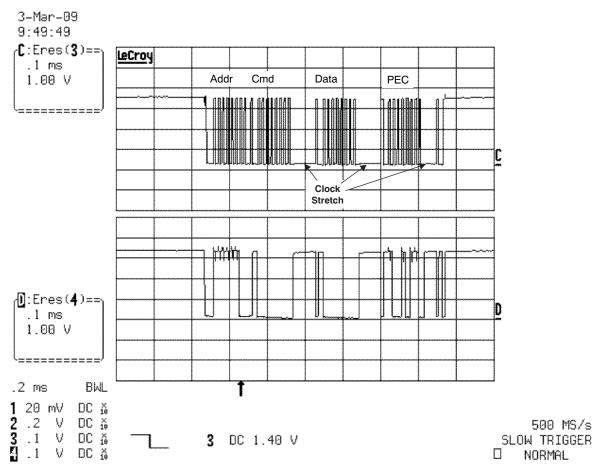

|   | A.3   | Clock Stretching                                              | 95 |

| В | Loca  | ating the Compensating Zeros                                  | 97 |

|   | B.1   | Overview                                                      |    |

## **List of Figures**

| 1.            | UCD9248 Block Diagram                                                                       | 8  |

|---------------|---------------------------------------------------------------------------------------------|----|

| 1-1.          | Fusion Digital Power Designer Software GUI: Startup Screen (Offline Mode)                   | 12 |

| 1-2.          | UCD92xx Naming Convention                                                                   | 12 |

| 1-3.          | Fusion GUI: Phase Assignment Selection Menu                                                 | 13 |

| 1-4.          | Fusion GUI: Voltage Configuration Menu                                                      | 13 |

| 1-5.          | Fusion GUI: Start Delay and Soft-Start Ramp Time Configuration to Illustrate PMBus Commands | 14 |

| 1-6.          | Fusion GUI: Turn-On and Turn-Off Timing (Voltage Configuration)                             | 15 |

| 1-7.          | Fusion GUI: Tooltip Example                                                                 | 15 |

| 1-8.          | Fusion GUI: I <sub>OUT</sub> , V <sub>IN</sub> , and Temperature Configuration              | 15 |

| 1-9.          | Fusion GUI: Design Menu                                                                     | 16 |

| 1-10.         | Fusion GUI: Design Schematic Example                                                        | 17 |

| 1-11.         | Fusion GUI: Bode Plots and Simulation Graphs                                                | 18 |

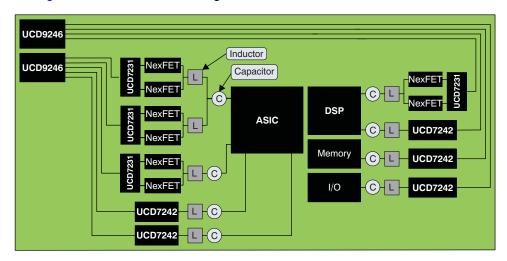

| 2-1.          | Typical Multi-Voltage-Rail Board                                                            | 22 |

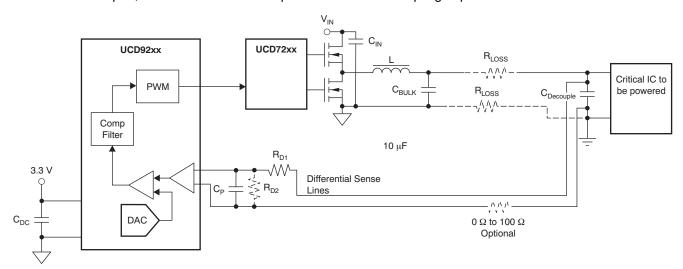

| 2-2.          | Single Board V <sub>OUT</sub> Sense                                                         | 23 |

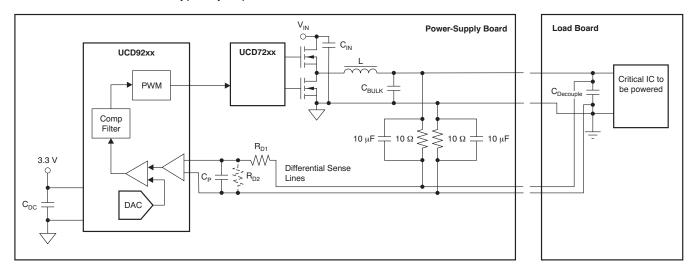

| 2-3.          | 10-Ω Backup Circuit for Remote Sense                                                        | 24 |

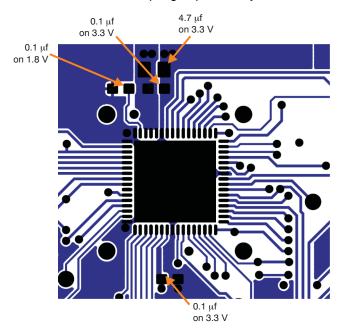

| 2-4.          | Recommended Decoupling Capacitor Layout                                                     | 25 |

| 2-5.          | Providing 3.3-V Power for the Controller                                                    | 25 |

| 2-6.          | External Temperature Sense Multiplexer                                                      | 27 |

| 2-7.          | Thermistor Circuit                                                                          | 28 |

| 2-8.          | Thermistor Circuit Response                                                                 | 29 |

| 2-9.          | Block Diagram of the 12-Bit ADC Used for Monitoring                                         | 29 |

| 2-10.         | Current Sense Schematic: Direct Current Resistance (DCR) Current Sense                      | 30 |

| 2-11.         | Adding an Additional Load to Check/Calibrate IOUT_CAL_GAIN                                  | 33 |

| 2-12.         |                                                                                             |    |

| 2-13.         | Setting UCD7230A CLF/FLT Threshold                                                          |    |

| 3-1.          | UCD92xx Fusion Peripheral Block Diagram                                                     | 38 |

| 3-2.          |                                                                                             | 41 |

| 3-3.          | $\cdot$                                                                                     | 42 |

| 3-4.          | ·                                                                                           | 44 |

| 3-5.          | Latency for an Example Three-Phase Power Supply                                             |    |

| 3-6.          | ·                                                                                           | 46 |

| 3-7.          |                                                                                             | 47 |

| 3-8.          |                                                                                             | 48 |

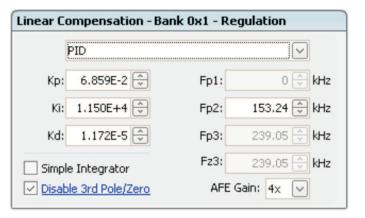

| 3-9.          | Fusion GUI: PID Gains Control                                                               |    |

| 3-10.         | ,                                                                                           | 52 |

| 3-11.         | 3                                                                                           | 54 |

| 4-1.          | ·                                                                                           | 56 |

| 4-2.          | '                                                                                           | 57 |

| 4-3.          | ·                                                                                           | 59 |

| 4-4.          | , , , ,                                                                                     | 60 |

| 4-5.          |                                                                                             | 61 |

| 4-6.          | ě i                                                                                         | 61 |

| 4-7.          | 3                                                                                           | 64 |

| 4-8.          |                                                                                             | 65 |

| 4 <b>-</b> 9. | Fusion GUI: Fault Shutdown Slave Control                                                    |    |

| 4-10.         | Fault on Rail #1; Rail #2 has a Rail #1 Stay-on Dependency with Soft-Off                    |    |

| 4-11.         | Fault on Rail #1; Rail #2 has a Rail #1 Stay-on Dependency with Immediate-Off               | 6/ |

#### www.ti.com

| 4-12. | Fault on Rail #1—Rail #2 is a Fault Slave for Rail #1; Shutdown After Retries | 67         |

|-------|-------------------------------------------------------------------------------|------------|

| 4-13. | Fusion GUI: Sequencing Timeout Control Screen                                 | 68         |

| 5-1.  | UCD92xx Analog Front-End                                                      | 72         |

| 5-2.  | Synchronization Options                                                       | 73         |

| 5-3.  | PWM Timing with Internal Synchronization                                      | 74         |

| 5-4.  | PWM Timing with External Synchronization                                      | 75         |

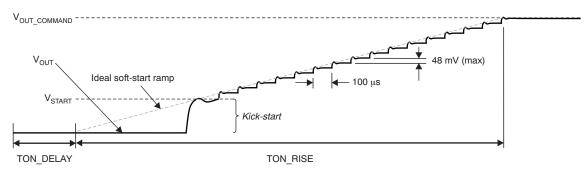

| 5-5.  | Soft-Start Ramp                                                               | 76         |

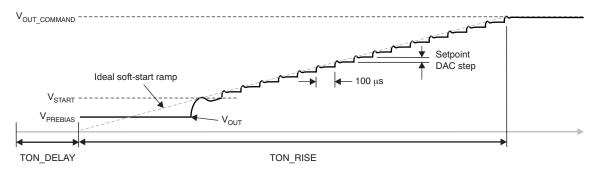

| 5-6.  | Soft-Start Ramp: V <sub>PREBIAS</sub> Less Than V <sub>START</sub>            | 77         |

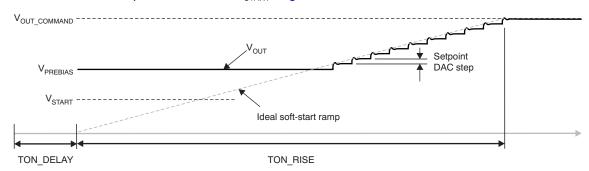

| 5-7.  | Soft-Start Ramp: V <sub>PREBIAS</sub> Greater Than V <sub>START</sub>         | 77         |

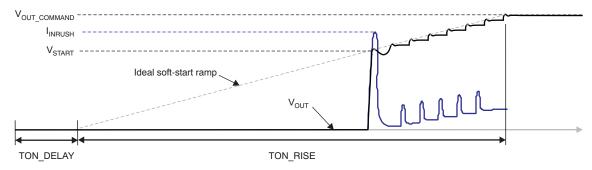

| 5-8.  | Soft-Start with Large DRIVER_MIN_PULSE                                        | 78         |

| 5-9.  | Simplified Schematic for Estimating Inrush Current                            | <b>7</b> 9 |

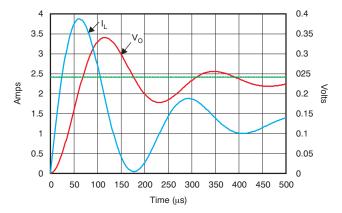

| 5-10. | Voltage and Current during the Kick-Start Period                              | 81         |

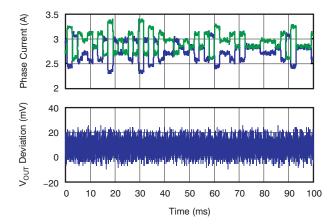

| 5-11. | Example Current Balance Action for a Dual-Phase Voltage Rail                  | 83         |

| 6-1.  | Fusion GUI: Project File Download Menu                                        | 86         |

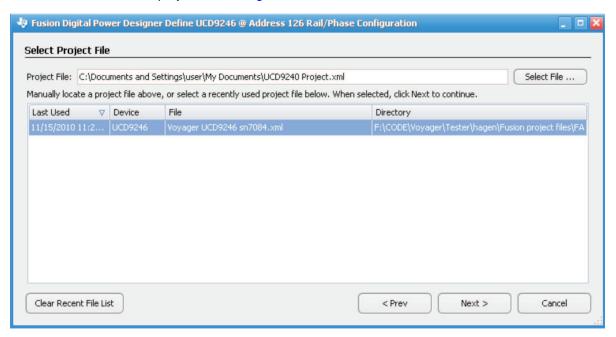

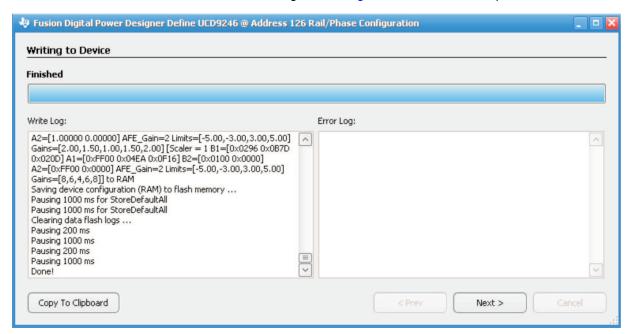

| 6-2.  | Fusion GUI: Project File Selection                                            | 87         |

| 6-3.  | Fusion GUI: Project File Configuration                                        | 87         |

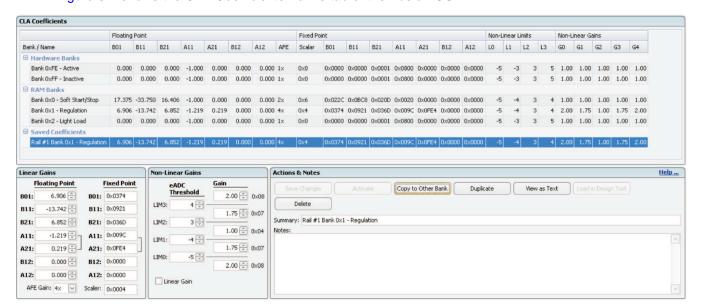

| 6-4.  | Fusion GUI: CLA Coefficients Banks Tab                                        | 89         |

| 6-5.  | Fusion GUI: Copy Design Window                                                | 90         |

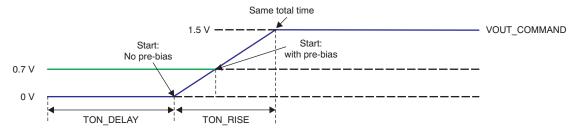

| A-1.  | TON_DELAY and TON_RISE                                                        | 93         |

| A-2.  | Trace C: PMBus Clock, Trace D: PMBus Data                                     | 95         |

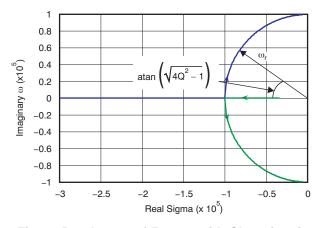

| B-1.  | Locus of Zeroes with Changing Q                                               | 98         |

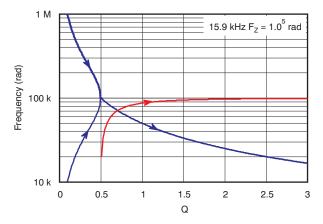

| B-2.  | Real and Imaginary Frequency vs Q                                             | 99         |

### **List of Tables**

| 2-1. | Example Assignment of PWM Outputs                       | 27 |

|------|---------------------------------------------------------|----|

|      | Resulting Power Stage to Multiplexer Address Assignment |    |

|      | Tracking Options                                        |    |

|      | Available UCD92xx Sequencing Pins                       |    |

|      | Output Dependency Configuration Bytes                   |    |

|      | AFE settings                                            |    |

|      | Example Circuit Component Values                        |    |

|      | Current Balance Update Rates                            |    |

|      | Example Spreading Factor (B) Values                     |    |

## Introduction

#### Overview

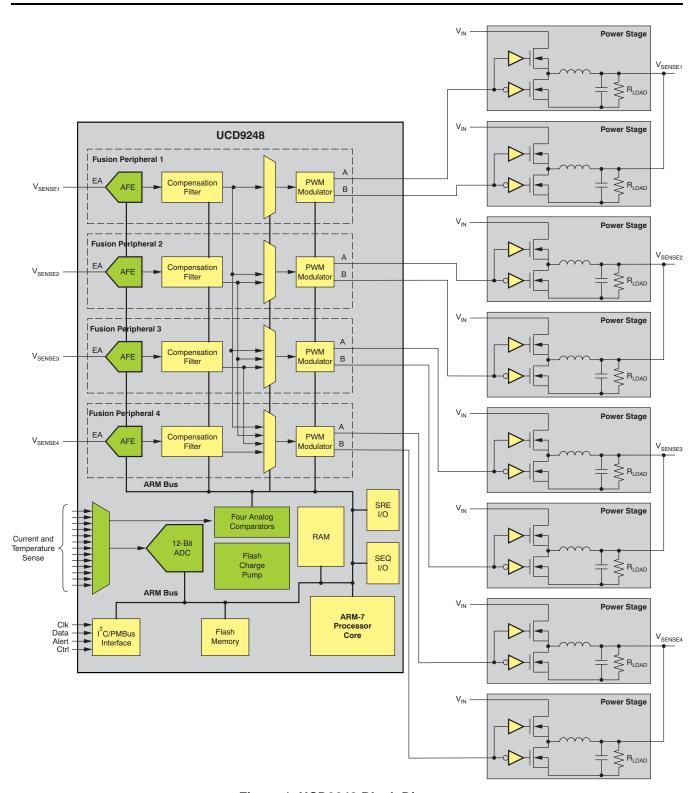

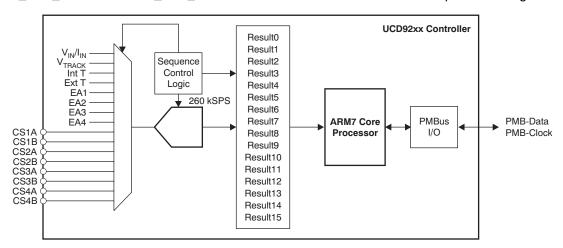

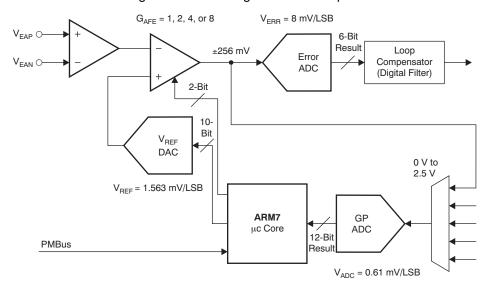

The <u>UCD92xx</u> family of digital pulse-width modulation (PWM) controllers are multi-rail, multi-phase synchronous buck digital devices designed for non-isolated dc/dc power applications. These controllers integrate dedicated circuitry for dc/dc loop management with flash memory and a serial interface to support configurability, monitoring, and management. These devices provide a wide variety of desirable features for non-isolated dc/dc converter applications while minimizing the total system component count by reducing external circuits. The solution integrates multi-loop management with sequencing, margining, tracking, and intelligent phase management to optimize the solution for total system efficiency. Additionally, loop compensation and calibration are supported without the need for additional external components. See Figure 1 for a block diagram of the UCD9248 as an example.

ARM7 is a trademark of ARM Ltd. I<sup>2</sup>C is a trademark of NXP Semiconductors. PMBus is a trademark of SMIF, Inc. All other trademarks are the property of their respective owners.

Overview www.ti.com

Figure 1. UCD9248 Block Diagram

www.ti.com Overview

The UCD92xx digital PWM controllers are PMBus™-compliant devices; they comply with and operate according to the PMBus version 1.1 or version 1.2 standards. The PMBus standard states that all configuration commands received by a device are first stored in volatile memory (RAM or hardware registers). These settings take effect immediately. To permanently configure the device, the PMBus command STORE\_DEFAULT\_ALL is issued. This command instructs the device to store all volatile configuration settings into nonvolatile memory (flash). In addition, the Fusion Digital Power Designer software graphical user interface (GUI) also maintains a level of configuration information called design information in the form of a project file that is stored as a Windows file.

To send design information to the device from the GUI, a **Write to Hardware** operation command is issued (normally by pressing a button on the left hand side of the GUI screen). The actual PMBus commands sent are shown in the log at the bottom right of the GUI. You must execute this command each time you make a design change that affects the configuration. To permanently store the configuration into the device, you must issue a **Store RAM to Flash** command. (This operation is always available under the *Device* drop-down menu.) To save your particular design information, which includes the power stage schematic that is not downloaded to the device, save the parameters from the Fusion GUI into an .xml project file.

The normal process of designing a power supply based on the UCD92xx series is to first create a project file using the GUI in *off-line mode* (that is, the software is not connected to a hardware device). In this mode, users select the voltage, switching frequency, rated current, and power stage circuit for each regulated voltage rail to be controlled by the UCD92xx device. Use the recommended component values and/or part numbers suggested by the Fusion software for the power stage circuits in order to complete the board schematic and layout. Once these parameters are established, fabricate and assemble the board with the related components.

Then apply power to the completed printed circuit board (PCB) and connect the PMBus to a PC with the Fusion Digital Power Designer GUI installed. The PC is generally connected to the PMBus with the TI USB Adapter. An unconfigured UCD92xx controller has all outputs disabled until the configuration stored in the previously created project file is downloaded to the device. Depending on the setting of ON\_OFF\_CONFIG, the power supply is now ready to accept a command to start regulating each controlled voltage rail. Once you have confirmed that each voltage rail can come up to the regulated voltage without errors, store any changes made to the configuration to the device flash memory, and then store the configuration to the project file.

Once the UCD92xx devices are configured to provide basic regulated power, they can be integrated into the overall management function of a system by communicating over the PMBus (with an I²C™ interface) from a microcontroller or FPGA. There are over 120 commands implemented in the device. The standard command syntax is found in the PMBus standard. The commands that are unique to the UCD92xx devices are found in the UCD92xx Command Reference, available for download at www.ti.com.

#### Information About Cautions and Warnings

This document contains caution statements.

#### **CAUTION**

This is an example of a caution statement. A caution statement describes a situation that could potentially damage your software or equipment.

The information in a caution or a warning is provided for your protection. Please read each caution carefully.

Overview www.ti.com

#### **Applications Questions**

There is a dedicated discussion forum for this device at <a href="http://e2e.ti.com/support/power\_management/digital\_power/default.aspx">http://e2e.ti.com/support/power\_management/digital\_power/default.aspx</a> on the TI website.

If you have questions about other Texas Instruments PWM controllers, post a question in the broader *Power* forum at <a href="http://e2e.ti.com">http://e2e.ti.com</a>. Include in the subject heading the product in which you are interested.

#### **Acknowledgements**

Much of the contents of this application note are based on correspondence between the design team at Texas Instruments and early customers of the device family. This information includes contributions on the operation of the PMBus interface from Karl Northrup; contributions on the behavior of the monitoring features from Mark Heminger; contributions on sequencing from Eric Oettinger; and descriptions of the operation of the Fusion Digital Power Designer software from Mike Muegel. I am also indebted to Brad Higgins, TI factory applications, for a review of the material, and to the work of the field application engineers who have helped numerous customers to use this device in their respective applications.

#### Electrostatic Discharge Warning

Many of the components on the UCD92xx are susceptible to damage by electrostatic discharge (ESD). Customers are advised to observe proper ESD handling precautions when unpacking and handling this device, including the use of a grounded wrist strap at an approved ESD workstation.

#### **CAUTION**

Failure to observe ESD handling procedures may result in damage to the device.

## **Quick-Start Guide**

This chapter presents 10 steps that show how to generate a project file that you can use to configure a device with the Fusion Digital Power Designer program.

Topic Page

| 1.1 | Procedure | 12 |

|-----|-----------|----|

| 1.2 | Summary   | 19 |

Procedure www.ti.com

#### 1.1 Procedure

Follow these steps to set up, configure, and create a project design file for use with the UCD92xx series of PWM controllers.

#### Step 1.

Download and install the latest version of the <u>Fusion Digital Power Designer</u> PC program, referred to as the **Fusion GUI** throughout this document.

#### Step 2.

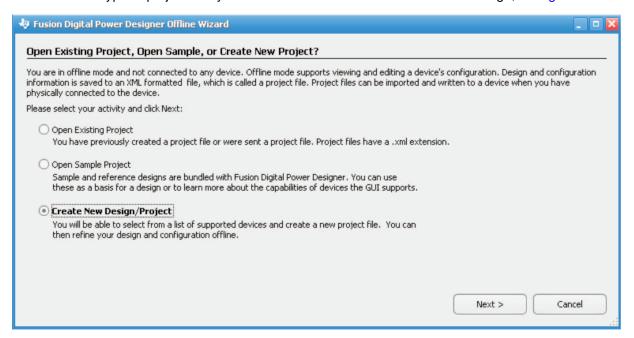

After installation, start the Fusion GUI. The Fusion GUI launches in offline mode, and prompts you to select the type of project that you wish to work on. Select *Create a New Design*, as Figure 1-1 shows.

Figure 1-1. Fusion Digital Power Designer Software GUI: Startup Screen (Offline Mode)

#### Step 3.

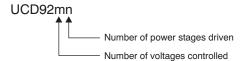

Pick the specific device you want to work with. Note that for most of the UCD92xx devices, the part number itself denotes the number of voltages that can be regulated and the number of power stages that can drive those voltage rails, as shown in Figure 1-2.

Figure 1-2. UCD92xx Naming Convention

www.ti.com Procedure

#### Step 4.

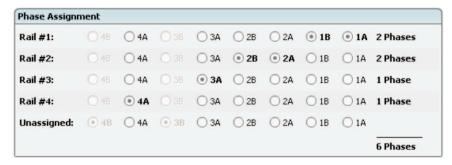

After you select the controller device, the GUI prompts you to define which PWM outputs are assigned to the respective  $V_{OUT}$  sense inputs. Note that in the Fusion GUI software, a MOSFET half-bridge is a *phase* and a regulated voltage is a *rail*. Figure 1-3 shows the phase assignment selection menu.

Figure 1-3. Fusion GUI: Phase Assignment Selection Menu

Regulated voltage Rail #1 is controlled by sensing its voltage at the  $EA_P1/EA_N1$  pins; voltage Rail #2 is controlled by sensing its voltage at  $EA_P2/EA_N2$ , and so on. The underlying PMBus command for this configuration is the PHASE\_INFO command.

#### Step 5.

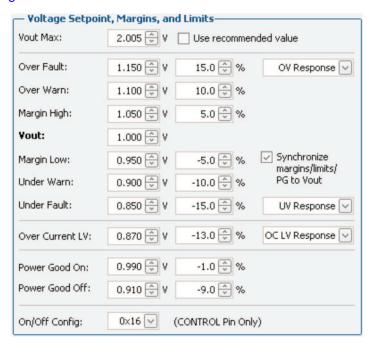

The GUI then takes you to the *Vout Config* page. This screen allows users to define the nominal regulated output voltage for each rail. The Fusion GUI then uses this value and a set of default percentages to define margin-high, margin-low, overvoltage (OV) warn level, OV fault level, undervoltage (UV) warn level, UV fault level, etc. Each of these output voltage related commands can be overridden with user-specific values. For this discussion, we simply select the default percentages presented, as Figure 1-4 shows.

Figure 1-4. Fusion GUI: Voltage Configuration Menu

Procedure www.ti.com

#### Step 6.

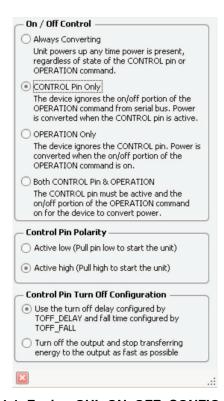

Next, you must determine the event(s) that tell your power supply to start. The PMBus standard identifies four events that can initiate regulation:

- The input voltage is greater than a configurable threshold.

- The CTRL line to the device goes active.

- The device receives an OPERATION command on the PMBus.

- The device receives an OPERATION command on the PMBus, and the CTRL line is active.

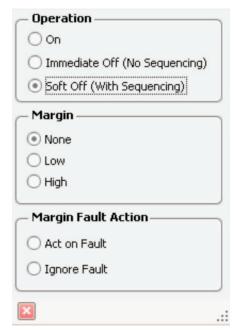

Each regulated voltage rail can be configured to have a different event initiate regulation. To configure the specific event that starts a particular voltage rail, click on the On/Off Config edit box; the Fusion GUI presents the list of events to select from.

To prepare for the initial device power-on, it is a good idea to set the On/Off Configuration to start on an OPERATION command. With this option, the output voltages are off when power is first applied to the board. Each voltage rail can then be turned on separately using the Fusion GUI. After you have tested each voltage rail, you can change the On/Off configuration to start with  $V_{\text{IN}}$  or with the CTRL signal.

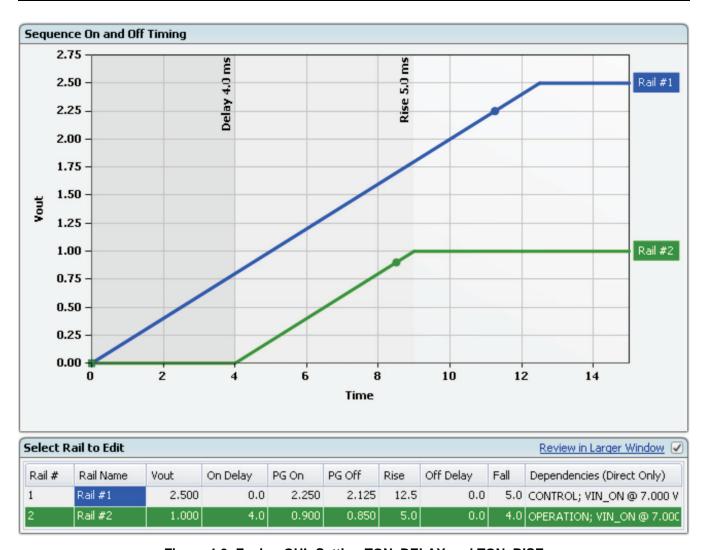

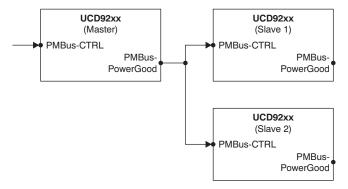

Set up the desired sequencing arrangement between the voltage rails. The UCD92xx controllers can perform complex sequencing procedures where one regulated voltage rail depends on other voltage rails and does not start until these rails are actively regulating. The sequencing can also depend on an external input signal. Additionally, a regulated voltage rail can be configured to track a second voltage under closed-loop control until the voltage being tracked exceeds the configured voltage for the regulated voltage rail. These features are reviewed in another section of this document.

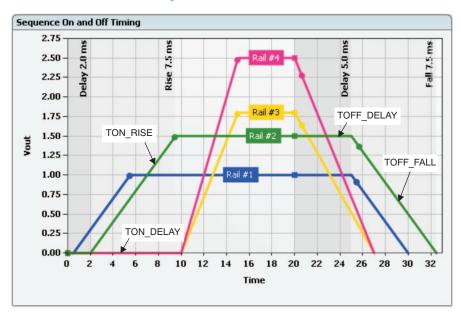

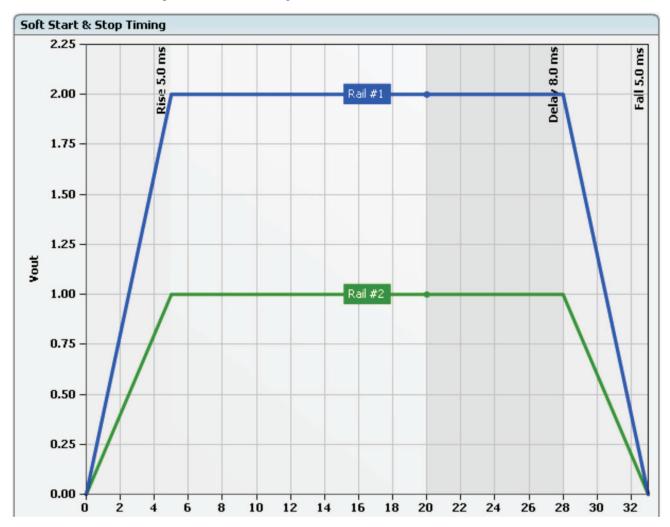

The simplest way to sequence several regulated voltage rails is to set the start delay and soft-start ramp time for each rail. The PMBus commands that set these timings are TON\_DELAY, TON\_RISE, TOFF\_DELAY, and TOFF\_FALL. Figure 1-5 illustrates these PMBus commands.

Figure 1-5. Fusion GUI: Start Delay and Soft-Start Ramp Time Configuration to Illustrate PMBus Commands

www.ti.com Procedure

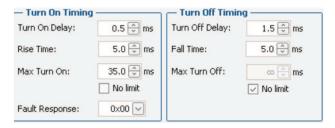

In the Fusion GUI, these values are entered in the *Turn On Timing* and *Turn Off Timing* boxes at the right of the *Vout Config* page, as shown in Figure 1-6.

Figure 1-6. Fusion GUI: Turn-On and Turn-Off Timing (Voltage Configuration)

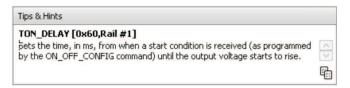

A detailed description of the underlying PMBus command and the range of allowable values for that command are displayed in the *Tips and Hints* window (such as Figure 1-7 illustrates) at the bottom of the screen when you hover the cursor over an editable parameter.

Figure 1-7. Fusion GUI: Tooltip Example

#### Step 7.

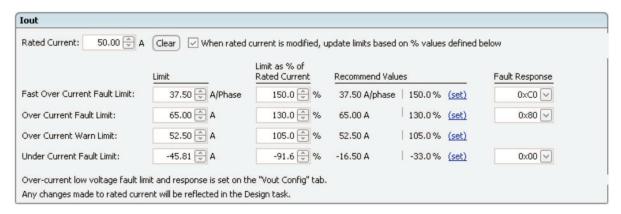

Next, go to the *lout, Vin, Temp Config* tab of the **Configure** page. Figure 1-8 shows this tab. You must define a *rated current* for the output voltage rail. This value is the maximum current for the power stage circuit that you will create later. Rated current is not a recognized PMBus command, but the Fusion GUI uses the concept of rated current to set the current-related PMBus commands such as OC warn level, OC fault level, voltage foldback setting, etc. The Fusion GUI also uses the rated current parameter to select various component values in the current sense circuits.

Figure 1-8. Fusion GUI: I<sub>OUT</sub>, V<sub>IN</sub>, and Temperature Configuration

A small icon with a *U* next to a given parameter setting indicates that the parameter has not yet been downloaded to the device. (The *U* means *Undo*.) Clicking this icon undoes the change. Pressing the **Write to Hardware** button at this point (or at any point in the process) sends any changes made to the configuration to the project file; if the software is connected to an active UCD controller, the **Write to Hardware** button sends the changes to the device registers as well. All PMBus commands sent when the **Write to Hardware** button is pressed are logged and can be retrieved for subsequent review. Note that when you switch between rails, any pending configurations are automatically written to the project file or device.

Procedure www.ti.com

#### Step 8.

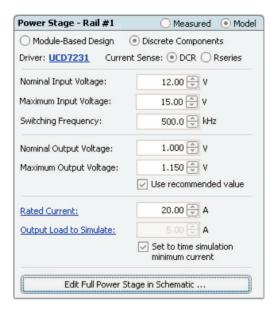

Go to the *Design* page of the GUI. This page requires that users specify the specific power stage that is to be used (a PTD power module or UCD7xxx-based circuit).

First, select whether the power stage is a module or consists of discrete components, as shown in Figure 1-9. Power modules contain a gate driver IC, MOSFETs, an inductor, input capacitor, and output capacitor. (1) If you choose to develop the power stage circuit yourself, select *Discrete Components*, then select the technique you plan to use to measure current. Last, select the *DCR* option, unless your current monitoring requirements are very stringent; this option does not reduce power-supply efficiency.

Figure 1-9. Fusion GUI: Design Menu

<sup>(1)</sup> The benefit of a choosing a power module is that it gives users the option of using an engineered layout of the circuits around the power MOSFETs, including the critical routing of ground currents between the MOSFETs and the input capacitor. However, this type of layout generally has an increased cost compared to a user-designed layout.

www.ti.com Procedure

#### Step 9.

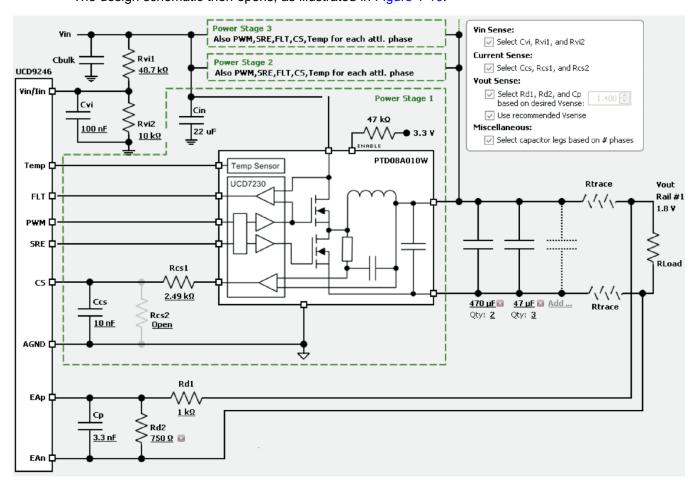

Now open the schematic by clicking the **Edit Full Power Stage in Schematic...** button. The design schematic then opens, as illustrated in Figure 1-10.

Figure 1-10. Fusion GUI: Design Schematic Example

At this point, users can select different inductors, insert additional output capacitance, and so forth. However, if you leave all the boxes in the upper right corner checked, each component is selected for you by the GUI and the design is complete (if you have selected a driver with internal MOSFETs; refer to Figure 1-9). If you choose a design with external MOSFETS, you must select those components yourself by clicking on the part numbers for Q1 and Q2.

Upon closing the design schematic, the Fusion GUI performs an *autotune* process to select a set of digital filter coefficients that properly compensate the voltage regulation loop for the power stage circuit specified by the schematic. The autotune algorithm attempts to minimize the closed-loop output impedance for the given schematic.

#### NOTE:

The compensation design is not written to the project file or to an attached device until the **Write to Hardware** button is pressed. This architecture allows users to try various loop compensation settings without concern for making the actual power-supply circuit unstable. A **Write to Hardware** operation must be performed for each rail. This requirement is unique to the design page. On the configuration page, when you switch from one rail to the next, any pending configuration changes are automatically applied.

Procedure www.ti.com

In addition to setting loop compensation, the Fusion GUI also issues the PMBus commands that set the scaling for sensing  $V_{IN}$ ,  $V_{OUT}$ ,  $I_{OUT}$ , temperature, and so forth, based on the circuit defined in the schematic. This software feature is controlled by the *Design* $\rightarrow$ *Device Synchronization* checkboxes. A more detailed description of this behavior is presented later in this document.

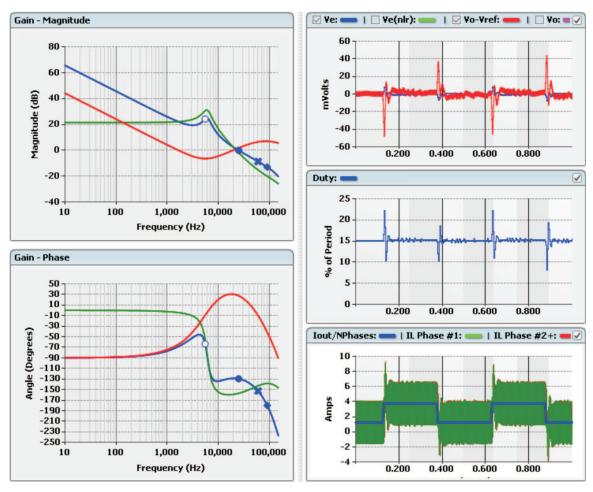

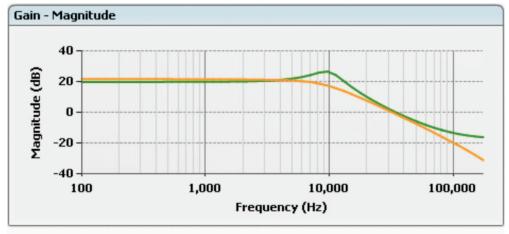

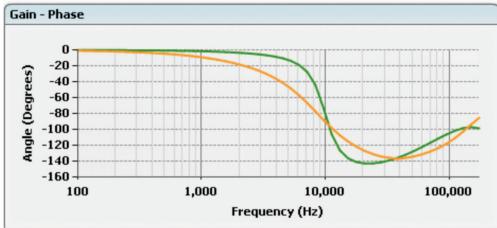

Now check the Bode plots and time simulation graphs of a load step (25% to 75% of rated current) on the design page in the GUI. If desired, the user can switch to manual compensation mode and make fine adjustments to the loop compensation in order to improve the step response. The compensation filter coefficients are sent to the device using the CLA\_GAINS command. Figure 1-11 shows the example Bode plots and simulation graphs.

Figure 1-11. Fusion GUI: Bode Plots and Simulation Graphs

#### Step 10.

Once you are satisified with the configuration, save it to a project file; use the *File/Save Project* menu command. If the GUI is connected to an actively powered device, selecting the **Store RAM to Flash** button issues a STORE\_DEFAULT\_ALL PMBus command and saves your configuration to nonvolatile memory on the device.

www.ti.com Summary

#### 1.2 Summary

The project file created in these 10 steps is the basis for operating your power-supply circuit hardware. Use the components recommended by the GUI to create the schematic and layout drawings that will be used to fabricate and populate your PCB assembly (PCBA). When the completed and assembled PCBA is ready, connect the controller PMBus to a PC using the TI USB Adapter. Apply power to the board and start the Fusion Digital Power Designer GUI. If the controller has never been configured, all the PWM outputs are disabled and no regulation occurs.

Import the project file into the GUI. Depending on the setting of the ON\_OFF\_CONFIG step (see Step 6), the power supply is now ready to accept a command to start regulating each controlled voltage rail. When you have confirmed that each voltage rail is active and error-free, save any final changes to the configuration to the device flash memory and then save the configuration to the project file.

The balance of this document describes the underlying functions of the Fusion Digital Power Designer software. For most applications, the Fusion GUI does the work of designing a complete power system; it is not necessary to understand all the details presented here. However, if a given power system is exhibiting behavior different from what is expected based on the software, it may be helpful to have a complete description of the design equations.

## Circuit Considerations Using the UCD92xx

This chapter describes the design of the circuits that the UCD92xx will control, starting with the layout of the voltage sense signals. The power stage that is controlled by the UCD92xx consists of a gate driver, power MOSFETs, and output LC filter circuits. The equations presented in this chapter are the same equations used by the Fusion GUI. In most cases, the easiest method is to allow the Fusion software determine the circuit component values, and refer to this document if a specific application has unique requirements. Additional information regarding the power stage circuits in the product data sheet for the various gate driver ICs is also included.

| 2.1  | Circuit Board Design                                          | 22 |

|------|---------------------------------------------------------------|----|

| 2.2  | Temperature Monitoring                                        | 26 |

| 2.3  | Current Monitoring                                            | 29 |

| 2.4  | Inductor Derating Used by the Fusion GUI                      | 31 |

| 2.5  | Determining IOUT_CAL_GAIN and IOUT_CAL_OFFSET                 | 32 |

| 2.6  | Calibration of IOUT_CAL_GAIN and IOUT_CAL_OFFSET              | 32 |

| 2.7  | Filtering Requirements on the UCD723x CS Outputs              | 34 |

| 2.8  | Filtering Requirements on the UCD7242 and UCD74106 CS Outputs | 34 |

| 2.9  | Calculation of UCD7230A ILIM Voltage                          | 35 |

| 2.10 | Calculation of UCD7231 ILIM Voltage                           | 36 |

Circuit Board Design www.ti.com

#### 2.1 Circuit Board Design

#### 2.1.1 Power Stage Schematics

A typical power system controlled by a UCD92xx device has multiple voltage rails with specific start-up and shutdown sequencing requirements. For the purpose of this document, we will assume a system that requires power has eight voltage rails and fits in a 19-inch (48.26-cm) rack. For a large board similar to this one, we want the generation of power to be located close to the IC that requires the power; the regulation controller, on the other hand, can be located anywhere on the PCB that is convenient. Thus, we want the output capacitors, inductor, MOSFETs, and gate drive circuits placed in close proximity to the powered IC. Figure 2-1 illustrates this configuration.

Figure 2-1. Typical Multi-Voltage-Rail Board

In addition, we also want the circuits that sense current to be close to the load. Because the currents may be large, in order to keep the impact on power conversion efficiency small, the voltage across the sense element must also be kept small. For this reason, the UCD92xx controllers do not include a current sense amplifier in the controller. Instead, each UCD72xx gate drive IC has a current sense amplifier to condition this small current sense voltage and send it to the digital controller.

When you select a power stage circuit to be controlled by the UCD92xx, you must make three significant design decisions:

- 1. Whether to lay out the gate drive, MOSFETs, inductor, and capacitors locations yourself, or purchase a power module with an engineered and tested circuit layout;

- 2. Whether to use external power MOSFETs or select a gate drive IC with power MOSFETs integrated into the device; and

- 3. Which type of circuit is to be used to detect load current.

For the first question, selecting a power module has a significant advantage: the layout of the input capacitor(s) relative to the MOSFETs has been tested and proven to be sufficiently tight, thereby ensuring that ringing on the ground and circulating currents has been minimized. The cost of this engineered design is reflected in the price of a power module compared to the cost of the individual components purchased separately.

As a response to the second question, consider whether the design uses voltage rails that must supply 10 A or less, or whether board space is at a premium. In either case, a gate driver with internal MOSFETS is a good choice. The UCD7242 provides two 10-A power stages and the UCD74106 provides a single 6-A power stage. Above 10 A, the power stage circuit must either gang multiple UCD7242 stages together, or users must select a design with external MOSFETs.

www.ti.com Circuit Board Design

To answer the third question in a broad sense, there are three commonly-used circuits available to measure load current:

- If the MOSFETs are internal to the gate drive IC, current mirroring techniques can be used to sense

the voltage across the R<sub>DS(ON)</sub> segment of the MOSFETs; these techniques then amplify this voltage

and make it available to the controller. The UCD7242 and UCD74106 devices follow this approach.

- A second option is to add a sense resistor in series with the load. The differential voltage across the sense resistor can then be applied to the input of the current sense amplifier.

- The third approach is to measure the voltage across the resistance of the copper windings in the inductor. This method has the advantage of providing a current sense voltage without inserting any additional losses into the system.

The description of this third method is detailed in Section 2.3.1.

#### 2.1.2 Differential Sense Lines

The UCD92xx controller has up to four differential error amplifier inputs to sense the voltage that is to be regulated. This architecture allows the controller to be placed some distance away from the point where precise voltage regulation is required. Figure 2-2 shows the case where the UCD92xx is located on the same board as the load that receives the regulated voltage. Typically, the gate driver and MOSFETs are located in fairly close proximity to the load to minimize wiring losses. The voltage sense signals should be laid out as a differential pair of traces, terminating at a decoupling capacitor located at the IC that is being powered. To ensure that the PCB layout tools properly feed the voltage sense back to the controller as a differential pair, a small resistor can be placed near the decoupling capacitor.

Figure 2-2. Single Board V<sub>out</sub> Sense

It is recommended that an RC network be placed across the differential sense lines near the UCD92xx to act as an antialias filter. This filter should have a corner frequency that is 35% of the switching frequency. The recommended value of  $R_{D1}$  is 1.0 k $\Omega$ . Making  $R_{D1}$  larger than this value may cause an error in the sensed voltage because of the non-zero offset currents present at the input to the error amplifier. Equation 1 shows the calculation of the input filter capacitor.

$$C_{P} = \frac{\sqrt{2}}{\pi F_{SW} R_{D1}} \left[ 1 + \frac{R_{D1}}{R_{D2}} \right]$$

(1)

Circuit Board Design www.ti.com

When the power supply controlled by the UCD92xx is on a separate board from the load, as shown in Figure 2-3, the differential sense leads can be brought out separately; this technique enables the regulated voltage to not droop as a result of the wires from the power supply to the load. In this case, a pair of  $10-\Omega$  resistors connect the output of the power stage with the UCD92xx error amplifier inputs. This configuration allows the output voltage to be controlled if the remote sense leads are not attached. When the remote sense signals are connected, the  $10-\Omega$  resistors are shorted out and the controller sees the actual voltage at the load. Texas Instruments' EVM boards use this remote sense circuit configuration because the EVM is typically separate from the load.

Figure 2-3. 10-Ω Backup Circuit for Remote Sense

#### 2.1.3 3.3-V and 1.8-V Core Voltage Decoupling

The UCD92xx controller can be powered from a 3.3-V supply, or from  $V_{IN}$  through a series pass transistor controlled by the V33FB pin. The core logic in the controller operates at 1.8 V. The digital PWM circuits are clocked by an internal 250-MHz oscillator. The microcontroller that manages the PMBus interface and responds to faults is clocked at 31 MHz. These clocks are fast enough that good decoupling of the 3.3-V and 1.8-V power is required for proper device operation.

The <u>product data sheet</u> states that  $0.1-\mu F$  and  $4.7-\mu F$  bypass capacitors should be connected from V33A and V33D to ground near the device. In addition, a  $0.1-\mu F$  to  $1-\mu F$  bypass capacitor must be connected from the BPCap pin to ground for the internal 1.8-V supply to the device logic circuits. As with any digital device with fast clock edges, decoupling capacitors should be placed so that they are physically close to the device. This requirement means that vias should be avoided between the decoupling capacitors and the power and ground pins. Placing additional decoupling capacitors (0.01  $\mu F$  to 0.1  $\mu F$ ) close to each power pin is also recommended.

www.ti.com Circuit Board Design

Figure 2-4 illustrates the recommended decoupling capacitor layout.

Figure 2-4. Recommended Decoupling Capacitor Layout

The UCD92xx device has separate analog and digital ground pins, and separate analog, digital, and I/O power pins. Tying the analog and digital ground together to a ground plane under the controller has been shown to produce good results. The V33A pin requires very good decoupling. If desired, this pin can be separated from the V33D and V33IO pins with a ferrite bead; in most cases, this bead is not necessary.

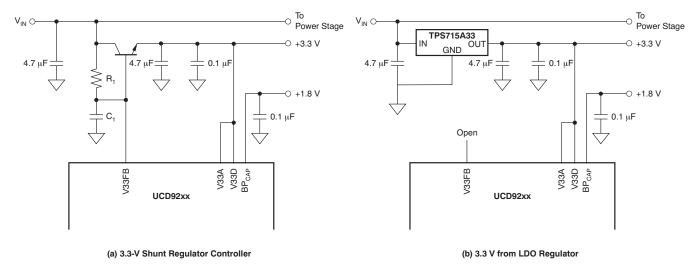

Figure 2-5 shows a typical application using an external transistor. The base of the transistor is driven by resistor  $R_1$  to  $V_{IN}$  and a transconductance amplifier with the output on the V33FB pin. The NPN emitter becomes the 3.3-V supply for the chip. Figure 2-5(a) illustrates an external transistor with a shunt regulator controller; a configuration with the 3-3 V provided from a low-dropout (LDO) regulator is shown in Figure 2-5(b).

Figure 2-5. Providing 3.3-V Power for the Controller

In order to generate the correct voltage on the base of the external pass transistor, the internal transconductance amplifier sinks current into the V33FB pin and a voltage is produced across  $R_1$ . This resistor value should be chosen so that  $I_{SINK}$  is in the range of 0.2 mA to 0.4 mA.  $R_1$  is defined by Equation 2.

$$R_{1} = \frac{V_{IN} - 3.3 \text{ V} - V_{BE}}{\frac{I_{E}}{(\beta + 1)} + I_{SINK}}$$

(2)

where:

- I<sub>SINK</sub> is the current into the V33FB pin;

- V<sub>IN</sub> is the power-supply input voltage, typically 12V;

- I<sub>E</sub> is the current draw of the device and any pull-up resistors tied to the 3.3-V supply;

- β is the beta of the pass transistor.

For  $I_{\text{SINK}} = 0.3$  mA,  $V_{\text{IN}} = 12$  V,  $\beta = 99$ ,  $V_{\text{BE}} = 0.7$  V, and  $I_{\text{E}} = 50$  mA, this formula selects  $R_{\text{1}} = 10$  k $\Omega$ . Weaker transistors or larger current loads require a lower resistance value to maintain the desired  $I_{\text{SINK}}$  current. For example, lowering  $\beta$  to 40 would require  $R_{\text{1}} = 5.23$  k $\Omega$ ; likewise, an input voltage of 5 V requires a value of 1.24 k $\Omega$  for  $R_{\text{1}}$  with the standard  $\beta = 99$  transistor.

The capacitor  $C_1$  in Figure 2-5(a) acts to compensate the loop that regulates the internal 3.3 V. As  $R_1$  changes, a proportional change to  $C_1$  must be made. Equation 3 shows this relationship.

$$C_1 = \frac{0.001}{R_1} \tag{3}$$

#### 2.2 Temperature Monitoring

#### 2.2.1 Internal Temperature Sense

The internal temperature of the controller die is periodically sampled by the 12-bit analog-to-digital converter (ADC). The temperature can be monitored by issuing a READ\_TEMPERATURE\_1 PMBus command. The expected relationship of the sensed temperature to the discrete value at the output of the ADC is given by Equation 4.

$$T_{LSB} = round \left[ \frac{10.44LSB}{^{\circ}C} T_{Internal} \right] + 2559LSB$$

(4)

This value is scaled by the firmware in the ARM7<sup>™</sup> core processor and returned on the PMBus using Equation 5.

$$T_{\text{C}} = T_{\text{LSB}} \frac{1.0^{\circ} \text{C}}{10.44 \text{LSB}} - 245^{\circ} \text{C}$$

(5)

Therefore, the maximum temperature that can be returned is approximately +150°C.

#### 2.2.2 External Temperature Sense

The UCD92xx is also able to measure the temperature of the inductor (and/or MOSFETS) of each controlled power stage. This temperature measurement is used to correct the monitored current when the dc resistance of the inductor is used to sense current. External temperature measurement is also used to detect an overtemperature fault. The device provides either one analog external temperature input pin and three select lines that can be used to drive an external analog multiplexer, or dedicated temperature sense inputs, so that up to eight external temperatures can be monitored.

www.ti.com Temperature Monitoring

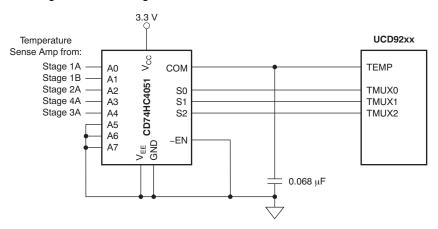

One example multiplexer that can be used is the <a href="CD74HC4051">CD74HC4051</a>. The three mux select lines TMUX0, TMUX1, and TMUX2 continuously cycle through all eight mux channel addresses. However, the CS signals are logically assigned to the mux input channels in the same order that they are defined by the PHASE\_INFO command. Given the following case (summarized in Table 2-1), where voltage Rail #1 is driven by two phases and Rail #3 uses PWM4A (perhaps because it lays out more efficiently than using PWM3A), the temperature sensor outputs are routed to the mux as shown in Table 2-2.

Table 2-1. Example Assignment of PWM Outputs

| Voltage Rail | PWM Output |

|--------------|------------|

| 1            | PWM1A      |

| ı            | PWM1B      |

| 2            | PWM2A      |

| 3            | PWM4A      |

| 4            | PWM3A      |

Table 2-2. Resulting Power Stage to Multiplexer Address Assignment

| Mux Address | Power Stage |

|-------------|-------------|

| 0           | 1A          |

| 1           | 1B          |

| 2           | 2A          |

| 3           | 4A          |

| 4           | 3A          |

| 5           | n/a         |

| 6           | n/a         |

| 7           | n/a         |

Figure 2-6 illustrates the example outlined in Table 2-1 and Table 2-2. The 68-nF capacitor rolls off the temperature sense signal at 12 kHz, given the nominal  $200-\Omega$  on-resistance of the multiplexer.

Figure 2-6. External Temperature Sense Multiplexer

Various circuits can be used to sense temperature. A dedicated temperature sensor IC has the best accuracy and linearity, but typically are the most expensive to purchase. Thermistors, on the other hand, are generally available at a lower cost, but have poor linearity compared to temperature sensors.

#### 2.2.3 Thermistor Temperature Sense

The resistance of a thermistor changes exponentially with temperature. Equation 6 shows this relationship, where B and  $R_{REF}$  are specified in the data sheet for a given device.

$$R_{T} = R_{REF} \exp \left[ B \left( \frac{1}{T} - \frac{1}{T_{REF}} \right) \right]$$

(6)

For instance, consider a Murata NCP15WB473J03 NTC thermistor: B = 4050 kelvins;  $T_{REF}$  = 298 kelvins, and  $R_{REF}$  = 47 k $\Omega$ .

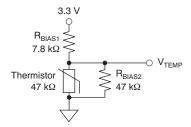

The temperature response of a thermistor can be linearized by placing it in a resistive voltage divider. Figure 2-7 uses the  $47-k\Omega$  Murata thermistor to illustrate this configuration.

Figure 2-7. Thermistor Circuit

The thermistor itself has very nonlinear characteristics. However, if it is used as the bottom half of a resistor divider, the nonlinearity is virtually canceled out, and the voltage becomes linear over a wide range. In the circuit of Figure 2-7, the second bias resistor pushes the linear region toward the high end of the temperature range.

From Equation 6 and the bias circuit in Figure 2-7, we can determine the slope of the temperature sense output voltage in Equation 7.

$$\frac{dv_{T}}{dT} = V_{REF} \frac{B}{T^{2}} \left[ \frac{R_{T}R_{B1}}{R_{T}R_{B1} + R_{T}R_{B2} + R_{B1}R_{B2}} + \frac{R_{T}^{2}R_{B2}(R_{B1} + R_{B2})}{(R_{T}R_{B1} + R_{T}R_{B2} + R_{B1}R_{B2})^{2}} \right]$$

(7)

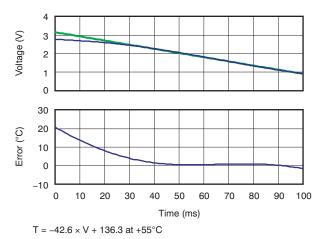

If we evaluate this formula for a given operating temperature (for example, +55°C, or 328 degrees Kelvin), then the values for the PMBus commands TEMPERATURE\_CAL\_GAIN and TEMPERATURE\_CAL\_OFFSET can be determined as shown in Equation 8.

TEMPERATURE\_CAL\_GAIN =

$$\frac{1}{\frac{dv_{T}(T_{OP})}{dT}}$$

TEMPERATURE\_CAL\_OFFSET =

$$T_{OP} - \frac{V_{OP}}{\frac{dV_T(T_{OP})}{dT}}$$

(8)

where

$$V_{OP} = \frac{R_{B2}}{R_{B1} + R_{B2} + \frac{R_{B1}R_{B2}}{R_{T}(T_{OP})}} V_{REF}$$

(9)

www.ti.com Current Monitoring

A plot of the temperature sense voltage and the expected error, given the linear gain and offset configuration in the UCD92xx, is shown in Figure 2-8.

Figure 2-8. Thermistor Circuit Response

#### 2.3 Current Monitoring

There are several techniques available to measure the output current of a power supply controlled by a UCD92xx device. In each case, the voltage across a series element feeds to an amplifier that generates a voltage; that voltage, in turn, is routed to the CS inputs of the UCD92xx.

Within the UCD92xx, the current sense signal is routed to a 12-bit ADC, shown in Figure 2-9. This voltage is converted to a current based on the configuration defined in the PMBus commands IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET. In the case of a multi-phase regulated output (that is, multiple MOSFET/inductor power stages driving one voltage rail), each power stage is configured by a separate IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET command.

In addition, the current sense signal input on the A CS inputs is routed to an analog comparator for fast overcurrent protection. The threshold for this fast comparator is set by the FAST\_OC\_FAULT\_LIMIT command. The units for this command are amps (A), and the controller uses the values defined in the IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET commands to set the actual comparator voltage threshold.

Figure 2-9. Block Diagram of the 12-Bit ADC Used for Monitoring

Current Monitoring www.ti.com

#### 2.3.1 Calculation of the Current Sense Voltage Using Inductor DCR

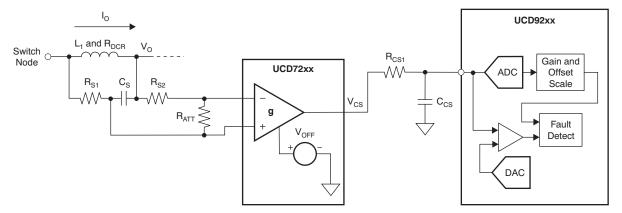

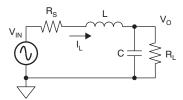

Many modern dc/dc power supplies measure output current by sensing the voltage across the winding resistance of the power stage inductor. The sensing circuit consists of a differential amplifier and an RC network that cancels the R/L zero of the inductor. Figure 2-10 shows the important circuit elements.

Figure 2-10. Current Sense Schematic: Direct Current Resistance (DCR) Current Sense

In addition, there is an optional low-pass network on the output of the current sense amplifier to provide antialias filtering for the ADC in the controller. The Fusion GUI determines the required component values to correctly measure the current across the dc resistance of the inductor. For reference, the following equations show the calculations used by the design tool.

The transfer function from sensed current to the output of the current sense amplifier is given in Equation 10.

$$v_{CSA} = \frac{G_{CSA} \frac{R_{ATT}}{(R_{S2} + R_{ATT})C_S} \left[ s + \frac{R_{DCR}}{L} \right] i_O}{s^2 + \frac{L + (R_{S1} + R_{DCR})(R_{S2} + R_{ATT})C_S}{(R_{S2} + R_{ATT})LC_S} s + \frac{R_{DCR} + R_{S1} + R_{S2} + R_{ATT}}{(R_{S2} + R_{ATT})LC_S}}$$

(10)

We would like to cancel the  $R_{DCR}/L$  zero in the transfer function of Equation 10. This result occurs when Equation 11 is valid.

$$\frac{R_{S1}(R_{S2} + R_{ATT})}{R_{S1} + (R_{S2} + R_{ATT})} C_S = \frac{L}{R_{DCR}}$$

(11)

From Equation 11, therefore, we can define the value for  $R_{\rm S1}$  as Equation 12.

$$R_{S1} = \frac{(R_{S2} + R_{ATT})L}{R_{DCR}C_S(R_{S2} + R_{ATT}) - L}$$

(12)

However,  $R_{S1}$  is a function of  $R_{ATT}$ . Consequently, before we can determine  $R_{S1}$ , we need to determine if the voltage across the inductor winding resistance must be attenuated by  $R_{ATT}$ .

#### 2.3.2 Calculation of Attenuation Resistor $R_{ATT}$

At dc, the output voltage of the current sense amplifier (as calculated in Equation 10) becomes that shown by Equation 13.

$$V_{CSA} = G_{CSA} \frac{R_{ATT}}{R_{S1} + R_{S2} + R_{ATT}} R_{DCR} i_L + V_{OFF}$$

(13)

When is the attenuation resistor R<sub>ATT</sub> necessary? It is needed to ensure that the current sense amplifier voltage does not saturate.

The maximum voltage for the fast overcurrent comparator in the UCD92xx is 2.0 V. Therefore, we want the current sense output voltage to be 2.0 V, when the current is at a level that generates a fault condition. We can find the required attenuation by solving Equation 6 and Equation 7 for  $R_{\text{ATT}}$  and  $R_{\text{S1}}$ . Unfortunately, this solution is rather messy. However, there are two cases that we are most interested in:

- 1. For the UCD7230A gate driver, the recommended circuit has  $R_{S2} = R_{S1}$ .

- 2. For the UCD7231 and UCD7232, the recommended circuit has  $R_{\text{S2}}$  = 0  $\Omega$ .

For the UCD7230A, where  $R_{S2} = R_{S1}$  and  $\Delta v_{CS} = 2.0 - 0.6 = 1.4$ , this result simplifies to Equation 14.

$$R_{\text{ATT}} = \frac{L}{C_{\text{S}}} \frac{4G_{\text{CSA}} \Delta v_{\text{CS}} i_{\text{L\_Max}}}{\left(G_{\text{CSA}} R_{\text{DCR}} i_{\text{L\_Max}}\right)^2 - \Delta v_{\text{CS}} i^2}$$

$$R_{S1} = \frac{L}{C_S} \frac{2G_{CSA}i_{L_{Max}}}{(G_{CSA}R_{DCR}i_{L_{Max}} + \Delta v_{CS}i)}$$

(14)

For the UCD7231, where  $R_{S2} = 0$  and  $\Delta v_{CS} = 2.0 - 0.5 = 1.5$ , the calculation is shown in Equation 15.

$$R_{\text{ATT}} = \frac{L}{C_{\text{S}}} \frac{G_{\text{CSA}} i_{\text{L}_{\text{Max}}}}{G_{\text{CSA}} R_{\text{DCR}} i_{\text{L}_{\text{Max}}} - \Delta v_{\text{CS}}}$$

$$R_{S1} = \frac{L}{C_S} \frac{G_{CSA} i_{L_{Max}}}{\Delta V_{CS}}$$

(15)

In either Case (1) or Case (2), if the equation for  $R_{ATT}$  results in a very large ( greater than 100 k $\Omega$ ) or a negative value, the attenuation resistor is not necessary;  $R_{S1}$  is thus calculated as shown in Equation 16.

$$R_{S1} = \frac{L}{R_{DCR}C_S} \tag{16}$$

The Fusion GUI software uses these equations to recommend the DCR current sense circuit component values.

#### 2.4 Inductor Derating Used by the Fusion GUI

When calculating the RC network values that sense the voltage across the inductor DCR, the *inductance* is derated by 90% to account for the effect of B-H saturation at elevated current and temperature. The dc *resistance* (DCR) of the inductor is derated as shown in Equation 17.

$$R_{DCR(Warm)} = R_{DCR} \left[ 1 + THERMAL\_COEFF(55^{\circ} - 25^{\circ}) \right]$$

$$R_{DCR(Hot)} = R_{DCR} \left[ 1 + THERMAL\_COEFF(100^{\circ} - 25^{\circ}) \right]$$

(17)

To determine if  $R_{ATT}$  is necessary,  $R_{DCR(HOT)}$  calculation is used to determine the maximum voltage expected out of the current sense amplifier, as Equation 18 shows.

$$V_{CS} = G_{CSamp} R_{DCR(Hot)} I_{MAX}$$

(18)

Where  $I_{MAX}$  is the specified FAST\_OC\_FAULT\_LIMIT. If this value is greater than 2.0 V (the maximum threshold at which the UCD92xx trips the Fast OC analog comparator), the GUI applies Equation 8 or Equation 9 to calculate  $R_{ATT}$ . The value for  $R_{DCR(WARM)}$  is used in these equations to determine  $R_{S1}$  and  $R_{ATT}$ .

#### 2.5 Determining IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET

The current sense voltage for the various methods of monitoring current can be described as shown in Equation 19: *current* times *sense resistance* times *current sense amplifier gain*, plus an offset (to allow for the measurement of negative current).

$$V_{CS} = G_{AMP}R_{SENSE}I_{OUT} + V_{OFF}$$

(19)

Then the controller uses the PMBus commands IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET to report the current as shown in Equation 20.

$$I_{MON} = (v_{CS} \text{ Volts}) \left[ \frac{1 \text{ Amp}}{\text{IOUT\_GAIN mV}} \right] \left( \frac{1000 \text{ mV}}{\text{Volt}} \right) + \text{IOUT\_OFFSET}$$

$$= (G_{AMP} R_{SENSE} I_{OUT}) \left( \frac{1000}{\text{IOUT\_GAIN}} \right) + v_{OFF} \left( \frac{1000}{\text{IOUT\_GAIN}} \right) + \text{IOUT\_OFFSET}$$

(20)

Therefore, the OFFSET and GAIN parameters are calculated as Equation 21.

$$IOUT\_CAL\_GAIN = G_{AMP}R_{SENSE}1000$$

$$IOUT\_CAL\_OFFSET = \frac{-V_{OFF}}{G_{AMP}R_{SENSE}}$$

(21)

#### 2.6 Calibration of IOUT\_CAL\_GAIN and IOUT CAL OFFSET

As a result of effects of board trace resistance and tolerances in the current sense circuit, the values for IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET for the physical PCBA may be somewhat different that the calculations discussed in this document. If the existing load current can be estimated, an additional load can then be applied in parallel with the application load and the gain and offset values calibrated for the actual physical PCB layout. Where high accuracy is required, this calibration can be done for each phase of every rail of every board as part of a manufacturing calibration process. More typically, users may sample a series of early prototype boards in the lab and then tweak the values of IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET. These resulting values, based on real measurements, can be stored in the project file for the device instead of those calculated by the GUI.

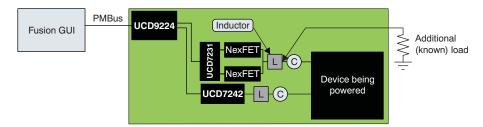

Figure 2-11 shows an example system board with one UCD9224 controller regulating two voltage rails. Here, an additional load is connected in parallel with the load on the board in order to calibrate the IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET values.

Figure 2-11. Adding an Additional Load to Check/Calibrate IOUT\_CAL\_GAIN

The load side of the inductor is typically an easy location to insert an additional load.

If we measure two or more points of estimated load current and note the value of the current monitored by the UCD92xx, we can calculate a correction to the first-pass estimates of IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET. From these two or more points, we can then calculate a slope, k, and offset, I<sub>OFF</sub>, that relate the monitored current to the actual current as shown in Equation 22. One common method of calculating the slope and offset for more than two data points is to use the linear regression functions in a spreadsheet.

$$I_{MON}(n) = k \cdot I_{OUT}(n) + I_{OFF}$$

(22)

If the initial values of IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET are perfectly accurate, then k should be 1.0 and  $I_{OFF}$  should be 0.0. If this condition is not the case, then we can use k and  $I_{OFF}$  to correct the IOUT\_CAL values. From Equation 12, we see that Equation 23 is valid.

$$I_{MON}(n) = (G_{AMP}R_{SENSE}) \left[ \frac{1000}{IOUT\_GAIN} I_{OUT}(n) + v_{OFF} \left[ \frac{1000}{IOUT\_GAIN_1} \right] + IOUT\_OFFSET_1$$

(23)

Then the slope and offset are given by Equation 24:

$$k = (G_{\text{AMP}}R_{\text{SENSE}}) \left[ \frac{1000}{\text{IOUT\_GAIN}_1} \right]$$

$$I_{OFF} = V_{OFF} \left[ \frac{1000}{IOUT\_GAIN_1} \right] + IOUT\_OFFSET_1$$

(24)

The actual current sense amplifier gain and offset are shown by Equation 25:

$$(G_{AMP}R_{SENSE}) = k \left[ \frac{IOUT\_GAIN_1}{1000} \right]$$

$$V_{OFF} = (I_{OFF} - IOUT\_OFFSET_1) \left[ \frac{IOUT\_GAIN_1}{1000} \right]$$

(25)

Substituting into Equation 13, we find that the IOUT\_CAL correction is calculated by Equation 26.  $IOUT\_CAL\_GAIN_2 = k \cdot IOUT\_GAIN_1$

$$IOUT\_OFFSET_2 = \frac{IOUT\_OFFSET_1 - I_{OFF}}{k}$$

(26)

If there are only two measured values of load current and UCD92xx monitored, then the formula for k and  $I_{\text{OFF}}$  are relatively simple and can be incorporated directly into the correction formula, shown in Equation 27:

$$IOUT\_CAL\_GAIN_{2} = IOUT\_GAIN_{1} \left( \frac{I_{MON1} - I_{MON2}}{I_{LOAD1} - I_{LOAD2}} \right)$$

$$IOUT\_OFFSET_{2} = \frac{I_{MON1}I_{LOAD2} - I_{MON2}I_{LOAD1} + (I_{LOAD1} - I_{LOAD2})IOUT\_OFFSET_{1}}{I_{LOAD1} - I_{LOAD2}}$$

(27)

#### 2.7 Filtering Requirements on the UCD723x CS Outputs

As noted above, the UCD92xx devices sample current with a 12-bit ADC. This ADC can sample up to 16 channels at 260 kS/s. These readings are scaled and processed by the core processor within the device at a sample period of 200  $\mu$ s / number of rails. Therefore, if the device is configured for one rail, the sample rate of measuring current is 5 kHz with each power stage current for that rail sampled consecutively at 260 kS/s. If four rails are configured, the sample rate for the current of any one rail is 1.25 kHz.

In addition to the measurement of current with the 12-bit ADC, the A CS inputs to the UCD92xx also have a programmable fast analog comparator that can be configured to terminate PWM action in case of an overcurrent condition. Assume that the fast OC threshold is set to the maximum limit of 2.0 V; further assume that the nominal operating current corresponds to a current sense voltage of 1.5 V. If we set a criteria that the current is to suddenly double, we would want to detect the OC event and shut down the device in 10  $\mu$ s. Thus, we want to set the filter time constant so that there is a 0.5-V change in voltage because of a 1.5-V change in the output of the current sense amplifier in 10  $\mu$ s. Equation 28 expresses this mathematically.

$$RC = \frac{\Delta t}{\ln\left(1 - \frac{\Delta V_{CS}}{\Delta V_{I}}\right)} = \frac{10 \,\mu s}{\ln\left(1 - \frac{0.5}{1.5}\right)} = 24.7 \,\mu s \tag{28}$$

Therefore, the RC filter on each of the current sense inputs should have a bandwidth of 6.45 kHz. The Fusion GUI software recommends values of  $R_{CS}$  = 2.49 k $\Omega$  and  $C_{CS}$  = 10 nF, respectively.

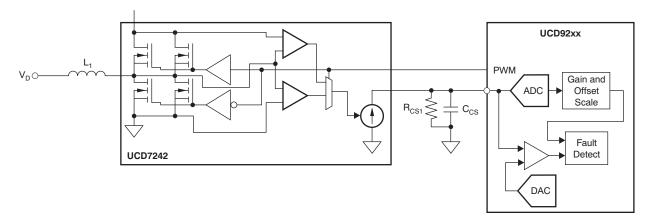

#### 2.8 Filtering Requirements on the UCD7242 and UCD74106 CS Outputs

Given the sampling rate in the UCD92xx, we must apply the same 6.5-kHz low-pass rolloff to the current sense output for the drivers with internal MOSFETs, as illustrated in Figure 2-12. These devices measure the current in the MOSFETs directly, multiplexing the current sense depending on which FET is active. The current sense output is a current proportional to the sensed current. In this way, the transresistance gain  $(V_{CS}/I_{OLIT})$  can be selected by adjusting  $R_{CS1}$ .

Figure 2-12. Current Sense for Drivers with Internal MOSFETS

For the UCD7242 driver, the current sense gain is 20  $\mu$ A/A. A 10-k $\Omega$  resistor then produces a transresistance gain of 0.2 V/A; the current sense voltage is 2.0 V at the rated current of 10 A. In this case, we want the filter capacitor,  $C_{CS}$ , to be 2.7 nF. Equation 29 shows the calculation for  $C_{CS}$ .

(**Note:** Several reference designs with C  $_{CS}$  = 10 nF have been defined with good results during lab investigations.)

$$C_{CS} = \frac{25 \ \mu s}{R_{CS1}} \tag{29}$$

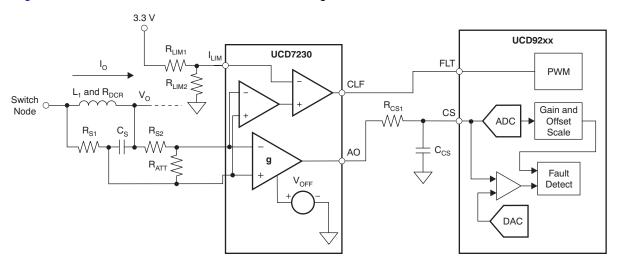

#### 2.9 Calculation of UCD7230A ILIM Voltage

Figure 2-13 illustrates a circuit that is ideal for setting a CLF/FLT threshold for the UCD7230A.

Figure 2-13. Setting UCD7230A CLF/FLT Threshold

The internal overcurrent threshold on the inductor current is set by the ILIM pin. The voltage on this pin is set to 10 times the voltage representing the maximum current at the POS and NEG pins. Therefore, the voltage on the ILIM pin should be equivalent to that shown by Equation 30.

$$V_{ILIM} = 10 \frac{R_{ATT}}{R_{S1} + R_{S2} + R_{ATT}} R_{DCR} I_{MAX}$$

(30)

There is also an internal divider on the ILIM pin; the equivalent circuit for this internal divider is a 0.5-V source with a 42-k $\Omega$  resistor. If we define this internal resistance as R<sub>LIM3</sub> and set R<sub>LIM1</sub> = 24.9 k $\Omega$ , we can then determine the desired value for R<sub>LIM2</sub> using Equation 31.

$$R_{LIM2} = \frac{V_{ILIM}}{\frac{3.3}{R_{LIM1}} + \frac{0.5}{R_{LIM3}} - V_{ILIM} \left[ \frac{1}{R_{LIM1}} + \frac{1}{R_{LIM3}} \right]}$$

$$= 15.6k \frac{V_{ILIM}}{2.26 - V_{ILIM}}$$

(31)

Leaving R<sub>LIM2</sub> open sets the internal threshold at 0.100 V, and in this case, Equation 32 is valid.

$$I_{MAX} = \frac{100m}{R_{DCR}} \left[ \frac{R_{S1} + R_{S2}}{R_{ATT}} + 1 \right]$$

(32)

#### 2.10 Calculation of UCD7231 ILIM Voltage

For the UCD7231, the overcurrent threshold that generates an active signal on the CLF pin is compared directly to the current sense amplifier output voltage. Equation 33 shows this relationship.

$$V_{ILIM} = \frac{R_{ATT}}{R_{S1} + R_{S2} + R_{ATT}} R_{DCR} I_{MAX} + 0.5$$

(33)

Normally, the ILIM voltage is set by a resistor divider connected between 3.3 V and ground. The Fusion GUI recommends a 24.9-k $\Omega$  resistor for R<sub>LIM1</sub>; therefore, R<sub>LIM2</sub> is calculated as shown in Equation 34.

$$R_{LIM2} = R_{LIM1} \frac{V_{ILIM}}{1 - V_{ILIM}} = 24.9k \frac{V_{ILIM}}{1 - V_{ILIM}}$$

(34)

### Voltage Regulation

This chapter gives a detailed description of how the UCD92xx controller regulates the supply voltage using digital feedback control. As noted in Chapter 2, the formula and equations presented here are incorporated into the Fusion Digital Power Designer software and in most cases, allowing the design tool to recommend the loop compensation gives the best results. However, the recommended compensation is only as good as the information provided to the Fusion GUI, which can be uncertain as a result of board layout issues or individual component tolerances. Therefore, this information is included to help users understand what is going on when the regulation behavior is different from what is expected.

#### **Topic Page** 3.1 3.2 Modeling Delay in the Control Loop ......43 3.3 3.4 Phase Loss as a Result of On-Time and Multiple Power Stages .......45 3.5 Quantization Effects 46 3.6 3.7 How to Tweak the Compensation ......49 3.8 3.9

Loop Compensation www.ti.com

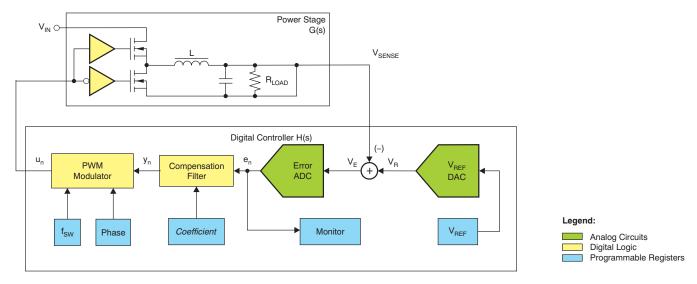

#### 3.1 Loop Compensation

The UCD9xxx family of point-of-load (POL) voltage regulation controllers use digital signal processing techniques to perform voltage regulation. This architecture enables programmable control of the regulation setpoint voltage, the switching frequency, the phase of the switching action for each power stage controlled, and the loop compensation. It also enables digital monitoring of the regulation control loop. Ultimately, through the use of a multiplexed, 12-bit ADC (not shown in Figure 3-1), voltage, current, and temperature fault limits can be digitally programmed and detected.

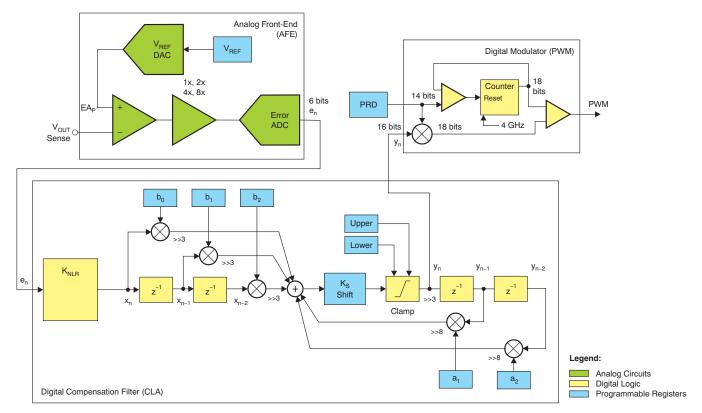

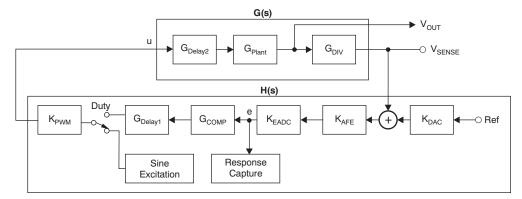

Figure 3-1. UCD92xx Fusion Peripheral Block Diagram

#### 3.1.1 Total Loop Gain

In Figure 3-1, we can define the transfer function for each block in this manner:

• Power Stage: The transfer function for the power stage is given in Equation 35:

$$G(s) = dV_{IN} \Biggl[ \frac{R_L}{R_S + R_L} \Biggr] \frac{R_C C s + 1}{\frac{R_C + R_L}{R_S + R_L} L C s^2 + \Biggl[ \frac{L}{R_S + R_L} + \frac{R_C R_L + R_S R_L + R_C R_S}{R_S + R_L} C \Biggr] s + 1}$$

where

- · d is the PWM signal duty cycle;

- R<sub>s</sub> is the series resistance of the MOSFETs and the inductor;

- R<sub>c</sub> is the effective series resistance of the output capacitor;

- R<sub>i</sub> is the load resistance;

- · L is the inductance; and

- C is the output capacitance.

Note that this transfer function has a second-order pole at approximately  $\frac{1}{\sqrt{LC}}$ , with a no-load Q of  $\frac{1}{R_s+R_c}\sqrt{\frac{L}{C}}$  and a zero at  $\frac{1}{R_cC}$ . The units of the power stage gain are volts/cycle.

(35)

- Error Amplifier Gain: The analog front end circuits of the UCD92xx have a programmable gain that can be set to 1x, 2x, 4x, or 8x.

- Error ADC: The ADC that samples the error between the setpoint reference and the voltage to be regulated has a gain of 125 LSB/V, or a resolution of 8 mV/LSB.

- Compensation Filter: See Section 3.2.

- Pulse Width Modulator: The pulse width modulator has an input-to-output gain of 2<sup>-15</sup> cycles/LSB.

- Computational Delay: There is a delay between sampling the error voltage and calculating the latest

control effort. This delay (T<sub>DELAY</sub>) causes a phase lag in the open-loop transfer function that is

expressed as a phase rotation, e<sup>-sTdelay</sup>.

The total open-loop gain that is displayed as the system Bode plot is calculated in Equation 36:

$$T(s) = G_{PLANT}(s) \cdot K_{AFE} \cdot K_{ADC} \cdot H(s) \cdot K_{PWM} \cdot G_{DELAY}(s)$$

(36)

From this equation, then, we can estimate the closed-loop bandwidth, phase margin, and gain margin by noting where the magnitude of T(s) crosses 0 dB and where the phase of T(s) crosses –180 degrees.

#### 3.2 Implementation of the Compensating Filter H(s)

The UCD9224/46/48 device uses a direct form digital filter to determine the compensated error signal. This filter has the form shown in Equation 38. To determine the numerator coefficients [b0, b1, and b2] and the denominator coefficients [a0, a1, and a2], it is most convenient to start with the required second-order, continuous-time polynomial in s. Given the requirement for Type 3 compensation (that is, a compensating filter with a two-zero, two-pole transfer function), we start with the polynomial transfer function in s shown in Equation 37.

$$H(s) = \frac{\left[\frac{s}{\omega_{z1}} + 1\right] \left[\frac{s}{\omega_{z2}} + 1\right]}{\left[\frac{s}{\omega_{0}}\right] \left[\frac{s}{\omega_{p2}} + 1\right]} = K_{DC} \frac{\frac{s^{2}}{\omega_{z}^{2}} + \frac{s}{\omega_{z}Q_{z}} + 1}{\frac{s^{2}}{\omega_{p2}} + s + 0}$$

(37)

By using feedback loop analysis (discussed in the *Autotune* section), we can determine the desired values of the compensator gain  $K_{DC}$ ; the center frequency of the zeroes  $F_z$ , the spreading of the zeroes  $Q_z$ , and the second-pole frequency  $F_{p2}$ . These constants define the compensator transfer function. Then, we can find an equivalent discrete-time, two-zero, two-pole compensating filter of the form shown by applying the bilinear transformation to Equation 37 and then equating the resulting terms to the coefficients in Equation 38.

$$H(z) = \frac{y(z)}{x(z)} = \frac{b_0 z^2 + b_1 z + b_2}{a_0 z^2 + a_1 z + a_2}$$

(38)

To do this algebraic process, we substitute the approximation given in Equation 39 for *s* into Equation 37. Then, collect the terms.

$$s = 2F_S \frac{z - 1}{z + 1} \tag{39}$$

The resulting discrete-time filter coefficients  $[b_0 \ b_1 \ b_2]$  and  $[a_0 \ a_1 \ a_2]$  are shown in Equation 40 and Equation 41.

$$\begin{bmatrix} b_0 \\ b_1 \\ b_2 \end{bmatrix} = \frac{K_{DC}}{2\pi} \begin{bmatrix} 1 & 1 & 1 \\ -2 & 0 & 2 \\ 1 & -1 & 1 \end{bmatrix} \bullet \begin{bmatrix} \left(\frac{F_s}{F_z^2}\right) \\ \left(\frac{\pi}{F_z Q}\right) \\ \left(\frac{\pi^2}{F_s}\right) \end{bmatrix} \bullet \frac{F_{P2}}{F_s + \pi F_{P2}} \tag{40}$$

To construct the compensation filter from Equation 38, we multiple the denominator by both sides of the equation, multiply through by  $z^{-2}$ , then replace ( $x \cdot z^{-1}$ ) with  $x_{n-1}$  and ( $x \cdot z^{-2}$ ) with  $x_{n-2}$ . We do likewise with the y expressions. This process results in Equation 42.

$$y_n = b_0 x_n + b_1 x_{n-1} + b_2 x_{n-2} - a_1 y_{n-1} + a_2 y_{n-2}$$

(42)

Finally, to reduce the bit length of the discrete filter coefficients, a binary gain (left shift) is applied to the filter, as shown in Equation 43:

$$y_{n} = 2^{Kscale}(b_{0}X_{n} + b_{1}X_{n-1} + b_{2}X_{n-2} - a_{1}y_{n-1} + a_{2}y_{n-2})$$

(43)

This result is the filter that is implemented in the UCD9224/46/48; the filter is shown in Figure 3-2.

#### 3.2.1 Compensating Filter Architecture

Figure 3-2 illustrates the compensating filter architecture.

Figure 3-2, UCD92xx Fusion Peripheral Block Diagram: Compensating Filter Overview

There are three major segments of the voltage regulation signal path in the UCD92xx device:

- 1. The analog front-end (AFE) that converts the error voltage to a discrete-time sequence;

- 2. The digital compensation filter; and

- 3. The digital pulse width modulator (dPWM).

The AFE subtracts the sensed regulated voltage from a programmed reference voltage using a switched capacitor difference amplifier. The reference voltage is set using a 10-bit, 0-V to 1.6-V DAC. The DAC is written to by the ARM7 processor core. (In fact, writing to the DAC register is the primary method by which the firmware in the ARM core controls the voltage regulation process.) The output of the AFE is a 6-bit value. This 6-bit error signal is applied to a nonlinear gain block, with a 9-bit output value that is fed into the digital compensation filter.

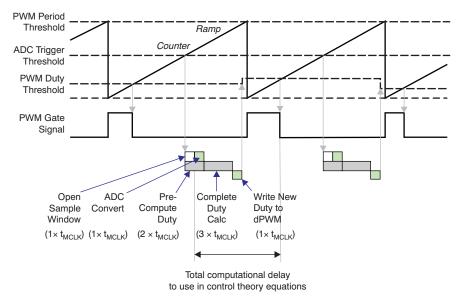

The compensated error signal out of the digital filter is applied to the pulse width modulator. At the PWM, it is multiplied by a value that represents the switching period (the PRD register). The result is a value that is compared to the PWM ramp counter. The modulator runs on a 250-MHz clock; there are 16 phases of the output, giving the modulator an effective 4-GHz clock rate. This configuration sets the pulse width resolution at 250 ps.

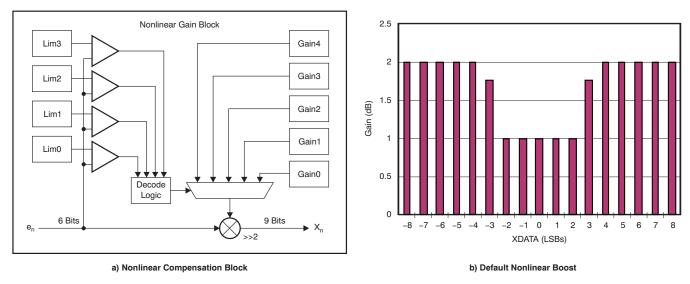

A nonlinear gain block (NLR) was added to the design of the UCD92xx device. This block sits between the AFE and the digital compensation filter. It boosts the gain when the error signal is large, and reduces the gain when the error signal is near zero. In practice, the primary benefit of the NLR circuit is to reduce the gain when the load is quiescent, thereby reducing jitter as a result of quantization effects in the signal path.

Figure 3-3 shows the NLR block and default boost.

Figure 3-3. Nonlinear Compensation Block and Default Boost Characteristic

#### 3.2.2 Fixed-Point Math

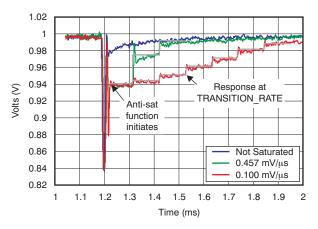

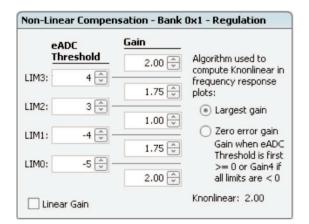

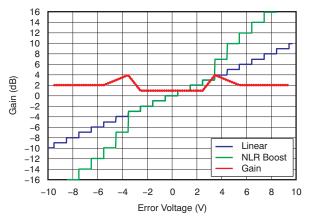

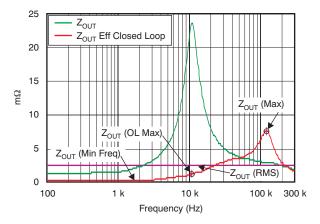

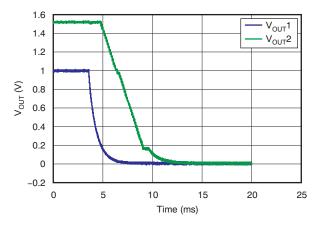

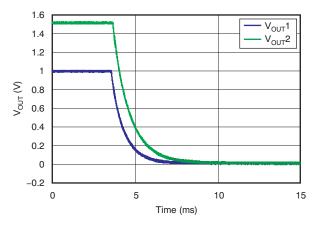

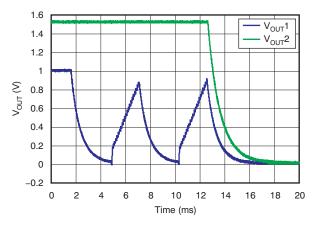

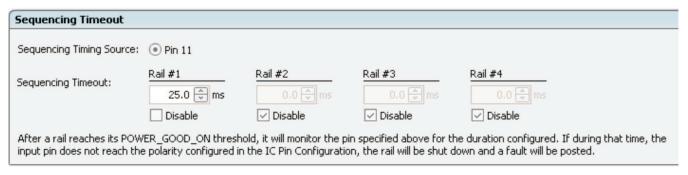

Each regulated voltage rail has a dedicated compensation filter implemented in digital logic, separate from the core processor that manages the PMBus interface. (It is not necessary for the core processor to run in order for the device to regulate the voltage.) The filer performs each multiply and summing operation in fixed-point math. The error signal is a 6-bit signal that becomes a 9-bit signal after passing through the nonlinear gain block. The filter coefficients are 12-bit integers; the result of each multiply operation is a 20-bit value; and the output that feeds the PWM modulator is a 16-bit value. All of the signals are signed integers.