# Benefiting from Step-Down Converters with an I<sup>2</sup>C Communication Interface

Dorian Brillet de Candé

#### **ABSTRACT**

This application report shows the benefits of using a step-down converter with an  $I^2C$  communication interface. Several applications benefit from controlling features and reading status information from a power management device. TI offers step-down converters with an  $I^2C$  communication interface, which focus on design flexibility while keeping a small solution size.

#### **Table of Contents**

| 1 Introduction                                                                                              | ∠              |

|-------------------------------------------------------------------------------------------------------------|----------------|

| 2 Smart Routing and Tiny IC Packages                                                                        | <mark>2</mark> |

| 3 Selectable Forced-PWM/PSM operation                                                                       |                |

| 4 Dynamic Output Voltage Adjustment During Operation                                                        |                |

| 5 Thermal Considerations                                                                                    |                |

| 6 Droop Compensation                                                                                        |                |

| 7 Step-Down Converter with an I <sup>2</sup> C Interface Selection Table                                    | 8              |

| 8 Conclusion                                                                                                |                |

| 9 References                                                                                                |                |

| 10 Revision History                                                                                         |                |

| List of Figures                                                                                             |                |

| Figure 2-1. TPS62861 Layout Connecting all Pins Without Vias                                                | 2              |

| Figure 3-1. TPS62866 Efficiency Versus Load Current with Power Save-Mode and Forced PWM Mode                |                |

| Figure 3-2. TPS62866 Output Voltage Ripple with Power-Save Mode (left) and Forced PWM Mode (right)          |                |

| Figure 4-1. The TPS62869 Powers all Rails on LPDDR5 DRAM with Dynamic Output Voltage Adjustment on the VDDQ |                |

| Rail                                                                                                        | 4              |

| Figure 4-2. 0.5 V to 0.3 V Output Transition in a 20 mV/us Slew Rate, IOUT=100mA Without FPWM During Change |                |

| Enabled (left) and With (right)                                                                             | 5              |

| Figure 5-1. Two TPS62873-Q1 Devices in a Stacked Configuration                                              |                |

| Figure 6-1. TPS62876-Q1 Load Transient Response with Droop Compensation Disabled (left) and Enabled (right) | 7              |

| List of Tables                                                                                              |                |

| Table 4-1. VDDQ Ramp Rates for DVFSQ transition                                                             | 5              |

| Table 6-1. Load Transient Response for a 20 A/us Load Change, Peak to Peak Value                            |                |

| Table 7-1. DC/DC Converters Suggestion Using an I <sup>2</sup> C Communication Interface                    |                |

|                                                                                                             |                |

#### **Trademarks**

All trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

When it comes to power management, many systems benefit from step-down converters with already built-in features. However, adding more features requires more pins to implement them. Offering more features can be at odds with the need to increase the power density. To achieve both, some buck converters use an I<sup>2</sup>C interface, which enables digital communication to control such features, read status information or adjust the buck converter control modes depending on the system operating conditions .

# 2 Smart Routing and Tiny IC Packages

A proper pinout assignment is critical to make sure a simple component placement and a small design size. It is also important to provide an easy access to all available pins on the package of the device. To integrate an I<sup>2</sup>C communication interface, two additional logic pins, SDA and SCL, need to be added. To allow easy routing without expensive microvias, the I<sup>2</sup>C pins should be added on the outside of the device.

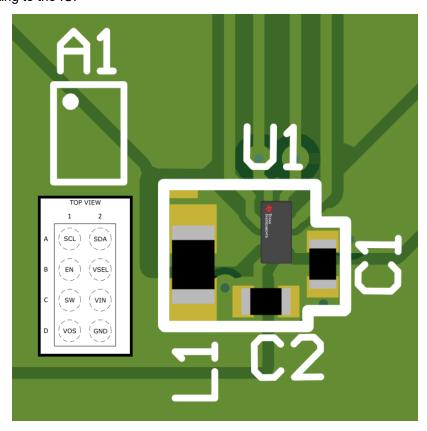

The TPS62861 combines a flexible design and a small design size. The TPS62861 is housed in a 8-pin tiny 0.7x1.4mm wafer chip scale package (WCSP). Figure 2-1 shows the PCB layout of the TPS62861 which is optimized for the design size of 12 mm² and has all pins accessible from the outside of the package. No vias are required for connecting to the IC.

Figure 2-1. TPS62861 Layout Connecting all Pins Without Vias

Layout Matters: Solving Pinout Assignment Issues for DC/DC Converters in WCSP Packages is a technical article describing how a good pinout assignment can help for a small and simple implementation of a DC/DC converter with an I<sup>2</sup>C communication interface.

# 3 Selectable Forced-PWM/PSM operation

Battery-powered applications require step-down converters to provide high efficiency numbers at light loads to save power and ensure a long battery run time. Therefore, many step-down converters implement a Power Save Mode (PSM) operation which automatically reduces the switching frequency when in a light load condition. However, this switching frequency reduction increases the output voltage ripple. The higher output voltage ripple magnitude as well as the lower switching frequency may not be acceptable for some sensitive loads.

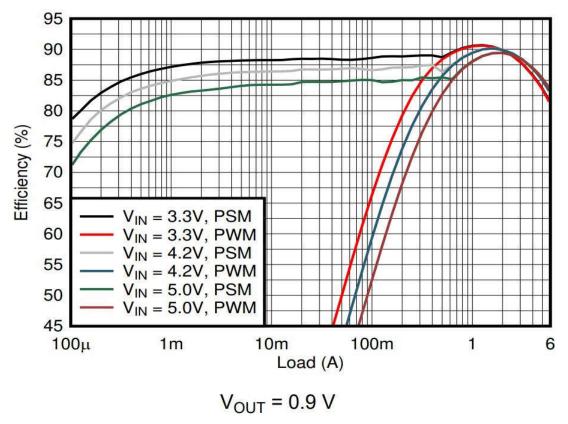

An *Enable FPWM Mode* bit is available in the Control Register of TPS62866. Enabling this bit forces PWM mode operation to achieve smallest output voltage ripple. Figure 3-1 shows the TPS62866 efficiency curves difference, while Figure 3-1 shows the output-ripple difference. The  $4\mu A I_Q$  of TPS62866 enables high light-load efficiency for many portable applications.

Figure 3-1. TPS62866 Efficiency Versus Load Current with Power Save-Mode and Forced PWM Mode

Figure 3-2. TPS62866 Output Voltage Ripple with Power-Save Mode (left) and Forced PWM Mode (right)

Operating Conditions: VIN=3.3V, Vout=0.9V and lout= 100 mA

# 4 Dynamic Output Voltage Adjustment During Operation

The  $I^2C$  interface allows adjustment of the output voltage during operation. One or more  $I^2C$  registers usually sets the output voltage, and these can be directly re-written during operation. Some devices also contain VID or VSEL pins, which switch between two or more output voltages. In this case, the registers can still be re-written as needed during operation, or can be written once to specific operating voltages.

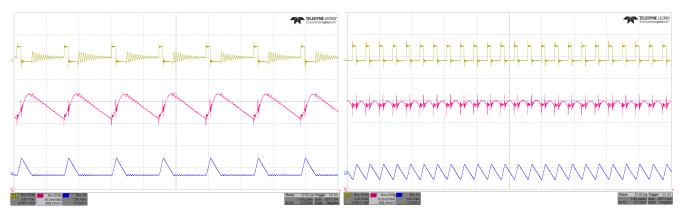

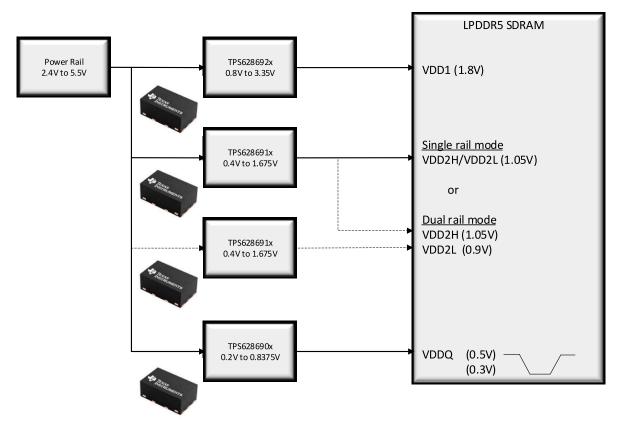

For example, LPDDR5 DRAMs VDDQ rail can be set to either 0.5 V or 0.3 V. This voltage change is accomplished by either rewriting the I²C register to change the output voltage or using the VID pin to change to a different I²C register with its different output voltage. LPDDR5 DRAMs provide additional power-savings compared to previous generations. In an idle condition when the LPDDR5 DRAM is in a low-power operating state, the memory controller can reduce both the supply voltage and frequency of operation using the dynamic voltage and frequency scaling VDDQ (DVFSQ) feature of the LPDDR5 DRAM.

Figure 4-1 shows a typical block diagram for powering LPDDR5 memory, with dynamic output voltage adjustment on the VDDQ rail.

Figure 4-1. The TPS62869 Powers all Rails on LPDDR5 DRAM with Dynamic Output Voltage Adjustment on the VDDQ Rail

The system design determines if dual rail mode will be used for additional power savings. Unlike the VDDQ rail – which can be changed dynamically – VDD2H/L are always operated at fixed voltages, regardless of whether single rail or dual rail mode is used.

TPS62869 provides different voltage ramp speeds to enable system engineers to select the right conditions for a DVFSQ low-to-high transition. For instance, if a fast response is required when VDDQ is returned to a 0.5 V nominal level for high-speed operations, TPS62869 can adapt its Voltage Ramp Speed from 1mV/us up to 20mV/us.

Table 4-1 shows the maximum VDDQ Ramp Rates for a DVFSQ transition.

www.ti.com Thermal Considerations

Table 4-1. VDDQ Ramp Rates for DVFSQ transition

| VDDQ Slew Rate                    | Max Value | Units |

|-----------------------------------|-----------|-------|

| Fast response mode (high current) | 20        | mV/us |

| Normal operation<br>(default)     | 4,8       | mV/us |

Furthermore, operating parameters for example, *Forced PWM mode during output voltage change* can be enabled to address strict timing requirements during the Low-to-High transition of VDDQ. This provides a fast transition in a lower operating state and can prevent the slow discharge of the output stage to limit the voltage ramp speed in a low load condition.

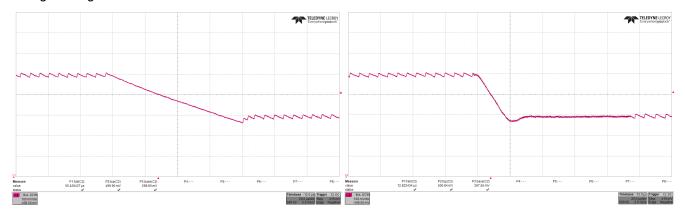

Figure 4-2 shows an example of a 0.5 V to 0.3 V transition with and without Forced PWM mode during output voltage change at a 100 mA load condition.

Figure 4-2. 0.5 V to 0.3 V Output Transition in a 20 mV/us Slew Rate, IOUT=100mA Without FPWM During Change Enabled (left) and With (right)

#### 5 Thermal Considerations

In some space-constrained applications, thermal performance of power management devices comes under close scrutiny. Controlling, on-the-fly, the output voltage and operating parameters to influence the heat dissipation is a highly valuable feature. Thermal adjustments can be achieved by adapting the output voltage as well as the load current during operation. Placing the memory controller in a lower power operating state enables significant power savings and subsequently reduces the system temperature .

A further benefit of thermal adjustments is to determine thermal margin in a design. Some I<sup>2</sup>C devices such as TPS62873-Q1 contain a thermal warning bit, which acts as an upper limit to take preventive measures and keep away from excessive heating or even thermal shutdown. As long as the junction temperature of the device is below the thermal warning threshold, the thermal warning bit is Low in the status register. If the junction temperature exceeds that temperature, the thermal warning bit goes High.

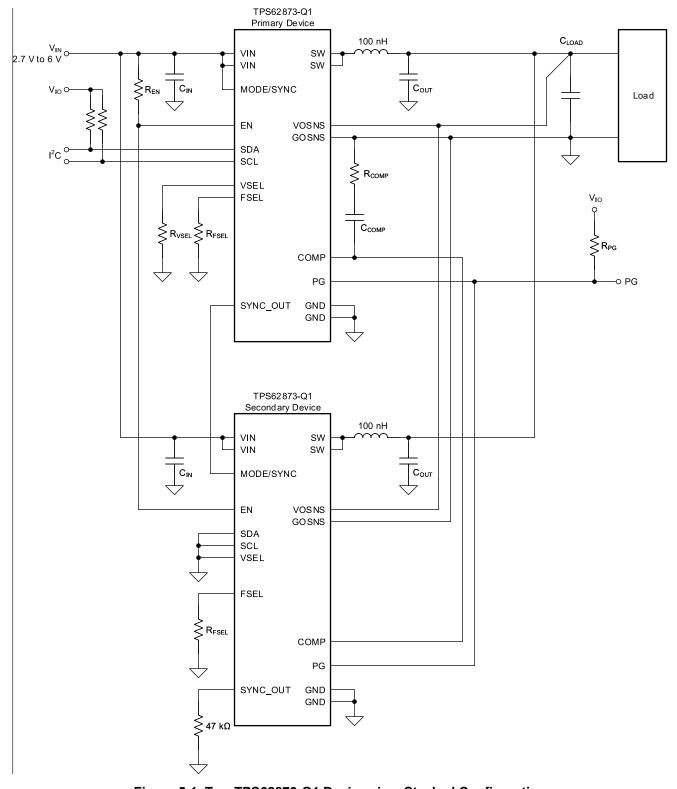

Furthermore, TPS62873-Q1 can operate in stacked mode to spread the power dissipation across multiple spots on the PCB and minimize a single device junction temperature. Refer to Operating TPS6287X-Q1 Devices in a Stacked Configuration to parallel TPS6287x-Q1 to supply the same load.

In a stacked configuration the output current capability is increased. A two TPS62873-Q1 stack is shown in Figure 5-1, this configuration can deliver higher current up to 30 A.

Thermal Considerations www.ti.com

Figure 5-1. Two TPS62873-Q1 Devices in a Stacked Configuration

www.ti.com Droop Compensation

## **6 Droop Compensation**

With increasing needs to compute data fast in a reliable way, DC-DC converters continue to see lower output voltages and even stricter core rail supply AC and DC regulation specifications. To be able to provide significant amount of current in a very short time window, features like droop compensation helps to reduce over shoot and undershoot of the core voltage during load variation.

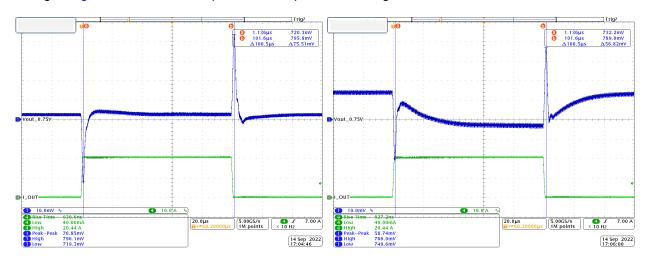

Some power rail like SoC and FPGA core rails have strict load requirement. By enabling the droop compensation setting via I<sup>2</sup>C, TPS62876-Q1/TPS6287B25 helps to increase the voltage margin on a supply rail, inherently allowing a reduction of the output capacitance needed to achieve a defined load transient peak to peak target. Figure 6-1 shows a comparison for a quick load change.

Figure 6-1. TPS62876-Q1 Load Transient Response with Droop Compensation Disabled (left) and Enabled (right)

Table 6-1. Load Transient Response for a 20 A/us Load Change, Peak to Peak Value

| Droop disabled | Droop enabled |

|----------------|---------------|

| 76.85 mV       | 58.74 mV      |

About 25% improvement can be observed on that specific case. By nature of the droop compensation feature implementation, best-case to use this feature is for a fast load change from 10 to 90% of output current rating.

# 7 Step-Down Converter with an I<sup>2</sup>C Interface Selection Table

Table 7-1 highlights the latest low input voltage (< 7 V) DC/DC converters with an I<sup>2</sup>C communication interface. The devices offer different operating modes and features over a wide range of output current.

Table 7-1. DC/DC Converters Suggestion Using an I<sup>2</sup>C Communication Interface

| OPN                                                                                                          | Current<br>Rating               | Switching<br>Frequency<br>(typical)                           | Features                                                                                                                                       | I <sup>2</sup> C Addressable Parameters                                                                                                                                                                                                                                                               | IC Size<br>x/y/z                                                                |

|--------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| TPS62860<br>TPS62861                                                                                         | 0.6A<br>1A                      | 1.5 MHz<br>4 MHz                                              | 0.35-mm pitch WCSP<br>package,<br>VSEL pin Options,                                                                                            | Output discharge,<br>Software Enable,<br>PSM/FPWM Mode,<br>Voltage Ramp Speeds                                                                                                                                                                                                                        | 0.7x1.4 mm<br>0.4 mm height                                                     |

| TPS62864<br>TPS62866                                                                                         | 4A<br>6A                        | 2.4MHz                                                        | 0.35-mm pitch WCSP<br>package,<br>Selectable<br>start-up voltage,<br>VID pin,<br>/PG pin,                                                      | Output discharge,<br>Software Enable,<br>PSM/FPWM Mode,<br>HICCUP Short-Circuit Protection,<br>Voltage Ramp Speeds,<br>Enable FPWM Mode during Output<br>Voltage Change,<br>Thermal Warning                                                                                                           | 1.05x1.78 mm<br>0.5 mm height                                                   |

| TPS62868<br>TPS62869                                                                                         | 4A<br>6A                        | 2.4MHz                                                        | QFN package,<br>Selectable<br>start-up voltage,<br>Output voltage range<br>options,<br>VID pin,<br>PG pin,                                     | Output discharge,<br>Software Enable,<br>PSM/FPWM Mode,<br>HICCUP Short-Circuit Protection,<br>Voltage Ramp Speeds,<br>Enable FPWM Mode during Output<br>Voltage Change,<br>Thermal Warning                                                                                                           | 1.5x2.5 mm<br>1.0 mm height                                                     |

| TPS62870-Q1<br>/TPS62870<br>TPS62871-Q1<br>/TPS62871<br>TPS62872-Q1<br>/TPS62872<br>TPS62873-Q1<br>/TPS62873 | 6A<br>9A<br>12A<br>15A          | 1.5MHz/<br>2.25MHz/<br>2.5MHz/3MHz<br>Resistor-<br>selectable | QFN package, Differential remote sensing, Stacked operation, Selectable start-up voltage, PG pin, External compensation, Clock synchronization | Output discharge, Software Enable, PSM/FPWM Mode, HICCUP Short-Circuit Protection, Voltage Ramp Speeds, Spread spectrum Clocking, Output voltage range options, Soft-Start ramp time, Enable FPWM Mode during Output Voltage Change, Thermal Warning, Power-bad Over/Undervoltage                     | 2.55x 3.55 mm<br>1.0 mm height                                                  |

| TPSM8287A06<br>TPSM8287A10<br>TPSM8287A12<br>TPSM8287A15                                                     | 6A<br>10A<br>12A<br>15A         | 1.5MHz/<br>2.25MHz                                            | QFN package, Differential remote sensing, Stacked operation, Selectable start-up voltage, PG pin, External compensation, Clock synchronization | Output discharge, Software Enable, PSM/FPWM Mode, HICCUP Short-Circuit Protection, Voltage Ramp Speeds, Spread spectrum Clocking, Output voltage range options, Soft-Start ramp time, Enable FPWM Mode during Output Voltage Change, Thermal Warning, Power-bad Over/Undervoltage                     | 4.5 x 6.8 mm<br>1.8 mm height<br>(6A and 12A)<br>4.0 mm height<br>(10A and 15A) |

| TPS6287B10 TPS62874-Q1/ TPS6287B15 TPS62875-Q1/ TPS6287B20 TPS62876-Q1/ TPS6287B25 TPS62877-Q1               | 10A<br>15A<br>20A<br>25A<br>30A | 1.5MHz/<br>2.25MHz/<br>2.5MHz/3MHz<br>Resistor-<br>selectable | QFN package, Differential remote sensing, Stacked operation, Selectable start-up voltage, PG pin, External compensation, Clock synchronization | Output discharge, Software Enable, PSM/FPWM Mode, HICCUP Short-Circuit Protection, Voltage Ramp Speeds, Spread spectrum Clocking, Output voltage range options, Soft-Start ramp time, Enable FPWM Mode during Output Voltage Change, Thermal Warning, Power-bad Over/Undervoltage, Droop Compensation | 4.05x 3.05 mm<br>0.65 mm height                                                 |

www.ti.com Conclusion

#### 8 Conclusion

TI offers high performance, simple to layout step-down converters with an I<sup>2</sup>C interface, easing trade-off considerations between design flexibility and higher power density. Having more integrated features, through the I<sup>2</sup>C interface, reduces the number of external components, lowering the system BOM cost and pin count. A more flexible design can address more rails within a system and therefore lower development efforts by providing a greater pricing advantage due to the economies of scale.

#### 9 References

- Texas Instruments, Methods of Output-Voltage Adjustment for DC/DC Converters analog design journal.

- Texas Instruments, Enabling Higher Data Rates for Optical Modules With Small and Efficient Power and Data-Converter Solutions technical white paper.

- Texas Instruments, Thermal Performance Optimization of High Power Density Buck Converters application note

- Texas Instruments, Layout Matters: Solving Pinout Assignment Issues for DC/DC Converters in WCSP Packages.

- Texas Instruments, Adjusting the Output Voltage of a Fixed Output Voltage DC-DC Converter application note.

- Texas Instruments, Operating TPS6287X-Q1 Devices in a Stacked Configuration application note.

# 10 Revision History

Revision History

| Changes from Revision A (May 2021) to Revision B (November 2023)                                                                                                                                                       | Page |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| <ul> <li>Added Droop Compensation topic</li> <li>Updated DC/DC Converters Suggestion Using an I<sup>2</sup>C Communication Interface table</li> </ul>                                                                  |      |  |  |

| Opdated DC/DC Converters Suggestion Using an I-C Communication Interface table      Added additional references                                                                                                        |      |  |  |

| Changes from Revision * (May 2021) to Revision A (April 2022)                                                                                                                                                          | Page |  |  |

| <ul> <li>Updated the numbering format for tables, figures, and cross-references throughout the document.</li> <li>Updated DC/DC Converters Suggestion Using an I<sup>2</sup>C Communication Interface table</li> </ul> |      |  |  |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated