# LVDS Application and Data Handbook

# High-Performance Linear Products Technical Staff

Literature Number: SLLD009 November 2002

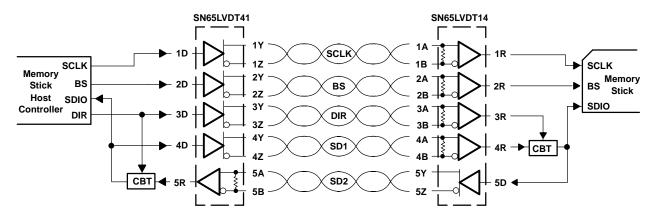

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

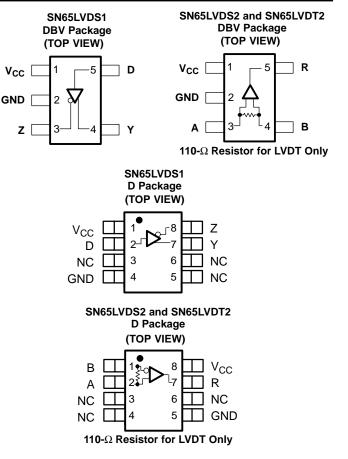

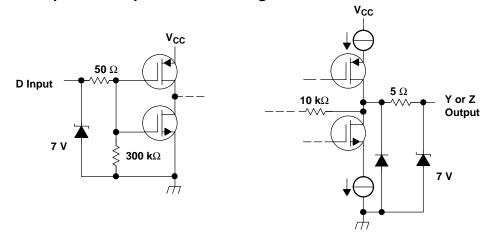

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2002, Texas Instruments Incorporated

# **Contents**

| Chapter 1 Data Transmission Basics                                  | 1–1 |

|---------------------------------------------------------------------|-----|

| Transmission Lines and Characteristics                              | 1–2 |

| Single-Ended vs Differential                                        | 1–4 |

| Point-to-Point, Multidrop, and Multipoint Buses                     | 1–6 |

| Benefits of Standardization                                         | 1–7 |

| 644 vs 644a vs LVDM vs M-LVDS                                       | 1–8 |

| LVDS/M-LVDS Summary                                                 | 1–9 |

| Chapter 2 LVDS and M-LVDS Line Circuit Characteristics and Features | 2–1 |

| Driver Output Voltage                                               |     |

| Differential Input Voltage Threshold                                |     |

| Common-Mode Voltage Range                                           |     |

| Signaling Rate                                                      |     |

| Power Consumption                                                   |     |

| Supply Voltage                                                      |     |

| Reliability                                                         |     |

| Integrated Terminations                                             |     |

| Fault Tolerance and Failsafe Receivers                              |     |

| Live Insertion (Hot Plugging)                                       |     |

| Chapter 3 Application Examples                                      | 2 1 |

|                                                                     |     |

| Receiving Single-Ended Logic Levels                                 |     |

| Receiving Other Differential Signals                                |     |

| Adjusting LVDS Output Levels                                        |     |

| Chapter 4 Product Selection                                         | 4–1 |

| Cross-Point Switches                                                | 4–1 |

| Serializers/Deserializers                                           | 4–2 |

| Line Driver and Receivers                                           | 4–3 |

| Line Transceivers                                                   |     |

| Line Receivers                                                      | 4–4 |

| Line Drivers                                                        |     |

| Repeaters                                                           |     |

| Cross Reference                                                     | 4–7 |

| Chapter 5 Product Specifications                                    | 5–1 |

| General Information                                                 |     |

| Data Sheets                                                         |     |

| Chapter 6 Design Guidelines and Tools                               | 6_1 |

| Common Problems                                                     |     |

| Printed-Circuit Board Guidelines                                    |     |

|                                                                     |     |

| Powering LVDS Devices                                               |     |

| Termination Techniques                                              |     |

| Connectors and Cables                                               |     |

| Design Tools                                                        |     |

| Other Design Help                                                   |     |

| Outer Design Neip                                                   |     |

|          | Conclusion                                                                       |      |

|----------|----------------------------------------------------------------------------------|------|

| ۰ı       | hapter 7 Testing Guidelines                                                      |      |

| <u>ا</u> | Introduction                                                                     |      |

|          | Using the Eye Pattern                                                            |      |

|          | Jitter Measurements                                                              |      |

|          | Eye Mask                                                                         |      |

|          | Bit-Error-Rate Test (BERT)                                                       |      |

|          | Electromagnetic Compatibility Testing                                            |      |

|          | Troubleshooting                                                                  |      |

|          | Common LVDS Problems                                                             |      |

|          | Signal Integrity                                                                 |      |

|          | Random Jitter                                                                    |      |

|          | Time Domain Reflectometry (TDR)                                                  |      |

|          | Conclusion                                                                       |      |

|          | References                                                                       |      |

|          | Glossary                                                                         | 7–12 |

|          | List of Illustrations                                                            |      |

|          | Figure Title                                                                     | Page |

|          | 1–1 Approximate Signaling Rate vs Transmission Distance for Various Interfaces   | •    |

|          | 1–2 Initial-Wave Circuit Model                                                   |      |

|          | 1–3 The Line-Load Boundary                                                       |      |

|          | 1–4 Reflected-Wave Example                                                       |      |

|          | 1–5 Single-Ending Interface Circuit Schematic Diagram                            |      |

|          | 1–6 Differential Interface Circuit Schematic Diagram                             |      |

|          | 1–7 A Point-to-Point Data Interchange Circuit                                    |      |

|          | 1–8 A Multidrop Data Interchange Circuit                                         |      |

|          | 1–9 A Multipoint Data Interchange Circuit                                        |      |

|          | 1–9 A Multipoint Data interchange Circuit                                        |      |

|          | ·                                                                                |      |

|          | 1–11 TIA/EIA-644-A Driver Output Test Circuit                                    |      |

|          | 1–12 Load Power Comparison of Differential Signals                               |      |

|          | 1–13 TIA/EIA Standard Voltage Ranges                                             | 1–11 |

|          | 2–1 V <sub>OD</sub> Definition                                                   | 2–1  |

|          | 2–2 Circuit Used to Measure the Driver Common-Mode Output Voltage                | 2–1  |

|          | 2-3 LVDS and M-LVDS Differential Input Voltage Thresholds                        | 2–2  |

|          | 2–4 Common-Mode Rejection Test of a Differential Line Receiver                   | 2–4  |

|          | 2–5 TIA/EIA-644-A Signal Quality Recommendations                                 | 2–6  |

|          | 2–6 MC100LVEP111 and SN65LVDS116 Power Comparison                                | 2–8  |

|          | 2–7 Differential Driver Circuit Model                                            | 2–8  |

|          | 2–8 Normalized Power vs Speed Comparison of Voltage-Mode and Current-Mode Driver |      |

|          | 2–9 Power-Up/Down Waveforms                                                      |      |

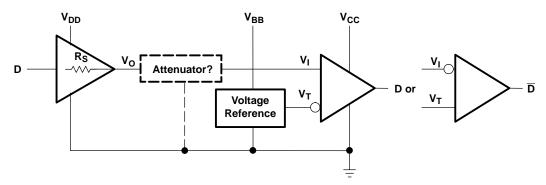

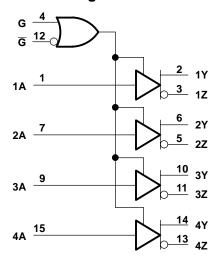

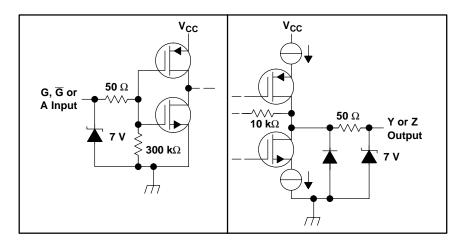

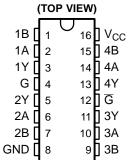

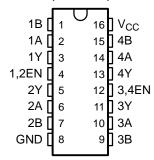

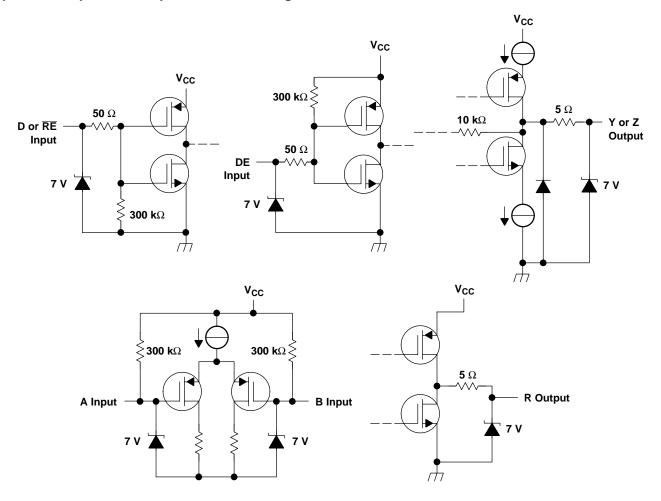

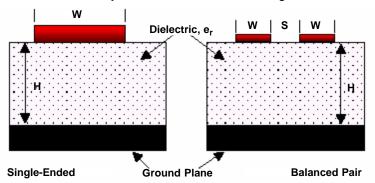

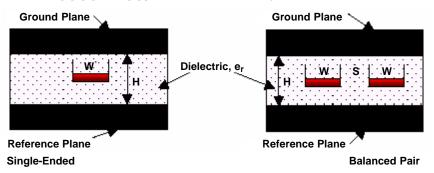

|          | 3–1 Circuit Blocks for Receiving Single-Ended Logic Signals                      |      |

|          |                                                                                  |      |

| 3–2 Simple Input Attenuator                                                      | 3–2  |

|----------------------------------------------------------------------------------|------|

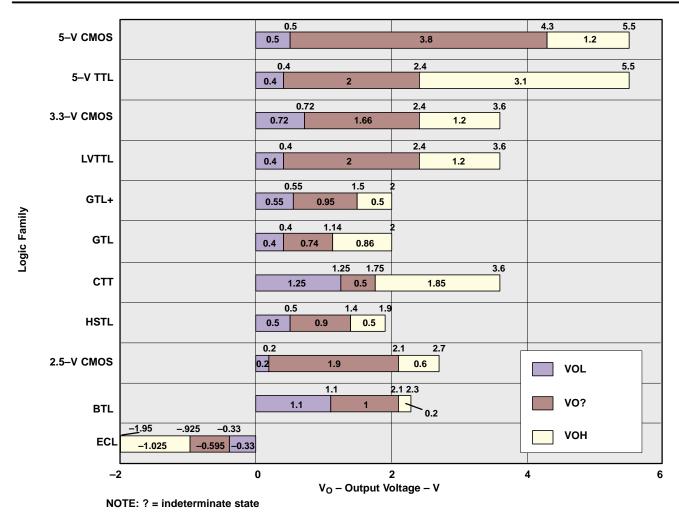

| 3–3 Single-Ended Logic Levels                                                    | 3–3  |

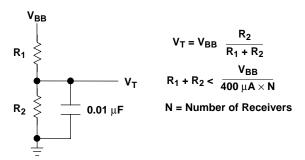

| 3–4 Voltage Divider Reference Circuit                                            | 3–4  |

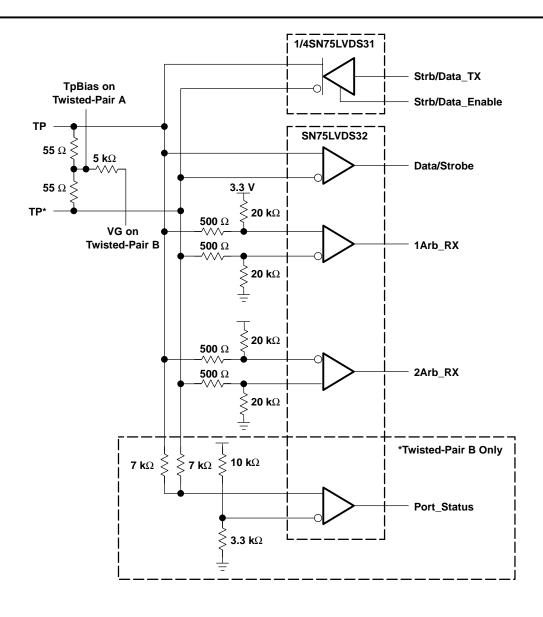

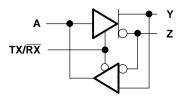

| 3–5 100-Mbps IEEE-1394 Transceiver With LVDS                                     | 3–5  |

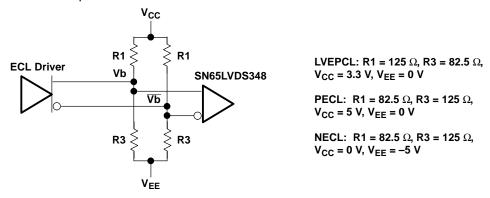

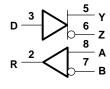

| 3–6 ECL-to-CMOS Conversion With the SN65LVDS348                                  | 3–6  |

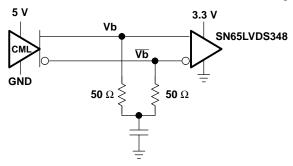

| 3–7 CML-to-CMOS Translation With the SN65LVDS348                                 | 3–6  |

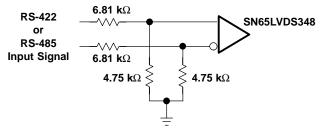

| 3–8 RS-422/485-to-CMOS Translator With the SN65LVS348                            | 3–6  |

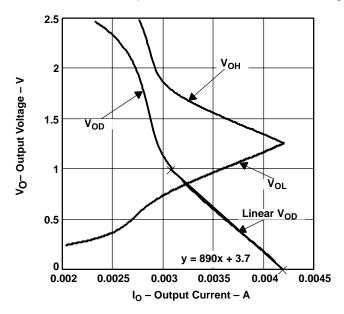

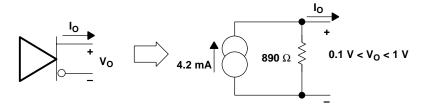

| 3–9 SN65LVDS31 Output Current vs Voltage                                         | 3–7  |

| 3-10 Equivalent Circuit of SN65LVDS31 Steady-State Differential Output           | 3–7  |

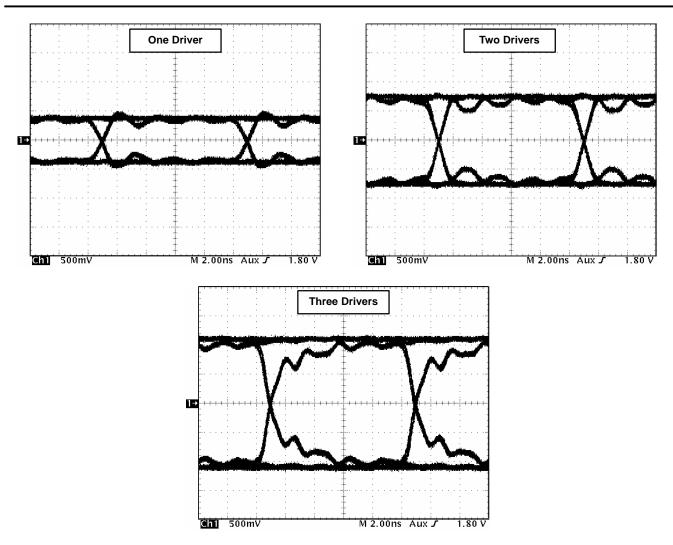

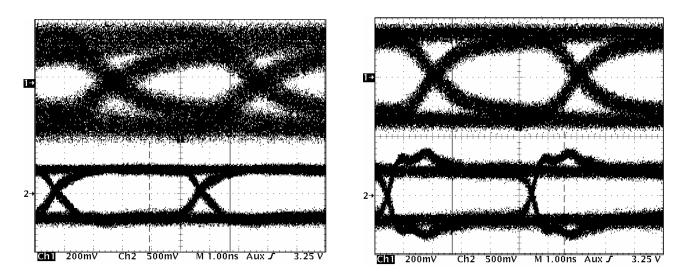

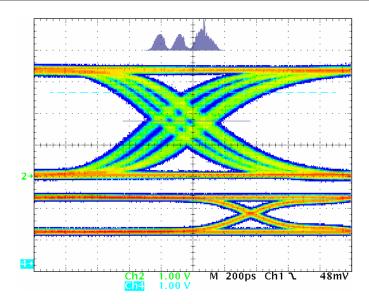

| 3–11 Eye Patterns for Multiple Drivers and 100- $\Omega$ Loads                   | 3–8  |

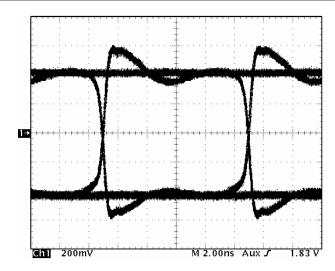

| 3–12 Eye Patterns With Four Parallel Drivers Into a 27- $\Omega$ Load            | 3–9  |

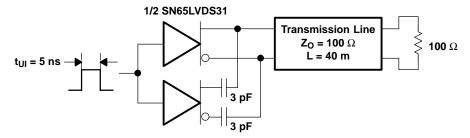

| 3–13 Precompensation Circuits With Two Drivers                                   | 3–9  |

| 3–14 Eye-Patterns With and Without Precompensation                               | 3–10 |

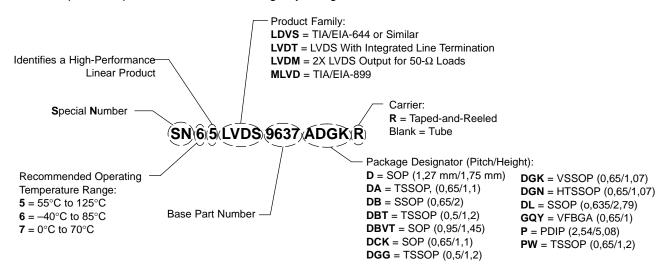

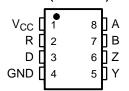

| 4–1 TI's LVDS Part Numbering Convention                                          | 4–1  |

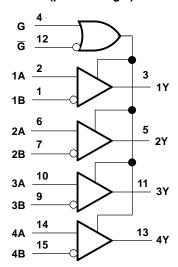

| 6–1 Microstrip Topology                                                          | 6–2  |

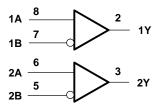

| 6–2 Stripline Topology                                                           | 6–2  |

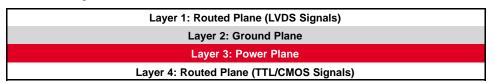

| 6–3 Four-Layer PCB Board                                                         | 6–3  |

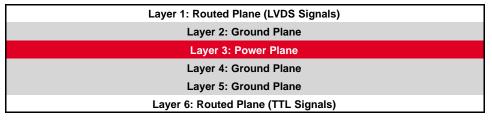

| 6–4 Six-Layer PCB Board                                                          | 6–3  |

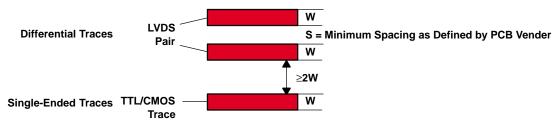

| 6–5 3-W Rule for Single-Ended and Differential Traces (Top View)                 | 6–4  |

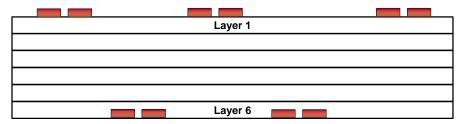

| 6–6 Staggered Trace Layout                                                       | 6–4  |

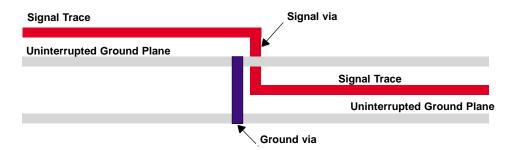

| 6–7 Ground Via Location (Side View)                                              | 6–5  |

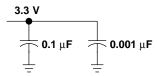

| 6-8 Recommended LVDS Bypass Capacitor Layout                                     | 6–6  |

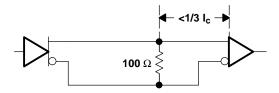

| 6–9 Point-to-Point Termination                                                   | 6–6  |

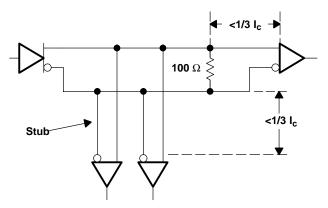

| 6-10 Multidrop Termination                                                       | 6–7  |

| 6–11 Multipoint Bus Termination                                                  | 6–7  |

| 6–12 Connector Configuration Minimizing Crosstalk                                | 6–8  |

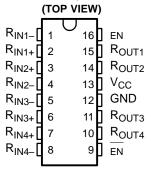

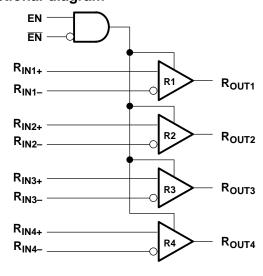

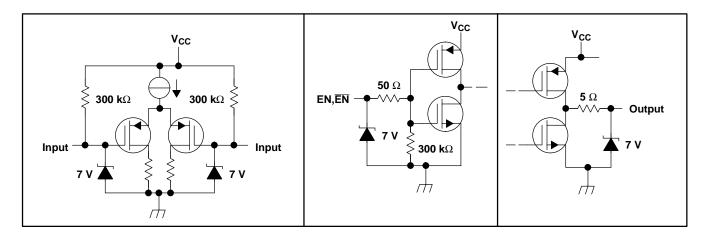

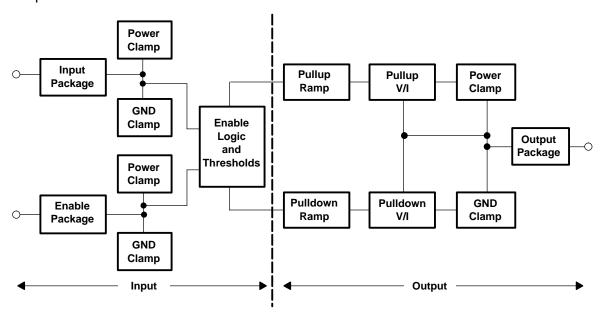

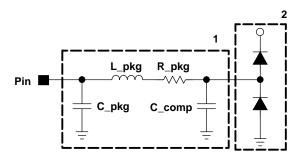

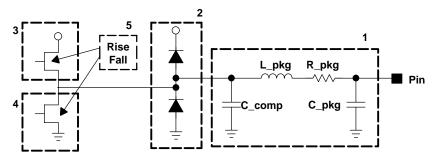

| 6–13 Input/Output Behavioral Model                                               | 6–10 |

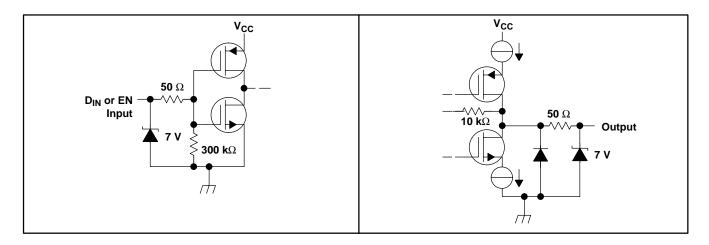

| 6–14 Input/Enable Model                                                          | 6–11 |

| 6–15 Output Model                                                                | 6–11 |

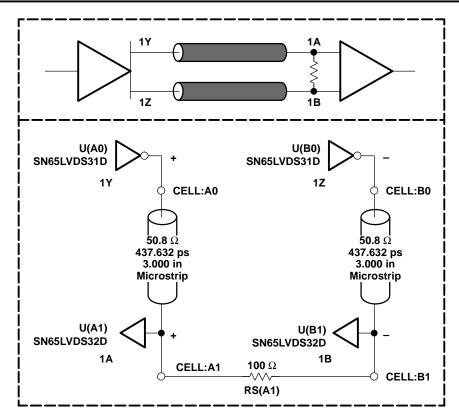

| 6-16 Schematic Drawing and Schematic Editor of LineSim                           |      |

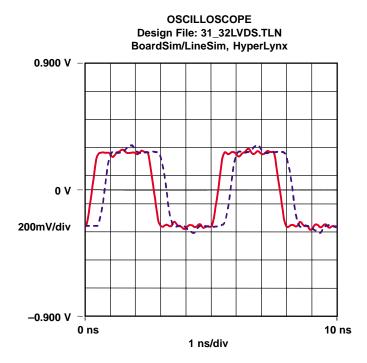

| 6–17 Differential Output Simulation With a Termination of 100 $\Omega$           | 6–13 |

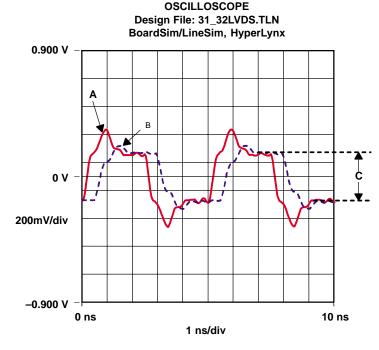

| 6–18 Differential Output Simulation With a Mismatched Termination of 60 $\Omega$ | 6–14 |

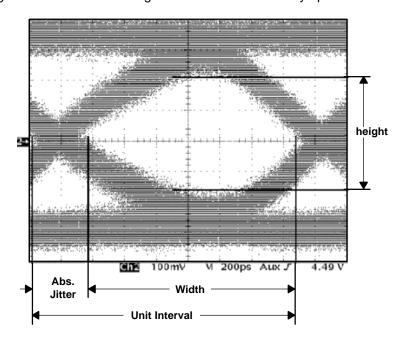

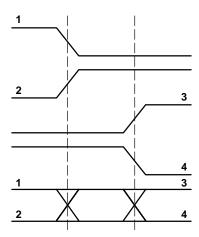

| 7–1 Typical Eye Pattern                                                          | 7–1  |

| 7–2 Sample Components of Eye Pattern                                             |      |

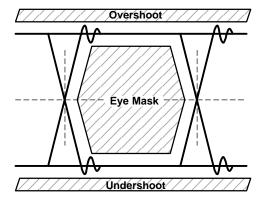

| 7–3 Eye Mask                                                                     | 7–3  |

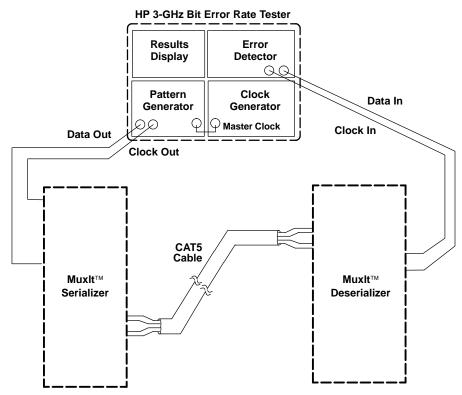

| 7–4 Example BER Test Setup With MuxIt EVM                                        | 7–5  |

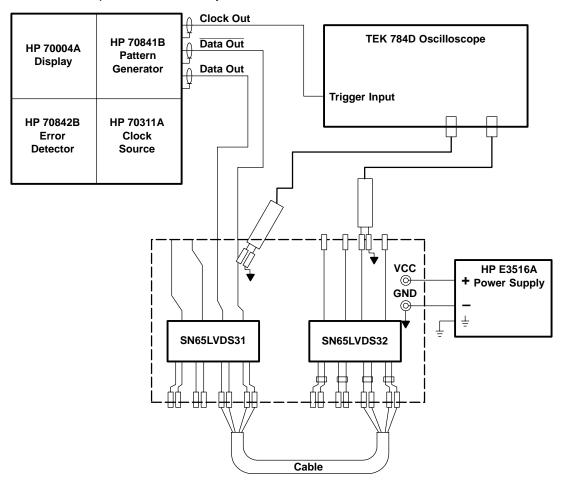

| 7–5 Test Setup for Trouble Shooting Section                                      | 7–6  |

| 7–6 Flying A                                                                     | 7–7  |

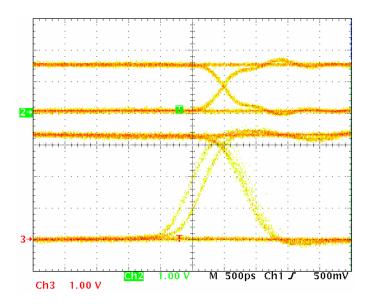

| 7–7 Input and Output Eye-Crossing With 100-MHz Clock Signal                      | 7–8  |

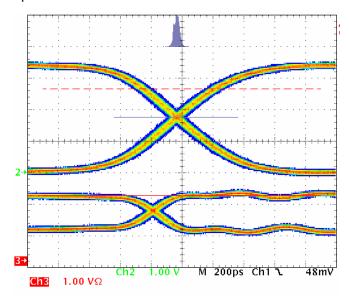

| 7–8 Input and Output Eye-Crossing With PRBS Data at 200 Mbps                     |      |

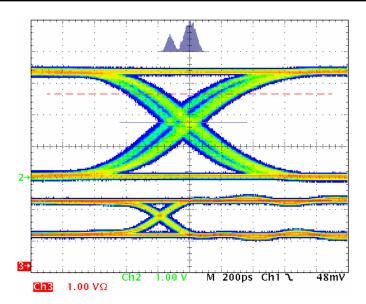

| 7–9 Jitter With Adjacent Channel In Operation and Clock Signal                   | 7–9  |

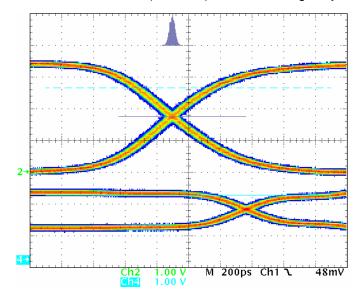

| 7-10 Jitter With Adjacent Channel and PBRS Data                                  | 7–10 |

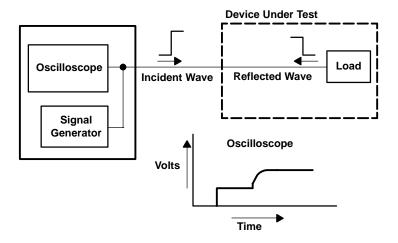

| 7–11 TDR Setup                                                                   | 7–10 |

# **List of Tables**

| Table                             | Title                            | Page |

|-----------------------------------|----------------------------------|------|

| 2–1 Noise Voltage Tolerance of    | Differential Signaling Standards | 2–5  |

| 3–1 ECL Output Voltage Levels     |                                  | 3–5  |

| 4–1 Cross-Point Switches          |                                  | 4–1  |

| 4–2 Serializers and Deserializers | s                                | 4–2  |

| 4-3 Driver and Receiver Combin    | nations Devices                  | 4–3  |

| 4-4 LVDM and M-LVDS Transce       | eivers                           | 4–4  |

| 4-5 LVDS Receivers                |                                  | 4–4  |

| 4–6 Line Drivers                  |                                  |      |

| 4–7 Repeaters                     |                                  | 4–7  |

| 5–1 Alphanumeric Listing          |                                  | 5–2  |

| 6-1 Types of Crosstalk            |                                  | 6–1  |

|                                   |                                  |      |

| 6–3 LVD FVMs                      |                                  | 6–15 |

#### INTRODUCTION

High-speed transmission of binary data has converged to a general class of low-voltage differential signaling (LVDS) that presents unique challenges to the designer. This handbook is a compilation of application notes for data transmission above 30 Mbps using an LVDS electrical layer.

What is LVDS? Where should it be used? What are its benefits? What are its limitations? Answers to these and other questions are the subject of this document. This guide examines the details of low-voltage differential signaling (LVDS) and provides applications information to help designers use these devices. This document looks at TI's broad selection of discrete LVDS devices ranging from single-channel drivers and receivers to serialization devices that significantly reduce the cabling, connector, and component costs required for today's interface solutions. However, before exploring the details of LVDS, step back first and look at data transmission in general, and see where LVDS fits in.

Transmitting data from one location to another, whether it takes place between integrated circuits on a printed-circuit board, or between networked computers located halfway around the world, has resulted in the development of numerous transmission technologies. These include electrical, optical, and wireless interfacing solutions. Over the past three decades, Texas Instruments has combined its expertise in high-speed digital and analog technologies to provide leading-edge solutions to meet the demands of today's data transmission needs. TI is constantly pushing the capabilities and extending the performance parameters of practically every electrical data-transmission standard.

Chapter 1 presents the basics of data transmission. Chapter 2 provides a mapping of system-level requirements to line-circuit features and characteristics; this becomes a basis for product selection in Chapter 4. To stimulate some design ideas, some application examples are provided in Chapter 3. Chapter 4 presents the product selection. Specifications are provided in Chapter 5 and Chapter 6 offer design guidelines and tools for obtaining optimum performance with the chosen line circuit. Finally, Chapter 7 presents common testing techniques used to verify or troubleshoot the design.

# Chapter 1 Data Transmission Basics

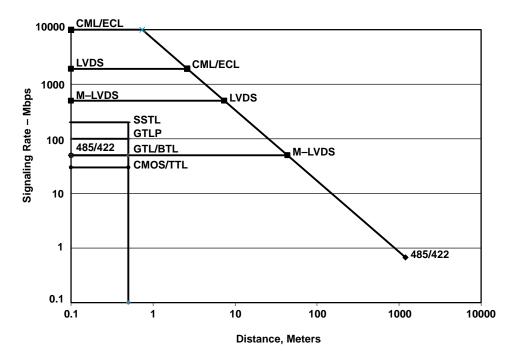

Data transmission, as the name suggests, is a means of moving data from one location to another. Choosing the best transmission standard to accomplish this requires evaluation of many system parameters. The first two considerations encountered are *How fast?* and *How far? How fast?* refers to the signaling rate or number of bits transmitted per second. *How far?* is concerned with the physical distance between the transmitter and receiver of the data. Consideration of these two primary system parameters usually results in a significant narrowing of the possible solutions. Figure 1–1 shows the speed and distance coverage of some familiar data transmission choices.

Figure 1-1. Approximate Signaling Rate vs Transmission Distance for Various Interfaces

As can be seen in Figure 1–1, signaling rate eventually decreases as transmission distance increases. While steady-state losses may become a factor at the longest transmission distances, the major factors limiting signaling rate, as the distance is increased, are time varying. Cable bandwidth limitations, which degrade the signal transition time and introduce intersymbol interference (ISI), are primary factors reducing the achievable signaling rate when transmission distance is increased.

Figure 1–1 also shows that general-purpose, single-ended logic, including backplane transceiver logic (BTL: IEEE 1194.1), gunning transceiver logic (GTL), and gunning transceiver logic plus (GTLP) provide satisfactory interface solutions when the transmission distance is short (< 0.5 m) and the signaling rate is moderate. When transmission distance is increased, standards with higher voltage swings or differential signaling often move the data.

If data transmission over about 30 m and less than 50 Mbps is required, differential signaling standards TIA/EIA-422 and TIA/EIA-485 should be considered. High differential outputs, sensitive receivers, and the capability to operate with up to 7 V of ground noise make these interfaces ideal for long direct connections between equipment. TIA/EIA-422 and TIA/EIA-485 use similar voltage levels but differ in the bus topologies they can support. TIA/EIA-422 is used for multidrop (one driver and many receivers) operation, while TIA/EIA-485 allows for multipoint signaling (many drivers and receivers).

For signaling greater than 50 Mbps or in low-power applications, low-voltage-differential signaling (LVDS) or multipoint-low-voltage-differential signaling (M-LVDS) provides an attractive solution. Introduced in 1996, LVDS, specified in TIA/EIA-644 offers high signaling rates and low power consumption for point-to-point or multidrop buses. M-LVDS, specified in TIA/EIA-899, was introduced in 2002 and offers similar benefits for the multipoint application. The benefits, features, and application of LVDS and M-LVDS are the subject of this handbook.

When the signaling rate requirements exceed the capabilities of LVDS, current-mode logic (CML) circuits are used, principally the emitter-coupled logic (ECL) and positive ECL (PECL) families. Signaling at 10 Gbps is possible with ECL/PECL devices. The high speeds are achieved at the cost of high power consumption.

#### **Transmission Lines and Characteristics**

An LVDS output voltage can switch from one logic state to the opposite in 260 ps and, in most applications, the interface must be modeled as a distributed-parameter circuit. This is not a model that most users relish analyzing. Fortunately, in most applications users can apply a transmission line model to the interconnect. Many others have solved transmission line characteristics and equations and only a summary is presented here.

Applying a transmission line model to the interconnection between LVDS circuits requires that two conditions be met.

- 1. The physical dimension of the interconnect circuit must be long compared to the shortest wavelength (highest frequency) of the signal. The highest frequency component of a binary signal is determined by the voltage (or current) transitions between logic states. This makes key parameters of the driver output voltage rise and fall times, since the fastest signal changes take place at this point in the circuit. If the delay time of the interconnect circuit is more than three times the 10%-to-90% transition time of the signal, the circuit is generally long enough to be modeled as a transmission line.

- 2. The dimensions of the conductors, the distance between the signal and return conductors, and the dielectric around them must be constant. The transmission line solution is based upon the model of each small segment along the transmission path being electrically the same and taking the segment length to zero. A discontinuity in the physical characteristics along the transmission path forces either a multiple transmission line model or a distributed parameter solution.

With the above conditions, the interconnect can be modeled as an ideal transmission line whose characteristics are determined by its distributed (per unit length) capacitance, C, and inductance, L. A good approximation results in the following characteristics:

- An ideal transmission line has a *characteristic impedance*, and both voltage and current at any point on the line are related by  $Z_0 = v/i$ . The characteristic impedance is real (resistance) and  $R_0 = \sqrt{L/C} \ \Omega$ .

- The time delay per unit length of an ideal transmission line is a constant with a value of  $v_0 = \sqrt{LC} \Omega$  seconds/length.

- The ideal transmission line is lossless, and there is no attenuation of the input signal along the transmission path.

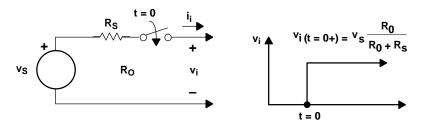

When a line driver changes output states, an initial voltage wave is launched into the transmission line. The driver output characteristics and the characteristic impedance of the transmission line determine the voltage and current of the wave (see Figure 1–2).

See reference 4 for one solution.

Figure 1–2. Initial-Wave Circuit Model

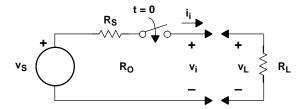

In the ideal transmission line model, the initial wave would continue to propagate to infinity. Since real circuits have an end to them, the wave encounters a load resistance,  $R_L$  (see Figure 1–3). At that point, the total signal power available is what was input some time ago as  $P_i = v_i^2/R_O$ . Since the power in the load is  $P_L = v_L^2/R_O$  and energy must be conserved, one might suppose that  $v_i^2/R_O = v_i^2/R_L$ . However, if  $R_O$  were greater than  $R_L$  and the incoming voltage and the voltage across the load were the same, there would be more power on the load than was input to the line. From the conservation of energy principal, this cannot be and means there is a missing term from the power equality and  $v_i^2/R_O = v_L^2/R_L + v_r^2/R_O$  where the term  $v_r^2/R_O$  is the power not absorbed by the load and reflected back into the transmission line.

Figure 1-3. The Line-Load Boundary

A bit of algebraic manipulation shows that the ratio of  $v_r$  to  $v_i$  needed to maintain energy equilibrium is  $\frac{v_r}{v_i} = \frac{R_L - R_O}{R_L + R_O}.$  This is defined as the voltage reflection coefficient of the load and is often designated as  $\rho_{v_i}$ .

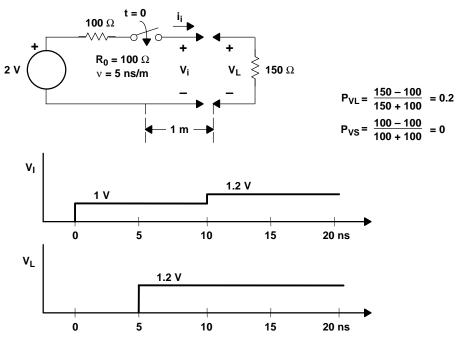

**Example**: Figure 1–4 gives an example of a 2-V source with a 100- $\Omega$  source resistance driving one meter of cable terminated with 150  $\Omega$ . At t = 0, an initial voltage wave of 1 V is generated at the source and is determined by division of 2 V by the 100- $\Omega$  source and characteristic impedance of the transmission line. The wave propagates down the cable at 5 ns/m where it reaches the 150- $\Omega$  load resistor. At that instant, a reflection is generated of  $v_r = v_i \times \rho_{VL} = 0.2$  V. The reflected voltage adds to  $v_i$  and the voltage across R<sub>L</sub> goes to  $v_i + v_r = v_i$  (1+ $\rho_{VL}$ ) = 1.2 V. The reflected wave travels back towards the source where the 100- $\Omega$  source resistance absorbs all of the signal power as indicated by the reflection coefficient of zero at the source.

Figure 1-4. Reflected-Wave Example

If transmission lines were ideal and lossless, there would be no limit on how long a cable could be and still be able to recover the input signal. As seen in Figure 1–1, the maximum signaling rate decreases as the cable length increases. This is due to the second-order effects not included in the ideal transmission line model. Skin, proximity, dielectric loss, and radiation loss effects all act to influence the primary line parameters and degrade the signal. Estimation of these effects is best made empirically and the application chapters of this document offer guidelines.

## Single-Ended vs Differential

We referred earlier to single-ended data transmission (as employed in BTL, GTL, GTLP, TIA/EIA–232, etc.) and differential transmission (as used with TIA/EIA-422, TIA/EIA-485, TIA/EIA–644 (LVDS), etc.). Each method of transmission has benefits and disadvantages.

## Single-Ended Transmission

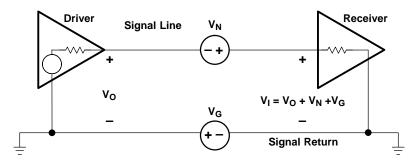

Single-ended transmission is performed by using one signal line for each information channel and a common ground return path shared among numerous information channels. Figure 1–5 shows the electrical schematic diagram of a single-ended transmission system. Single-ended receivers interpret the logical state at their inputs based upon the voltage at the single input line with respect to ground.

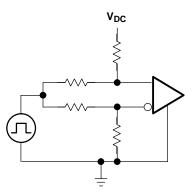

Figure 1-5. Single-Ending Interface Circuit Schematic Diagram

The advantages of single-ended transmission are simplicity and low cost of implementation. A single-ended system requires only one line per signal. It is therefore ideal when cabling and connector costs are more important than the signaling rate or transmission distance. You will find this tradeoff in low-speed PC applications such as a parallel printer port or serial communication with many handshaking lines.

The main disadvantage of the single-ended solution is its relatively poor noise performance at high signaling rates or long distances. Because the noise coupled to the circuit adds to the signal voltage, it is susceptible to data errors. The signal line of a single-ended circuit acts as an antenna to radiate and receive electric fields while the area formed around the circuit path is an antenna for magnetic fields. The voltage source  $V_N$ , as shown in Figure 1–5, represents this high-frequency electromagnetic coupling. Since single-ended interface circuits generally share the return path with other circuits, there is also a component of conducted susceptibility as changes in the ground current create the ground noise voltage represented by  $V_G$ . This noise is generally low in frequency (i.e., 60 Hz from main power).

#### Differential Transmission

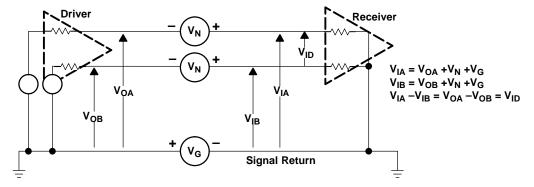

Differential transmission addresses many of the shortcomings of single-ended solutions by using a pair of signal lines for each information channel. Figure 1–6 shows an electrical schematic diagram of a differential transmission system. The differential driver uses a pair of complementary outputs to indicate the state transmitted. The differential receiver detects the voltage difference between the signal pair, rather than relative to ground, to determine its output state.

Figure 1-6. Differential Interface Circuit Schematic Diagram

This mode of transmission has several important advantages over single ended. You can see the fundamental advantage in the derivation of the differential input voltage,  $V_{ID}$ , in Figure 1–6. The noise sources  $V_{N}$  and  $V_{G}$  add to the input signals  $V_{IA}$  and  $V_{IB}$ , just as with the single-ended circuit, but by taking the difference between the two input voltages, the common noise terms are cancelled from the desired signal. The differential receiver accomplishes this and, with small differential input voltage thresholds, maintains high signal-to-noise ratios.

There is a presumption that the  $V_N$  coupled to each signal line are equal or nearly so. Differential signal pairs that are close together are generally exposed to the same noise sources. Twisting the signal wires together adds to this advantage. This ensures similar exposure to electric fields and cancels differential emf from magnetic field coupling by reversing the polarity in adjacent loops created by the twist.

In addition to noise immunity, differential circuits radiate substantially less noise to the environment than single-ended circuits. This is primarily due to the complementary current in each line of the signal pair canceling each other's generated fields. Conducted noise is also lower because there is little common-mode current to circulate through the signal return path.

Differential signaling adds cost and complexity in silicon and interconnecting hardware where it is roughly double that for a single-ended interface. As signaling rate or the number of circuits increase, this becomes less of a disadvantage as you add ground wires to make the single-ended signaling work. Indeed, you can find few data interfaces above 10 Mbps or longer than a half meter or so that are not differential.

#### Point-to-Point, Multidrop, and Multipoint Buses

Each electrical interface design is different, but interface problems can be categorized into certain common topologies or architectures. The number of drivers and receivers physically interconnected via a common media determines the architecture, limits the possible interface solutions, and drives the requirements on line circuits.

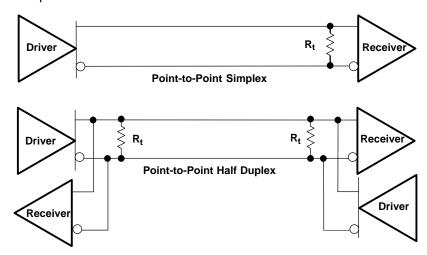

#### Point-to-Point

A point-to-point interface consists of only two connections to the transmission media. This can be a single driver and a single receiver in a simplex connection (unidirectional transmission) or a transceiver at each end operating in half duplex (bidirectional transmission). The point-to-point connection provides the optimum configuration from a performance viewpoint. A point-to-point connection avoids mainline stubs and other discontinuities, and provides the highest possible signaling rate. Figure 1–7 shows a differential point-to-point simplex and half-duplex connection.

Figure 1-7. A Point-to-Point Data Interchange Circuit

#### Multidrop

A multidrop or distributed simplex distribution bus is the second common interconnection approach. A multidrop bus consists of a single driver with multiple receivers connected to the main transmission line. The line termination is most often located at the far end of the line. Like point-to-point, a multidrop connection provides unidirectional transmission. Multidrop communication is common when a single master needs to broadcast the same information to multiple slaves. Figure 1–8 shows a differential multidrop interconnection.

Figure 1-8. A Multidrop Data Interchange Circuit

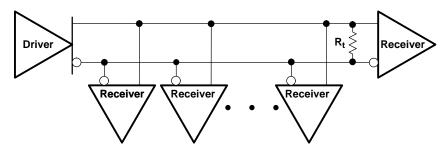

#### Multipoint

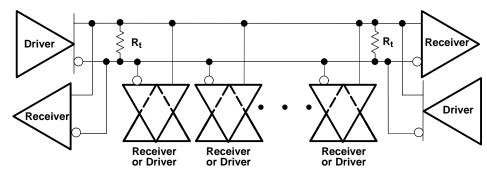

The final architecture is multipoint, also called multiplex, communication. A multipoint bus is three or more stations or nodes connected to a common transmission line where any two nodes can establish communication. Electrical requirements for the line circuits are the same as for the point-to-point half-duplex connection but are flexible in the number of listen-only, talk-only, or talk-and-listen stations. Figure 1–9 shows a multipoint interconnection.

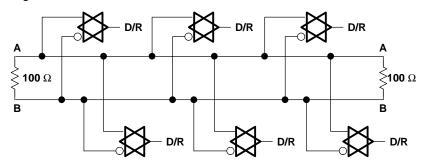

Figure 1-9. A Multipoint Data Interchange Circuit

Physical location of stations may require other system topologies. However, once you adopt the transmission-line model, it must be constructed using these basic interconnections and linked through repeaters or concentrators to maintain a clean electrical path between stations connected to a single transmission-line segment. Data-flow management of these hybrid configurations is complex and beyond the scope of this handbook.

#### **Benefits of Standardization**

Data transmission, as the name suggests, is a means of moving data from one location to another. To accomplish this, the sender and receiver must have agreed upon the nominal rate of transmission, the information-to-bit mapping pattern, the communication protocol, and the electrical states and pulse codes used to represent logical states on the bus. These (and other) agreements are often made in either formal or informal interface standards and can specify the requirements to varying depths or layers. This handbook addresses only the lowest (electrical) layer of the interface.

Standardization allows for interoperability of equipment or parts from different suppliers, and independence from sole-source suppliers. It also encourages competition between multiple producers. When multiple vendors compete for the same standardized business, design innovations and production efficiency become key competitive factors. The benefits are higher quality and more readily available mass-produced goods at lower prices.

Without standards, common items such as screws and nuts, light bulbs, tires, and computer parts would be significantly more expensive, and it would be much harder to find replacements for them. A simple example of how a lack of standardization raises costs and makes replacements harder to find is valve stems for faucets. The local building centers or plumbing-supply houses have a variety of choices; getting exactly the right one is costly and quite often a gamble.

More to the point of this document is the world of electrical interfaces, where standardization permits interoperation of systems produced by different vendors. The worlds of computers and telecommunications are based on standards. You can trace the explosive growth of the IBM-compatible personal computers in the consumer market directly to the availability of a large number of publicly available electrical and mechanical interface standards. Numerous other personal-sized computer systems have failed commercially because either their makers kept the interfaces secret, or they were incompatible with already established and popular standards.

#### 644 vs 644a vs LVDM vs M-LVDS

Standardization bodies conceived LVDS (as specified in TIA/EIA-644) to provide a general-purpose electrical-layer specification for drivers and receivers connected in a point-to-point simplex interface. The standard requires receivers to have input leakage currents below 20  $\mu$ A, which drive the receiver input impedance requirements. Figure 1–10 shows the driver test circuit.

Figure 1–10. TIA/EIA-644 Driver Output Test Circuit

Although 644 compliant devices have seen rapid and broad acceptance in point-to-point communications, the 644 standard does not quantify the driver characteristics required for multidrop operation. (As discussed previously, a multidrop application has one driver communicating with multiple receivers.) The 644 receiver leakage requirement of 20  $\mu$ A has a small effect on the driver output voltage when only one receiver is connected, but this effect becomes more pronounced as the driver is loaded with additional receivers. An update to LVDS, designated TIA/EIA-644-A, standardizes the driver requirements for LVDS devices being used in a multidrop configuration. The full-load test required for the driver output identifies 644-A compliant devices. Figure 1–11 shows the 644-A test circuit, which ensures connection of 32 receivers in a multidrop configuration.

Figure 1–11. TIA/EIA-644-A Driver Output Test Circuit

A distinct difference for the driver in a half-duplex point-to-point or multipoint bus versus a point-to-point simplex or multidrop bus is the load presented to the driver as the output switches. When transmitting from the end of the line, the driver load is a transmission line with characteristic impedance of  $R_0$  in parallel with the termination resistor used to prevent reflections from other driver(s). If properly terminated, the termination value is  $R_0$  and the equivalent load becomes  $R_0/2$ . The load presented to a driver located midbus is two transmission lines in parallel and presents a time-varying load to the driver of  $R_0/2$ . Since reflection prevention requires termination resistors equal to  $R_0$  at both ends of the line, the steady-state load is also  $R_0/2$ .

The need for multipoint LVDS-like drivers quickly emerged and TI and National Semiconductor offered proprietary solutions. TI offers an LVDM family of drivers, which are compliant with the 644 LVDS standard, with the exception of a doubling of the output current. These LVDM drivers are also useful for additional noise margin in a multidrop or a point-to-point connection.

The proprietary solutions were not necessarily interchangeable or did not address all of the requirements for a robust multipoint interface circuit. In response, the technical committees of TIA developed TIA/EIA-899 to standardize and provide the benefits of LVDS in a multipoint environment. Familiarly known as multipoint-LVDS or M-LVDS, TIA/EIA ratified and published this standard in early 2002. TI participated in the development of this standard, and has developed components that are in full compliance.

TIA/EIA-644-A LVDS and TIA/EIA-899 are both ANSI-accredited international standards and higher-level standards reference them for the electrical layer of data interfaces. Higher-level standards address mechanical and protocol requirements.

#### LVDS/M-LVDS Summary

The most attractive features of LVDS include its high signaling rate, low power consumption, and electromagnetic compatibility. The following sections summarize each of these benefits and Chapter 2, LVDS and M-LVDS Line Circuit Characteristics and Features, offers a more detailed explanation.

#### Signaling Rate

We define the number of state changes per unit time as the signaling rate for the interface. Knowing the unit interval time, t<sub>UI</sub>, between state changes, you can derive the signaling rate as the inverse of the unit interval.

TIA/EIA-644-A and TIA/EIA-899 require that driver output transition times be less than 30% of the unit interval, with a lower limit of 260 ps and 1 ns, respectively. The standards also recommend that the transition time at the receiver input be less than 50% of the unit interval. The difference between driver output rise time and receiver input rise time allows for signal degradation through the interconnect media.

Combining the driver transition times required by the standard, and receiver input rise time recommendations, LVDS supports a theoretical maximum signaling rate of 1.923 Gbps and M-LVDS 500 Mbps. Longer transition times, leading to lower signaling rates, are also allowed by the standards. You should note that the standards define the characteristics at the interface to the bus and not the line circuit. Line circuits may support signal transitions faster than 260 ps and even higher signaling rates if standard compliance is not required.

When estimating the minimum signaling rate for a particular line circuit, designers should use the maximum output transition time. For example, in the SN65LVDS31, the maximum specified 20%-to-80% differential output transition time is 600 ps. Using the 30% relationship between rise time and unit interval, we see that this driver can support standard unit interval of 600 ps/0.3 = 2000 ps or a signaling rate of 500 Mbps. The 30% rule is conservative and users can obtain higher signaling rates with appropriate timing budgets.

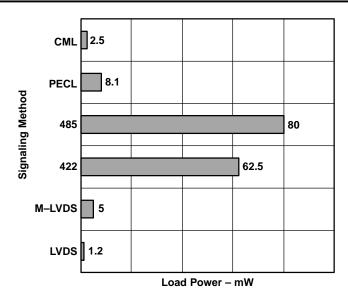

#### Power

As the name implies, LVDS is a low-voltage signaling standard. An LVDS output driver provides 350 mV, nominal, into a  $100-\Omega$  load. This results in  $\approx 1.2$  mW of power delivered to the load. Figure 1–12 compares the load power of LVDS and other differential signaling techniques and shows LVDS to be 1.5% to 50% of the presented signaling approaches. In general, a lower load power correlates closely with lower overall power for the interface.

Figure 1–12. Load Power Comparison of Differential Signals

## Electromagnetic Compatibility

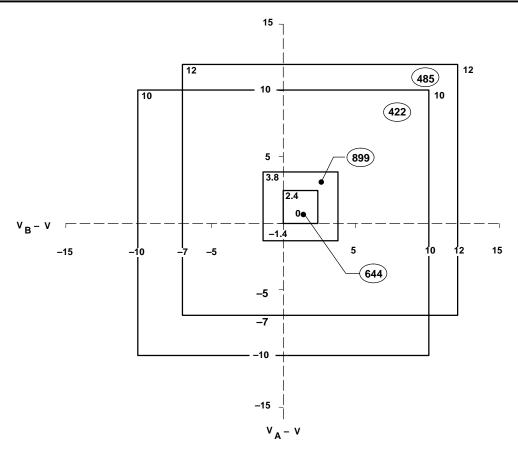

Differential signaling allows LVDS to operate in the presence of electromagnetic noise, while at the same time minimizes its own radiated emissions. Differential signaling also rejects externally coupled noise common-mode when within the input range of the differential receiver. Figure 1–13 shows the voltage range for different TIA/EIA standardized interfaces. It is interesting to note that an attempt to include ECL, CML, or other informal standards is difficult or impossible due to the lack of a single specification but rather a family of similar device data sheets.

Figure 1-13. TIA/EIA Standard Voltage Ranges

# References

- TIA/EIA-644: Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits in 1996

- 2. TIA/EIA-899: Electrical Characteristics of Multipoint-Low-Voltage Differential Signaling (M-LVDS)

- 3. Hayt, William H., Engineering Electromagnetics, McGraw Hill, Inc., 1974: 407–424

# Chapter 2

#### LVDS And M-LVDS Line Circuit Characteristics and Features

This chapter builds on the introductory material presented in Chapter 1 by attempting to provide the reader with some insight into the line circuit features and their impact on system performance. The chapter presents specific requirements of the TIA-644-A and -899 standards along with nonstandard characteristics that affect overall performance.

#### **Driver Output Voltage**

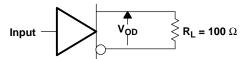

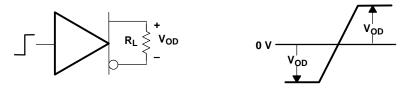

The driver's primary function is to launch an electromagnetic wave into one or two transmission lines. As explained earlier, this is equivalent to generating a voltage across a resistor, albeit a low-valued resistor. Most device specifications designate the differential output voltage as  $V_{OD}$  and referenced to the inverting output. Both the minimum and maximum output voltages are significant parameters, as the minimum sets the minimum noise margin for the interface and the maximum establishes the input voltage range of circuits connected to the bus.

Figure 2–1. V<sub>OD</sub> Definition

TIA/EIA-644-A drivers must generate a  $V_{OD}$  of 247 mV to 454 mV across 100  $\Omega$ , while 899 drivers require more voltage, 480 mV to 650 mV, across the smaller load of 50  $\Omega$ . The reasons for the difference fall back to the extra noise contributors in the multipoint environment versus point-to-point discussed earlier.

Beyond the basic function, the symmetry of the complementary outputs becomes an important characteristic for noise emissions from the line. Ideally the current in each conductor of the signal pair is equal and opposite; as usual, the ideal is too expensive to achieve. This means that there is always some inequality in the two currents called imbalance. Imbalance can result from differences in the electrical characteristics of the complementary driver output circuitry or the loads, or from time delay between switching outputs. This is particularly critical, as the common-mode components created during switching imbalance are high in frequency and radiate readily.

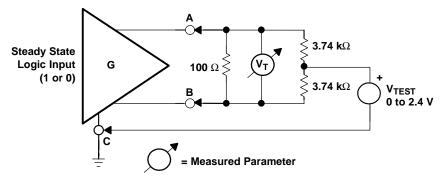

The differential driver parameter of significance in this regard is the common-mode output voltage,  $V_{OC}$  (sometimes designated a  $V_{OS}$ ), and is the arithmetic mean of the two complementary output voltages. You measure this driver characteristic directly by monitoring the output voltage at the node between two identical resistors connected across the line as shown in Figure 2–2. The common-mode output can be broken down to the steady-state and peak-to-peak parameters  $V_{OC(SS)}$  and  $V_{OC(PP)}$  with emitted noise frequency fundamentals of 0.5/t<sub>UI</sub> Hz with  $V_{OC(SS)}$  and out to 3/t<sub>UI</sub> Hz and beyond with  $V_{OC(PP)}$ .

Figure 2-2. Circuit Used to Measure the Driver Common-Mode Output Voltage

The smaller the V<sub>OC(PP)</sub> parameters are, the better the noise emission performance of the interface. Both TIA/EIA-644 and -899 require their drivers to create no more than 150 mV of V<sub>OC(PP)</sub>. When comparing the radiation potential of a data line, V<sub>OC(PP)</sub> is directly comparable to the voltage swing of a single-ended signal, and the advantage of differential over single-ended signaling in this regard becomes obvious.

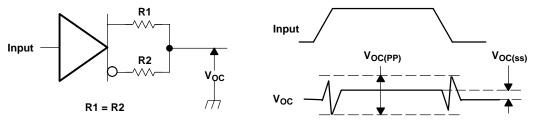

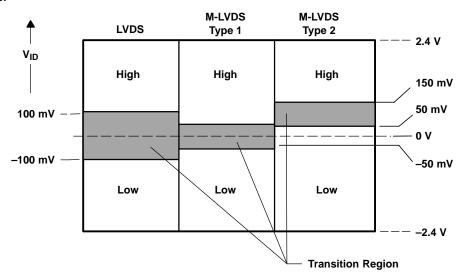

## Differential Input Voltage Threshold

The input signal to the transmission line is the driver output voltage; the differential receiver must detect what comes out. The first parameter to consider for a receiver is the differential input voltage threshold, VIT, as it defines the voltage needed to change the receiver output state. The specified maximum and minimum VIT establish the limits for VIT, and difference voltages above or below them assure that the receiver indicates a valid logic state at its output.

The EIA/TIA-644-A standard specifies a maximum VIT of 100 mV and a minimum of -100 mV under all operating conditions and over the input common-mode voltage range. With a minimum driver differential output voltage of 247 mV, this provides a worst-case differential noise margin of 147 mV. Although this may seem like a small value, interference in a well-balanced differential transmission system introduces virtually no differential noise.

In addition to a higher minimum output voltage for TIA/EIA-899 drivers, compliant receivers must exhibit a maximum V<sub>IT</sub> of 50 mV and a minimum of -50 mV for Type-1 receivers, for a minimum 400 mV differential noise margin. TIA/EIA-899 also specifies Type-2 receivers with a maximum V<sub>IT</sub> of 150 mV and a minimum of 50 mV. The offset V<sub>IT</sub> of a Type-2 receiver allows a 0-V difference to be a valid bus state and is useful for wired-logic signaling or failsafe provisions. Figure 2-3 shows a graphical summary of the input voltage thresholds.

Figure 2-3. LVDS and M-LVDS Differential Input Voltage Thresholds

A differential input voltage between the maximum and minimum thresholds lies in the transition region and results in an indeterminate output state. The output may be high, low, or on its way between states. The time-varying behavior of the output during transition depends upon the bandwidth of the receiver and the time variation of the input voltage.

Consider an LVDS line receiver as a differential amplifier with a gain of about 100,000. VIT is the input voltage where the output would be one-half of the way between high and low and, with no feedback for hysteresis, it takes only a few 10s of microvolts above or below the threshold for the output to switch to a high or low state. The system is likely to have this much differential noise and, if near the threshold, could cause oscillation of the output<sup>2</sup>.

<sup>2</sup>See Fault Tolerance and Failsafe Receivers section later in this chapter for handling this condition.

Fortunately, the gain at high frequencies goes down to a point where the circuit does not respond to noise riding on the input signal. A rule of thumb is to transverse the input transition region  $(V_{IT(MAX)} - V_{IT(MIN)})$  in less than 10 x  $t_T$ , where  $t_T$  is the 20%-to-80% output transition time of the receiver. For example, for a receiver with an output transition time of 1 ns, you would want the input signal to go through the transition region in under 10 ns. If the design cannot assure the input transition times, we recommend a receiver with some internal feedback to provide input voltage hysteresis. TI has LVDS and M-LVDS receivers that provide 25 mV of hysteresis.

#### Common-Mode Voltage Range

Referring back to Figure 1–6 in Chapter 1 and related discussion, differential signaling works well because noise is common to both signal lines and is rejected. As with all circuits, there is a limit to the noise voltage magnitude and frequency that a differential receiver can reject. This leads to the need to specify a receiver's input common-mode voltage range, commonly designated as V<sub>ICR</sub>. The common-mode voltage range required for an interface circuit represents a compromise that takes into account numerous factors including the available semiconductor technologies, signaling rates, cable impedances, distance goals, and other relevant environmental factors.

The impact of EMI on a perfectly balanced differential transmission line is to induce a purely common-mode voltage which is identical on each of the two conductors. The magnitude of the induced common-mode voltage is a function of several factors: The strength, orientation, and proximity of the disturbing source; the effects of any shielding that may be present; and the common-mode impedance characteristics of the transmission system. Predicting the exact nature of EMI-induced common-mode voltage is difficult at best, but the reader should assume there is always some amount present.

Ground potential differences are another major source of common-mode noise voltage<sup>3</sup>. They may be induced by EMI, by the power distribution system, or by ground-return currents in the local power supplies. Predicting the magnitude of ground shift induced common-mode voltage is also very difficult, and designers need to examine each installation and use good design and layout techniques to reduce or eliminate these problems.

Common-mode rejection is an inherent feature of true differential receivers, just as it is with other differential-input circuits such as operational amplifiers. The degree to which a differential amplifier or receiver can reject common-mode voltages is a function of several factors. Careful electrical and mechanical design of the receiver components and interconnections is required to ensure that the matching is as close to ideal as possible. Designers can use an input attenuator to reduce the common-mode voltage seen by the circuit, typically with a proportional loss in the differential signal. The attenuator can employ active feedback circuits to sense and partially compensate for the received common-mode voltage such that they attenuate more of the common-mode than the differential signal. They have finite response times and so are of decreasing value as the frequencies increase.

Passive filtering termination circuits can also attenuate the common-mode noise seen at the receiver terminals more than the differential signals. Common-mode chokes, or baluns, along with split termination resistors with capacitors to ground from the center point, are frequently used filter implementations.

The receiver common-mode input voltage is the mean value of the voltages at the inputs,  $V_{IA}$  and  $V_{IB}$ . Summing the defining equation for these two voltages from Figure 1–6 in Chapter 1 and dividing by two gives the expression for the common-mode voltage below.

$$V_{IC} = \frac{V_{IA} + V_{IB}}{2} = \frac{V_{OA} + V_{N} + V_{OB} + V_{N} + V_{G}}{2}$$

<sup>&</sup>lt;sup>3</sup>Some additional information related to common-mode noise and LVDS is available in several TI application reports. *A Statistical Survey of Common-Mode Noise* (SLLA057); LVDS in Harsh Environments with the Next Generation Receivers (SLLA061), and Solving Noise *Problems with LVDS* (SLLA073).

Combining and rearranging the terms gives,  $V_{IC} = \frac{V_{OA} + V_{OB}}{2} + V_{N} + V_{G}$ , and recognizing that  $\frac{V_{OA} + V_{OB}}{2} = V_{OC}$  gives  $V_{IC} = V_{OC} + V_{N} + V_{G}$ . This means that the receiver input common-mode voltage range includes the driver  $V_{OC}$  as well as the noise terms and must accommodate both. It is also important to recognize that  $V_{IC}$  contains steady-state as well as time-varying components.

TI measures common-mode rejection versus frequency for a differential line receiver as a go/no-go test since it has only two output states. Parameters such as common-mode rejection ratio (CMRR) applied to differential amplifiers have meaning only at nodes internal to the differential line receiver circuit. Instead, we evaluate the common-mode rejection of a differential line receiver by applying a steady-state maximum and minimum  $V_{IT}$  (100 mV and -100 mV in the case of LVDS) and a common-mode test pulse to the inputs as shown in Figure 2–4. The common-mode pulse transverses the  $V_{ICR}$  and we verify that the receiver's output does not change state. This test determines the common-mode frequency response by the high-order harmonics generated in the edges of the pulse and usually specifies a transition time of less than 20% of the intended minimum unit interval for the circuit. For example, a 500-ps transition time applies high-frequency harmonics out to the gigahertz range.

Figure 2-4. Common-Mode Rejection Test of a Differential Line Receiver

Table 2–1 shows the tolerance of the various differential signaling standards to common-mode noise voltage and introduces the SN65LVDS33 LVDS receiver with extended  $V_{ICR}$ . Texas Instruments' family of LVDS products includes several receivers with common-mode ranges that extend beyond the minimum specified in TIA/EIA-644-A. Wider  $V_{ICR}$  allows LVDS signaling in environments that would otherwise be too hostile for standard LVDS. Many of these devices are pin-compatible replacements for other popular receivers.

Table 2–1. Noise Voltage Tolerance of Differential Signaling Standards

| STANDARD                            | MAXIMUM<br>RECEIVER<br>INPUT<br>VOLTAGE | MINIMUM<br>RECEIVER<br>INPUT<br>VOLTAGE | RECEIVER<br>COMMON-MODE<br>INPUT VOLTAGE<br>RANGE              | MAXIMUM DRIVER<br>COMMON-MODE<br>OUTPUT VOLTAGE | MINIMUM DRIVER<br>COMMON-MODE<br>OUTPUT VOLTAGE | MAXIMUM<br>COMMON-MODE<br>NOISE VOLTAGE                                                                                |

|-------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Generic                             | V <sub>I(MAX)</sub>                     | V <sub>I(MIN)</sub>                     | V <sub>ICR</sub> =<br>V <sub>I(MAX)</sub> –V <sub>I(MIN)</sub> | V <sub>OC(MAX)</sub>                            | V <sub>OC(MIN)</sub>                            | $ \begin{aligned} & V_N + V_G = \\ & MIN(V_{I(MAX)} - \\ & V_{OC(MAX)}, \\ & V_{OC(MIN)} - V_{I(MIN)}) \end{aligned} $ |

| ECL <sup>4</sup>                    | -0.88                                   | -1.81                                   | 0.93                                                           | -1.25                                           | -1.417                                          | 0.37                                                                                                                   |

| PECL                                | 4.12                                    | 3.19                                    | 0.93                                                           | 3.75                                            | 3.583                                           | 0.37                                                                                                                   |

| LVPECL <sup>5</sup>                 | 2.42                                    | 1.355                                   | 1.065                                                          | 2.005                                           | 1.73                                            | 0.375                                                                                                                  |

| TIA/EIA-644-A                       | 2.4                                     | 0                                       | 2.4                                                            | 1.375                                           | 1.125                                           | 1.025                                                                                                                  |

| TIA/EIA-899                         | 3.8                                     | -1.4                                    | 5.2                                                            | 2.1                                             | 0.3                                             | 1.7                                                                                                                    |

| SN65LVDS33<br>with M-LVDS<br>Driver | 5                                       | -4                                      | 9                                                              | 2.1                                             | 0.3                                             | 2.9                                                                                                                    |

| SN65LVDS33<br>with LVDS Driver      | 5                                       | -4                                      | 9                                                              | 1.375                                           | 1.125                                           | 3.625                                                                                                                  |

| TIA/EIA-485-A                       | 12                                      | <b>-7</b>                               | 19                                                             | 3                                               | <b>-1</b>                                       | 6                                                                                                                      |

| TIA/EIA-422-B                       | 10                                      | -10                                     | 20                                                             | 3                                               | -3                                              | 7                                                                                                                      |

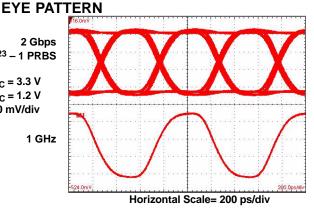

# Signaling Rate

The basic function of a line driver or receiver is the recreation of a logic state change over a distance. The signaling rate or data signaling rate is simply the number of state changes made per unit of time. It does not distinguish between data, clock, or handshaking signals, nor depends upon the bus architecture or protocol. It simply describes the transmission or reception rate of a single bit. Hence, the unit bits per second (bps) is used (this has replaced the term baud in binary transmission systems).

Signaling rate is an important parameter when determining the bandwidth requirements of a data interchange circuit of a line driver, interconnecting media, and line receiver. The transmission of two successive state changes forms the beginning and end of a voltage and current pulse down the circuit. As one expects, there is a limit to how short the pulse duration can be to allow successful reception at the other end of the signal chain.

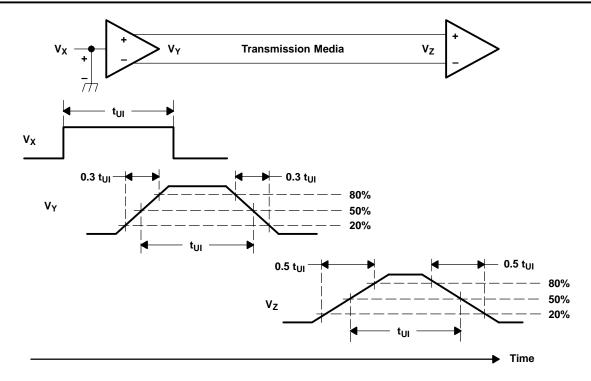

There must be signal quality criteria to specify or describe the minimum pulse duration or maximum signaling rate of a circuit. Many specifications describe the quality of a binary data pulse by the amount of time spent in transition between states relative to the duration of the pulse. TIA/EIA-644 and TIA/EIA-899 and other specifications define this criteria. These standards define the pulse duration as the unit interval or t<sub>UI</sub> and the maximum transition times as a fraction of t<sub>UI</sub>. Figure 2–5 shows the signal quality criteria from TIA/EIA-644-A.

<sup>&</sup>lt;sup>4</sup>100E series, High Performance ECL Data, Motorola, DL140/D, 1995 <sup>5</sup>MC100EP16 Data Sheet, On Semiconductor, April 2001

Figure 2–5. TIAS/EIA-644-A Signal Quality Recommendations

When the signal transition time reaches  $0.5 \ t_{UI}$  at the end of the transmission line, we have achieved the minimum pulse duration and maximum signaling rate for a single interface circuit. When evaluating the signaling rate capability of the line circuits however, most assume a lossless line and apply the  $0.3 \ t_{UI}$  limits to both the driver and receiver. (This is because the degradation of the transition time to  $0.5 \ t_{UI}$  allows for losses in the transmission media and not the line circuits.) This implies that the signaling-rate capability of the line circuits can be determined by their output rise and fall times and, on first order, is a good approximation.

#### NOTE:

Figure 2–5 shows that the transition time is measured from the entire signal swing and not from the receiver threshold. For example,  $0.5\ t_{UI}$  transitions still allow the minimum duration pulse to attain a steady-state level.

Basing the signaling rate upon the real-time shape of the data pulse ignores when the bus state becomes valid relative to the sampling instant. Assuming that the sampling time is stable and repeats, any variation in time of the bus state change adds or subtracts from the set-up or hold time required for sampling. We generically call this variation jitter and it comes from several sources in the line circuits.

Ideally, a line driver or receiver reproduces a state change at the output some fixed time after it occurs at the input. In reality, the propagation delay time varies with temperature, supply voltage, manufacturing process, the preceding bit sequence, and noise. All of these factors affect when the state is valid for sampling and further processing. The interface designer must allocate a budget for each within the communication system's timing budget. There are few standard methods used to characterize and specify these variables, but we can make some general observations and conclusions.

The highest speed interface circuits normally transmit timing information along with the data, encoded either in the data or in a separate parallel circuit. The method of transmitting timing information (clock) determines which type of line-circuit jitter must be budgeted. In general, only high-frequency jitter components are a concern in clock-encoded data and all jitter components are budgeted in the parallel-clocking approach.

Propagation delay time variation with temperature or manufacturing process is very low in frequency and specified in the propagation delay time limiting values of device data sheets. Since most parallel circuits operate at the same temperature and supply voltage, data sheets specify an additional parameter called part-to-part skew or  $t_{SK(PP)}$  to characterize manufacturing process variability only. This parameter is the propagation delay time of separately packaged line circuits when operated at the same supply voltage and temperature in the recommended operating range. A related parameter is output skew or  $t_{SK(O)}$  and is the propagation delay time difference between two parallel circuits residing in the same integrated line circuit. In a monolithic device, the two circuits were subjected to the same manufacturing process and the delays are closely matched.

The state changes or bits that have occurred before a transition affect the initial operating points in the line circuit and the propagation delay time. Data sheets often specify two parameters for this effect. Pulse skew, or  $t_{SK(P)}$ , is simply the difference in the propagation delay of a high-to-low and a low-to-high transition from a steady-state input condition and represents the maximum pattern-dependent delay time variation. A subset of  $t_{SK(P)}$  is the deterministic jitter or  $t_{j(d)}$ . This is a measurement of the delay time variation with a pseudo-random bit sequence and includes intermediate operating points for a statistical description of this jitter component. This jitter contribution is high in frequency (at or above the signaling rate).

Finally, the jitter contribution from noise is difficult to characterize and specify for line circuits and is best evaluated in the actual interface and environment. Data sheets may indicate noise-induced jitter in the typical characteristic sections of device data sheets that break out a random jitter parameter, show peak-to-peak jitter comparisons of multichannel line circuits under various operating combinations, graph propagation delay time versus common-mode or differential input voltage, or others.

#### **Power Consumption**

High signaling rates and low power are often mutually exclusive features of a data line interface. As the signal frequency increases, circuit impedances tend to decrease requiring more current to generate a voltage. Since power is the product of voltage and current, maintaining or reducing power levels requires a reduction in operating voltage. This is the impetus behind the development of LVDS and M-LVDS line circuits.

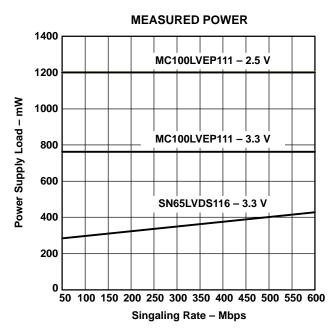

While the advantage of reducing supply and signal voltages is apparent, the authors designed both the LVDS and M-LVDS standards to minimize the amount of common-mode power by using a purely differential line termination with no low-impedance path to ground. This is most apparent when comparing LVDS to ECL circuits. The graph in Figure 2–6 shows a comparison between the power vs signaling rate characteristics of a 10-output ECL repeater and a 16-output LVDS repeater<sup>6</sup>. Even though the LVDS has 1.6 times the number of outputs, you can see that the LVDS device has roughly half the power dissipation. In fairness, you should note that most ECL/PECL devices run at higher maximum speeds than presently available LVDS devices, so there are some situations where the additional power of ECL/PECL is justified.

Figure 2-6. MC100LVEP111 and SN65LVDS116 Power Comparison

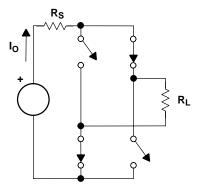

LVDS and M-LVDS drivers further reduce this wasted power by the common use of high impedance (relative to the load) outputs. Referring to Figure 2-7, as the source resistance (R<sub>S</sub>) increases, I<sub>O</sub> becomes less sensitive to changes in load resistance. This includes variation in R<sub>L</sub> and, more importantly, the momentary internal shorts from R<sub>S</sub> to ground that occur when transistors replace the ideal switches.

Figure 2-7. Differential Driver Circuit Model

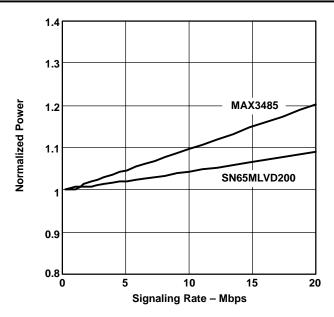

When compared to drivers with relatively lower output impedance (such as most RS-422 and -485 drivers), high-impedance outputs result in more stable power consumption with increasing signaling rate. To illustrate, Figure 2-8 shows the normalized power consumption of the MAX3485 3.3-V RS-485 and SN65MLVD200 M-LVDS driver<sup>7</sup>. It is important to note that MAX3485 consumes 142 mW while the SN65MLVD200 only consumes 54 mW in the steady state and the signaling rate extends to 200 Mbps for the SN65MLVD200.

<sup>7</sup>SLLA106 TIA/EIA-485 and M-LVDS, Power and Speed Comparison, Texas Instruments Incorporated, 2001

Figure 2-8. Normalized Power vs Speed Comparison of Voltage-Mode and Current-Mode Driver

## **Supply Voltage**

The LVDS and M-LVDS standard levels were designed around a 3.3-V supply system but do not specify the supply voltage for interface circuits. Provided the designer meets the interface specifications, LVDS or M-LVDS integrated circuits can operate from any voltage. There are 5-V LVDS circuits and some that operate down to 2.5-V, such as the SN65LVDS1050.

# Reliability

When operated within recommended operating conditions, interface circuits are as reliable as any other silicon-based circuit. However, exposure to transient noise coupled to long transmission lines or to static discharges through connector pins can damage interface circuits.

Although designers must treat noise in general application of interface circuits as random, manufacturers model certain recurring types of noise sources and specify the tolerances at the integrated-circuit level. Following is a brief overview of some of the more common models<sup>8</sup>.

Human-Body Model (HBM)—The HBM simulates the action of a human body discharging accumulated static charge through a device to ground, and employs a series RC network consisting of a 100-pF capacitor and a 1500- $\Omega$  resistor.

**Machine Model (MM)**—The MM simulates a machine discharging accumulated static charge through a device to ground. It comprises a series RC network of a 200-pF capacitor, and nominal series resistance of less than 1  $\Omega$ . The output waveform usually is described in terms of peak current and oscillating frequency for a given discharge voltage.

Charged-Device Model (CDM)—The CDM simulates charging/discharging events that occur in production equipment and processes. Potential for CDM ESD events occur when there is metal-to-metal contact in manufacturing. One of many examples is a device sliding down a shipping tube and hitting a metal surface. The CDM addresses the possibility that a charge may reside on a lead frame or package (e.g., from shipping) and discharge through a pin that subsequently is grounded, causing damage to sensitive devices in the path. The parasitic impedance and capacitance of the device limit the discharge current. CDM testing consists of charging a package to a specified voltage, then discharging this voltage through the relevant package leads. TI conducts CDM testing using a field-induced CDM (FCDM) simulator.

<sup>8</sup>SSY010 Electrostatic Discharge (ESD), Texas Instruments Incorporated, 2000

High specifications with any of the above noise models are an indication of how a device tolerates noise transients when installed in a printed-circuit card and an enclosure. Data sheets sometime specify the ESD tolerance separately for the bus pins (those connected to the transmission line) with respect to the supply pins, since these are the most susceptible after installation. Unfortunately, the installation has much to do with the ultimate performance in this regard and any claims of compliance with system-level specifications must come with complete specification of test conditions.

Texas Instruments offers LVDS devices with 15 kV of HBM ESD protection on the bus pins. This superior ESD performance is a direct result of the advanced analog silicon processes<sup>9</sup> used at TI, and is unavailable from most other vendors.

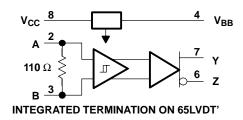

#### **Integrated Terminations**

Proper termination of a transmission line is necessary to reduce reflected signals. Reflected signals may lead to an increase in data errors, and so transmission system standards are very careful to define termination requirements. EIA/TIA-644-A defines a terminating receiver load in terms of a combination of line-termination impedance plus a receiver. The standard also defines the characteristics of receivers without line-termination impedances. The differential input impedance of a terminating receiver is to be between 90  $\Omega$  and 132  $\Omega$ , or approximately 111  $\Omega \pm 19\%$ .

Although the standard does not state specifically how the line-termination impedance is to be physically located as a part of the terminating receiver, it does have several cautionary notices about not introducing stubs and reflections. The ideal location of the line termination is as close to the receiver as possible, which then has a near-zero stub length. Texas Instruments has integrated termination resistors into several LVDS receivers. This gives the ideal zero-length stub, in addition to saving end users the need for purchasing and installing external components.

Integrating the termination resistors with the receiver circuit is essentially impossible with standard digital silicon processes, as used in ASICs. The reason is that the majority of those processes are incapable of providing resistive components that can meet the tolerance requirements of the standard. The advanced analog processes used to fabricate TI's terminated receivers include proprietary additions that provide the needed stable resistive components.

The cost savings potential provided by using TI's internally terminated LVDS receivers includes the purchase and stocking costs; the fabrication, QC, and R&M costs; and the additional PC board area. The board space savings can be particularly significant in situations where multiple parallel signal paths are involved. Texas Instruments has available a family of 8- and 16-channel LVDS receivers, both with and without internal terminations. In addition to saving the 8 or 16 termination circuits for each of these devices, they ease the layout of PC-board traces and eliminate stubs for maintaining signal quality.

<sup>9</sup>See SLLA065 A Comparison of LinBiCMOS and CMOS Processes Technologies for LVDS, Texas Instruments Incorporated, 2000

#### **Fault Tolerance and Failsafe Receivers**

One area of performance that is described, but not always specified, in the standards is the area of fault conditions. These may include conditions where the driver power is off, the receiver is not connected, and the transmission line is open or short circuited. All of these conditions may cause the differential input voltage to fall within the transition region<sup>10</sup> of the receiver and cause an indeterminate output state. *Failsafe* defines the behavior of the receiving circuit under these fault conditions. The consequences of not including failsafe provisions are the detection of random noise as valid data or receiver oscillation; depending on the application, this could cause serious system response problems.

Experienced designers use a number of receiver design techniques to provide a predictable response from a receiver under these different fault conditions. With a differential input voltage within the transition regions, a small amount of positive feedback from the output stage of a receiver can cause the positive-going input threshold to be greater than the negative-going threshold creating hysteresis in the response. This feature prevents oscillation of the receiver output from differential noise below the hysteresis value. This failsafe feature does not force the output to a predetermined state but keeps in the last one before entering the transition region. Due to the sensitive thresholds and high signaling rates of LVDS and M-LVDS receivers, large amounts of hysteresis voltage is neither possible nor desirable. The data sheet for a receiver generally specifies the input hysteresis voltage in the electrical tables.

If the fault condition results in a high resistance or open circuit between the receiver inputs (such as a disconnected cable), most differential receivers from TI offer an open-circuit failsafe feature. This technique connects high-value internal resistors to pull the receiver inputs to a valid input voltage when the inputs are not connected to anything else. Data sheets specify open-circuit failsafe in the feature bullets, function tables, or equivalent input schematics of the data sheet.

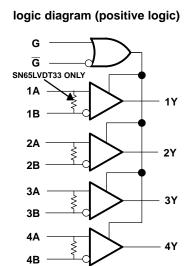

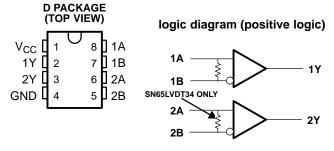

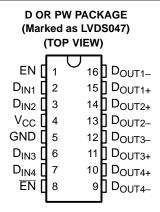

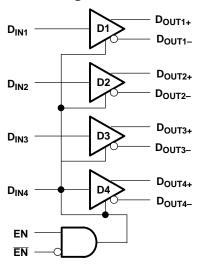

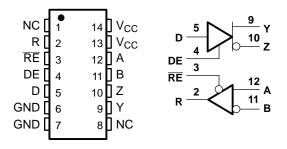

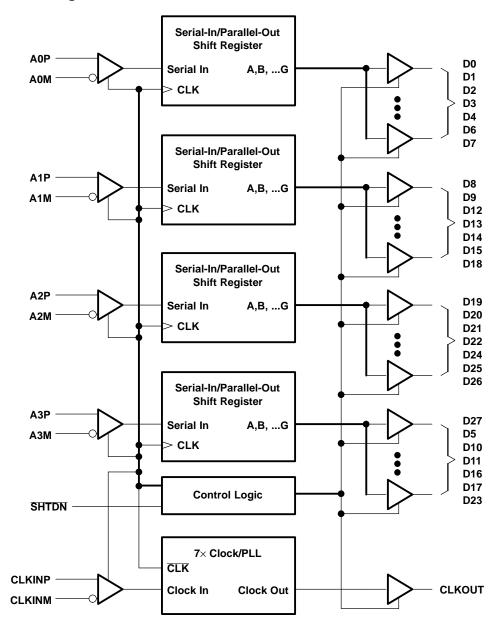

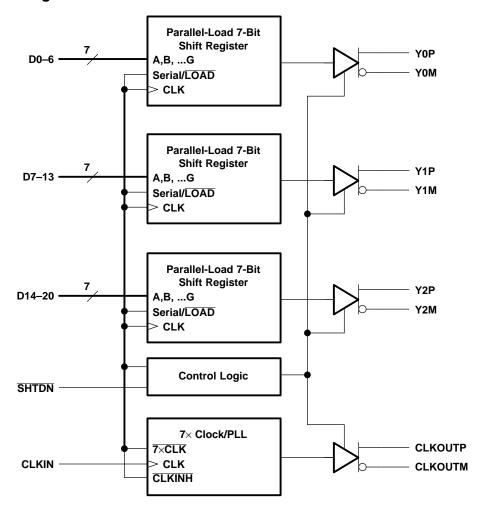

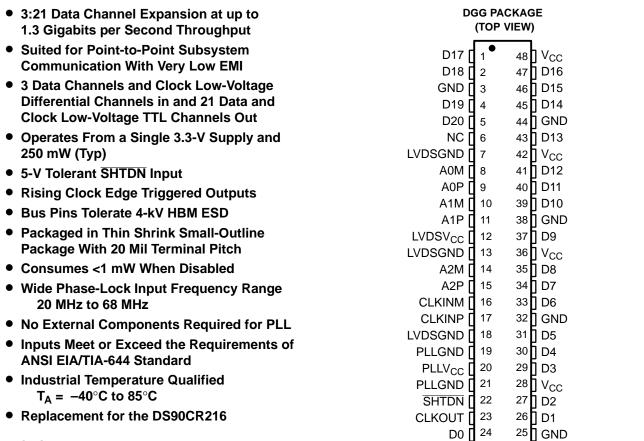

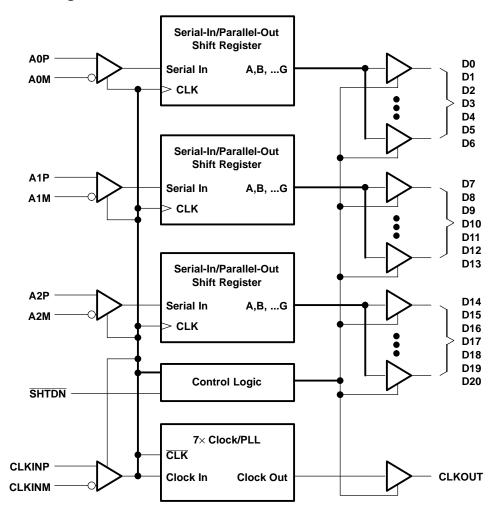

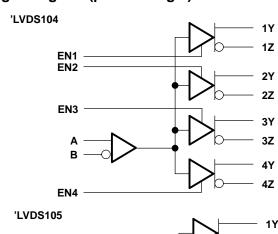

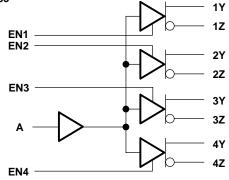

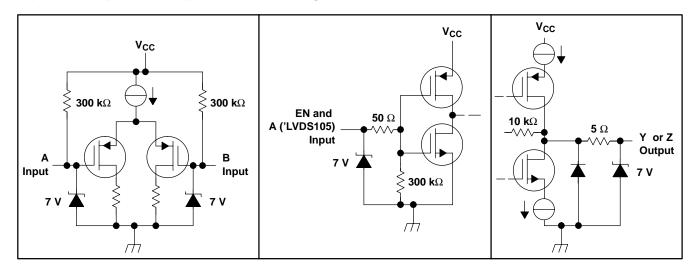

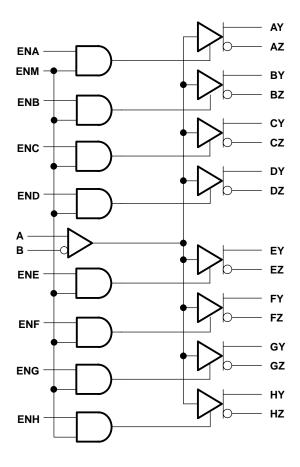

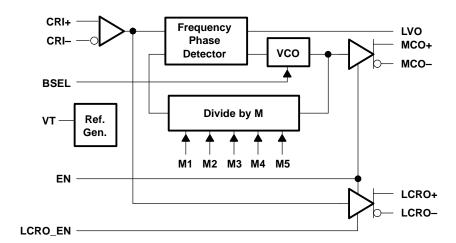

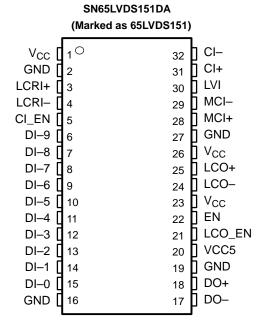

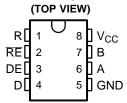

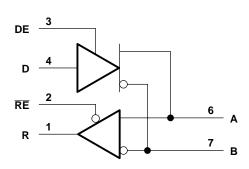

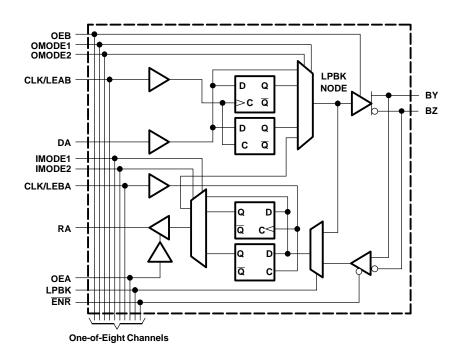

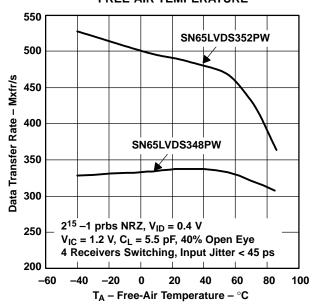

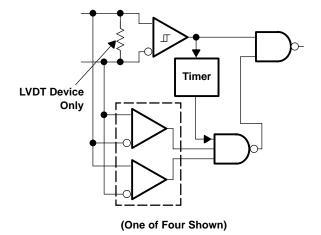

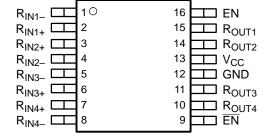

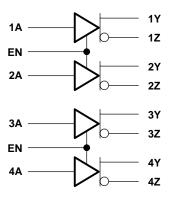

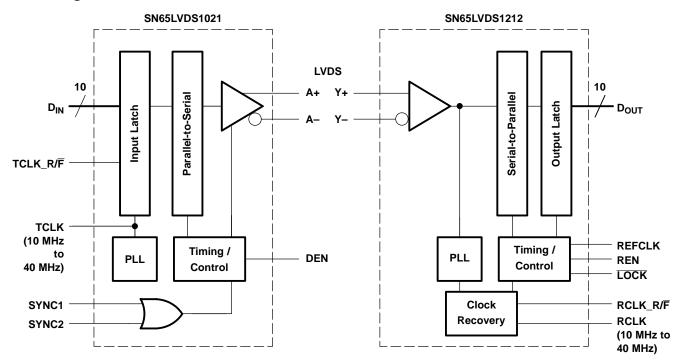

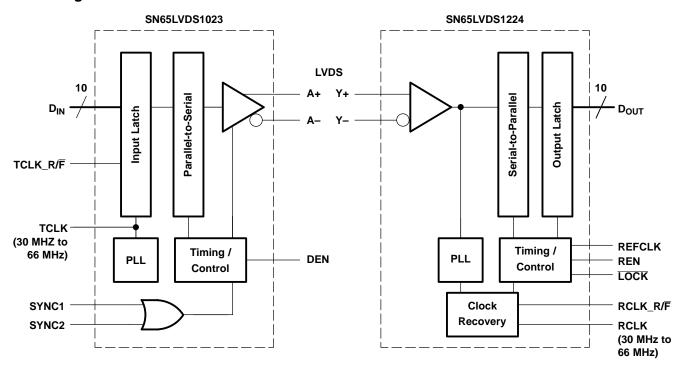

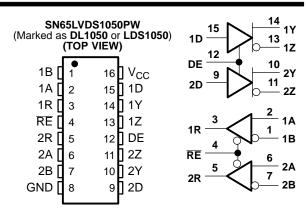

The Type-2 receivers specified in the TIA/EIA-899 M-LVDS standard provide another means of failsafe response. The standard requires the Type-2 receiver to have a differential input voltage threshold offset from zero such that even shorted lines (0 V differential) provide a valid bus and receiver output state. Offset of the threshold does subtract from the noise margin and adds pulse distortion (jitter) over Type-1 receivers with thresholds near zero volts. Designers can use Type-2 receivers in parallel with Type-1 receivers to detect loss of input signal and gate the Type-1 receiver output.