#### Gerardo Leyva-Hernandez

TPLD™ devices need a serial peripheral interface (SPI) or inter-integrated circuit (I2C) interface to be configured temporary or permanently. Moreover, TPLD801 and TPLD1201 devices need a general purpose input (GPI) line as well, which means that five general-purpose input/output (GPIO) total (IO5, IO4, IO2, IO1 and GPI) must be used for configuration. In some cases, the user prefers to install the TPLD device in one's own system specially in the development phase of a given project.

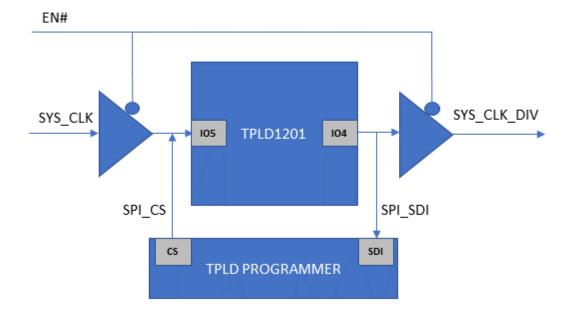

Because the number of general purpose input/outputs (GPIOs) are limited, a method to temporarily program the device using SPI can be possible by installing tri-state buffers in the lines that are going to be used for temporary programming and also used as GPIOs in the system. In this way, isolation can be generated when the programming lines are needed to update the TPLD functionality. Figure 1 illustrates this concept.

Figure 1. TPLD In-system Developing Block Diagram

#### **Testing the Prototype**

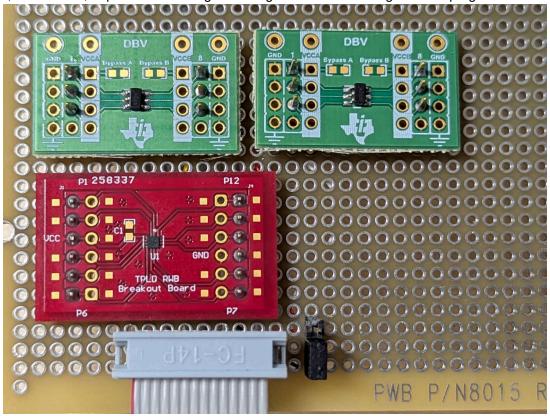

Figure 2 shows a developing system including some TI SN74LVC1G125 tri-state buffers (top), the TPLD1201 (middle), a jumper and a programming port (bottom). The jumper is going to be used to select either the programmer lines or the external signals that are being used by the TPLD GPIOs in the current system. To reach the TPLD pins that are needed to program the device, the customer must install pin headers or a double-row connectors, for instance, to provide the configuration signals that are coming from the programmer.

Figure 2. TPLD In-System Developing Prototype Example

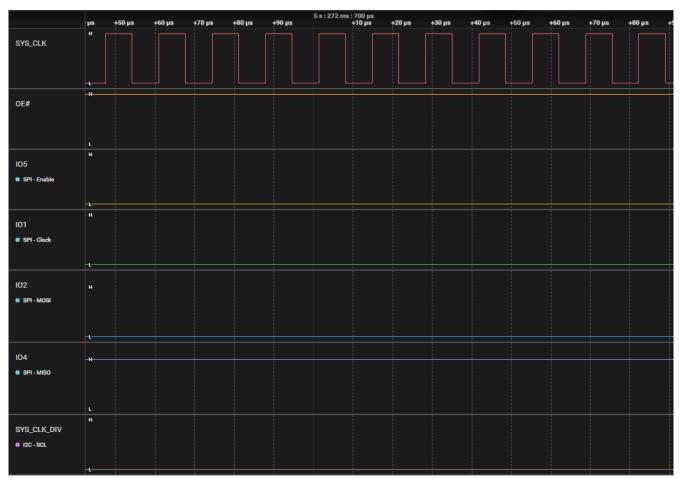

Suppose the TPLD is going to divide by two an input frequency. In this case, the input signal SYS\_CLK is active all the time and attached to a tri-state buffer input. Meanwhile TPLD GPIO5 is tied to the tri-state buffer output. Figure 3 shows that SYS\_CLK is running all the time but is not able to reach GPIO5 because the tri-state enable (OE#) is deasserted high.

Figure 3. TPLD Unprogrammed

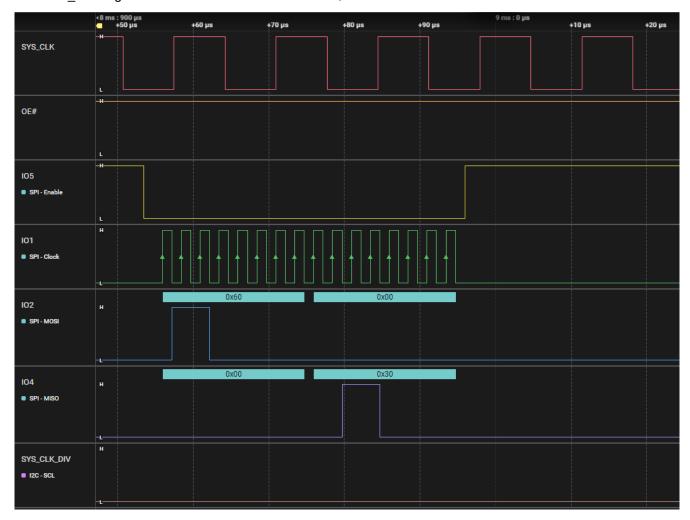

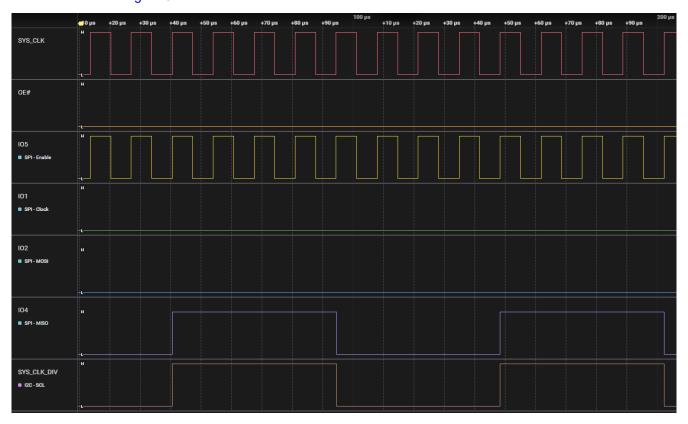

Figure 4 shows that the TPLD is being programmed through the SPI interface using the same OE# configuration. The SYS\_CLK signal is active but isolated from GPIO5, but the SPI CS line.

**Figure 4. TPLD During Programming**

www.ti.com Trademarks

Once the device is programmed, OE# can be grounded to activate the tri-state buffers so the external clock is reaching IO5 and the clock output (CLK\_SYS divided by 2) is present in IO4 and also at the output tri-state buffer as shown in Figure 5.

Figure 5. TPLD After Programming

## Conclusion

It is possible to make changes to or add features to a system with TPLD devices using external tri-states buffers to isolate the device during the upgrade of its internal configuration. The number of such buffers depends on how many GPIOs must be used both as GPIO and as configuration pins as well. Finally, it is important to remember that the method described above can not be applied to GPI because it also has an alternative function as +8V VPP, a voltage that is at the top of the maximum 5V typically accepted by tri-state buffers.

# **Trademarks**

TPLD™ is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated