# HART-Enabled Transmitter Based on an Evaluation Module Design

Joseph Wu

#### **ABSTRACT**

This application note describes using the AFE882H1 in an evaluation module (EVM) to construct a HART<sup>®</sup>-enabled field transmitter for 4-20mA loop instrumentation. HART (Highway Addressable Remote Transducer) enables two-way digital communication across the current loop at the same time as transmitting the value of a primary process variable. First, a brief introduction to 4-20mA loops and the HART protocol is presented. The AFE882H1 is then introduced as an ultra-low-power, 16-bit digital-to-analog converter (DAC) combined with a HART modem. This device also has an on-board analog-to-digital converter (ADC) and integrated diagnostic sensors for system monitoring. The EVM used for this device is set up as a loop transmitter that sets the current in a 4-20mA loop. This EVM is coupled with a digital back-end board that connects with an MSP-EXP430FR5969 LaunchPad™ as the controller for the HART communications. Testing for this transmitter for HART registration is also presented. The physical layer test results for the waveform are described and the data link layer (DLL) test results for the HART signaling and timing are described. Application layer tests for HART universal commands (UAL) and commonly-implemented commands (CAL) are also described.

## **Table of Contents**

| 1 Introduction                           |                |

|------------------------------------------|----------------|

| 1.1 The 4-20mA Loop                      | <mark>2</mark> |

| 1.2 The HART Protocol                    | 2              |

| 2 AFE882H1 EVM-Based HART Transmitter    | 5              |

| 2.1 AFE882H1 HART Modem                  |                |

| 2.2 AFE882H1 Evaluation Module           | 6              |

| 2.3 HART Transmitter Construction        | <mark>7</mark> |

| 3 HART Testing and Registration          | 15             |

| 3.1 HART History and the FieldComm Group |                |

| 3.2 HART Testing Overview                | 15             |

| 3.3 HART Test Equipment                  | 16             |

| 3.4 HART Physical Layer Testing          |                |

| 3.5 Data Link Layer Tests                | 29             |

| 3.6 Universal Command Tests              | 33             |

| 3.7 Common-Practice Command Tests        | 34             |

| 3.8 Device Specific Command Tests        | 36             |

| 3.9 HART Protocol Test Submission        |                |

| 3.10 HART Registration                   | 37             |

| 4 Summary                                | 38             |

| 5 Acknowledgments                        | 38             |

| 6 References                             | 38             |

#### **Trademarks**

LaunchPad<sup>™</sup> is a trademark of Texas Instruments. HART<sup>®</sup> is a registered trademark of FieldComm Group, Inc. Linux<sup>®</sup> is a registered trademark of Linus Torvalds. All trademarks are the property of their respective owners. Introduction www.ti.com

## 1 Introduction

#### 1.1 The 4-20mA Loop

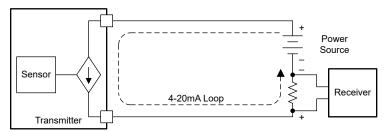

Understanding the 4-20mA loop is essential to explaining how HART is implemented in a field transmitter. The 4-20mA loop is a standard signaling method often used in factory automation and control to transmit information on a current loop. A sensor at a remote location measures a process variable and sets the current through the loop to indicate the measurement value. Figure 1-1 shows basic diagram of the loop.

Figure 1-1. Components of the 4-20mA Loop

The 4-20mA loop has four basic components. The first component is the wired path of the loop. Each transmitter operates on a separate circuit and a receiver measures the current in the path across a resistor. The wired loop is simple, durable, and easy to debug. This circuit is robust against electrical noise, making the current loop reliable for long-distance transmissions. The 4-20mA loop can be extended to 500 meters or longer. The wiring is also cost-effective and already commonly exists in many factory automation and control systems.

Second, the loop has a transmitter with a sensor used in process control. The sensor measures a parameter such as pressure, temperature, flow, or any other input for an industrial process or factory floor. The transmitter converts the measurement into the current value in the loop. For example, a transmitter measures the temperature of an oven from between 100°C to 500°C. In the 4-20mA loop, 4mA is used as the minimum value of the measurement and 20mA is used as the maximum value of the measurement. In that case, 4mA translates to 100°C and 20mA translates to 500°C. All measurements are linearly converted to this current value. In some systems, loop currents under 4mA and currents over 20mA can be used to indicate some error from the transmitter. For transmitters compliant to the NAMUR (User Association of Automation Technology in Process Industries) NE 43 recommendation, currents below 3.6mA or above 21mA are interpreted as a sensor fault. For designers of these systems, noise, resolution, and linearity are all important parameters for transmitter design.

Next, the loop has a power supply capable of sourcing at least 20mA. If NAMUR fault levels are supported by the transmitter, then higher levels of current are needed to indicate an error. The power supply is often a standard voltage of 24V. However, voltages of 36V, 15V, 12V or other voltages are used depending on the system. This power supply sends current through the loop and often also powers the transmitter.

Finally, there is a receiver that measures the current on the loop. The receiver measures the voltage across a series resistance. The current is calculated and converted to the *primary variable*. A load resistance of typically  $250\Omega$  is measured with an ADC to convert the primary variable back to the measured result from the transmitter.

## 1.2 The HART Protocol

HART is a backwards-compatible enhancement to 4-20mA instrumentation that allows two-way communication with smart, microprocessor-based field devices.

The HART frequency shift keyed (FSK) signal is superimposed onto a 4-20mA loop current and modulated for two-way digital communications. This is important because 4-20mA loops are already a well-adopted standard in factory automation and control. The fact that this technology is backwards compatible and can be used with already-existing infrastructure means that this is easy to adopt and cost effective.

HART is a standardized communication protocol, where the controller sends commands, and a field transmitter returns standardized responses. The application layer data received from commands communicates device status and diagnostics. Process data can be sent to include the data's floating-point digital values, the engineering units of the primary variable, and other information about the process the device is measuring.

www.ti.com Introduction

There are several different versions of the HART protocol. This application note discusses only the basic HART FSK signal in a field transmitter on a 4-20mA loop. For more in-depth information about the HART protocol see *A Basic Guide to the HART Protocol*.

#### 1.2.1 Adding HART to the 4-20mA Loop

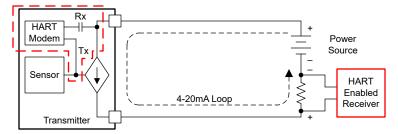

Starting with the original diagram for the 4-20mA loop in Figure 1-1, HART can be added to the transmitter and receiver. HART communication uses the original 4-20mA loop and adds a two-way digital signal to the loop using HART modems. Again, this backwards compatibility makes HART any easy add-on to existing infrastructure. Figure 1-2 shows how HART is added to the basic 4-20mA loop.

Figure 1-2. Adding HART to the 4-20mA Loop

When the HART-enabled receiver sends a command through the loop, the FSK signal is capacitively coupled into the HART modem in the field transmitter. The command is interpreted by the transmitter and the FSK response is superimposed to the current in the loop. The magnitude of current in the loop still represents the sensor measurement. The receiver uses a low-pass filter to measure the voltage across the resistor and the receiver uses a band-pass filter to decode the FSK signal.

With the FSK superimposed on the current in the loop, two-way communications can be achieved with both the field transmitter and the receiver. HART is a command-response protocol, where a host sends commands and the field transmitter returns standardized responses.

## 1.2.2 HART FSK

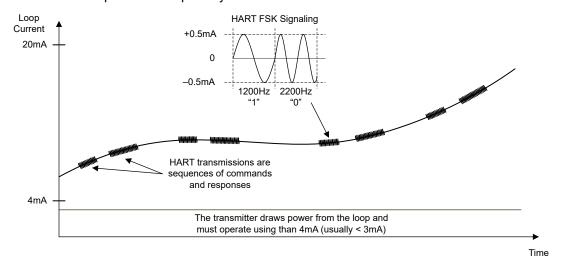

HART communication uses an FSK signal to create digital bits in the communication. The modem modulates two different frequencies for bits that become the 0 or 1 in the digital communications. This digital communication is similar to UART in byte structure using 8 data bits, odd parity, and 1 stop bit. Figure 1-3 shows a representation of the instantaneous current in the loop with a HART modulated signal. This HART signal is superimposed onto the 4-20mA current that represents the primary variable.

Figure 1-3. The HART FSK Modulated Onto the 4-20mA Current Loop

Introduction www.ti.com

Transmitters often operate on the loop power. Because the loop's zero scale is 4mA and currents below 3.6mA represent errors, the transmitter must operate with a maximum current budget of 3mA. The current budget is shown in the shaded section at the bottom of Figure 1-3.

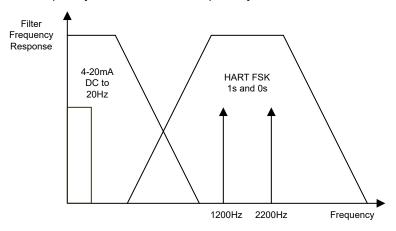

Bits for HART transmissions are represented as two FSK signals. Different frequencies represent 1s and 0s. A 1200Hz signal is a digital 1 and a 2200Hz signal is a digital 0. The data is sent at 1200 baud so each bit is 833µs. The primary variable is sent as the current in the loop. This current operates at a low frequency below 20Hz. Figure 1-4 shows the frequency bands used for the primary variable and the HART FSK frequencies.

Figure 1-4. The Primary Variable and HART Frequency Bands the 4-20mA Current Loop

Because the primary variable and the HART signal share the same transmission, the signals must be filtered to be received. The frequency content of the primary variable and the HART signal are shown by the shaded area and the two arrows.

In the HART-enabled receiver, the primary variable is read using a low-pass filter to measure the voltage across a resistor. This signal, represented as the shaded area of the figure, is generally under 20Hz so the low-pass filter has a cutoff frequency of about 25Hz. The HART transmits at a higher frequency, with the FSK bits at 1200Hz and 2200Hz. This HART signal is received using a band-pass filter that typically operates from 500Hz to 10kHz.

## 2 AFE882H1 EVM-Based HART Transmitter

The HART transmitter is constructed from a new front-end EVM of the AFE882H1. The AFE882H1 is a HART modem combined with a voltage output DAC. The EVM is set up as a field transmitter connected to a 24V supply, and the AFE882H1 sets the loop current through a voltage-to-current stage set up on the EVM. The EVM is independently controlled from a digital back-end board connected to an MSP430FR5969 LaunchPad. A basic HART stack is programmed into the LaunchPad.

## 2.1 AFE882H1 HART Modem

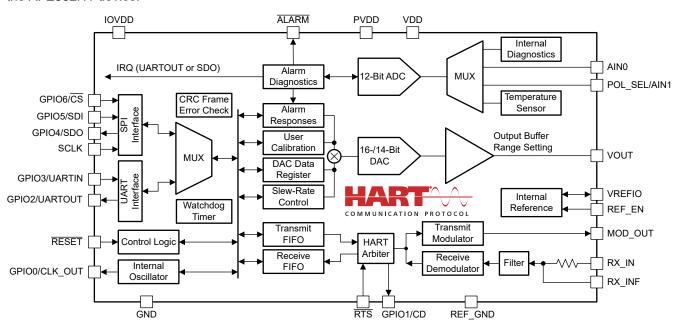

The device at the center of the HART-enabled transmitter is the AFE882H1. Figure 2-1 shows a block diagram of the AFE882H1 device.

Figure 2-1. AFE882H1 Block Diagram

The block diagram shows many of the features of the device. The AFE882H1 has a 16-bit voltage output DAC used to set the loop current and has an integrated HART modem. The DAC voltage output has a range from 0V to 2.5V. The DAC has user calibration that can adjust for offset and gain error. The DAC also has slew rate control that can slow DAC output transitions. The slew rate control can be used to help shape the output signal for HART testing.

The device also has an internal, 12-bit, multiplexed ADC. ADC measurements of internal nodes of the device can be monitored for programmable alarms for functional safety. An internal precision reference can be used for both the DAC and ADC.

SPI or UART communication can be used to program the device, or a combination of the two can be used for the HART protocol. The device has optional cyclic redundancy check (CRC) for error checking communications and a watchdog timer verify communication connections.

#### 2.2 AFE882H1 Evaluation Module

The AFE882H1 front-end (FE) EVM is constructed as a field transmitter. The EVM uses a digital back-end board (DAC-FT-DBE) that connects to USB for control. The prototype versions of the two boards are shown in Figure 2-2.

Figure 2-2. AFE882H1 Evaluation Module with an FTDI Digital-Back-End Board

In the normal evaluation configuration, the board on the left is the DBE controller board. This board has a USB micro connection for computer control using a PC-based GUI. The DBE uses an FT4232H as the bridge between the USB and the digital communication with the AFE882H1. A 2x8 100mil connector joins the DBE board with the AFE882H1 FE EVM board.

The AFE882H1-FE-EVM board is shown on the right side of the figure. The board is constructed as a transmitter for a 4-20mA loop. The J6 terminal block on the right side board connects to an external 24V loop power supply. The current in the loop is set based on the DAC voltage output of the AFE882H1. When connected to the PC, the GUI sets the DAC output voltage and controls the current in the loop.

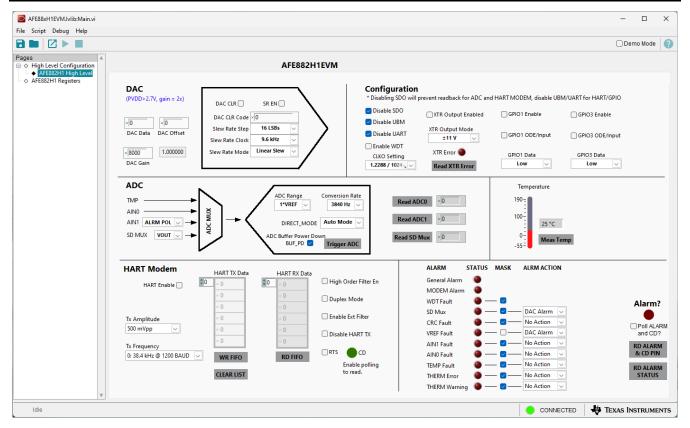

For this EVM, the board can be controlled by a GUI that can set the configuration of the device. The AFE882H1EVM GUI window is shown in Figure 2-3. The GUI is compatible with the AFE882H1-FE-EVM when connected to the DAC-FT-DBE.

Figure 2-3. AFE882H1EVM GUI Window

#### 2.3 HART Transmitter Construction

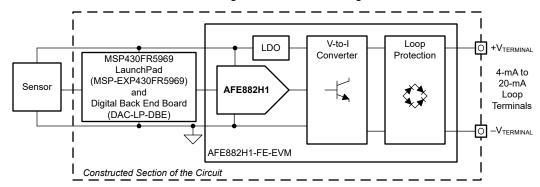

Using the AFE882H1-FE-EVM, a HART transmitter can be constructed using a TI microprocessor with a LaunchPad connection. The DBE board from Figure 2-2 is replaced with a DBE board with a LaunchPad connector footprint (LP-DBE board). Figure 2-4 shows a MSP-EXP430FR5969 LaunchPad with a LP-DBE connector board. The LaunchPad is programmed with a basic stack used to control the loop current and respond to HART communication.

Figure 2-4. MSP-EXP430FR5969 LaunchPad with a LP-DBE Connector Board

Figure 2-5 shows the AFE882H1 HART block diagram transmitter design.

Figure 2-5. Block Diagram of a 2-wire Transmitter Design Using an AFE882H1 Evaluation Module and a Digital-Back-End Board

The terminals connected to the loop are shown on the right side of the block diagram. This connection to the loop powers the entire transmitter. A bridge rectifier at the input protects against reverse connection to the loop. The rectified loop voltage powers a start-up circuit that provides power to a low-dropout regulator (LDO), that in turn powers the AFE882H1. The LDO powers the remainder of the circuit including a LaunchPad programmed with a HART stack.

HART communications are translated with the AFE882H1 HART modem. The device receives the HART signal through a capacitive coupled connection to the positive terminal side after the loop protection to the board. The HART signal is transmitted to the loop through the voltage-to-current (V-to-I) stage of the board.

Note that this transmitter board does not have a sensor to transmit data. The loop current is nominally set to 4mA as an output, except for specific HART tests. The main purpose of this board is to test the HART communication functionality of the AFE882H1.

#### 2.3.1 Detailed Schematic

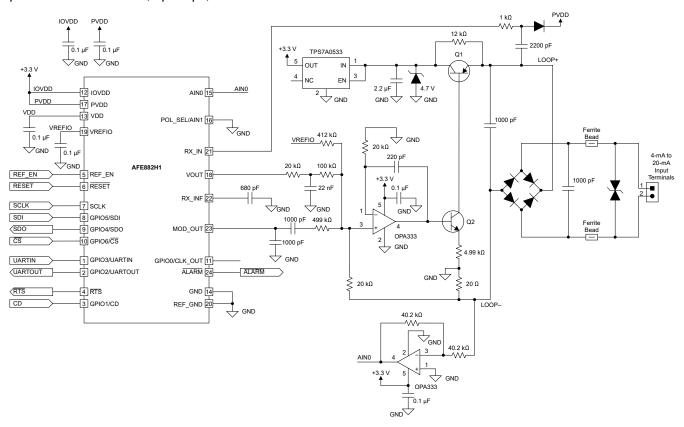

Figure 2-6 shows a schematic of the AFE882H1-FE-EVM board. The schematic shows the 24V loop power connection on the right side of the figure. Input protection is placed between the input terminals and the transmitter circuit. The positive loop connects to a startup circuit for the board and powers an LDO. This LDO powers the AFE device, op-amps, and V-to-I control.

Figure 2-6. 2-Wire Transmitter Design Using an AFE882H1 Circuit Schematic

The AFE882H1 controls the loop current through the V-to-I section. The DAC voltage has an output range from 0V to 2.5V. The output is sent through a V-to-I converter stage using an OPA333 and an NPN bipolar junction transistor (BJT) that controls the loop current. In the constructed transmitter, the digital signals of the AFE882H1 are driven by an MSP430FR5969 LaunchPad. The DAC-LP-DBE bridges the digital signals between the AFE882H1-FE-EVM and the LaunchPad and also powers the LaunchPad from an LDO sourced by the loop

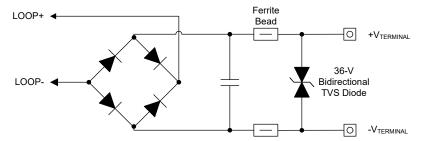

#### 2.3.1.1 Input Protection

Figure 2-7 shows input protection for the board starting with a TVS diode to prevent damage from over-voltage events. Ferrite beads and input capacitance also help reduce any high-frequency transients seen at the inputs. An input rectifier allows for operation when miswiring the positive and negative input, protecting the board.

Figure 2-7. Input Protection Circuit at the Input Terminals of the Board

When voltage is applied to the input terminals, the power is delivered to the circuit through LOOP+ and LOOP-setting the current in the 4-20mA loop.

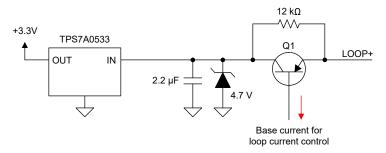

## 2.3.1.2 Start Up With Low-Dropout Regulator

The schematic in Figure 2-8 shows a simplified startup circuit of the HART transmitter.

Figure 2-8. Transmitter Board Startup Circuit

When power is applied to the input terminals, voltage pulls up on LOOP+ to start up the circuit. Before Q1 turns on, the  $12k\Omega$  resistor supplies current to the 4.7V Zener diode. This voltage starts up the TPS7A0533 3.3V LDO. This LDO supplies the power to the AFE882H1 and OPA333 devices on the FE EVM board. As power is supplied to the AFE882H1, the current control of the EVM pulls base current from Q1 to set the current in the loop.

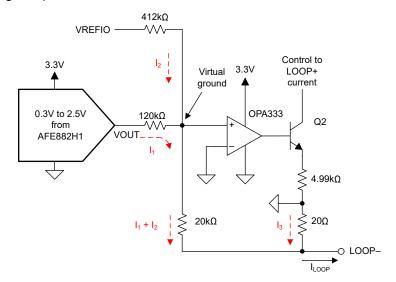

#### 2.3.1.3 Voltage-to-Current Stage

Figure 2-9 shows a simplified schematic of the V-to-I stage of the transmitter. This stage sets the current of the loop based on the voltage output of the DAC.

Figure 2-9. Voltage-to-Current Converter Stage for the Transmitter Board

In this circuit, the DAC voltage is set across  $120k\Omega$  of equivalent resistance. The voltage at the opposite end of the  $120k\Omega$  is a virtual ground set by the feedback of the OPA333. The output of the OPA333 drives Q2 which sets the loop current.

The current flowing from VOUT,  $I_1$  combines with the current of  $I_2$ .  $I_2$  is sourced from VREFIO across a 412k $\Omega$  resistor. This current contributes an offset to set the minimum current in the loop. The currents of  $I_1$  and  $I_2$  combine to set the voltage across a 20k $\Omega$  resistor below ground at LOOP—. The following equations show the voltage at LOOP—.

$$I_1 = VOUT / 120k\Omega \tag{1}$$

$$I_2 = VREFIO / 412k\Omega$$

(2)

$$-V_{LOOP-} = (I_1 + I_2) \times 20k\Omega \tag{3}$$

$I_1$  and  $I_2$  are pulled from ground to LOOP–. Current through the 20k $\Omega$  resistor is amplified 1000:1 in the 20 $\Omega$  resistor shown in  $I_3$ .

$$I_3 = -V_{LOOP} / 20\Omega = (I_1 + I_2) \times 20k\Omega / 20\Omega = 1000 \times (I_1 + I_2)$$

(4)

The loop current is the sum of the currents through these paths and can be calculated as a function of I<sub>1</sub> and I<sub>2</sub>.

$$I_{LOOP-} = I_1 + I_2 + I_3 = 1001 \times (I_1 + I_2)$$

(5)

# 2.3.1.4 Voltage-to-Current Calculation

As previously calculated in Equation 5, the loop current is shown as a sum of the current through the paths to LOOP—. This total current is a function of the DAC code and the reference voltage. With a static reference voltage, the DAC code sets the magnitude of the current through the loop.

$$I_{LOOP} = 1001 \times [(VOUT / 120k\Omega) + (1.25V / 412k\Omega)]$$

(6)

$$I_{LOOP} = 1001 \times \{ [(DAC\_CODE / 2^{16}) \times 2.5V] + (1.25V / 412k\Omega) \}$$

(7)

Table 2-1 shows different DAC code values and how the values map to the loop current in milliamps. Loop currents 3.375mA and 21.75mA are chosen as the sensor error indicator levels.

Table 2-1. DAC Code Values Converted to Voltage Output and Loop Current Setting

| OUTPUT CONDITION   | DAC CODE | DAC OUTPUT (V) | LOOP CURRENT (mA) |

|--------------------|----------|----------------|-------------------|

| DAC minimum        | 0x0000   | 0              | 3.037             |

| Error low          | 0x0426   | 0.04051        | 3.375             |

| In-range minimum   | 0x0BD2   | 0.1154         | 4                 |

| In-range mid-scale | 0x6E07   | 1.0745         | 12                |

| In-range maximum   | 0xD03C   | 2.0335         | 20                |

| Error high         | 0xE5B7   | 2.2433         | 21.75             |

| DAC maximum        | 0xFFFF   | 2.5            | 23.891            |

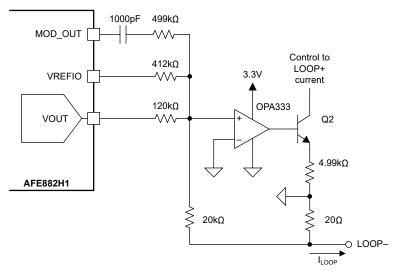

## 2.3.1.5 HART Signal Transmission

The HART signal is added to the loop current through superposition of a summing junction from the OPA333 shown in Figure 2-10.

Figure 2-10. Addition of the HART Signal From MOD\_OUT to the V-to-I Stage

The MOD\_OUT signal is nominally  $500 \text{mV}_{PP}$ . This voltage is summed into the loop current through a DC blocking 1000 pF capacitor and a  $499 \text{k}\Omega$  resistor.  $499 \text{k}\Omega$  is a standard 1% resistor value.

Similar to the VOUT calculation of the V-to-I stage, the HART current is calculated to be  $1.002mA_{PP}$ , where the HART signal amplitude is  $1mA_{PP}$ .

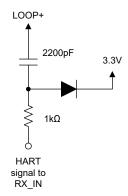

#### 2.3.1.6 HART Input Protection

The HART input to the AFE882H1 is capacitively coupled to LOOP+ which operates at a voltage near to the positive supply. With higher voltages of operation, the HART RX\_IN pin requires protection from these voltages at startup. Figure 2-11 shows a clamp used in the circuit to prevent the pin from being exposed to high loop voltages.

Figure 2-11. RX\_IN Clamp Circuit for Over-Voltage Protection

To sense the HART signal, the RX\_IN pin is connected to LOOP+ through a DC blocking capacitor, which keeps the RX\_IN pin at a low voltage. However at startup, LOOP+ goes to a high voltage and the capacitor starts at 0V. This pulls the RX\_IN pin up to a high voltage which quickly drops from the low capacitance.

The clamp protects the HART input pin. A series  $1k\Omega$  resistor limits any current going into the pin while a diode clamps the resistor to 3.3V.

#### 2.3.1.7 HART Transmitter Board

Figure 2-12 shows picture of the AFE882H1 HART transmitter design. Loop power is applied to the board through a terminal at the right side of the board. In series with this connection is a  $500\Omega$  resistor. Modems attached to a HART test system can be attached to across the input of the transmitter. The transmitter and resistor then connect to a power supply that typically runs at 24V.

Figure 2-12. HART Transmitter Circuit With AFE882H1-FE-EVM, DAC-LP-DBE, and MSP430 LaunchPad

#### 2.3.1.8 Current Consumption

Table 2-2 shows the current consumption of the various components on the board. The AFE882H1 in particular operates on very low power. The power savings is particularly important because the transmitter must be able to operate with less than 3mA of current, and power savings for this portion can be applied to use in the sensor.

**Table 2-2. Design Components Current Consumption**

| DEVICE     | DESCRIPTION           | TYPICAL CURRENT (μA)  |

|------------|-----------------------|-----------------------|

| TPS7A0533  | LDO                   | 4                     |

| AFE882H1   | 16-bit DAC            | 180                   |

| OPA333 (2) | Operational amplifier | 17 (each)             |

| MSP430     | Microcontroller       | Dependent on firmware |

#### 2.3.2 HART Protocol Stack

As a HART modem, AFE882H1 organizes the physical layer of the transmissions. The physical layer refers to the HART FSK signal superimposed on the 4-20mA loop. The AFE882H1 translates this signal for the microprocessor to UART or SPI. However, the firmware programmed into the microprocessor sets the framing for communication or interprets the HART commands. This firmware is the known as HART protocol stack.

The HART stack manages the communication between devices in the of the protocol. The firmware checks that messages are delivered correctly and handles error checking and correction. The stack also is responsible for the correct responses to application commands in the HART protocol.

For this design, the HART stack was written for the MSP430FR5969. This firmware for this transmitter was developed by Smart Embedded Systems (SES) of Pleasanton, CA. For more information about SES, see SES Services.

# 3 HART Testing and Registration

## 3.1 HART History and the FieldComm Group

HART was established by Rosemount Incorporated in the mid-1980s. This protocol is based on the Bell 202 modem communication standard. Rosemount is now a subsidiary of Emerson Electric Company.

Rosemount developed HART as a proprietary communication standard to add smart capability to field instruments. As this communication standard became popular, the standard developed into HART and became an open protocol. Since 2015, the HART protocol has been governed by the FieldComm Group. FieldComm maintains the protocol and oversees any changes or modifications.

HART compliant devices are also registered by the FieldComm Group. Registration is completed after testing the device for compliance to the protocol and a paid registration fee.

#### 3.2 HART Testing Overview

Previously, Figure 2-1 showed the block diagram of the AFE882H1 device. In the middle of the figure is the HART communication protocol logo. The logo indicates the device was designed into a transmitter in a HART-registered product.

To be HART registered, the device is first tested by the company that created the device. Test results are used to generate a report sent to the FieldComm Group with an application for registration. Test results include physical layer tests that verify the waveform, check the timing of the HART FSK carrier signal, and verify timing with some HART specific digital lines built into the HART modem. Additionally, there are many tests that verify the HART protocol to check that the device has the proper response to commands from a HART controller.

## 3.2.1 HART Protocol Specifications

Below is a list of HART protocol specifications. These specifications outline how HART devices respond to commands as well as describe how the physical layer of the protocol.

- HART Communication Protocol Specification (HCF SPEC-13 FCG TS20013)

- Token-Passing Data Link Layer Specification (HCF\_SPEC-81 FCG TS20081)

- Command Summary Specification (HCF\_SPEC-99 FCG TS20099)

- Universal Command Specification (HCF\_SPEC-127 FCG TS20127)

- Common Practice Command Specification (HCF\_SPEC-151 FCG TS20151)

These specifications can be viewed online at the FieldComm Group website. These specifications cannot be downloaded by non-member companies, but can be purchased as a bound book. Member companies can download electronic copies of the protocol specifications in a PDF. Companies purchase membership from the FieldComm Group.

## 3.2.2 HART Protocol Test Specifications

This is a list of HART protocol *test* specifications. The following documents describe the details of HART testing. The documents describe how the tests are constructed and what different test failures look like.

- FSK Physical Layer Test Specification (HCF\_TEST-2 FCG TT20002)

- Token-Passing Data Link Layer Test Specification (HCF TEST-1 FCG TT20001)

- Universal Command Test Specification (HCF TEST-3 FCG TT20003)

- Common Practice Command Test Specification (HCF\_TEST-4 FCG TT20004)

While the entire HART protocol specifications can be viewed online, only the *table of contents* of these test specifications can be viewed online at the FieldComm Group website. Non-member companies must purchase the bound books. Member companies can download electronic copies of the specifications in a PDF.

#### 3.2.3 Field Transmitter Device Testing

There are several different physical device types compatible with HART communication. Devices are categorized by impedance level. These devices can be high impedance devices such as current output, voltage inputs, or field, two-wire transmitter devices attached to 4-20mA loops. Other devices can be low impedance devices such as current inputs, voltage outputs, or actuators that must have an impedance of  $230\Omega$  to  $600\Omega$ within the HART frequency band of operation.

Each of these different physical device types require different tests and different test setups. This application note discusses the testing for a field transmitter device.

## 3.3 HART Test Equipment

Below are some of the equipment needed to run HART testing for your field transmitter.

- A test load resistor used in the loop. This is typically  $500\Omega$  depending on the particular test.

- An oscilloscope is required to observe the HART signals. The physical layer tests require the FSK to have a certain waveshape and magnitude, that have specific rise and fall times.

- A frequency counter is needed to observe the frequency of the FSK bits. In these tests, an oscilloscope is used to verify the frequency.

- A DC power source of approximately 40V maximum powers the loop.

- A signal generator is used for generate interference noise of different frequencies and amplitude to verify HART communications in presence of noise.

There are also a few specialized pieces of equipment required to run the HART physical layer tests. These devices are shown in Figure 3-1.

Figure 3-1. HART Test System Shown With an HCF\_TOOL-31, HCF\_TOOL-32, and an FSK Physical Test Interface

16

A HART test system is required for the HART protocol testing. While this system is mostly required for the data link layer and command tests, the test system can be used to generate the HART responses from the transmitter to view the specific FSK bits and responses. The HART test system is Linux® based, and runs tests with a set of commands designed by FieldComm. The HART test system requires two HART registered RS-232 modems.

The HCF\_TOOL-31 filter is needed for the physical layer tests. This filter is a passband Butterworth filter that passes the HART FSK digital signal. The filter has a 2<sup>nd</sup> order roll-off below 500Hz, 1st order roll-off above 10kHz, and a passband gain of 10. This filter passes the HART FSK signal but removes the lower frequencies of the primary variable and any noise from higher frequencies.

The HCF\_TOOL-32 filter is also required. This filter is a low-pass Butterworth filter with a 2<sup>nd</sup> order roll-off above 25Hz and a passband gain of 10. This low-pass filter passes the analog primary variable from a field transmitter and rejects the HART FSK signal and higher frequencies.

Finally, the FSK Physical Layer Test interface is used to increase and decrease the HART sinusoids from the HART test system in the transmission. This device is used to determine the sensitivity of the field transmitter for detecting the HART signal.

The HART test system, the HCF\_TOOL-31 filter, the HCF\_TOOL-32 filter, and the FSK Physical Layer Test interface can be purchased from FieldComm.

# 3.4 HART Physical Layer Testing

The HART physical layer tests are described in HCF TEST-2. This document defines the requirements for testing HART devices for compliance with the HART FSK Physical Layer Specification. These tests verify many different parameters of the HART communication.

- · Verify the bit rate and signal frequencies for the HART transmission.

- Verify that a carrier detect signal is sent within a minimum time after the start or stop of a HART transmission.

- Measure the low-pass primary variable signal to check that a carrier detect start or stop does not disrupt the transmission of the primary variable.

- · Check that the output noise is below a maximum level when the HART is not transmitting.

- Testing HART communications while cycling the primary variable between the minimum of 4mA and maximum of 20mA (analog rate of change test).

- Measure the HART device to verify high receive impedance over the frequency of the primary variable and HART frequency band.

- Test HART transmission in the presence of in-band and out-of-band sinusoidal noise.

- Check the carrier detect level to make sure a HART signal is detected when the signal is at the minimum amplitude, and not detected below a lower amplitude, while maintaining carrier detect timing.

As part of the physical layer of the HART protocol, these tests cover the timing and amplitude of the HART signal as generated by the AFE882H1 and with the surrounding circuitry. The following sections describe the HART physical layer tests and test setups.

#### 3.4.1 FSK Sinusoid Test

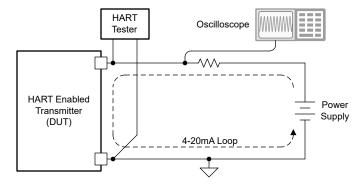

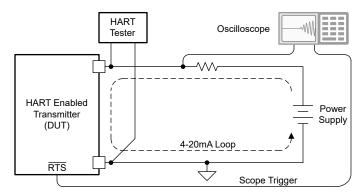

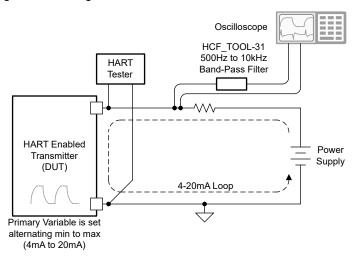

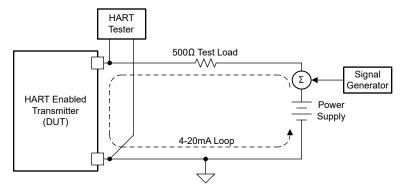

Figure 3-2 shows a block diagram of the HART FSK sinusoid test. Most HART tests require a similar setup with the transmitter as the device under test. The FSK sinusoid test verifies that the HART signal have the correct frequencies and wave shape for transmission.

Figure 3-2. HART FSK Sinusoid Test Block Diagram

A Keysight E36313A is used as the 24V power supply. The power supply powers the loop and the transmitter sets the current through the loop. A series resistor is used to measure the current through the loop, but also attaches to the HART test system through a modem.

For the HART FSK sinusoid test, an oscilloscope measures the HART transmitted signals. The HART tester sends commands and the oscilloscope plots the responses to find a series of 1s and 0s to measure the HART bits. A frequency counter can be used to measure the frequency of the FSK bits, but an oscilloscope can also be used to verify the timing.

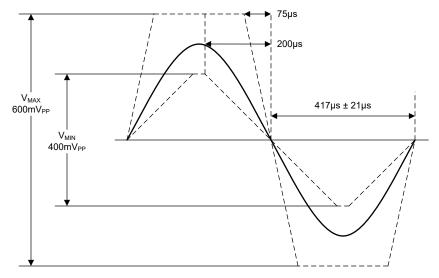

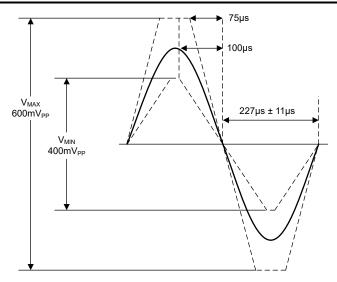

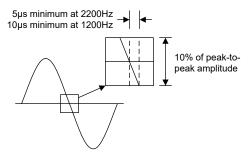

Figure 3-3 and Figure 3-4 define the tolerance of the HART FSK signals. As previously mentioned, the two FSK signals are 1200Hz and 2200Hz. However, there is some acceptable variation in the signal.

Figure 3-3. HART 1200Hz FSK Waveform Limits

18

Figure 3-4. HART 2200Hz FSK Waveform Limits

These measurements define the FSK frequency variation allowed, the minimum and maximum voltages, and the rise times needed for the HART signal. In addition to the waveform requirements the two FSK frequencies, there is a transition requirement for the waveform shown in Figure 3-5.

Figure 3-5. HART Sinusoidal Signaling Transition

These diagrams show the tolerance for amplitude of the HART signal, the frequency variation, and the rise time of the signals. To pass the tests, the HART sinusoid must fit within these trapezoidal windows shown in the figures.

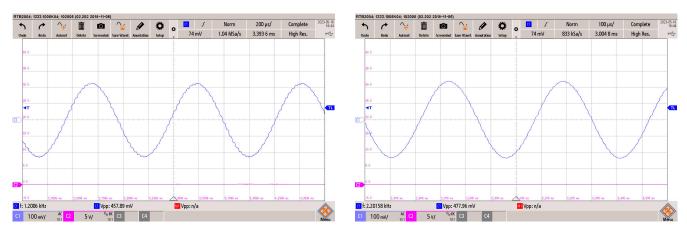

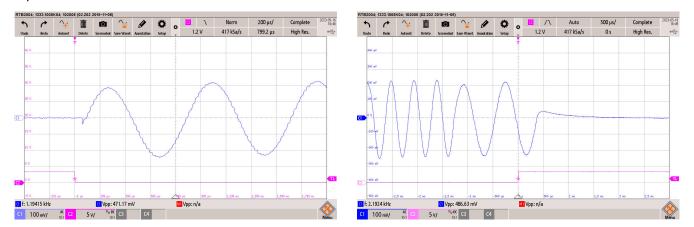

The waveforms are taken from the AFE882H1 transmitter test setup using an oscilloscope. Figure 3-6 shows the oscilloscope photos taken for the two HART FSK sinusoids and Table 3-1 shows the test data taken from the measurements.

Figure 3-6. FSK Sinusoid Test Oscilloscope Results

**Pass**

| Table 5-1. I SK Siliusolu Wavelollii lest Data |                    |                     |                     |                     |        |  |

|------------------------------------------------|--------------------|---------------------|---------------------|---------------------|--------|--|

| FSK FREQUENCY                                  | TEST               | MEASURED            | MINIMUM             | MAXIMUM             | RESULT |  |

| 1200Hz                                         | Frequency          | 1201Hz              | 1188Hz              | 1212Hz              | Pass   |  |

|                                                | Amplitude          | 458mV <sub>PP</sub> | 400mV <sub>PP</sub> | 600mV <sub>PP</sub> | Pass   |  |

|                                                | Waveform rise time | 130µs               | 80µs                | 200µs               | Pass   |  |

|                                                | Waveform fall time | 130µs               | 80µs                | 200µs               | Pass   |  |

| 2200Hz                                         | Frequency          | 2202Hz              | 2178Hz              | 2222Hz              | Pass   |  |

|                                                | Amplitude          | 478mV <sub>PP</sub> | 400mV <sub>PP</sub> | 600mV <sub>PP</sub> | Pass   |  |

|                                                | Waveform rise time | 80µs                | 75µs                | 200µs               | Pass   |  |

Table 3-1, FSK Sinusoid Waveform Test Data

While a  $250\Omega$  resistor is commonly used in 4-20mA loops, a  $500\Omega$  current sense resistor is required for this and the other physical layer tests.

75µs

200µs

80µs

#### 3.4.2 Carrier Start and Stop Time Tests

Waveform fall time

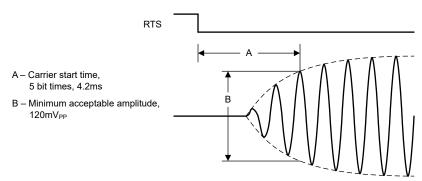

In addition to the FSK characteristics, the physical layer tests also measure the start and start times of the carrier from the transmitter. Figure 3-7 shows a figure of the carrier start and stop time test setup. When the microprocessor in the HART transmitter sends a transmission, the request-to-send (RTS) pin on the AFE882H1 is set low as a trigger to enable the modulator for the FSK. The modulator generates the sine-wave signals for the HART communication.

Figure 3-7. HART Carrier Start and Stop Time Tests Setup

When the active-low  $\overline{RTS}$  pin on the AFE882H1 is set low, the modulator is enabled and the HART sinusoid appears on the MOD\_OUT pin of the device. Part of the physical layer tests measure the time to enable the modulator when the  $\overline{RTS}$  signal is set low, and the time to disable the modulator when the  $\overline{RTS}$  signal is returned high.

In this setup, the RTS signal from the microprocessor triggers an oscilloscope to plot the enable and disable time for the HART signal. Figure 3-8 and Figure 3-9 show the required timing for the HART carrier start and stop tests.

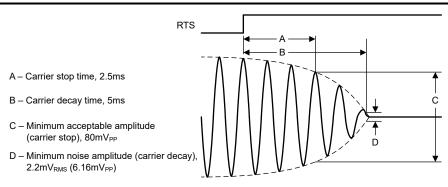

Figure 3-8. Carrier Start Timing

Figure 3-9. Carrier Stop Timing

For  $\overline{RTS}$  enable, the maximum amount of time allowed to start the modulator is 5 HART bit times or 4.2ms. This is the time for the sinusoid to reach the minimum amplitude of 120mV<sub>PP</sub>. For  $\overline{RTS}$  disable, the maximum carrier stop time is 2.5ms to verify that the carrier amplitude is below  $80\text{mV}_{PP}$ . There is a total of 5ms of allowable decay time. After this time period, the maximum noise amplitude from the HART signal is  $2.2\text{mV}_{RMS}$  (or about  $6.16\text{mV}_{PP}$ ). Figure 3-10 shows the oscilloscope plot for the HART carrier start and stop timing and Table 3-2 reports the measured data.

Figure 3-10. HART Carrier Start and Stop Time Test Oscilloscope Results

Table 3-2. FSK Sinusoid Start and Stop Time Test Results

| TEST               | MEASURED | MAXIMUM | RESULT |

|--------------------|----------|---------|--------|

| Carrier start time | 100µs    | 4.2ms   | Pass   |

| Carrier stop time  | 0.5ms    | 2.5ms   | Pass   |

| Carrier decay time | 2.0ms    | 5.0ms   | Pass   |

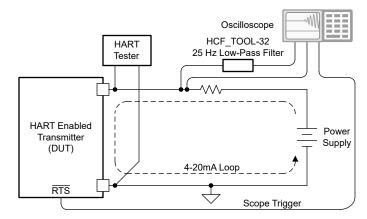

## 3.4.3 Carrier Start and Stop Transient Tests

The next test is the carrier start and stop transient measurements. The test setup in Figure 3-11 is similar to the previous test where the carrier start and stop are measured. In this test setup, an HCF\_TOOL-32 filter is measured by another channel of the oscilloscope. This low-pass filter removes the higher-frequency HART signal band and passes any signal below 25Hz. The filtered signal shows the current measurement of the primary variable. This test verifies that the HART transmission start and stop does not create any noise that interferes with the primary variable measurement.

Figure 3-11. HART Carrier Start and Stop Transient Test Setup

Figure 3-11 shows the oscilloscope plots of the HART signal while being enabled and disabled. Additionally, the oscilloscope measures the same signal filtered through the HCF\_TOOL-32. The HCF\_TOOL-32 is capacitively coupled to the resistive load. The low-pass filtered signal in blue shows the output noise amplitude of the transmitter. Here, the specification requires a peak amplitude of 100mV maximum. The transmitter maximum shows a 3.9mV<sub>PP</sub> noise amplitude for the transition noise. Table 3-3 reports the results of the scope measurements.

Figure 3-12. HART Carrier Start and Stop Time Transient Test Oscilloscope Results

Table 3-3. Carrier Start and Stop Measurement Results Filtered Through an HCF\_TOOL-32

| TEST                                    | MEASUREMENT         | MAXIMUM             | RESULT |

|-----------------------------------------|---------------------|---------------------|--------|

| Carrier start peak analog filter output | 3.9mV <sub>PP</sub> | 100mV <sub>PP</sub> | Pass   |

| Carrier stop peak analog filter output  | 3.5mV <sub>PP</sub> | 100mV <sub>PP</sub> | Pass   |

#### 3.4.4 Output Noise During Silence

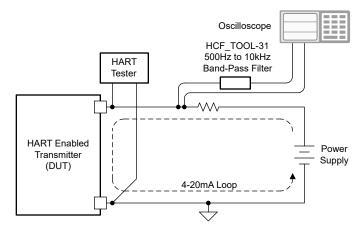

Similar to the previous test, this test measures the HART signal band through a filter. Here, the HCF\_TOOL-31 filter is used. This filter is a 500Hz to 10kHz bandpass filter that allows all of the in-band HART signal through. The test is devised to view the noise when the HART signal is inactive and verify there is no in-band noise that can be received as a HART signal in error. Figure 3-13 shows the test setup for the output noise during silence.

Figure 3-13. HART Output Noise During Silence Test Setup

Figure 3-14 shows the oscilloscope shot of the measurement of the output noise during silence. This shows the inactive HART signal at the top of the oscilloscope plot after the HART has been disabled. The middle trace in the plot shows the same signal filtered through the HCF\_TOOL-31, showing the in-band noise for the primary variable. The bottom trace of the oscilloscope plot is the RTS which is high indicating the HART is inactive. Table 3-4 shows the results of the noise measured during silence.

Figure 3-14. Output Noise During Silence Oscilloscope Test

**Table 3-4. Output Noise During Silence Test Results**

| TEST                                            | MEASUREMENT          | MAXIMUM              | RESULT |

|-------------------------------------------------|----------------------|----------------------|--------|

| Broadband noise without filter                  | 4.49mV <sub>PP</sub> | 138mV <sub>RMS</sub> | Pass   |

| In-band noise using HCF_TOOL-31 bandpass filter | 13.2mV <sub>PP</sub> | 22mV <sub>RMS</sub>  | Pass   |

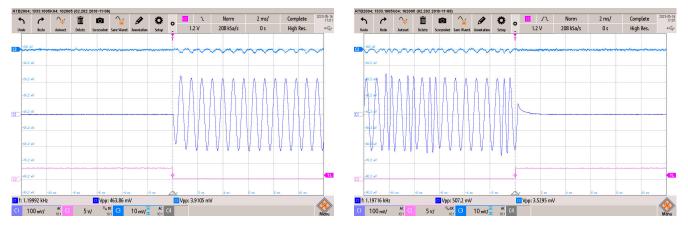

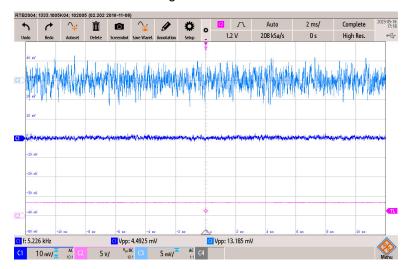

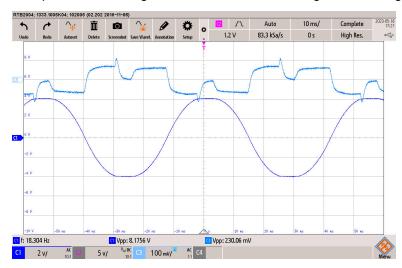

#### 3.4.5 Analog Rate of Change Test

The analog rate of change test shows how fast the primary variable can be changed from minimum to maximum value and back again. For this test, a special test mode is encoded in the device to cycle the output from 4mA to 20mA at a rate of about 18Hz. This test mode is enabled through switches on the transmitter board. In the transmitter, the AFE882H1 is set to the sinusoidal slew-rate mode so that the transitions from minimum to maximum approximate a sine-wave shape. The sinusoidal slew-rate mode maximizes the signal in the low-pass primary-variable band.

This signal is then filtered through a HCF\_TOOL-31 filter. This filter is a 500Hz to 10kHz bandpass filter that passes all of the in-band HART signal through. The test is devised to show that when the primary variable is changed, the transition does not cause any noise large enough to trigger a HART reception. Figure 3-15 shows the test setup for the analog rate of change test.

Figure 3-15. HART Analog Rate of Change Test Setup

Figure 3-16 shows a plot of the analog rate of change test. The bottom trace is the primary variable transitioning back and forth from minimum to maximum. This is a transition of 4mA to 20mA. Across a  $500\Omega$  resistor, this is an 8V transition. Table 3-5 reports the resulting measurements of the analog rate of change test.

Figure 3-16. Analog Rate of Change Test Oscilloscope Results

The top trace shows the same signal filtered through an HCF\_TOOL-31. This signal must be less than 150mV<sub>PEAK</sub>. For this test, the 230mV<sub>PP</sub> result is the equivalent to 115mV<sub>PEAK</sub>, and the device passes this test.

Table 3-5. HART Analog Rate of Change Measurement Results

| TEST                                         | MEASUREMENT         | MAXIMUM               | RESULT |

|----------------------------------------------|---------------------|-----------------------|--------|

| Analog signaling filtered signal amplitude   | 230mV <sub>PP</sub> | 150mV <sub>PEAK</sub> | Pass   |

| Communication errors during analog signaling | 100 attempts        | 0 errors              | Pass   |

During the test, the HART test system was also used to test active transmissions during this periodic output transition. Using the HART test system, the *comtest* command sends a set of consecutive commands. While the device is cycling through the minimum and maximum values, the HART test system sends 100 commands and the transmitter responds to these commands to verify there are no errors in transmission.

## 3.4.6 Receive Impedance Test

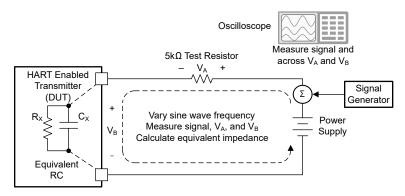

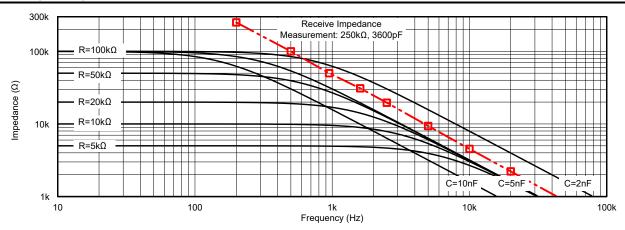

Another physical layer test is to measure the receive impedance of the transmitter. The AFE882H1 is built into a high-impedance transmitter and the receive impedance must be above a minimum level over both the primary variable and HART transmission frequencies. In this test, a  $5k\Omega$  series test resistance is used in the loop to measure the receive impedance of the transmitter. This test requires a significantly higher power supply voltage. The normal starting current of the transmitter is 4mA. This amount of current across  $5k\Omega$  is 20V and a supply of over 40V is required to operate this test. Figure 3-17 shows a block diagram of the test setup for measuring the receive impedance of the transmitter.

Figure 3-17. HART Receive Impedance Test Setup

A signal generator inputs a sine wave of different frequencies into the loop. The oscilloscope measures the voltage from the signal generator, the voltage across the test resistor, and the voltage dropped across the transmitter. From these three measured values on the oscilloscope, and using the known  $5k\Omega$  resistance of the test resistor, the equivalent impedance of the transmitter is calculated. Over frequency, an equivalent resistance and capacitance (Rx and Cx) can be calculated and plotted.

Table 3-6 tabulates the measured values for  $V_A$  and  $V_B$  and the calculated equivalent impedance for  $Z_M$  looking into the transmitter.

Table 3-6. Measured and Calculated Results from the Receive Impedance Test

| FREQUENCY | V <sub>A</sub> (V) | V <sub>B</sub> (V) | Z <sub>M</sub> (Ω, calculated) |

|-----------|--------------------|--------------------|--------------------------------|

| 200Hz     | 0.02               | 1                  | 250000                         |

| 500Hz     | 0.05               | 1                  | 100000                         |

| 950Hz     | 0.10               | 1                  | 50000                          |

| 1.6kHz    | 0.16               | 0.99               | 30938                          |

| 2.5kHz    | 0.25               | 0.98               | 19600                          |

| 5kHz      | 0.47               | 0.90               | 9375                           |

| 10kHz     | 0.75               | 0.68               | 4533                           |

| 20kHz     | 0.90               | 0.40               | 2222                           |

| 50kHz     | 0.98               | 0.17               | 867                            |

The impedance is then plotted versus frequency in Figure 3-18.

Figure 3-18. Receive Impedance Test Results Plotted Over Frequency

For this test, signals in a frequency range from 200Hz to 50kHz are measured and calculated. The equivalent receive resistance is tested to be greater than  $250k\Omega$  and the equivalent receive capacitance is tested to be 3600pF. For high-impedance transmitters, the minimum equivalent resistance is  $100k\Omega$  and the maximum capacitance is 5nF.

#### 3.4.7 Noise Sensitivity Test

The transmitter is also tested for the HART transmission in the presence of noise at different frequencies. For this test, a signal generator varies the supply voltage at different magnitudes and frequencies to simulate noise.

The noise sensitivity test verifies that the HART signal is received despite having out-of-band noise, and even some low-signal in-band noise. Figure 3-19 shows the test setup for the HART noise sensitivity test.

Figure 3-19. Noise Sensitivity Test

The signal generator is set to frequencies and amplitudes to mimic noise during a HART transmission. There are five frequency and amplitude combinations used for this test. Table 3-7 lists the different frequency and amplitude combinations used for the signal generator to simulate the noise.

Table 3-7. Measured Data from the Noise Sensitivity Test

| TYPE OF INTERFERENCE | FREQUENCY | LEVEL               | NUMBER<br>OF MISSED<br>COMMAND<br>ERRORS | RESULT |

|----------------------|-----------|---------------------|------------------------------------------|--------|

| In band              | 1700Hz    | 55mV <sub>PP</sub>  | 0                                        | Pass   |

| Out of band          | 250Hz     | 220mV <sub>PP</sub> | 0                                        | Pass   |

| Out of band          | 125Hz     | 880mV <sub>PP</sub> | 0                                        | Pass   |

| Out of band          | 63Hz      | 3.52V <sub>PP</sub> | 0                                        | Pass   |

| Out of band          | 29Hz      | 16V <sub>PP</sub>   | 0                                        | Pass   |

While the signal generator is active, the HART test system sends 100 consecutive commands to the transmitter. The transmitter sends a response to the commands. Any missed command or interrupted transmission is considered an error.

#### 3.4.8 Carrier Detect Test

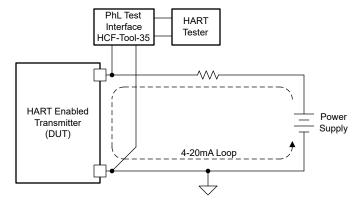

The last of the physical layer tests are the carrier detect tests. During these tests, the modem is replaced with the HCF\_TOOL-35 physical layer test interface. This tool is a HART modem interface with an adjustable output that can vary the amplitude of the tester HART signals. Figure 3-20 shows the HART carrier detect test setup.

Figure 3-20. HART Carrier Detect Test Setup

The carrier detect tests verify what minimum amplitude of transmission is needed to identify the signal as a HART signal. The test also identifies the maximum in-band signal that is not identified as a HART signal. An oscilloscope is used to verify the amplitude of the signal. The test also verifies the time required for a start and stop with a HART minimum amplitude transmission.

For the carrier detect tests, the signal level is dropped from the typical  $500 \text{mV}_{PP}$  level to  $120 \text{mV}_{PP}$ . The HART modem communication must still be received by the transmitter. After completion, the signal level is dropped even further to  $80 \text{mV}_{PP}$ , where the transmitter must reject any commands. Finally, the signal level is raised back to  $120 \text{mV}_{PP}$ . The device must again receive HART communication from the test system. Each of these tests are performed while sending 100 HART commands to the transmitter.

After these tests are completed the start and stop time are re-tested with the  $120 \text{mV}_{PP}$  signal to verify transmission. Table 3-8 reports the results for the Carrier Detect tests

| TEST                                          | SIGNALING AMPLITUDE | MEASUREMENT                | MAXIMUM                     | RESULT |

|-----------------------------------------------|---------------------|----------------------------|-----------------------------|--------|

| Successful error-free communications          | 120mV <sub>PP</sub> | 100 communication attempts | 0 errors                    | Pass   |

| Unsuccessful Communications                   | 80mV <sub>PP</sub>  | 100 communication attempts | 0 successful communications | Pass   |

| Successful error-free communications (return) | 120mV <sub>PP</sub> | 100 communication attempts | 0 errors                    | Pass   |

**Table 3-8. Carrier Detect Test Results**

This test uses a  $250\Omega$  current sense resistor. Carrier start and stop times must be less than 5ms (less than 6 bit times).

## 3.5 Data Link Layer Tests

After the physical layer tests, the data link layer (DLL) tests verify the syntax of the commands and the structure of the HART communication frames. These tests check the construction of the frame including the preamble, delimiter, addressing, and byte counts. Tests also check the transmitter frame generation, constructing the response data into the proper format to be understood by a controller. DLL tests also verify different cases for bus arbitration, with specific time responses from the transmitter in request-response and in burst modes.

## 3.5.1 Data Link Layer Test Specifications

HCF\_SPEC-081 defines the token-passing data link layer specification. The DLL is responsible for the reliable, error free communication of data between HART compatible devices. This document specifies the rules used by HART products to communicate digital information over a physical link.

To test the DLL, the test specifications are outlined by HCF TEST-1. These tests cover:

- HART communication frame detection and recognition by the transmitter

- · Frame generation from the transmitter for reception by the controller

- Bus arbitration to check that the transmitter responds promptly after receiving a command, and sending commands in burst mode

- Data link layer services that control bytes sent in the data frame for the application layer

The Linux-based HART test system has a set of pre-programmed tests to verify the data link layer. For all DLL tests, the HART test system runs the test and records a log of the test and results. In the HART test system, the *hartmenu* command gives a list of different tests available. These tests can be run consecutively, where the tests are run one after another until user intervention is required. Alternately, tests can be run individually, where the user can select a specific test.

Table 3-9 shows a list of data link layer tests.

Table 3-9. DLL Test List and Results

|             | Table 3-3. DEL Test List and Nesults                        |        |

|-------------|-------------------------------------------------------------|--------|

| TEST NUMBER | DESCRIPTION                                                 | RESULT |

| DLL001      | FSK preamble check                                          | Pass   |

| DLL002      | Delimiter check                                             | Pass   |

| DLL003      | Frame expansion check                                       | Pass   |

| DLL004      | Short frame check                                           | Pass   |

| DLL005      | HART controller address bit check                           | Pass   |

| DLL006      | Burst mode bit check                                        | Pass   |

| DLL007      | Long frame address check                                    | Pass   |

| DLL009      | Incorrect byte count check                                  | Pass   |

| DLL010      | Vertical parity check                                       | Pass   |

| DLL011      | Framing error check                                         | Pass   |

| DLL012      | Check byte test                                             | Pass   |

| DLL014      | Long message test                                           | Pass   |

| DLL015      | Start of message in data field check                        | Pass   |

| DLL016      | Preamble check for BACK frames                              | Pass   |

| DLL017      | Preamble check for ACK frames                               | Pass   |

| DLL018      | Gap errors in ACK frames check                              | Pass   |

| DLL019      | Gap check for BACK frames                                   | Pass   |

| DLL020      | Dribble byte check for ACK frames                           | Pass   |

| DLL021      | Dribble byte check for BACK frames                          | Pass   |

| DLL022      | Test host address bit for BACK frames                       | Pass   |

| DLL023      | Test burst mode bit of burst-mode transmitter device frames | Pass   |

| DLL024      | Test transmitter device responds within STO                 | Pass   |

| DLL025      | Burst hold during HART controller preamble                  | Pass   |

| DLL026      | Test burst response time after a DUT ACK                    | Pass   |

| DLL027      | Test response time between consecutive bursts               | Pass   |

| DLL028      | BACK timing with STXs errors                                | Pass   |

| DLL029      | Burst mode timeout on other transmitter device              | Pass   |

| DLL030      | Burst after response from other transmitter device          | Pass   |

| DLL032      | Read unique identifier                                      | Pass   |

| DLL033      | Write polling address                                       | Pass   |

| DLL034      | Read unique identifier with tag (Command 11)                | Pass   |

| DLL035      | Write number of response preambles                          | Pass   |

| DLL038      | Read unique identifier with tag (Command 21)                | Pass   |

| DLL039      | Transmitter device time-out stress test                     | Pass   |

| DLL040      | Unique address test                                         | Pass   |

| DLL041      | Framing successive messages                                 | Pass   |

| DLL042      | Command number expansion                                    | Pass   |

| ·           | -                                                           |        |

The DLL tests with the exception of DLL039 take about 13 hours to complete. Near the end of the run, there are a few tests that require user intervention to cycle power on the devices.

DLL039 is the final DLL test to be run. In this time-out stress test, the tester sends 2 million consecutive commands and records the log with any errors in the response from the device. Because HART communication responds at about 1 command per second, this test takes about 19 days to complete. An uninterrupted power supply is highly recommended when running this test.

## 3.5.2 Data Link Layer Test Logs

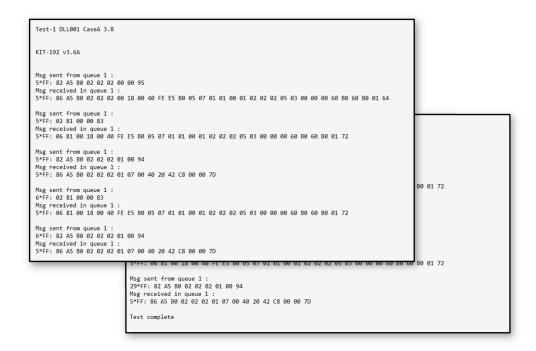

When the data link layer tests are run, the HART test system opens up a HART sniffer window to view the commands and responses from the tester to the transmitter device. Figure 3-21 shows this HART utility window and gives a active reading of the HART communication as the signal occurs. The "Msg sent from queue 1" indicates that there is a preamble sent as a communication to the device. The preamble is followed by a delimiter, address, command, and error correction bytes from the HART test system.

Figure 3-21. HART Sniffer Display From the HART Tester

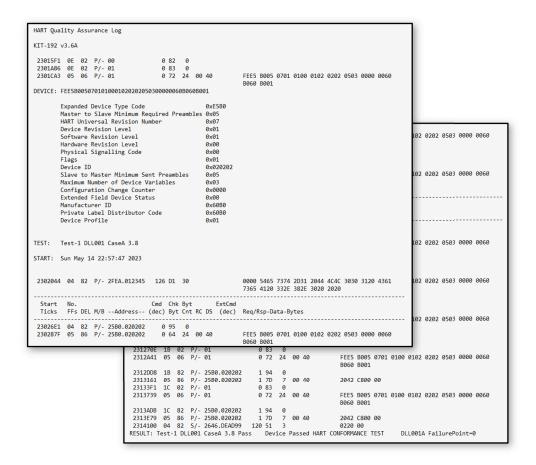

While each of the data link layer tests are run, the HART test system generates a log that is used to show the communication and can be reviewed by FieldComm Group. Figure 3-22 shows a small segment of one of these logs.

Figure 3-22. DLL Test System Logs

These test logs record which test is run, device information, the communication transaction with a time stamp, verifies the communication, and flags any failures. After all tests are complete, the HART test system generates a full set log files. These log files are zipped together and sent to FieldComm with the device registration request.

#### 3.6 Universal Command Tests

The HART test system also runs the universal command tests of the application layer (UAL) starting from the *hartmenu* application. The universal command specification is defined under HCF\_SPEC-127. These tests verify the application layer of the protocol and check the universal HART commands supported by the transmitter. The UAL test specification is defined by HCF\_TEST\_3. The test setup is the same as the DLL test setup, and also uses the HART test system to send commands to the transmitter. These tests verify the following functions of the applications layer:

- Verify Support for All Universal Commands. These tests scan for the range of universal commands from 0 to 31 and look for a proper response.

- Read Dynamic Variables. These tests check the responses to commands 1, 2, 3, and 9 for dynamic variable.

- Verify Write Commands. The write tests check initial values, and subsequent write values. This tests the

results of different data fields.

- · Verify Configuration Read Commands.

- Confirm Write Protect. This is a test of the write protect into the transmitter (if this function is supported).

- Test Cold Start Bit. The controller must be able to detect a cold start (i.e. a power failure).

- Read Device Variables. This test verifies the proper operation of command 9.

- Test the Configuration Changed Bit. This test verifies support for and proper operation of command 38 and checks a configuration changed counter to reset the status bit.

- Support for Command 48, Read Additional Device Status. This test verifies support for command 48 and checks the ability to reset the More Status Available bit.

The end of the tests available require some user intervention for setting the cold start bit and checking the more status available bit.

Table 3-10 lists the tests run by the HART test system to verify support for universal commands and the results of the test.

| TEST NUMBER | DESCRIPTION                                   | RESULT         |

|-------------|-----------------------------------------------|----------------|

| UAL000      | Confirm all universal commands are supported  | Pass           |

| UAL001      | Read dynamic variables (commands 1, 2, and 3) | Pass           |

| UAL005      | Write message                                 | Pass           |

| UAL006      | Write tag descriptor and date                 | Pass           |

| UAL007      | Verify command 14 and 15 response             | Pass           |

| UAL008      | Verify final assembly number                  | Pass           |

| UAL009      | Verify write protect                          | Not applicable |

| UAL010      | Verify cold start bit                         | Pass           |

| UAL011      | Read device variables (command 9)             | Pass           |

| UAL012      | Read dynamic variable classification          | Pass           |

| UAL013      | Write long tag                                | Pass           |

| UAL038      | Reset configuration changed flag              | Pass           |

| UAL048      | Read additional device status                 | Pass           |

Table 3-10. UAL Command Test List and Results

The HART stack programmed into the transmitter passes these tests, except that the write protect was not programmed into the functionality. For this verify write protect test (UAL009), the test is checked as *Not applicable*. The complete set of UAL tests take about 30 minutes to complete. As with the DLL tests, running the UAL tests enables a HART sniffer window and generates a set of test logs for these tests for the application submission.

## 3.7 Common-Practice Command Tests

The last of the HART tests verify that common-practice commands of the application layer (CAL) are implemented in the transmitter. The CAL test specification is described by HCF\_TEST\_4. These tests check for highly-recommended commands that are implemented in many HART devices. Here is a basic list of common-practice commands that can be implemented in HART devices and tested as part of the CAL tests:

- · Read selection of up to four dynamic variables

- · Write damping time constant

- Write device range values

- Calibrate (set zero, set span)

- · Set fixed output current

- · Perform self-test

- · Perform host reset

- Trim primary variable zero

- · Write primary variable unit

- · Trim DAC zero and gain

- · Write transfer function (square root/linear)

- · Write sensor serial number

- Read or write dynamic variable assignments

Table 3-11 shows the set of common-practice command tests run by the HART tester. While the transmitter designed in this application note uses a HART stack that shows functionality of the device, this design is not a full-functioned device used as a real transmitter in an application. Many commands have been implemented, but not all are supported from this list of tests. This complete set of CAL tests take about 4 hours to complete.

Table 3-11. CAL Command Test Results

| TEST NUMBER | DESCRIPTION                                          | RESULT          |

|-------------|------------------------------------------------------|-----------------|

| CAL000      | Checks for common practice commands                  | Pass            |

| CAL001      | Write protect test                                   | Not implemented |

| CAL033      | Read device variables                                | Pass            |

| CAL034      | Write primary variable damping value                 | Pass            |

| CAL035      | Write primary variable range values                  | Pass            |

|             | Primary variable units code unaffected by command 35 | Pass            |

| CAL036      | Set primary variable upper range value               | Not applicable  |

| CAL037      | Set primary variable lower range value               | Not applicable  |

| CAL040      | Enter/exit fixed current mode                        | Pass            |

| CAL041      | Perform self test                                    | Pass            |

| CAL042      | Perform device reset                                 | Pass            |

| CAL043      | Set primary variable zero                            | Not applicable  |

| CAL044      | Write primary variable units                         | Pass            |

| CAL045      | Trim loop current zero                               | Pass            |

| CAL046      | Trim loop current gain                               | Pass            |

| CAL047      | Write primary variable transfer function             | Not applicable  |

| CAL049      | Write primary variable transducer serial number      | Not applicable  |

| CAL050      | Read dynamic variable assignments                    | Not applicable  |

| CAL051      | Write dynamic variable assignments                   | Not applicable  |

| CAL052      | Set device variable zero                             | Not applicable  |

| CAL053      | Write device variable units                          | Not applicable  |

| CAL054      | Read device variable information                     | Pass            |

| CAL055      | Write device variable damping value                  | Not applicable  |

| CAL056      | Write device variable transducer serial number       | Not applicable  |

| CAL060      | Read analog channel and percent of range             | Not applicable  |

| CAL062      | Read analog channels                                 | Not applicable  |

Table 3-11. CAL Command Test Results (continued)

| TEST NUMBER | DESCRIPTION                                   | RESULT         |

|-------------|-----------------------------------------------|----------------|

| CAL063      | Read analog channel information               | Not applicable |

| CAL064      | Write analog channel additional damping value | Not applicable |

| CAL065      | Write analog channel range values             | Not applicable |

| CAL066      | Enter/exit fixed analog channel mode          | Not applicable |

| CAL067      | Trim analog channel zero                      | Not applicable |

| CAL068      | Trim analog channel gain                      | Not applicable |

| CAL069      | Write analog channel transfer function        | Not applicable |

| CAL070      | Read analog channel endpoint values           | Not applicable |

| CAL071      | Lock device                                   | Not applicable |

| CAL072      | Squawk                                        | Pass           |

| CAL073      | Find device                                   | Not applicable |

| CAL074      | Verify I/O system commands                    | Not applicable |

| CAL078      | Command aggregation                           | Not applicable |

| CAL079      | Write device variable                         | Not applicable |

| CAL080      | Verify device variable trim commands          | Not applicable |

| CAL091      | Trending                                      | Not applicable |

| CAL101      | Subsystem burst mode                          | Not applicable |

| CAL103      | Support for multiple burst messages           | Pass           |

| CAL104      | Smart data publishing                         | Pass           |

| CAL107      | Write burst device variables                  | Pass           |

| CAL108      | Write burst mode command number               | Pass           |

| CAL109      | Burst mode control                            | Pass           |

| CAL115      | Event notification                            | Not applicable |

| CAL512      | Country code                                  | Not applicable |

| CAL518      | Location description                          | Not applicable |

| CAL520      | Process unit tag                              | Not applicable |

| CAL523      | Read condensed status mapping array           | Not applicable |

| CAL524      | Manipulating condensed status map             | Not applicable |

| CAL526      | Status simulation                             | Not applicable |

As with the DLL and UAL tests, running the CAL tests from *hartmenu* generates a set of logs for the registration submission.

# 3.8 Device Specific Command Tests

In addition to the universal commands and the common-practice commands, manufacturers can implement device specific commands into devices. The following list shows some device specific commands that can be implemented.

- · Read or write low-flow cut-off

- · Start, stop, or clear totalizer

- · Read or write density calibration factor

- Choose PV (mass, flow, or density)

- · Read or write materials or construction information

- · Trim sensor calibration

- PID enable

- · Write PID set point

- · Valve characterization

- Valve set point

- · Travel limits

- User units

- · Local display information

Again, these commands can be implemented by device manufacturers but are not required. Device specific commands are not tested through the HART specification and are not implemented as tests in the HART test system.

#### 3.9 HART Protocol Test Submission

After all the physical layer tests and DLL, UAL, and CAL tests are completed, the device is ready to submit for registration. Fieldcomm HART registration applications require the following documentation:

- · Complete a HART Field Device Test Report

- · Compose a test document describing the setup and test procedure for the device

- · Complete marketing forms for FieldComm on how this device is to be used and marketed

- Physical layer test results are compiled in the Field Device Test Report

- Results from DLL, UAL, and CAL tests are zipped up from the test logs and submitted

# 3.10 HART Registration

After the submission, FieldComm reviews the test results and log files. After reviewing the submission and checking the results, FieldComm requests a couple of transmitters to verify testing.

Testing and registration requires about six weeks to complete as long as there are no problems discovered in the tests. Any problems discovered in the tests require a re-submission of the device. If the design has been reviewed to satisfaction, FieldComm informs you that the device has been registered.

After completion, FieldComm sends a letter recognizing that the design is now HART registered. The response is accompanied by a certificate of registration for the design. Figure 3-23 shows the certificate of registration for the AFE882H1 transmitter device.

Figure 3-23. HART Registration for an AFE882H1-Based Transmitter Design

Summary Summary Www.ti.com

# 4 Summary

This application note describes the use of an AFE882H1 evaluation module as the basis of a HART-enabled transmitter design. Details of construction are presented showing the operation, input protection, voltage-to-current conversion, and HART signal transmission. Using the EVM with a digital-back-end board, an MSP430FR5969 LaunchPad programmed with a basic HART stack is used to complete a transmitter design. This application note also describes the basics of HART protocol testing and registration. Physical layer tests are first shown, describing different tests for FSK shape, frequency, and in-band and out-of-band noise. The HART test system is used to check the data link layer, universal command, and commonly-implemented commands in the device. For any developer, these tests are run on the HART-enabled device, compiled, and sent to FieldComm for HART device registration.

# 5 Acknowledgments

TI acknowledges Smart Embedded Systems (SES) in Pleasanton, California for the development of the HART stack used in this design. SES was instrumental in achieving device registration with the FieldComm Group. To reach out to SES, go to smartembeddedsystems.com.

#### 6 References

- Texas Instruments, AFEx81H1 16-Bit and 14-Bit, Low-Power DACs With Internal HART® Modem, Voltage Reference, and Diagnostic ADC for 4-mA to 20-mA Loop-Powered Applications, data sheet.

- Texas Instruments, AFEx82H1 16-Bit and 14-Bit, Low-Power DACs With Internal HART® Modem, Voltage Reference, and Diagnostic ADC for 4-mA to 20-mA Loop-Powered Applications, data sheet.

- Texas Instruments, MSP430FR596x, MSP430FR594x Mixed-Signal Microcontrollers, data sheet.

- Texas Instruments, MSP430FR5969 LaunchPad™ Development Kit (MSP-EXP430FR5969), user's guide.

- Texas Instruments, AFE881H1EVM User's Guide.

- Texas Instruments, AFE882H1EVM User's Guide.

- Texas Instruments, A Basic Guide to the HART Protocol, application note.

- Texas Instruments, Design and Test of a HART-Enabled Field Transmitter for 4-20mA Loops, application note.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated