# Using TMS320C5402 DMA Channels to Read from the TLV1570 ADC

Lijoy Philipose AAP Data Conversion

#### **ABSTRACT**

This application report presents hardware and software solutions for using the DMA channels of the 16-bit, fixed-point TMS320C5402 DSP to collect digital samples from the TLV1570 10-bit, 1.25-MSPS, 8-channel, serial analog-to-digital converter. Project collateral discussed in this application report can be downloaded from the following URL: <a href="http://www.ti.com/lit/zip/SLAA097">http://www.ti.com/lit/zip/SLAA097</a>.

#### **Contents**

| 1                          | introa  | ction               |                                         |    |  |

|----------------------------|---------|---------------------|-----------------------------------------|----|--|

| 2                          | Hardw   | ıre                 |                                         | 2  |  |

|                            | 2.1 T   | IS320C5402 DSK      | Starter Kit                             | 2  |  |

|                            | 2.2 T   | L1570 EVM           |                                         | 3  |  |

| 3                          | Softwa  | e                   |                                         |    |  |

|                            |         |                     |                                         |    |  |

|                            |         |                     |                                         |    |  |

|                            | 3.      | .1 DSP CNTL2 (      | Control Register (I/O Address = 0x0004) | 3  |  |

|                            |         | 2 Write to CPLI     | D Register CNTL2                        | 4  |  |

|                            |         |                     |                                         |    |  |

|                            |         |                     |                                         |    |  |

|                            |         |                     |                                         |    |  |

|                            | 3.      |                     | ter Operation                           |    |  |

|                            | 3.      |                     | rerview                                 |    |  |

|                            | 3.      |                     | erview                                  |    |  |

| 4                          | Refere  | nces                |                                         | 14 |  |

| App                        | endix   | main.c              |                                         | 15 |  |

| App                        | endix l |                     |                                         |    |  |

| App                        | endix ( | dma_src.c           |                                         | 38 |  |

| App                        | endix l | Mcbspsrc.c          |                                         | 41 |  |

| App                        | endix I | adc_const.h         |                                         | 43 |  |

| App                        | endix l | C5402 Memory        | Mapping                                 | 44 |  |

|                            |         |                     | Link of Figures                         |    |  |

|                            |         |                     | List of Figures                         |    |  |

| 1 M                        | cBSP F  | egister Addressing  | g Scheme                                | 5  |  |

| 2 M                        | cBSP F  | egister Bits With R | Respect to Serial-Port Function         | 7  |  |

| 3 DMA Subaddressing Scheme |         |                     |                                         |    |  |

| 4 O                        | verview | of How DMA Is Us    | sed to Collect Samples                  | 12 |  |

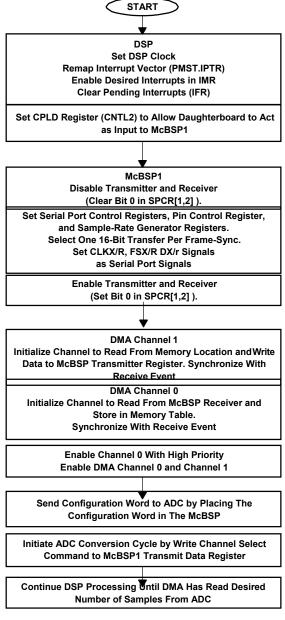

| 5 | Program Flow Chart                      | 13   |

|---|-----------------------------------------|------|

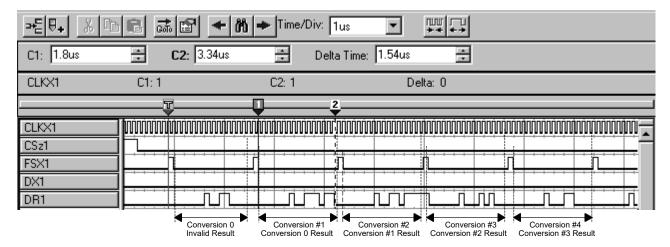

| 6 | DMÄ Triggered Multiple Conversions      | . 14 |

|   | List of Tables                          |      |

| 1 | CNTL 2 Control Register Bit Definitions | 4    |

|   | McBSP Register Settings                 |      |

|   | DMA Register Settings                   |      |

|   | Configuration Register Definitions      |      |

## 1 Introduction

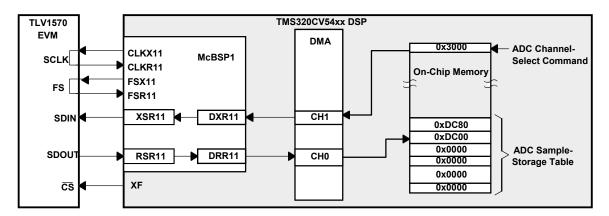

It is inefficient to waste DSP cycles to service slow serial analog-to-digital converters. One solution is to assign the nursing duties to DSP peripherals, specifically to the DMA controller, since it is designed to function without tasking the powerful DSP. The slower serial-data converter in this case is the TLV1570. The TLV1570 is an 8-channel, 10-bit, 1.25-MSPS ADC with a four-wire serial interface. After reading this report, users will be able to implement the hardware and software interface of this ADC to the TMS320C5402 DSP via the McBSP and DMA peripherals. The C-language source code used in developing this report is provided in the appendixes.

## 2 Hardware

The hardware interface consists of the TMS320C5402 DSK and the TLV1570 EVM.

#### 2.1 TMS320C5402 DSK Starter Kit

The C5402 DSK is specifically designed for digital communications applications and comes complete with a TMS320C5402-based target board, DSK-specific *Code Composer Studio* debug tools, 32K application-size-limited C-compiler/assembler/linker, parallel-port interface, power supply, and cables.

The C5402 device features 100-MHz clock, 40-bit ALU, 16K x 16-bit dual-access on-chip RAM, 4K x 16-bit on-chip ROM, advanced multibus architecture with three separate 16-bit data-memory busses, and one program memory bus. In addition to these features, the DSK has an embedded JTAG emulation via the TBC and IEEE-1284 parallel ports. The onboard parallel-port controller allows the host PC to use the parallel port for emulation, or to directly access the host-port interface of the 'C5402. Other features include onboard standard JTAG-interface connection for optional emulation and expansion connectors for add-on accessories. Texas Instruments now provides expansion connectors or adapter boards to interface all data-converter EVMs to this DSK.

The enhanced peripherals of particular interest to this report are the McBSP serial ports. These ports are further explained in Chapter 3.

The 'C5402 DSK supports a TMS320VC5402 DSP which can operate at frequencies up to 100 MHz with a core voltage of 1.8 V and an I/O voltage of 3.3 V. The DSK provides support for all the DSP interfaces and control signals. The JTAG-emulation interface is used to support both embedded and external JTAG emulations. The control interface is used to reset the device and to provide external interrupts. The McBSP0, by default, is used to interface to a telephone DAA port; this port is also available to the daughterboard via an onboard multiplexer. The McBSP1, by default, is used on microphone/speaker interfaces; it is also brought to the peripheral-expansion connector for use on the daughterboard. The CPLD controls the source of McBSP0 and McBSP1.

#### 2.2 TLV1570 EVM

The TLV1570 evaluation module (EVM) is a complete stand-alone board designed to allow quick and accurate evaluation of the TLV1570 analog-to-digital converter (ADC).

The TLV1570 is an 8-channel, 10-bit, 1.25-MSPS (megasamples-per-second) ADC with a four-wire serial interface. It is compatible with both 3-V and 5-V systems and directly interfaces to Texas Instruments digital-signal processors. This EVM provides a 12-bit digital-to-analog converter that can be used to loopback DAC output signals to ADC inputs. Circuits such as an external-voltage-reference source are provided for use with both the ADC and the DAC. An operational amplifier has been placed between the ADC multiplexer-output pin (MO) and the analog input pin (AIN) to allow for signal conditioning. The EVM provides control signals and power pins (VCC and GND) via connector J2. Analog-input signals can be provided via connector J1. Refer to the *TLV1570 Evaluation Module* user's guide for more information on this EVM.

## 3 Software

The DSP, McBSP, and CPLD devices must be initialized correctly before attempting to read or write to the data converter. The following sections explain the sample code included in the appendixes.

## 3.1 DSP

The 'VC5402 DSK provides the DSP with a single 20-MHz frequency reference via the DSP built-in crystal oscillator. The DSP's clock-mode pins are configured via dip-switch settings to allow for a number of different frequencies, up to the part's maximum rate of 100 MHz. The CLKMD register can also be changed after reset to select the DSP's operating frequency. The CPU clock frequency is 100 MHz when CLKMD is equal to 0x4007.

## 3.2 CPLD

There are seven DSP CPLD registers mapped into the DSP's lower I/O address space starting at address 0x0000. Only control register 2 (CNTL2) is of interest to this report.

## 3.2.1 DSP CNTL2 Control Register (I/O Address = 0x0004)

This register selects the source of data for both McBSPs. Bit 1 of this register needs to be modified; otherwise the McBSP1 defaults to the onboard device as its input source. The McBSP1 should be set to use the daughterboard as its source of data on this report. Table 2 shows the register-bit definitions.

| BIT | NAME      | R/W | DESCRIPTION                                                    |

|-----|-----------|-----|----------------------------------------------------------------|

| 7   | DAAOH     | RW  | DAA off-hook control (0 = on-hook, 1 = off-hook)               |

| 6   | DAACID    | RW  | DAA caller ID enable (0 = disabled, 1 = enabled)               |

| 5   | FLASHENB- | RW  | Select FLASH =1 (default) or SRAM (=0) for external memory (1) |

| 4   | INT1SEL   | RW  | Interrupt 1 source selection (0 = UART, 1 = daughterboard)     |

| 3   | FC1CON    | RW  | MIC/Speaker AD50 FC control bit (0)                            |

| 2   | FC0CON    | RW  | DAA AD50 FC control bit (0)                                    |

| 1   | BSPSEL1   | RW  | McBSP1 select control (0 = mic/speaker, 1 = daughterboard)     |

| 0   | BSPSEL0   | RW  | McBSP0 select control (0 = TelSet DAA, 1 = daughterboard)      |

# 3.2.2 Write to CPLD Register CNTL2

Control register 2 should be set to enable the daughterboard as the source for McBSP1. This is accomplished by setting CNTL2=0x0002. This register is mapped to I/O space 4h; therefore, the port instruction is used to access the register.

#### 3.3 McBSP

The multichannel buffered serial port (McBSP) is a superset of the standard serial ports found on Texas Instrument's digital signal processors (DSP). In addition to features found on the previous serial-port interfaces, the McBSP is able to directly interface to TI/E1 framers, IOM-2-compliant devices, MVIP switching-compatible and ST-BUS-compliant devices, AC97-compliant devices, IIS-compliant devices, and SPI devices. It provides a wide selection of transmit/receive data sizes,  $\mu$ -Law and A-Law companding, programmable polarity for both frame synchronization and data clocks, and highly-programmable internal clock and frame generation. These features and programming requirements are described in TMS320C54x DSP Enhanced Peripherals Reference Set, Volume 5 by Texas Instruments.

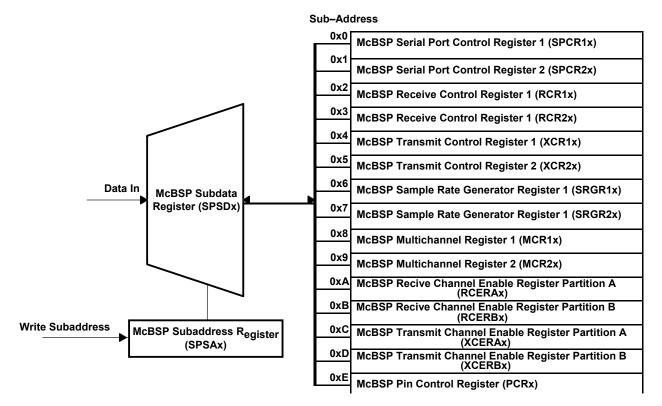

First let us look at how the McBSP registers are accessed. The McBSP registers are memory-mapped using a register-subaddressing scheme. Figure 1 shows a visual representation of this scheme. Register subaddressing involves multiplexing a set of registers to a single location in the memory map. A sub-bank address register is used to control the multiplexer. A subdata register (SPSDx) is used to read or write data to the desired subaddressed register. To access a specific subaddressed register, the register's subaddress location is written to the subaddress register (SPSAx). This directs the multiplexer to connect to the desired physical location in memory. When a write access occurs, the data written to the subdata register is moved to the embedded data register specified by the subaddress register. Similarly for a read access, the contents of the register specified by the subaddress register is moved to the subdata register.

Figure 1. McBSP Register Addressing Scheme

Let us use the McBSP0 as an example: the subdata register (SPSD) is at location 0x039, and the subaddress register (SPSAx) is at location 0x038 in physical memory. The following assembly-code sample writes 0x000 to serial-port control register 1 of the McBSP0:

```

SPSA0    .set 038h ;McBSP0 subaddress register

SPSD0    .set 039h ;McBSP0 subdata register

SPCR10_SUB    .set 000h ;McBSP0 serial port control register 1 subaddress

mmr(#SPSA0) = #SPCR10_SUB

mmr(#SPSD0) = #000h

```

There are 16 registers associated with each McBSP. Interfacing a single TLV1570 ADC to the McBSP requires the proper configuration of only nine of these registers.

- The serial port control register 1 (SPCR1) contains the McBSP receiver status bits and the

main switch to enable or disable the receiver. This register includes the clock-stop mode bit,

which sets the serial port for various clocking modes for SPI and non-SPI schemes. Also

included in SPCR1 is the ABIS-mode bit and the receiver-interrupt mode bit.

- The serial port control register 2 (SPCR2) contains the McBSP transmitter-status bits and the main switch to enable or disable the transmitter. This register also contains the bits to reset the frame-sync generator and the sample-rate generator.

- The pin control register (PCR) contains the bits to configure the McBSP pins as inputs or

outputs during normal serial-port operation. This register is used to reconfigure the

serial-port pins as general-purpose inputs or outputs when the receiver or transmitter is

disabled. The PCR configures the transmitter and receiver clock and frame-sync modes. For

example, these bits determine whether CLKX/R and FSX/R are input or output pins and what their polarity is.

- Receive control register 1 (RCR1) contains the bits to configure various options of the receiver. The value of this register determines the receiver word size (between 8 and 32 bits) and the number of words per frame (1 to 128) expected per receiver event.

- Receive control register 2 (RCR2) determines the size of the word received and the bit delay

after the frame-sync pulse. This register configuration plays an essential role when transfers

greater than 16 bits and multiple phases are necessary. In this application the register bit of

interest is the data-bit delay. The RCR2 register bits also select between μ-law, A-law

companding, and whether the MSB or the LSB is transferred first for noncompanding 8-bit

transfers.

- The *transmit control register 1 (XCR1*) contains the bits which determine the transmit-word length and frame size. A transfer can be 8 to 32 bits wide and anywhere from one to 128 words long.

- Transmit control register 2 (XCR2) contain the bits which determine the transmit-data delay and select between μ-law, A-law companding, and whether the MSB or the LSB is transferred first for noncompanding 8-bit transfers.

- Sample-rate generator register one (SRGR1) and sample-rate generator register 2 (SRGR2) control the sample-rate generator. The sample-rate generator is composed of a three-stage clock divider that allows programmable data clocks (CLKG) and framing signals (FSG). These are McBSP internal signals that can be programmed to drive the receive/transmit clock (CLKR/X) and the receive/transmit data framing (FSR/X). Sample-rate generator registers (SRGR[1,2]) control the operation of the various features of the sample-rate generator. These registers are used to control the width of the frame-sync pulse and to determine whether frame-sync is an external input driven by the sample-rate generator or a signal to indicate that data has been copied from DXR[1,2] to XSR[1,2]. These registers specify whether the sample-rate generator clock is derived from the CPU clock or from the CLKS pin, and by what value to divide the CPU clock to produce the desired serial clock (CLKX/R).

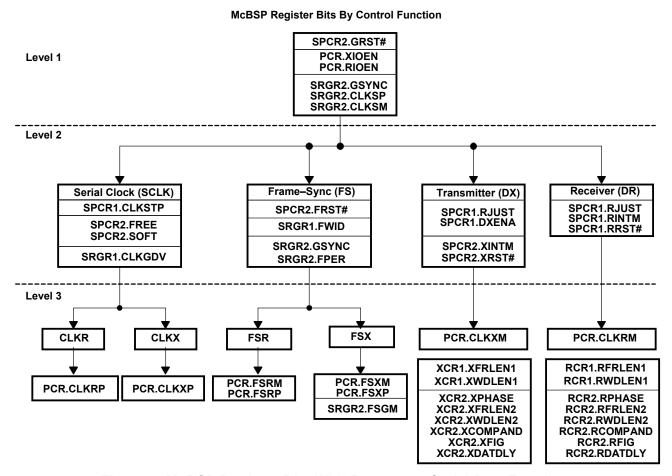

Figure 2. McBSP Register Bits With Respect to Serial-Port Function

Describing all nine registers in detail is not practical in this report. Figure 2 presents these register bits in relation to the serial lines. Table 3 summarizes the register configuration used in this application report. The multichannel registers are not included in this mapping, since they are not used for this particular interface. Figure 2 is divided into horizontal levels to illustrate the details of the bit control. Level-one register bits relate to the overall serial port. These register bits define the function of the serial-data pins, the state of the sample-rate generator, the clock input to the sample-rate generator, etc. Level-three bits define the specifics of that particular serial port signal line. Take for example the serial clock: level-three bits describe the polarity of the receive and transmit clocks. Detailed descriptions of all the register bits are found in the *TMS32054x DSP Enhanced Peripherals Reference Set, Volume 5* (Literature number SPRU302) from Texas Instruments.

Table 2. McBSP Register Settings

| McBSP1<br>ADDRESS | McBSP1<br>SUBADDRESS | ACRONYM | REGISTER<br>INITIALIZED | COMMENT                                                                                                                                 |

|-------------------|----------------------|---------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 0041              |                      | DRR11   |                         | Receive data register                                                                                                                   |

| 0043              |                      | DXR11   |                         | Transmit data register                                                                                                                  |

| 0048              |                      | SPSA1   |                         | McBSP1 subaddressing register                                                                                                           |

|                   | 0x0000               | SPCR11  | 0x0001                  | The LSB bit must be 0 (0x0000) while configuring McBSP so that the transmitter is disabled.                                             |

|                   | 0x0001               | SPCR21  | 0x02C1                  | The LSB bit must be 0 (0x02C0) while configuring McBSP so that the receiver is disabled.                                                |

|                   | 0x0002               | RCR11   | 0x0040                  | Selects one 16-bit word transfer per frame                                                                                              |

| 0049              | 0x0003               | RCR21   | 0x0001                  | Sets 1-bit delay on receiver. Receiver assumes first MSB bit to arrive on the next clock cycle after FSR pulse.                         |

|                   | 0x0004               | XCR11   | 0x0040                  | Selects one 16-bit word transfer per frame.                                                                                             |

|                   | 0x0005               | XCR21   | 0x0001                  | Transmitter shifts out data immediately following the falling edge of FSX                                                               |

|                   | 0x0006               | SRGR11  | 0x0009                  | CLKX has a 10-MHz frequency, assuming a 100-MHz CPU clock. CLKX = CPU clock/(CLKGDV +1) when CLKGDV = SRGR1[7,0]                        |

|                   | 0x0007               | SRGR21  | 0x2000                  | The sample-rate generator clock is derived from the CPU clock                                                                           |

|                   | 0x000E               | PCR1    | 0x0A00                  | FSX is determined from sample-rate generator frame-synchronization mode bit SRGR2.FSGM. CLKX output is driven by sample-rate generator. |

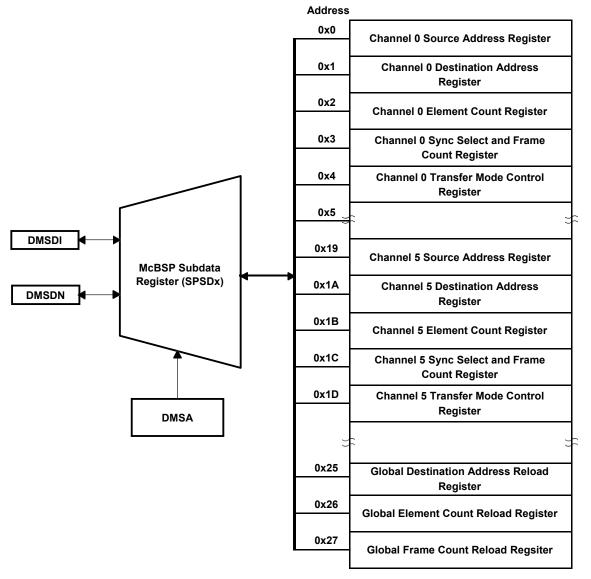

#### 3.4 DMA

The direct memory access (DMA) controller uses the same subaddressing scheme as the McBSP. So the same procedure used for writing to and reading from McBSP registers must be used here. The DMA provides one additional register which makes programming the registers easier. Figure 3 shows two registers at the input to the multiplexer. DMSDI is the sub-bank access register (DMSA) which increments the sub-bank address register after each read/write. Register DMSDN does not increment the sub-bank address register after read/write operations. The advantage in using the DMSDI is that the user no longer has to change the contents of DMSA to point to the next register. For example, programming the DMA channel 0 registers involves writing 0x00 to DMSA. The first value written to DMSDI is moved to DMSCR0, the second to DMDST0, the third to DMCTR0, etc. Register DMSDN should be used to write to the DMA register if that particular register is the only one to be modified.

Five channel-specific registers and the channel priority and enable control register (DMPREC) need to be configured for each DMA channel used:

Figure 3. DMA Subaddressing Scheme

- Source (DMSRCn) and destination (DMDSTn) registers (where n is the DMA channel) store the address of the data to be read. Likewise, the address where data is to be written is stored in the DMSTn register.

- The element count register(DMCTRn is a 16-bit counter that keeps track of the number of DMA transfers to be completed. This register is always initialized to one less than the number of elements to be stored.

- The DMA sync event and frame count (DMSFCn) register controls three services: 1) the synchronization event used to trigger a DMA transfer; 2) the word size for each transfer, specified as either 16-bit or 32-bit words; 3) the number of frames to be transferred (one to 256); for example, if only one frame is desired, this register field should be written as zero (the desired value minus one).

- The *transfer-mode control register(DMMCRn)* controls the transfer mode of the channel. This register determines whether the source/destination address is postincrement or

postdecrement after each transfer. This register also determines whether the channel is operating in autobuffering mode (ABU) or multiframe mode, when the DMA will interrupt the DSP, and the address space where the source/destination addresses are located.

• The channel priority and Enable Control Register (DMPREC) controls the function of the overall DMA. Due to the limited number of interrupts available in the 'C54xx family, some DMA interrupts are multiplexed with other peripheral interrupts. Bits in this register determine which interrupts are assigned to the interrupt-flag register. The DMPREC also sets the priority given to each channel to either low or high so those channels with high priority are serviced before those with low priority. The DMA register settings used in this application report are summarized in Table 3.

**Table 3. DMA Register Settings**

| REGISTER   |              | COMMENT                                                                                                                                                                                                                                                                                                                     |  |  |

|------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME VALUE |              | COMMENT                                                                                                                                                                                                                                                                                                                     |  |  |

| DMSRC0     | DRR11        | DMA channel 0: source-address register Source-memory-mapped address to read from                                                                                                                                                                                                                                            |  |  |

| DMDST0     | &DataTable_0 | DMA channel 0: destination-address register Destination address for sample storage                                                                                                                                                                                                                                          |  |  |

| DMCTR0     | NSAMPLES-1   | DMA channel 0: element-count register Number of samples to store minus one                                                                                                                                                                                                                                                  |  |  |

| DMSFC0     | 0x5000       | DMA channel 0: sync-select and frame-count register Synchronization transfers with McBSP1 receive event. CH0 reads data out of DRR1 when McBSP REVT occurs, then CH1 moves channel-command word to DXR1.                                                                                                                    |  |  |

| DMMCR0     | 0xC004       | DMA channel 0: transfer-mode control register The content of the registers are reinitialized upon completion of block transfer. DMAC0 interrupt is generated after block transfer. No modification is made to source address register after each transfer. Destination address register is post-incremented after transfer. |  |  |

| DMSRC1     | &ChnlSelCmd  | DMA channel 1: source-address register Source-memory address to read command word from                                                                                                                                                                                                                                      |  |  |

| DMDST1     | DXR11        | DMA channel 1: destination address register Destination address to store command, that is, McBSP1 transmitter                                                                                                                                                                                                               |  |  |

| DMCTR1     | NSAMPLES-1   | DMA channel 1: element-count register Number of times to transfer command word to transmitter, minus 1                                                                                                                                                                                                                      |  |  |

| DMSFC1     | 0xE000       | DMA channel 1: sync-select and frame-count register Synchronization transfers with INT3 receive event. When INT3 occurs, CH0 reads data out of DRR1, then CH1 moves channel-command word to DXR1.                                                                                                                           |  |  |

| DMMCR1     | 0x8000       | DMA channel 1: transfer-mode control register The contents of the registers are reinitialized upon completion of block transfer. No modification is made to source-address register after each transfer. No modification is made to destination-address register after each transfer.                                       |  |  |

| DMAPREC    | 0x0103       | DMA priority and enable-control register Enable DMA CH0 and CH1. CH0 has high priority. CH0 reads data out of DRR1 and stores it before CH1 triggers another conversion cycle.                                                                                                                                              |  |  |

Now that the basic operation of the McBSP and DMA peripherals has been covered, let us look at the TLV1570 analog-to-digital converter.

#### 3.5 TLV1570

## 3.5.1 Data Converter Operation

The TLV1570 accepts an analog-input range from 0 V to AVdd, and digitizes the input at a maximum throughout rate of 1.25 MSPS. To achieve this rate it must be clocked at 20 MHz with power supplied at 5 V. Using a 3-V supply and a maximum serial-clock input of 10 MHz, the throughput rate drops to 625 KSPS. The sampling rate is determined by dividing the serial-clock frequency by 16. This data converter requires 16 serial clocks for each conversion (sample and convert). The result from the current cycle is placed on the serial-data-out line at the start of the next conversion cycle. Before accepting valid conversion results, the device needs to be programmed to the desired operating state. This is done by writing to the 16-bit configuration register. Table 4 explains all the different operating states for this ADC.

**Table 4. Configuration Register Definitions**

| BIT           | DESCRIPTION                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|--|

|               | Software power down:                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

| DI15          | 0: Normal                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

|               | 1: Power down enabled  DI14 Reads out values of the internal register, 1 – read, Only DI15 – DI1 are read out                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

| DI14          | Reads out values of the internal register, 1 – read. Only DI15 – DI1 are read out.                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

|               | These two bits select the self-test voltage to be applied to the ADC input during next clock cycle:                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

|               | 00: Allow AIN to come in normally                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

| DI13, DI12    | 01: Apply AGND to AIN                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

|               | 10: Apply VREF/2 to AIN                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

|               | 11: N/A                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

|               | Choose speed application                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Х | Х |  |

| DI11          | 0: High speed (higher power consumption)                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

|               | 1: Low speed (lower power consumption)                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

|               | This bit enables channel autoscan function.                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

| DI10          | 0: Autoscan disabled                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |  |

|               | 1: Autoscan enabled                                                                                                                                                                          | Into the state of |   |   |  |

|               | DI9 – DI7: These three bits select which of the eight channels is to be used (if DI10 = 0).  DI9, DI8: These two bits select the channel swept sequence used by auto scan mode (if DI10 = 1) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | Х |  |

|               | 000: Channel 0 selected as input                                                                                                                                                             | 00: Analog inputs CH0, CH1, CH2,, CH7 sequentially selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |  |

|               | 001: Channel 1 selected as input                                                                                                                                                             | 01: Analog inputs CH1, CH3, CH5, CH7 sequentially selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |  |

| DI9, DI8, DI7 | 010: Channel 2 selected as input                                                                                                                                                             | 10: Analog inputs CH0, CH2, CH4, CH6 sequentially selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |  |

| , ,           | 011: Channel 3 selected as input                                                                                                                                                             | 11: Analog inputs CH7, CH6, CH5,, CH0 sequentially selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |  |