# Application Note LDO Thermal Performance Improvements Enable Die Size Reduction

Hannah Grace, Bobby Abraham, Jorge Del Rio, Sowmya Sankaranarayanan, Keith Kunz

#### ABSTRACT

This application note covers a thermal exploration into the decreasing LDO die and package size of Texas Instruments low-dropout regulators (LDO). Additionally, an overview on thermal resistance, FET description and design, as well as LDO thermal performance are provided. This application note covers thermal resistance results of transitioning from a 2.68mm<sup>2</sup> die size to a 0.75mm<sup>2</sup> die size, otherwise viewed as a 72% decrease in die area.

## **Table of Contents**

| 1 Introduction                       | .2 |

|--------------------------------------|----|

| 2 Simulation and Measurement Results | .3 |

| 2.1 Measurements                     |    |

| 3 Summary                            |    |

| 4 References                         |    |

|                                      | -  |

#### Trademarks

All trademarks are the property of their respective owners.

## **1** Introduction

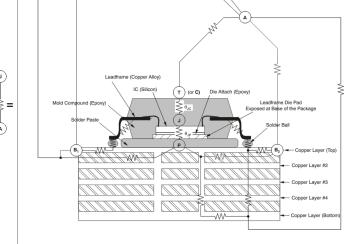

LDO package thermal limitations are a key factor when determining the functionality of a device. Many applications require a device to handle large differences between the input and output voltage, leading to a significant increase in junction temperature,  $T_J$ , due to the power dissipated,  $P_D$ , in the system. High junction temperature can affect the lifetime reliability and accelerate common failures (*LDOs Thermal Performance in Small SMD Packages*, application note). Additionally, the region of operation of the LDO can become limited due to thermal shutdown being triggered from a rise in  $T_J$ . Consequently, the device can become unable to perform as intended. Reducing the thermal resistance,  $R_{\Theta JA}$ , is critical to extending device lifetime and operation. The thermal resistance is a measure of a package's ability to dissipate heat to the ambient environment , $T_A$ , which is typically calculated using Equation 1.

$$R_{\Theta JA} = (T_J - T_A) / P_D$$

(1)

Figure 1-1. Thermal Resistance Network

Additionally, the LDO die size can contribute to thermal limitations. By spreading the same amount of heat over a smaller area, peak temperature and the resulting  $R_{\Theta JA}$  parameter can increase. A well designed die can efficiently spread heat generated by power dissipation of the LDO. In a LDO, the pass FET is the main source of heat in the device. The die helps to distribute and spread heat throughout the bulk of the silicon. Heat is then transferred to the path of least thermal resistance or the path with the highest thermal conductivity. In a package with a large thermal pad, heat flows through the silicon die to the *die attach* material. After reaching the die attach material, heat transfers to the thermal pad, and then to the PCB, where the heat finally flows to the ambient, otherwise known as the external environment.

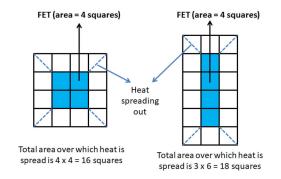

Thermal performance can also be impacted through the LDO's pass FET design. A properly laid out pass FET can maximize the FET area, perimeter, and aspect ratio to spread the heat across a larger area through the bulk of the silicon die.

#### Figure 1-2. FET Redesign to Allow for Greater Heat Dissipation

When redesigning a LDO to reduce the die size, alternate FET shapes can modify the electrical performance. The thermal performance can be optimized to make sure that the electrical performance of the LDO still meets data sheet specifications. Ultimately, the TPS74801 die area was decreased by over 72% while also maintaining the  $R_{\Theta JA}$  specification, which has allowed for an improved ability to maintain device thermal specification and accuracy.

## **2 Simulation and Measurement Results**

There are multiple properties of an LDO which influence thermal performance, including the following:

- 1. Shape and area of the pass FET

- 2. Shape and area of the die

- 3. Die thickness

- 4. Die attach thickness

- 5. Die attach conductivity

- 6. Mold compound conductivity

- 7. Metal layer deposition

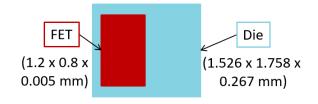

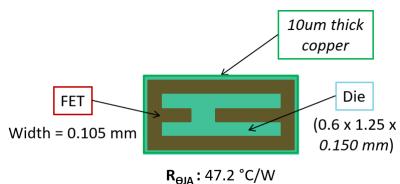

With the preceding discussion in mind, the TPS748 die (Figure 2-1) was redesigned (Figure 2-2) to reduce the die area by 72% while maintaining nearly identical thermal performance.

R<sub>014</sub>: 44.2 °C/W

Figure 2-1. Legacy Die of TPS748

For the redesigned TPS748, the die attach and mold compound were improved and incorporated into the design.

Change in R<sub>OIA</sub>: 9.2%

## Figure 2-2. New Die of TPS748

#### 2.1 Measurements

Measurements were taken using the TPS74801EVM-177 at an ambient temperature,  $T_A$ , of 25°C. Measurements were conducted comparing the legacy TPS748 design and the new TPS748 design, using test methodologies described in Measuring the Thermal Impedance of LDOs in Situ.

| Table 2-1. Legacy Die VS. New Die Thermai Performance. Vin and VBIAS – 3V |            |         |  |  |  |

|---------------------------------------------------------------------------|------------|---------|--|--|--|

| Conditions                                                                | Legacy Die | New Die |  |  |  |

| V <sub>OUT</sub>                                                          | 1.2V       | 1.2V    |  |  |  |

| I <sub>OUT</sub>                                                          | 1A         | 1A      |  |  |  |

| Power Dissipated (P <sub>D</sub> )                                        | 1.8W       | 1.8W    |  |  |  |

| Ambient Temperature (T <sub>A</sub> )                                     | 132.8°C    | 122.6°C |  |  |  |

| Table 2-1. Legacy Die vs. New Die Thermal Performance: $V_{IN}$ and $V_{BIAS}$ = 3V |  |

|-------------------------------------------------------------------------------------|--|

|-------------------------------------------------------------------------------------|--|

| Table 2-2. Legacy Die vs. New Die Thermal Performance: V <sub>IN</sub> and V <sub>BIAS</sub> = 4V |            |         |  |  |

|---------------------------------------------------------------------------------------------------|------------|---------|--|--|

| Conditions                                                                                        | Legacy Die | New Die |  |  |

| V <sub>OUT</sub>                                                                                  | 1.2V       | 1.2V    |  |  |

| I <sub>OUT</sub>                                                                                  | 1A         | 1A      |  |  |

| Power Dissipated (P <sub>D</sub> )                                                                | 2.8W       | 2.8W    |  |  |

| Ambient Temperature (T <sub>A</sub> )"                                                            | 115.3°C    | 101.9°C |  |  |

| Table 2-2. Legacy Die vs. | New Die Thermal Performance: | $V_{IN}$ and $V_{PIAS} = 4V$ |

|---------------------------|------------------------------|------------------------------|

|                           |                              |                              |

Using the following junction to ambient thermal resistance equation stated in the Measuring the Thermal Impedance of LDOs in Situ, paper:

Legacy die:

$$R_{\theta JA} = \frac{T_{A}' - T_{A}''}{P_{D}'' - P_{D}'} = \frac{132.8^{\circ}C - 115.3^{\circ}C}{(4V - 1.2V) \times 1A - (3V - 1.2V) \times 1A} = 17.5 \frac{^{\circ}C}{W}$$

(2)

New die:

$$R_{\theta JA} = \frac{T_{A}' - T_{A}''}{P_{D}'' - P_{D}'} = \frac{122.6^{\circ}C - 101.9^{\circ}C}{(4V - 1.2V) \times 1A - (3V - 1.2V) \times 1A} = 20.7 \frac{^{\circ}C}{W}$$

(3)

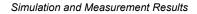

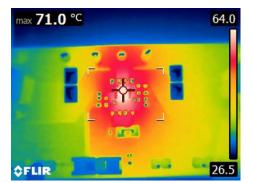

Finally, thermal camera imaging was used to measure the case temperature for both the legacy and new devices. Both devices with the VSON package were placed on the EVM. The test conditions were Vout = 1.2V, Vin = 2.2V, Vbias = 2.7V, and lout = 1.5A (for example, Power Dissipation = 1.5W), and after maintaining this for 30 minutes, thermal camera imaging was done as shown in Figure 2-3 and Figure 2-4. Maximum case temperatures were measured as 71°C and 69°C for the legacy and new device respectively.

Figure 2-3. Thermal Camera Shot Legacy TPS748 Device

Figure 2-4. Thermal Camera Shot Redesigned TPS748 Device

Now using equation 8 stated in the Semiconductor and IC Package Thermal Metrics paper,  $T_J = T_C + (\psi_{JT} x Power)$ , and  $\psi_{JT}$  values mentioned in the data sheet,  $T_J$  can be calculated as 72.05°C for the legacy die and 75.3°C for the new die.

# 3 Summary

The die reduced by 72% with only a modest change to the thermal resistance, 44.2°C/W for the legacy die versus 47.2°C/W for the new die using a JEDEC standard layout. An EVM, which represents a more accurate layout to the test methodologies stated in *Measuring the Thermal Impedance of LDOs in Situ*, was used to capture the R<sub>0JA</sub> value. The test metholodies showed similar results for R<sub>0JA</sub> between the legacy die and new die, 17.5°C/W for the legacy die versus 20.7°C/W for the new die.  $\psi$  parameters are intended to, by the JEDEC committee, accurately estimate the junction temperature given by a board thermal measurement. Thermal images were captured of the legacy and new TPS748 LDO. While using the  $\psi$ <sub>JT</sub> parameters, the junction temperature between the legacy die and 75.3°C for the new die. Ultimately, the thermal performance of the legacy and new TPS748 LDO devices are comparable.

# 4 References

- Texas Instruments, LDOs Thermal Performance in Small SMD Packages, application note.

- Texas Instruments, TPS748 1.5A, Low-Dropout Linear Regulator With Programmable Soft-Start, data sheet.

- Texas Instruments, *Semiconductor Packaging Assembly Technology*, application note.

- Texas Instruments, *Measuring the Thermal Impedance of LDOs in Situ*, application note.

- Texas Instruments, *TPS74701EVM-177, TPS74801EVM-177 Evaluation Module*.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated