# MSC121x Precision ADC and DACs with 8051 Microcontroller and Flash Memory

User's Guide

March 2007 Data Acquisition

SBAU101A

# **Contents**

| Prefa | ce          |                                                   | . 9 |

|-------|-------------|---------------------------------------------------|-----|

| 1     | Intro       | duction                                           | 11  |

|       | 1.1         | MSC121x Description                               | 12  |

|       | 1.2         | MSC121x Pinout                                    | 14  |

|       |             | 1.2.1 Input/Output (I/O) Ports—P0, P1, P2, and P3 | 17  |

|       |             | 1.2.2 Oscillator XOUT (pin 1) and XIN (pin 2)     | 20  |

|       |             | 1.2.3 Reset Line—RST (pin 13)                     | 20  |

|       |             | 1.2.4 Address Latch Enable—ALE (pin 45)           | 20  |

|       |             | 1.2.5 Program Store Enable—PSEN (pin 44)          | 20  |

|       |             | 1.2.6 External Access—EA (pin 48)                 | 20  |

|       | 1.3         | Enhanced 8051 Core                                | 21  |

|       | 1.4         | Family Compatibility                              | 22  |

|       | 1.5         | Flash Memory                                      | 22  |

|       | 1.6         | Internal SRAM                                     | 22  |

|       | 1.7         | High-Performance Analog Functions                 | 22  |

|       | 1.8         | High-Performance Peripherals                      | 22  |

| 2     | MSC         | 121x Addressable Resources                        | 23  |

|       | 2.1         | Introduction                                      | 24  |

|       | 2.2         | Program Memory and Data Memory                    | 25  |

|       | 2.3         | Scratchpad RAM and Special Function Registers     | 27  |

|       | 2.4         | Beyond 64K Bytes                                  | 28  |

| 3     | Spec        | ial Function Registers                            | 29  |

|       | 3.1         | Introduction                                      |     |

|       | 3.2         | Referencing SFRs in Assembly and C Languages      | 31  |

|       | 3.3         | SFR Types                                         |     |

|       | 3.4         | SFR Overview                                      |     |

| 4     | Prog        | rammer's Model and Instruction Set                | 39  |

| •     | 4.1         | Introduction                                      |     |

|       | 4.2         | Registers                                         |     |

|       | 4.3         | Instruction Types and Addressing Modes            |     |

|       | 4.4         | MSC121x Op-Code Table                             |     |

|       | 4.5         | Example of MSC121x Instructions                   |     |

| 5     | Syste       | em Clocks, Timers, and Functions                  |     |

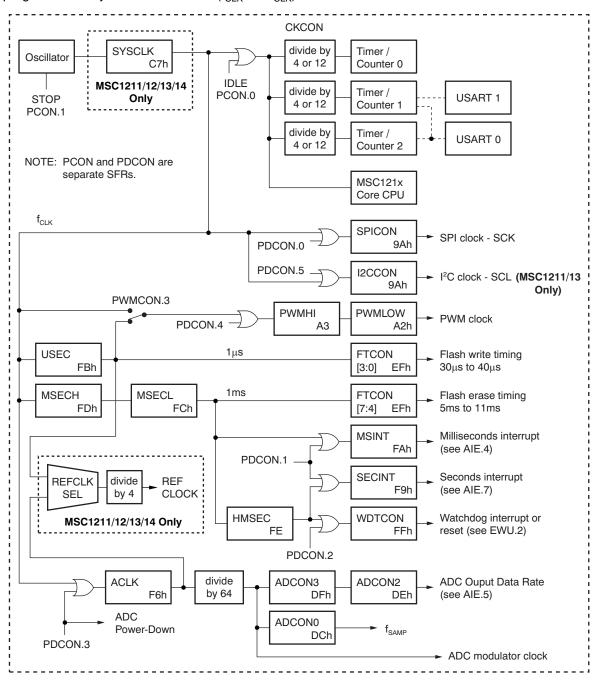

|       | 5.1         | Timing Chain and Clock Controls                   |     |

|       | 5.2         | System Clock Divider (MSC1211/12/13/14)           |     |

|       | V. <u> </u> | 5.2.1 Behavior in Delay Mode (DIVMOD = '10')      |     |

|       | 5.3         | Watchdog Timer                                    |     |

|       | 0.0         | 5.3.1 Watchdog Timer Example Program              |     |

|       | 5.4         | Low-Voltage Detection.                            |     |

|       | 5.5         | Hardware Configuration                            |     |

|       | 5.6         | Breakpoints                                       |     |

| 6     |             | pg-To-Digital Converters                          |     |

| U     | Ailai       | 29-10-Digital Collecters                          | บง  |

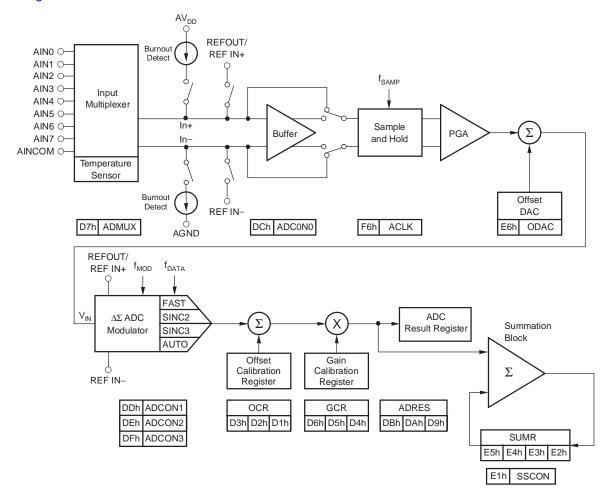

|    | 6.1                    | ADC Functional Blocks                                              | 64  |

|----|------------------------|--------------------------------------------------------------------|-----|

|    | 6.2                    | ADC Signal Flow and General Description                            | 65  |

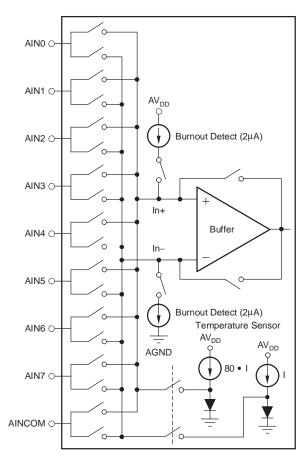

|    | 6.3                    | Analog Input Stage                                                 |     |

|    | 6.4                    | Input Impedance, PGA, and Voltage References                       | 67  |

|    | 6.5                    | Offset DAC                                                         |     |

|    | 6.6                    | ADC Data Rate, Filters, and Calibration                            |     |

|    | 6.7                    | 32-Bit Summation Register                                          |     |

|    | 6.8                    | Accessing the ADC Multi-Byte Conversion in C                       |     |

|    | 6.9                    | ADC Example Program                                                |     |

| 7  | Digita                 | al-To-Analog Converters                                            |     |

| •  | 7.1                    | Introduction                                                       |     |

|    | 7.1                    | DAC Selection                                                      |     |

|    | 7.3                    | DAC Configuration and Control                                      |     |

|    | 7.3<br>7.4             | DAC Technology and Limitations                                     |     |

|    | 7. <del>4</del><br>7.5 | DAC Example Program                                                |     |

|    | _                      |                                                                    |     |

| 8  |                        | e-Width Modulator and Tone Generator                               |     |

|    | 8.1                    | Description                                                        |     |

|    | 8.2                    | PWM Generator Example                                              | 87  |

| 9  | Inter-                 | IC (I <sup>2</sup> C™) Subsystem                                   | 89  |

|    | 9.1                    | Introduction to the I <sup>2</sup> C Bus                           | 90  |

|    | 9.2                    | I <sup>2</sup> C Terminology                                       | 90  |

|    | 9.3                    | I <sup>2</sup> C Bus Lines and Basic Timing                        | 91  |

|    | 9.4                    | I <sup>2</sup> C Data Transfers and the Acknowledge Bit            | 92  |

|    | 9.5                    | I <sup>2</sup> C Principal Registers                               | 93  |

|    | 9.6                    | I <sup>2</sup> C Related Registers                                 | 96  |

|    | 9.7                    | I <sup>2</sup> C Example—MSC1211/13 as a Master                    | 97  |

|    | 9.8                    | I <sup>2</sup> C Example—MSC1211/13 as a Slave                     | 99  |

|    | 9.9                    | I <sup>2</sup> C Example—MSC1211/13 as an Interrupt-Driven Slave   | 100 |

|    | 9.10                   | I <sup>2</sup> C Synchronization and Arbitration                   | 101 |

|    | 9.11                   | I <sup>2</sup> C Fast Mode                                         | 101 |

|    | 9.12                   | I <sup>2</sup> C General Call                                      | 101 |

|    | 9.13                   | I <sup>2</sup> C 10-Bit Addressing                                 | 102 |

| 10 | Seria                  | l Peripheral Interface (SPI™)                                      | 103 |

|    | 10.1                   | ·                                                                  | 104 |

|    | 10.2                   | ·                                                                  | 104 |

|    | 10.3                   | -                                                                  | 107 |

|    | 10.4                   |                                                                    | 108 |

|    | 10.5                   | SPI Examples                                                       |     |

| 11 |                        | rs and Counters                                                    |     |

| 11 |                        |                                                                    |     |

|    | 11.1                   | Description                                                        |     |

|    | 11.2                   | Timer/Counters 0 and 1                                             |     |

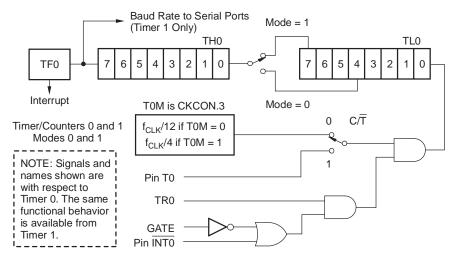

|    |                        |                                                                    | 116 |

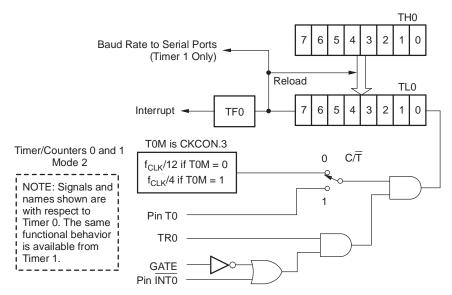

|    |                        |                                                                    | 117 |

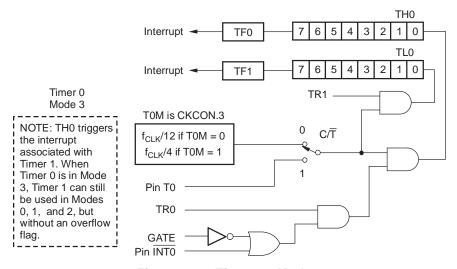

|    |                        | 11.2.3 Mode 3                                                      |     |

|    | , .                    | 11.2.4 Summary of Control Bits and SFRs for Timer/Counters 0 and 1 |     |

|    | 11.3                   |                                                                    | 119 |

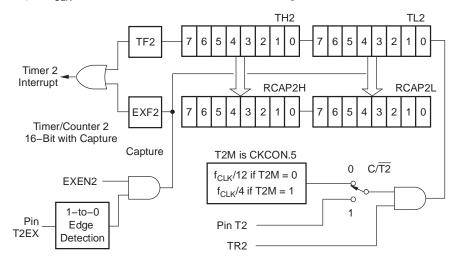

|    |                        | 11.3.1 16-Bit Timer/Counter with Optional Capture                  | 120 |

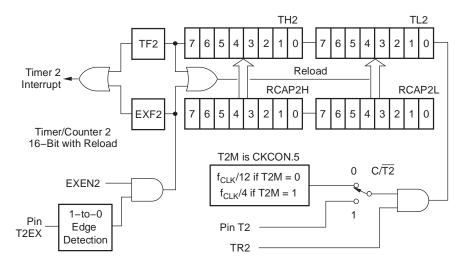

|      |         | 11.3.2 16-Bit Timer/Counter with Automatic and Forced Reload | 21 |

|------|---------|--------------------------------------------------------------|----|

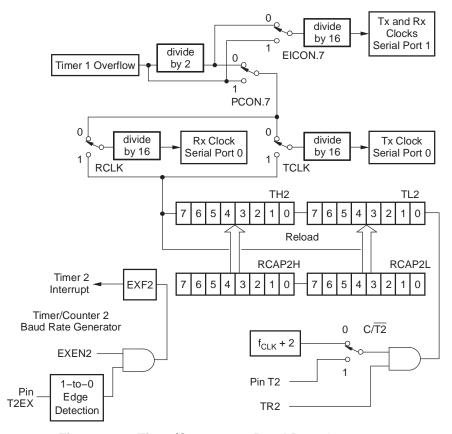

|      |         | 11.3.3 Baud Rate Generator                                   | 22 |

|      |         | 11.3.4 Summary of Timer/Counter 2 Mode Control               | 23 |

|      |         | 11.3.5 Summary of Control Bits and SFRs for Timer/Counter 2  |    |

|      |         | 11.3.6 Summary of Timer Modes                                |    |

|      | 11.4    | Example Program Using Timers 0, 1, and 2                     | 24 |

| 12   | Seria   | Ports (USART0 and USART1)12                                  | 25 |

|      | 12.1    | Description                                                  |    |

|      | 12.2    | Control Bits in SCON0 and SCON1                              | 26 |

|      | 12.3    | Pin and Interrupt Assignments 12                             | 27 |

|      | 12.4    | Timer/Counters 1 and 2 Baud Rate Generation                  | 27 |

|      | 12.5    | Mode 0—8-Bit Synchronous 12                                  | 29 |

|      | 12.6    | Mode 1—10-Bit Asynchronous                                   | 30 |

|      | 12.7    | Modes 2 and 3—11-Bit Asynchronous                            | 31 |

|      | 12.8    | Multiprocessor Communications                                | 32 |

|      | 12.9    | Example Program                                              | 32 |

| 13   | Interr  | pts                                                          | 35 |

|      | 13.1    | Description                                                  | 36 |

|      | 13.2    | Standard and Extended Interrupts                             | 37 |

|      | 13.3    | Auxiliary Interrupt Sources                                  | 39 |

|      | 13.4    | Multiple Interrupts14                                        | 40 |

|      | 13.5    | Example of Multiple and Nested Interrupts14                  | 40 |

|      | 13.6    | Example of Wake Up from Idle                                 | 43 |

| Revi | sion Hi | tory 14                                                      | 45 |

|      |         |                                                              |    |

# **List of Figures**

| 1-1  | MSC121x Block Diagram                                             |      |

|------|-------------------------------------------------------------------|------|

| 1-2  | MSC121x Pin Configuration                                         |      |

| 1-3  | Standard 8051 I/O Pin Structure                                   |      |

| 1-4  | CMOS Output Pin Structure                                         |      |

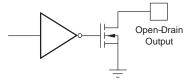

| 1-5  | Open-Drain Output Pin Structure                                   |      |

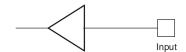

| 1-6  | Input Pin Structure                                               |      |

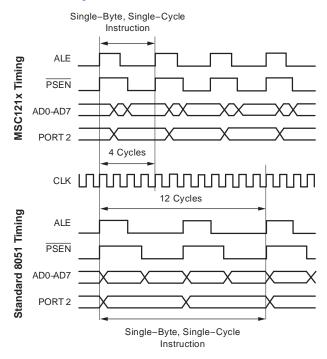

| 1-7  | Comparison of MSC121x Timing to Standard 8051 Timing              |      |

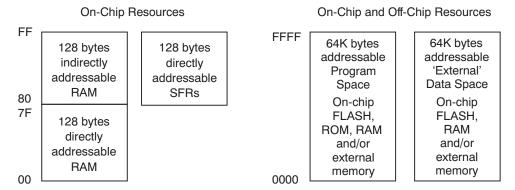

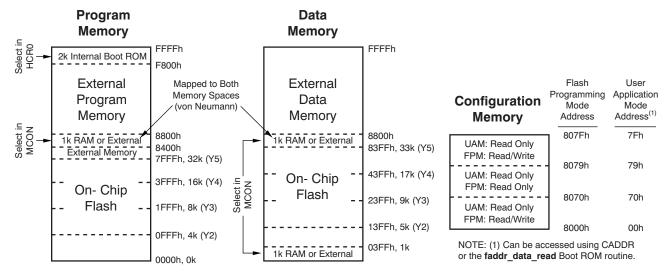

| 2-1  | On-Chip and Off-Chip Resources                                    |      |

| 2-2  | Memory Map                                                        |      |

| 5-1  | MSC121x Timing Chain and Clock Control                            |      |

| 6-1  | ADC Subsystem Elements                                            |      |

| 6-2  | Input Multiplexer Configuration                                   |      |

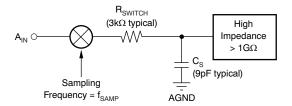

| 6-3  | Analog Input Structure without Buffer                             | . 67 |

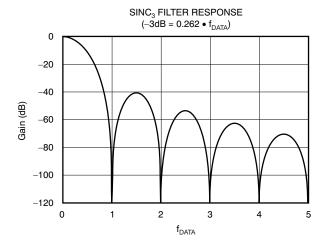

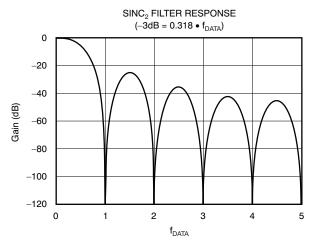

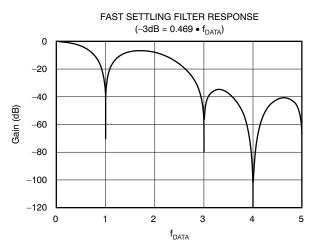

| 6-4  | Filter Frequency Responses                                        | . 71 |

| 7-1  | DAC Architecture                                                  | . 80 |

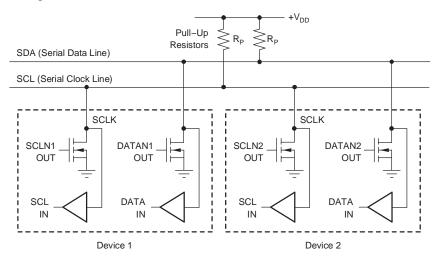

| 9-1  | I <sup>2</sup> C Bus Connection of Standard and Fast Mode Devices | . 91 |

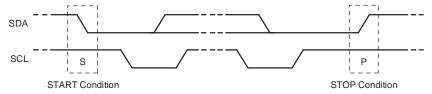

| 9-2  | START and STOP Conditions                                         | . 91 |

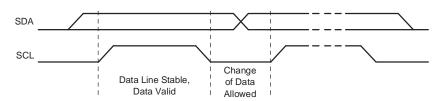

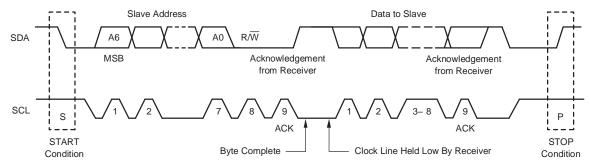

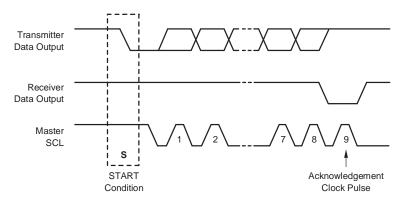

| 9-3  | I <sup>2</sup> C-Bus Bit Transfer                                 | . 91 |

| 9-4  | I <sup>2</sup> C-Bus Data Transfer                                | . 92 |

| 9-5  | I <sup>2</sup> C Acknowledge                                      | . 92 |

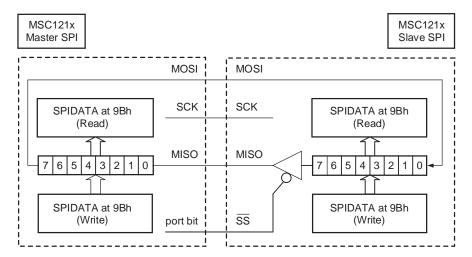

| 10-1 | SPI Master/Slave Interconnect                                     | 104  |

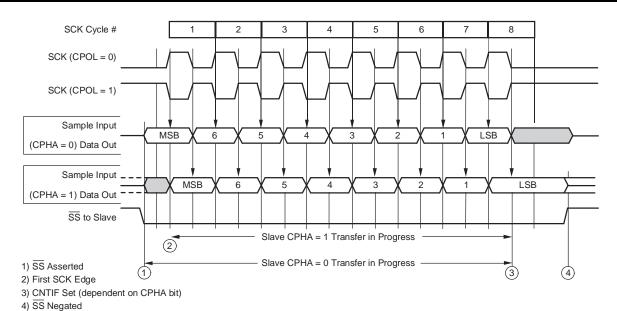

| 10-2 | SPI Clock/Data Timing                                             | 106  |

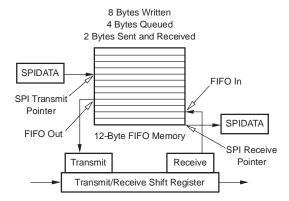

| 10-3 | SPI FIFO Operation                                                | 108  |

| 11-1 | Timer 0/1—Modes 0 and 1                                           | 116  |

| 11-2 | Timer 0/1—Mode 2                                                  | 117  |

| 11-3 | Timer 0—Mode 3                                                    | 117  |

| 11-4 | Timer/Counter 2—16-Bit with Capture                               | 120  |

| 11-5 | Timer/Counter 2—16-Bit with Reload                                | 121  |

| 11-6 | Timer/Counter 2—Baud Rate Generator                               | 122  |

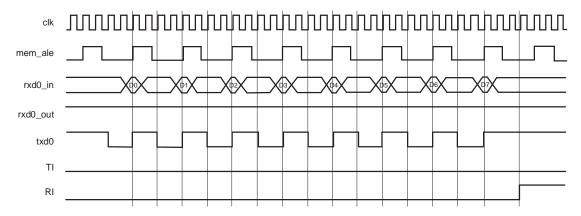

| 12-1 | Synchronous Receive at f <sub>CLK</sub> /4                        | 129  |

| 12-2 | Synchronous Transmit at f <sub>CLK</sub> /4                       | 129  |

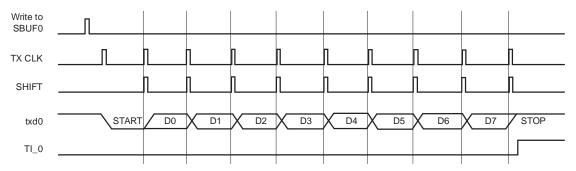

| 12-3 | Asynchronous 10-Bit Transmit Timing                               |      |

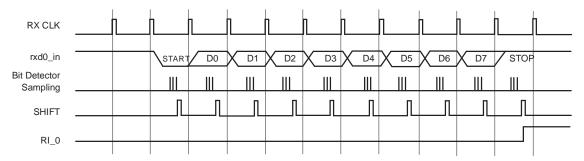

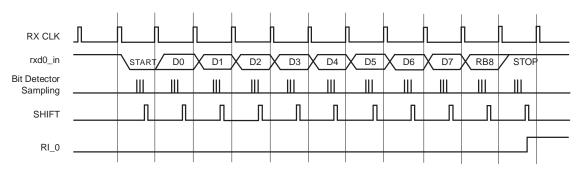

| 12-4 | Asynchronous 10-Bit Receive Timing                                |      |

| 12-5 | Asynchronous 11-Bit Receive                                       |      |

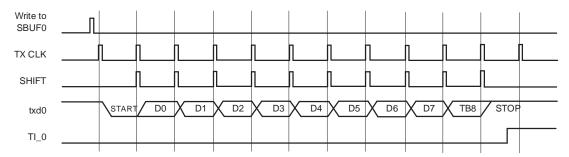

| 12-6 | Asynchronous 11-Bit Transmit                                      |      |

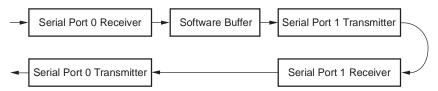

| 12-7 | Serial Port with Software Buffer.                                 |      |

| 13-1 | Interrupts                                                        |      |

# **List of Tables**

| 1-1  | MSC121x Product Family Matrix                                       | . 13 |

|------|---------------------------------------------------------------------|------|

| 1-2  | Pin Descriptions                                                    | . 15 |

| 1-3  | Port 1 Alternate Functions                                          | . 18 |

| 1-4  | Port 3 Alternate Functions                                          | . 19 |

| 2-1  | Program Memory and External Data Memory Addresses                   | . 25 |

| 2-2  | MSC121x Flash Memory Partitioning and Addresses                     | . 26 |

| 2-3  | On-Chip 8051 Memory                                                 | . 27 |

| 3-1  | Special Function Register Map                                       | . 30 |

| 3-2  | SFR Overview                                                        | . 32 |

| 4-1  | 8051 Working Registers                                              | . 41 |

| 4-2  | Symbol Descriptions for Instruction List of Table 4-3               | . 42 |

| 4-3  | Instruction List                                                    |      |

| 4-4  | MSC121x Op-Codes                                                    | . 46 |

| 5-1  | SYSCLK—System Clock Divider Register                                | . 54 |

| 5-2  | Watchdog Control Bits                                               | . 55 |

| 5-3  | LVDCON—Low-Voltage Detect Control                                   | . 57 |

| 5-4  | Low-Voltage Detect                                                  | . 57 |

| 5-5  | HCR0—Hardware Configuration Register 0                              | . 58 |

| 5-6  | HCR1—Hardware Configuration Register 1                              | . 59 |

| 5-7  | MCON—Memory Control                                                 | . 60 |

| 5-8  | BPCON—Breakpoint Control                                            | . 60 |

| 5-9  | BPL—Breakpoint Low Address for BP Register Selected in MCON at 95h  | . 61 |

| 5-10 | BPH—Breakpoint High Address for BP Register Selected in MCON at 95h |      |

| 5-11 | Breakpoints                                                         |      |

| 6-1  | ADMUX—ADC Multiplexer                                               |      |

| 6-2  | Impedance Divisor (G) for a Given PGA                               | . 67 |

| 6-3  | ADCON0—ADC Control Register 0                                       |      |

| 6-4  | ADCON0 PGA Bit Parameters                                           |      |

| 6-5  | ADCON1—ADC Control Register 1                                       |      |

| 6-6  | ADC Interrupt Controls                                              |      |

| 6-7  | Summation Register                                                  |      |

| 6-8  | SSCON—Summation/Shift Control                                       |      |

| 6-9  | Summation Interrupt Controls                                        |      |

| 7-1  | DACSEL Values                                                       | . 81 |

| 7-2  | LOADCON SFR                                                         |      |

| 7-3  | DxLOAD Output Modes for DACx                                        |      |

| 7-4  | DAC Control Registers                                               |      |

| 8-1  | PWMCON—PWM Control                                                  |      |

| 8-2  | PWM Output                                                          |      |

| 9-1  | I <sup>2</sup> C Terminology                                        |      |

| 9-2  | I2CCON—I <sup>2</sup> C Control Register                            |      |

| 9-3  | I2CDATA SFR                                                         |      |

| 9-4  | I2CGM—I <sup>2</sup> C General Call / Multiple Master Control       |      |

| 9-5  | I2CSTAT SFR                                                         |      |

| 9-6  | I <sup>2</sup> C Status Codes                                       |      |

| 9-7  | PDCON of I <sup>2</sup> C and SPI                                   |      |

| 9-8  | Interrupt Control for I <sup>2</sup> C                              |      |

| 9-9  | Address Allocation                                                  |      |

| 10-1 | SPICON—SPI Control                                                  | 105  |

| 10-2  | P1—Port 1                                                      | 105 |

|-------|----------------------------------------------------------------|-----|

| 10-3  | P1DDRH—Port 1 Data Direction Register                          | 105 |

| 10-4  | SPIDATA—SPI Data Register                                      | 106 |

| 10-5  | SPI Interrupts Have Highest Priority and Jump to Address 0033h | 107 |

| 10-6  | PAI—Pending Auxiliary Interrupt Register                       | 107 |

| 10-7  | SPISTART—SPI Buffer Start Address                              | 109 |

| 10-8  | SPISEND—SPI Buffer End Address                                 | 109 |

| 10-9  | SPIRCON—SPI Receive Control Register                           | 110 |

| 10-10 | SPITCON—SPI Transmit Control Register                          | 110 |

| 11-1  | TMOD—Timer Mode Control                                        | 114 |

| 11-2  | TCON—Timer/Counter Control                                     | 115 |

| 11-3  | Modes 0 and 1 Operation                                        | 116 |

| 11-4  | Control Bit and SFR Summary for Timer/Counters 0 and 1         | 118 |

| 11-5  | T2CON—Timer 2 Control                                          | 119 |

| 11-6  | Mode Control Summary for Timer/Counter 2                       | 123 |

| 11-7  | Control Bit and SFR Summary for Timer/Counter 2                | 123 |

| 11-8  | Timer Modes                                                    | 123 |

| 12-1  | SCON0 and SCON1—Serial Port 0 and Serial Port 1 Control        | 126 |

| 12-2  | USART Pin and Interrupt Assignments                            | 127 |

| 12-3  | Timer/Counter 2 Baud Rate Generation                           | 127 |

| 12-4  | Timer/Counter 1 Baud Rate Generation                           | 127 |

| 12-5  | USART Baud Rate Generation                                     | 128 |

| 13-1  | Standard and Extended Interrupts                               | 137 |

| 13-2  | Auxiliary Interrupts with Highest Group Priority               | 139 |

| 13-3  | EWU—Enable Wake Up                                             | 143 |

|       |                                                                |     |

#### **About This Manual**

This user's guide describes the function and operation of the MSC121x family of precision ADC and DACs with 8051 microcontroller and flash memory.

This document applies to the following MSC devices:

- MSC1210

- MSC1211

- MSC1212

- MSC1213

- MSC1214

For convenience, the abbreviation MSC121x is used to indicate all of the MSC devices listed in this user's guide, unless otherwise specified.

#### **Related Documentation and Tools From Texas Instruments**

| Data Sheets                       | Literature Number         |

|-----------------------------------|---------------------------|

| MSC1210                           | SBAS203                   |

| MSC1211                           | SBAS323                   |

| MSC1212                           | SBAS323                   |

| MSC1213                           | SBAS323                   |

| MSC1214                           | SBAS323                   |

|                                   | 32.13323                  |

| User's Guides                     | Literature Number         |

|                                   |                           |

| User's Guides                     | Literature Number         |

| User's Guides  MSC120x User Guide | Literature Number SBAU112 |

For a complete list of application notes and related documentation, see the MSC web site at www.ti.com/msc.

#### **Trademarks**

I<sup>2</sup>C is a trademark of NXP Semiconductors.

SPI is a trademark of Motorola Inc.

All other trademarks are the property of their respective owners.

# Introduction

This chapter provides a functional overview of the MSC121x precision analog-to-digital converter (ADC) and digital-to-analog converters (DACs) with 8051 microcontroller and flash memory.

| • | Topic |                                   | Page      |

|---|-------|-----------------------------------|-----------|

|   |       |                                   |           |

|   | 1.1   | MSC121x Description               | 12        |

|   | 1.2   | MSC121x Pinout                    | 14        |

|   | 1.3   | Enhanced 8051 Core                | <b>21</b> |

|   | 1.4   | Family Compatibility              | 22        |

|   | 1.5   | Flash Memory                      | 22        |

|   | 1.6   | Internal SRAM                     | 22        |

|   | 1.7   | High-Performance Analog Functions | 22        |

|   | 1.8   | High-Performance Peripherals      | 22        |

|   |       |                                   |           |

#### 1.1 MSC121x Description

The MicroSystem family of devices is designed for high-resolution measurement applications in smart transmitters, industrial process control, weigh scales, chromatography, and portable instrumentation. They provide cost-effective, high-performance, mixed-signal solutions. The MicroSystem family not only includes high-performance analog features and digital processing capability, but also integrates many digital peripherals to offer a unique and effective system solution.

The main components of a MicroSystem product include:

- High-performance analog functions

- Low-power enhanced 8051 microcontroller core

- RAM and Flash memory

- · High-performance digital peripherals

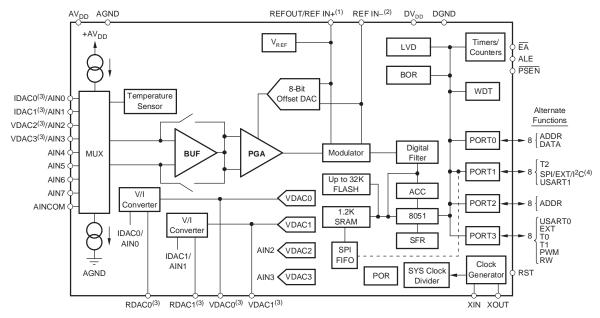

The enhanced 8051 microcontroller includes dual data pointers and executes most instructions up to three times faster than a standard 8051 core. This increased execution speed provides greater flexibility in applications requiring a trade-off among speed, power and noise. A block diagram is shown in Figure 1-1.

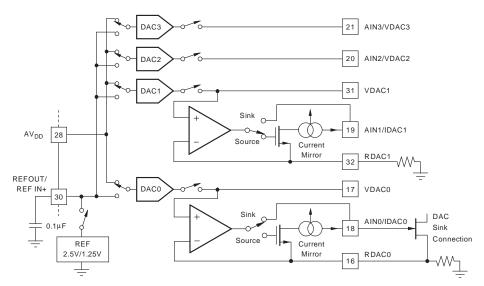

NOTES: (1) On the MSC1210, the REF IN + (pin 30) and REFOUT (pin 31) functions are split onto two pins. On the MSC1211/12/13/14, REFOUT and REF IN+ are combined onto pin 30, and the VDAC1 output is on pin 31.

- (2) REF IN- must be tied to AGND when using internal V<sub>RFF</sub>.

- (3) DAC functions are only available on the MSC1211/12/13/14.

- (4) I<sup>2</sup>C is available only on the MSC1211 and MSC1213.

Figure 1-1. MSC121x Block Diagram

For some designers, the MSC121x is viewed as a microcontroller with integrated analog functions, while to others it is a high-performance analog-to-digital converter (ADC) with an integrated microcontroller. The MSC121x provides unparalleled analog and digital integration for all designers who are concerned with embedded instrumentation and control.

Complementing the high-resolution ADC are a precision voltage reference, programmable gain amplifier (PGA), and analog multiplexer (mux), as well as a temperature sensor and low voltage detectors.

Apart from numerous bit-wise programmable digital ports, there are two USARTs, three timer/counters, a watchdog timer, and a serial (SPI<sup>TM</sup>) bus. Up to 32k of FLASH memory and 1.2K RAM are included as well. The MSC1211/13 also support I<sup>2</sup>C serial transfers.

Taken together, the MSC121x features blend analog and digital functions to significantly simplify the overall system design, which reduces the design time and board space as well as the need for external components.

For systems requiring additional memory, address and data lines are provided via multifunction I/O ports.

Table 1-1 compares the basic features and functionality of the MSC121x family.

Table 1-1. MSC121x Product Family Matrix

|                                                                                                                           | • • • • • • • • • • • • • • • • • • • •                            |                                                                                                      |                                                                                       |                                                                                                      |                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|                                                                                                                           | MSC1210                                                            | MSC1211                                                                                              | MSC1212                                                                               | MSC1213                                                                                              | MSC1214                                                                               |

| Clock Frequency<br>(kB)                                                                                                   | 33                                                                 | 33                                                                                                   | 33                                                                                    | 33                                                                                                   | 33                                                                                    |

| Flash Memory<br>(kB)                                                                                                      | 32                                                                 | 32                                                                                                   | 32                                                                                    | 32                                                                                                   | 32                                                                                    |

| SRAM<br>(kB)                                                                                                              | 1.2                                                                | 1.2                                                                                                  | 1.2                                                                                   | 1.2                                                                                                  | 1.2                                                                                   |

| ADC<br>(Channel x Resolution)                                                                                             | 8 × 24                                                             | 8 × 24                                                                                               | 8 × 24                                                                                | 8 × 24                                                                                               | 8 × 24                                                                                |

| DAC<br>(Channel x Resolution)                                                                                             | N/A                                                                | Quad Voltage / Dual<br>Current x 16                                                                  | Quad Voltage / Dual<br>Current x 16                                                   | Dual Voltage / Dual<br>Current x 16                                                                  | Dual Voltage / Dual<br>Current x 16                                                   |

| Features: 32-Bit Accumulator Internal V <sub>REF</sub> Internal PGA Internal Buffer SPI Brownout Reset Low-Voltage Detect | 34 I/O External Memory Dual USARTs - Serial/Parallel Programming - | 34 I/O External Memory Dual USARTs I <sup>2</sup> C Serial/Parallel Programming System Clock Divider | 34 I/O External Memory Dual USARTs - Serial/Parallel Programming System Clock Divider | 34 I/O External Memory Dual USARTs I <sup>2</sup> C Serial/Parallel Programming System Clock Divider | 34 I/O External Memory Dual USARTs - Serial/Parallel Programming System Clock Divider |

| Package                                                                                                                   | TQFP-64                                                            | TQFP-64                                                                                              | TQFP-64                                                                               | TQFP-64                                                                                              | TQFP-64                                                                               |

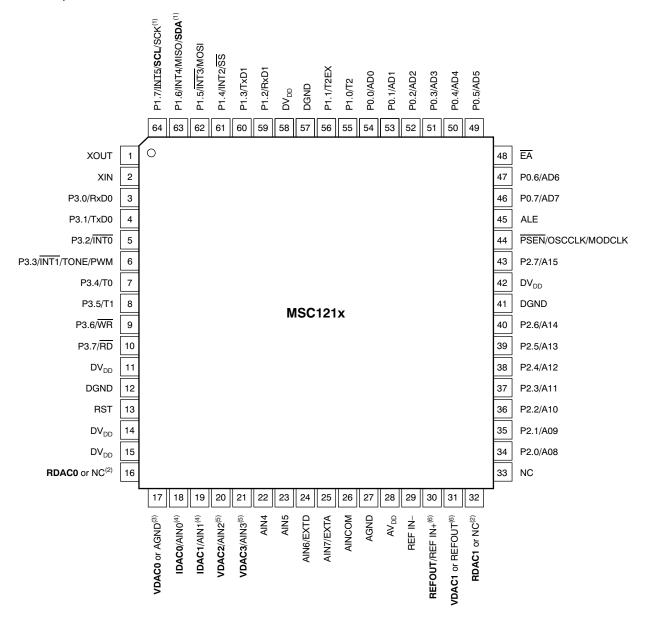

#### 1.2 MSC121x Pinout

The names and functions of pins are similar to those found on most 8051-compatible devices, but with extensions that are specific to the MSC121x. The pin configuration is shown in Figure 1-2, and the pin descriptions are listed in Table 1-2.

NOTES: Non-bolded pin names are on MSC1210.

- (1) SCL and SDA not present on MSC1210/12/14.

- (2) Pins 16 and 32 are not connected (NC) on MSC1210.

- (3) AGND for MSC1210; VDAC0 for MSC1211/12/13/14.

- (4) IDAC0 and IDAC1 on MSC1211/12/13/14.

- (5) VDAC2 and VDAC3 on MSC1211/12.

- (6) For MSC1210, REFOUT is on pin 31. For MSC1211/12/13/14, REFOUT is shared with REF IN+ on pin 30, and VDAC1 is on pin 31.

Figure 1-2. MSC121x Pin Configuration

## **Table 1-2. Pin Descriptions**

| Pin #              | Name             | Description                                                                                         |                                       |                                             |  |  |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------|--|--|

| 1                  | XOUT             | The output of an oscillator that supports parallel resonant AT-cut crystals and ceramic resonators. |                                       |                                             |  |  |

| 2                  | XIN              | The input to the crystal oscillator that can also be used as an external clock input.               |                                       |                                             |  |  |

| 3-10               | P3.0-P3.7        | Port 3 is an 8-bit bidirectional Input/Output port with alternate functions.                        |                                       |                                             |  |  |

|                    |                  | Port 3.x                                                                                            | Alternate Name(s)                     | Alternate Use                               |  |  |

|                    |                  | P3.0                                                                                                | RxD0                                  | Serial port 0 input                         |  |  |

|                    |                  | P3.1                                                                                                | TxD0                                  | Serial port 0 output                        |  |  |

|                    |                  | P3.2                                                                                                | ĪNT0                                  | External Interrupt 0                        |  |  |

|                    |                  | P3.3                                                                                                | INT1/TONE/PWM                         | External interrupt 1/TONE/PWM output        |  |  |

|                    |                  | P3.4                                                                                                | T0                                    | Timer 0 input                               |  |  |

|                    |                  | P3.5                                                                                                | T1                                    | Timer 1 input                               |  |  |

|                    |                  | P3.6                                                                                                | WR                                    | External data memory write strobe           |  |  |

|                    |                  | P3.7                                                                                                | RD                                    | External data memory read strobe            |  |  |

| 11, 14, 15, 42, 58 | DV <sub>DD</sub> | Digital power supp                                                                                  | olies. All must be used.              |                                             |  |  |

| 12, 41, 57         | DGND             | Digital grounds. A                                                                                  | Il must be used.                      |                                             |  |  |

| 13                 | RST              |                                                                                                     | et input for two clock cycles re      | sets the device.                            |  |  |

|                    |                  | Base MSC1210 F                                                                                      | · · · · · · · · · · · · · · · · · · · | Alternate or Additional in MSC1211/12/13/14 |  |  |

| 16                 | NC               | No connection                                                                                       |                                       | RDAC0 (MSC1211/12/13/14 only)               |  |  |

| 17                 | AGND             | Analog ground                                                                                       |                                       | VDAC0 (MSC1211/12/13/14 only)               |  |  |

| 18                 | AIN0             | Analog input char                                                                                   | inel 0 = AIN0                         | AIN0 and IDAC0 (MSC1211/12/13/14 only)      |  |  |

| 19                 | AIN1             | Analog input char                                                                                   | nel 1 = AIN1                          | AIN1 and IDAC1 (MSC1211/12/13/14 only)      |  |  |

| 20                 | AIN2             | Analog input char                                                                                   | nel 2 = AIN2                          | AIN2 and VDAC2 (MSC1211/12 only)            |  |  |

| 21                 | AIN3             | Analog input channel 3 = AIN3                                                                       |                                       | AIN3 and VDAC3 (MSC1211/12 only)            |  |  |

| 22                 | AIN4             | <u> </u>                                                                                            |                                       | Same                                        |  |  |

| 23                 | AIN5             | Analog input char                                                                                   | inel 5 = AIN5                         | Same                                        |  |  |

| 24                 | AIN6, EXTD       | Analog input char detect input                                                                      | nel 6 = AIN6 and digital low v        | oltage Same                                 |  |  |

| 25                 | AIN7, EXTA       | Analog input char detect input                                                                      | nel 7 = AIN7 and analog low           | voltage Same                                |  |  |

| 26                 | AINCOM           | Analog common f                                                                                     | or single-ended inputs                | Same                                        |  |  |

| 27                 | AGND             | Analog ground                                                                                       |                                       | Same                                        |  |  |

| 28                 | $AV_{DD}$        | Analog power sup                                                                                    | pply                                  | Same                                        |  |  |

| 29                 | REF IN-          | Voltage reference                                                                                   | negative input                        | Same                                        |  |  |

| 30                 | REF IN +         | Voltage reference                                                                                   | positive input                        | REFOUT/REF IN+                              |  |  |

| 31                 | REFOUT           | Voltage reference                                                                                   | output                                | VDAC1 (MSC1211/12/13/14 only)               |  |  |

| 32                 | NC               | No connection                                                                                       | ·                                     | RDAC1 (MSC1211/12/13/14 only)               |  |  |

| 33                 | NC               | No connection                                                                                       |                                       | Same                                        |  |  |

| 34-40, 43          | P2.0-P2.7        |                                                                                                     | pidirectional input/output port v     |                                             |  |  |

| ,                  |                  | Port 2.x                                                                                            | Alternate Name                        | Alternate Use                               |  |  |

|                    |                  | P2.0                                                                                                | A8                                    | Address bit 8                               |  |  |

|                    |                  | P2.1                                                                                                | A9                                    | Address bit 9                               |  |  |

|                    |                  | P2.2                                                                                                | A10                                   | Address bit 10                              |  |  |

|                    |                  | P2.3                                                                                                | A11                                   | Address bit 11                              |  |  |

|                    |                  | P2.4                                                                                                | A12                                   | Address bit 12                              |  |  |

|                    |                  | P2.5                                                                                                | A13                                   | Address bit 13                              |  |  |

|                    |                  | P2.6                                                                                                | A14                                   | Address bit 14                              |  |  |

|                    |                  | . 2.0                                                                                               | 7311                                  | / Iddi ooo bit 11                           |  |  |

### **Table 1-2. Pin Descriptions (continued)**

| Pin #         | Name                                    | Description                                                                                                                                                                                                                                                                                                                                                              |                                     |                                   |  |  |

|---------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------|--|--|

| 44            | PSEN, OSCCLK,<br>MODCLK, Low or<br>High | Program store enable. Connected to optional external memory as a chip enable. PSEN provides an active low pulse. It is used in conjunction with RST and ALE to define serial or parallel programming mode. When not using external program memory, this pin can also be selected to output the oscillator clock, ADC modulator clock, low or high. (See SFR PASEL, F2h.) |                                     |                                   |  |  |

|               |                                         | ALE                                                                                                                                                                                                                                                                                                                                                                      | PSEN                                | Program Mode Selection (at reset) |  |  |

|               |                                         | NC                                                                                                                                                                                                                                                                                                                                                                       | NC                                  | Normal operation                  |  |  |

|               |                                         | 0                                                                                                                                                                                                                                                                                                                                                                        | 1                                   | Parallel programming of FLASH     |  |  |

|               |                                         | 1                                                                                                                                                                                                                                                                                                                                                                        | 0                                   | Serial Programming of FLASH       |  |  |

|               |                                         | 0                                                                                                                                                                                                                                                                                                                                                                        | 0                                   | Reserved                          |  |  |

| 45            | ALE, Low or High                        | Address latch enable. Used for latching the low byte of the address during an access to external memory. (See PSEN and SFR PASEL, F2h.)                                                                                                                                                                                                                                  |                                     |                                   |  |  |

| 48            | EA                                      | If EA is low as RST falls, and neither ALE nor PSEN is low (see above), code access will always be to external memory starting at address 0000h. Otherwise, internal program memory will be accessed where available.                                                                                                                                                    |                                     |                                   |  |  |

| 46, 47, 49-54 | P0.0-P0.7                               | Port 0 is an 8-bit                                                                                                                                                                                                                                                                                                                                                       | t bidirectional input/output port w | rith alternate functions.         |  |  |

|               |                                         | Port 0.x                                                                                                                                                                                                                                                                                                                                                                 | Alternate Name                      | Alternate Use                     |  |  |

|               |                                         | P0.0                                                                                                                                                                                                                                                                                                                                                                     | AD0                                 | Address/Data bit 0                |  |  |

|               |                                         | P0.1                                                                                                                                                                                                                                                                                                                                                                     | AD1                                 | Address/Data bit 1                |  |  |

|               |                                         | P0.2                                                                                                                                                                                                                                                                                                                                                                     | AD2                                 | Address/Data bit 2                |  |  |

|               |                                         | P0.3                                                                                                                                                                                                                                                                                                                                                                     | AD3                                 | Address/Data bit 3                |  |  |

|               |                                         | P0.4                                                                                                                                                                                                                                                                                                                                                                     | AD4                                 | Address/Data bit 4                |  |  |

|               |                                         | P0.5                                                                                                                                                                                                                                                                                                                                                                     | AD5                                 | Address/Data bit 5                |  |  |

|               |                                         | P0.6                                                                                                                                                                                                                                                                                                                                                                     | AD6                                 | Address/Data bit 6                |  |  |

|               |                                         | P0.7                                                                                                                                                                                                                                                                                                                                                                     | AD7                                 | Address/Data bit 7                |  |  |

| 55, 56, 59-64 | P1.0-P1.7                               | Port 1 is an 8-bit bidirectional input/output port with alternate functions.                                                                                                                                                                                                                                                                                             |                                     |                                   |  |  |

|               |                                         | Port 1.x                                                                                                                                                                                                                                                                                                                                                                 | Alternate Name                      | Alternate Use                     |  |  |

|               |                                         | P1.0                                                                                                                                                                                                                                                                                                                                                                     | T2                                  | Address/Data bit 0                |  |  |

|               |                                         | P1.1                                                                                                                                                                                                                                                                                                                                                                     | T2EX                                | Address/Data bit 1                |  |  |

|               |                                         | P1.2                                                                                                                                                                                                                                                                                                                                                                     | RxD1                                | Address/Data bit 2                |  |  |

|               |                                         | P1.3                                                                                                                                                                                                                                                                                                                                                                     | TxD1                                | Address/Data bit 3                |  |  |

|               |                                         | P1.4                                                                                                                                                                                                                                                                                                                                                                     | INT2/SS                             | Address/Data bit 4                |  |  |

|               |                                         | P1.5                                                                                                                                                                                                                                                                                                                                                                     | ĪNT3/MOSI                           | Address/Data bit 5                |  |  |

|               |                                         | P1.6                                                                                                                                                                                                                                                                                                                                                                     | INT4/MISO/SDA(1)                    | Address/Data bit 6                |  |  |

|               |                                         | P1.7                                                                                                                                                                                                                                                                                                                                                                     | ĪNT5/SCL(1)/SCK                     | Address/Data bit 7                |  |  |

|               |                                         |                                                                                                                                                                                                                                                                                                                                                                          |                                     |                                   |  |  |

<sup>(1)</sup> SCL and SDA not present on MSC1210/12/14.

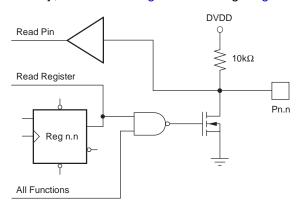

#### 1.2.1 Input/Output (I/O) Ports—P0, P1, P2, and P3

In principle, each port consists of eight bits, each of which may be placed low, high, or read by accessing the corresponding bit in the appropriate special function register (SFR). However, when alternate functions are used, the port SFRs are not usually accessed.

Every I/O port bit has an optional pull-up resistor that is enabled when the bit is in 8051-compatible mode (default after reset), as configured by the PxDDRH and PxDDRL SFRs, where x = 0 to 3. The pull-up resistor is disabled when the port bit is configured as either a CMOS output, open drain output or input, or when accessing external memory, as shown in Figure 1-3 through Figure 1-6.

Figure 1-3. Standard 8051 I/O Pin Structure

Figure 1-4. CMOS Output Pin Structure

Figure 1-5. Open-Drain Output Pin Structure

Figure 1-6. Input Pin Structure

#### Note that:

- When a port pin is to act as an input to an alternate function, it is essential that the pin not be configured as an output.

- To make use of the alternate functions associated with Ports 1 and 3, the corresponding port output latches should be high, with the data direction bits defined in a manner appropriate to the alternate function.

- A special case exists for the 8051 mode, which has a weak pull-up resistor and offers bidirectional capability.

#### 1.2.1.1 Port 0—P0

By default, Port 0 provides eight independently-programmable input/output bits. However, it may be configured to provide eight multiplexed, low-order address and data lines so that external memory may be accessed. See bit 1 of hardware configuration register 1 (HCR1).

External memory cycles may occur if:

- 1. The  $\overline{EA}$  pin is low when the RST pin is released;

- 2. An instruction is fetched from an address that is not associated with on-chip FLASH; or

- 3. When EGP0 (of HCR1) = 0 and a MOVC or MOVX instruction executes.

#### 1.2.1.2 Port 1—P1

Port 1 provides not only eight independently-programmable bits, but also a variety of alternate functions, as shown in Table 1-3.

**Table 1-3. Port 1 Alternate Functions**

| Port 1 Bit Name      | Alternate Function                                                                                                                                                                                             |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1.0 (T2)            | Clock source for Timer/Counter 2 when C/T2 (T2CON.1) is 1.                                                                                                                                                     |

| P1.1 (T2EX)          | If Timer/Counter 2 is in auto-reload mode and EXEN2 (T2CON.3) is 1, a negative edge (1–0 transition) causes Timer/Counter 2 to be reloaded and EXF2 (T2CON.6) to be set, which in turn may cause an interrupt. |

| P1.2 (RxD1)          | Serial input to USART1. An external receiver is needed to level shift RS-232 signals.                                                                                                                          |

| P1.3 (TxD1)          | Serial output from USART1. An external driver is needed to level shift RS-232 signals.                                                                                                                         |

| P1.4 (INT2/SS)       | Positive-edge triggered external 2 interrupt or active-low Slave-Select output during SPI operations.                                                                                                          |

| P1.5 (INT3/MOSI)     | Negative-edge triggered external 3 interrupt or the Master-Out/Slave-In during SPI operations.                                                                                                                 |

| P1.6 (INT4/MISO/SDA) | Positive-edge triggered external 4 interrupt or Master-In/Slave-Out during SPI operation, serial data during I <sup>2</sup> C operation.                                                                       |

| P1.7 (INT5/SCK/SCL)  | Negative-edge triggered external 5 interrupt or serial clock output for SPI operations, serial clock during I <sup>2</sup> C operation.                                                                        |

#### 1.2.1.3 Port 2—P2

By default, Port 2 acts as eight general-purpose input/output signals. However, its alternate function is to provide the upper byte of a 16-bit external address as determined by the  $\overline{EA}$  pin and bit 0 (EGP23) of HCR1. If  $\overline{EA}$  is low when RST is de-asserted, all memory accesses are external, and Port 2 continually outputs the high-order byte of 16-bit addresses. It also outputs bits of an address if EGP23 is 0 and a MOVX instruction is executed, regardless of  $\overline{EA}$ . This is either the upper byte of the data pointer or the value in MPAGE at 92h, depending on whether the MOVX instruction references DPTR or @Rx, respectively.

When  $\overline{\text{EA}}$  causes external memory accesses, the read and write strobes at P3.7 and P3.6, respectively, are enabled automatically. Selective external accesses must enable these strobes by clearing bit 1 (EGP0) or bit 0 (EGP23) of HCR1 to 0.

If EGP23 = 1 and  $\overline{EA}$  = 1, Port 2 output pins are always derived from its data latch.

#### 1.2.1.4 Port 3—P3

Port 3 provides not olny eight independently programmable bits, but also a variety of alternate functions, as shown in Table 1-4.

**Table 1-4. Port 3 Alternate Functions**

| Port 3 Bit Name      | Alternate Function                                                                                                     |

|----------------------|------------------------------------------------------------------------------------------------------------------------|

| P3.0 (RxD0)          | Serial input to USART0. An external receiver is needed for RS-232 signals.                                             |

| P3.1 (TxD0)          | Serial output from USART0. An external driver is needed for RS-232 signals.                                            |

| P3.2 (INTO)          | Active-low or negative-edge triggered interrupt. Gate for Timer/Counter 0.                                             |

| P3.3 (INT1/TONE/PWM) | Active-low or negative-edge triggered interrupt. Tone or Pulse-Width-Modulated output. Gate for Timer/Counter 1.       |

| P3.4 (T0)            | Clock source for Timer/Counter 0 if TMOD.2 is 1. See description of the Timer/Counters for gated conditions.           |

| P3.5 (IT1)           | Used as a clock source for Timer/Counter 1 if TMOD.6 is 1. See description of the Timer/Counters for gated conditions. |

| P3.6 (WR)            | Active-low write strobe for external memory if used.                                                                   |

| P3.7 (RD)            | Active-low read strobe for external memory if used.                                                                    |

### 1.2.2 Oscillator XOUT (pin 1) and XIN (pin 2)

In many applications, a quartz crystal or ceramic resonator is connected between XOUT and XIN to provide a reference clock that is between 1MHz and approximately 30MHz. The static design of the MSC121x allows a digital clock to be applied to XIN that is between 0MHz and 30MHz. A commonly-used crystal for exact baud rates is 11.0592MHz.

Note: The load capacitors for the crystal must be verified to work over the operating conditions of the application. It is generally better to use lower value load capacitors than those recommended by the crystal manufacturer because of the design of the oscillator circuit.

#### 1.2.3 Reset Line—RST (pin 13)

RST is the master reset line. When it is brought high for two or more clock cycles, the MSC121x is reset. All SFRs are placed at their default values and the program counter is reset to 0000h. The contents of internal SRAM are not affected by a reset, and instruction execution begins when RST is brought low, when both PSEN and ALE are high. If either PSEN or ALE is low when RST is brought low, the MSC121x enters Flash Programming mode.

The RST pin has a CMOS Schmitt-trigger input that permits the use of a simple RC network to achieve reset when power is first applied. For the MSC1210, the internal pull-down resistor is typically 200k $\Omega$ . For the MSC1211/12/13/14, there is no internal pull-down resistor.

#### 1.2.4 Address Latch Enable—ALE (pin 45)

As RST is de-asserted (low), ALE temporarily acts as an input with a  $9k\Omega$  internal pull-up resistor and is used in conjunction with PSEN to place the MSC121x in a programming mode. If neither ALE nor PSEN are pulled low, the MSC121x begins normal operation, where ALE is always an output that usually controls a strobed latch to demultiplex the address appearing on Port 0.

When no external memory is present, ALE may be used as an independent output that can be placed low or high via the ALE mode bits in PASEL at F2h.

#### 1.2.5 Program Store Enable—PSEN (pin 44)

As RST is de-asserted (low),  $\overline{\text{PSEN}}$  temporarily acts as an input with a 9k $\Omega$  internal pull-up resistor, and is used in conjunction with ALE to place the MSC121x in a programming mode. If neither ALE nor PSEN are pulled low, the MSC121x begins normal operation, where PSEN is always an output that usually acts as an active-low strobe to read from external program memory.

When no external memory is present, PSEN may be used as an independent output that can be placed low, high, or reflect the ADC modulator clock, via PSEN mode bits in PASEL at F2h.

#### 1.2.6 External Access—EA (pin 48)

EA is sampled as the RST pin is de-asserted (low) and determines whether the MSC121x fetches instruction codes from internal or external memory. When EA is high, code is fetched from internal memory; otherwise, code is always fetched from external memory. Changing the level on EA during normal operation has no effect.

Code is fetched at addresses pointed to by the Program Counter (PC) during program execution and also when a MOVC instruction is executed. In either case, if  $\overline{EA}$  is high but there is no internal memory associated with a particular address, an external fetch will occur.

#### 1.3 Enhanced 8051 Core

All members of the MSC121x family of mixed-signal microcontrollers use a core that is instruction-set-compatible with the industry-standard 8051. All instruction codes have the same binary patterns and produce exactly the same logical changes. However, the MSC121x is approximately three times faster in execution for the same clock frequency; instead of using 12 clocks per instruction cycle, the MSC121x uses four, as shown in Figure 1-7.

Figure 1-7. Comparison of MSC121x Timing to Standard 8051 Timing

The designer can either make use of the increased speed of execution or achieve the same speed, but at a lower clock frequency. A lower clock speed results in less system noise and lower power dissipation.

When porting existing 8051 code to the MSC121x, the designer/programmer may need to consider the change in performance associated with all software timing loops and make adjustments where necessary. By default, hardware timers are still clocked every 12 clock cycles, but can be changed to every four cycles, if required.

Existing software development tools for the 8051/8052 can be used directly to develop programs for the MSC121x.

#### 1.4 Family Compatibility

The MSC121x family allows the most cost-effective part to be used for each application and ensures a migration path towards larger memories when required. Code written for the 4K byte part runs unaltered on 8K, 16K, and 32K parts. Between the MSC1210 and MSC1211, the allocation and meaning of pins are similar, but not identical because of the different functions that are provided.

#### 1.5 Flash Memory

The MSC121x parts feature flexible Flash memory that can be partitioned into program and data areas that are best suited for each application. They may be programmed over the entire operating voltage range and temperature range using serial, parallel, and self-programming methodologies.

#### 1.6 Internal SRAM

The MSC121x contains a total of 1280 bytes of static random access memory (SRAM). 128 bytes are directly addressable using instructions that incorporate the address. An additional 128 bytes are indirectly addressable via instructions using a register as a pointer, while 1024 bytes are logically external but physically internal and accessed with the MOVX instruction.

#### 1.7 High-Performance Analog Functions

The analog functionality of the MSC121x is state-of-the-art. The ADC is extremely low-noise, and meets the most stringent requirements for analog instrumentation. The integrated programmable gain amplifier (PGA) further improves the performance of the ADC, which then achieves nanovolt resolution.

The integrated low-drift, high-accuracy voltage reference complements the performance of the ADC and usually eliminates the need for an external reference. However, ratiometric measurements are still possible and easily implemented.

Also present are a programmable filter, an analog multiplexer for single-ended and differential signals, a temperature sensor, burnout current sources, an analog input buffer, and an offset DAC.

#### 1.8 High-Performance Peripherals

Additional digital peripherals are included, which offload CPU processing and control functions from the core to improve further the overall efficiency. In particular, there is a 32-bit accumulator closely associated with the ADC, an SPI-compatible serial port with a FIFO buffer, two USARTs, power-on reset, brownout reset, low-voltage detection, multiple digital ports with configurable I/O, a 16-bit pulse-width modulator (PWM), a watchdog timer, and three timer/counters.

The SPI interface and FIFO buffer allow synchronous serial communications with minimal CPU overhead. For the MSC1211 and MSC1213, an I<sup>2</sup>C interface may be enabled, which replaces the SPI.

The 32-bit accumulator significantly reduces the processing overhead associated with multi-byte data. It allows automatic 32-bit additions from the ADC, and shifts without using CPU registers. 32-bit addition is supported with minimal program interaction.

# MSC121x Addressable Resources

This chapter provides a detailed description of the MSC121x addressable resources.

| Topic |                                               | Page      |

|-------|-----------------------------------------------|-----------|

|       |                                               |           |

| 2.1   | Introduction                                  | 24        |

| 2.2   | Program Memory and Data Memory                | <b>25</b> |

| 2.3   | Scratchpad RAM and Special Function Registers | <b>27</b> |

| 2.4   | Beyond 64K Bytes                              | <b>28</b> |

|       |                                               |           |

#### 2.1 Introduction

Some microprocessors have a single unified address space that is used for program code, data values and input/output ports. However, most 8051 cores (and thus the MSC121x), have several distinct addressable spaces that serve different purposes, as shown in Figure 2-1. In fact, the MSC121x implements all address spaces found in the 8051, but with a feature that permits self-modifiable code.

Direct and indirect 8-bit addresses access up to 384 bytes of on-chip resources, comprised of 256 bytes of static random access memory (SRAM) and up to 128 SFRs. 16-bit pointers (PC and DPTR) allow up to 64K bytes of program memory and 64K bytes of extended data memory to be accessed, which may be on-chip and/or off-chip.

Memory for data may be allocated in different places, depending upon the size of the data, how frequently it is altered, and how efficiently it is accessed. The resources available on the MSC121x are:

- 256 bytes of on-chip SRAM for working registers, bit-wide variables, byte and multi-byte variables, and a stack. This memory is accessed by the majority of data-processing instructions.

- 1024 bytes of on-chip extended SRAM, which is considered by the architecture as logically external data. It is used for variables that are needed less frequently and accessed only with MOVX (*X* for external) instructions, even though it is on-chip.

- A configurable number of kilobytes of on-chip FLASH memory that is accessed only with MOVX (X for external) instructions, even though it is on-chip. Typically, data here consist of lookup tables.

- A configurable number of kilobytes of user-defined, read-only memory (ROM) that is off-chip. It is

accessed only with MOVX instructions.

Figure 2-1. On-Chip and Off-Chip Resources

Memory for program code may be on-chip or off-chip. On-chip, it is realized by FLASH, ROM, or SRAM within the address range of 0000 to FFFFh. During program execution, if a code address is referenced that is not associated with on-chip memory, off-chip memory will be accessed. Even if on-chip program memory is present, off-chip memory will be used, as long as  $\overline{EA}$  is low when the RST (reset) pin is released.  $\overline{EA}$  also overrides access to on-chip SRAM that is mapped into code space.

Both program memory and data memory have 16-bit address spaces. They are logically distinct and usually physically separate.

#### 2.2 Program Memory and Data Memory