# Power-Supply Design for Sitara AM62A/P/D(-Q1) Using TPS6522430-Q1 and TPS6522230-Q1 PMICs

## Christian Oluwaniyi

This application brief shows the design considerations for implementing the TPS6522x-Q1 PMIC in systems the need compact, safe and cost-effective multi-rail power delivery like digital clusters, driver monitoring systems, camera mirrors and industrial vision modules. As embedded processors like the Sitara<sup>™</sup> and Jacinto<sup>™</sup> Processors become increasingly central to ADAS and infotainment platforms, power solutions must scale with performance demands while staying within strict size, thermal and reliability constraints.

The TPS65222-Q1 and TPS65224-Q1 address these challenges by integrating four high-efficiency buck converters and three configurable low-dropout regulators into a single 5x6mm package. With support for 5.5A single and dual phase buck operation up to 10A. It is capable of powering high-performance SoCs while reducing board space and BOM complexity. The PMIC also includes integrated power sequencing logic and GPIO-configurable PDN profiles, allowing reusability across multiple system configurations with minimal hardware changes. For variants that include an internal 12-bit ADC, *such as the TPS65224-Q1*, voltage telemetry enables in system monitoring of critical rails for diagnostic and safety assurance.

Functional safety is a cornerstone of the TPS6522x-Q1 design. Developed with ISO26262 in mind, it meets ASIL-B hardware integrity requirements and includes built-in protections like an integrated watchdog, over/undervoltage monitoring, thermal shutdown, and error signal management.

#### **Device Versions**

There are three different variants with the same functionality but slightly different features that are highlighted in Table 1. In this document, all these devices are referenced with TPS6522x30-Q1.

**Table 1. Device Versions**

| Generic Part Number (GPN) | Orderable Part Number | ADC | Package            |

|---------------------------|-----------------------|-----|--------------------|

| TPS65224-Q1               | TPS6522430RAHRQ1      | Yes | Non-Wettable Flank |

|                           | TPS6522430WRAHRQ1     | Yes | Wettable Flank     |

| TPS65222-Q1               | TPS6522230WRAHRQ1     | No  | Wettable Flank     |

Trademarks www.ti.com

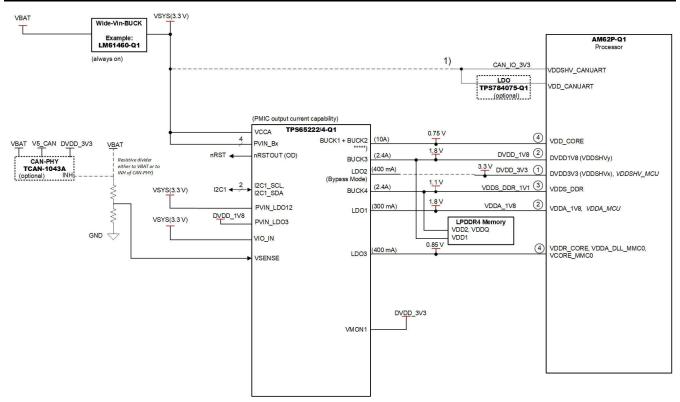

Figure 1. Block Diagram

Optional components are available for integration. Certain use cases may require these to achieve full functionality.

For a more detailed power design user's guide and supported use cases, request access at the following link: https://www.ti.com/drr/opn/TPS6522X-DESIGN-RESOURCES to make integration as easy as possible.

### **Trademarks**

2

Sitara<sup>™</sup> and Jacinto<sup>™</sup> are trademarks of Texas Instruments. All trademarks are the property of their respective owners.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated