# Understanding Gate Driver Slew Rate Control, MOSFET Switching Optimization and Protection Features

Audrey Kuehler, Sarah Anthraper, Joseph Chou, Anthony Lodi

#### Intro

The usage of DC motors is becoming pervasive in the automotive and industrial markets. Selecting a gate driver is not a trivial task since each end equipment often has unique requirements. There are many requirements for motor driver systems including Electromagnetic interference (EMI) performance, thermal performance, acoustic noise performance and system fault responses.

To meet the diverse requirements of customers' systems, TI's motor driver portfolio offers a wide variety of device features to support various needs. The purpose of this document is to provide an overview of some of the available features on the various Motor Driver gate drivers in TI's portfolio, focusing on features that are used for MOSFET switching control and optimization. Features include VDS slew rate control, deadtime control, parasitic dV/dt turn-on reduction, pre and post miller MOSFET switching optimization, duty cycle compensation, and voltage transient spiking reduction during fault shutdown. Table 1 provides an overview of which devices have each of the available features.

**Table 1. Device Features**

|                       | Device<br>(Gate<br>Driver) | VDS Slew Rate Control (IDRIVE) (O = Open Loop C = Closed Loop) | e Deadtime<br>(O = Open<br>Loop | Turnoff Pre-<br>Discharge<br>Current<br>(O = Open<br>Loop,<br>C = Closed<br>Loop) | Turnon Pre-<br>charge<br>Current<br>(O = Open<br>Loop<br>C = Closed<br>loop) | Turnon Post- Charge Current (O = Open Loop C = Closed Loop) |   | Fault Soft<br>Turnoff | Turnon<br>Dv/Dt<br>protection |

|-----------------------|----------------------------|----------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------|---|-----------------------|-------------------------------|

| Brushed<br>DC/Stepper | DRV8711                    | <b>√</b> 0                                                     |                                 |                                                                                   |                                                                              |                                                             |   |                       |                               |

|                       | DRV8702/3-<br>Q1           | <b>√</b> 0                                                     |                                 |                                                                                   |                                                                              |                                                             |   |                       |                               |

|                       | DRV8x05/6-<br>Q1           | <b>√</b> 0                                                     |                                 |                                                                                   |                                                                              |                                                             |   |                       |                               |

|                       | DRV8714/8-<br>Q1           | <b>√</b> O/C                                                   |                                 | <b>√</b> C                                                                        | <b>√</b> C                                                                   | <b>√</b> C                                                  | ✓ |                       |                               |

|                       | DRV8000/2-<br>Q1           | <b>√</b> O/C                                                   |                                 | <b>√</b> C                                                                        | <b>√</b> C                                                                   | <b>√</b> C                                                  | 1 |                       |                               |

|                 | Device<br>(Gate<br>Driver) | VDS Slew Rate Control (IDRIVE) (O = Open Loop C = Closed Loop) |              | Turnoff Pre-<br>Discharge<br>Current<br>(O = Open | Turnon Pre-<br>charge<br>Current<br>(O = Open<br>Loop<br>C = Closed<br>loop) | Turnon Post- Charge Current (O = Open Loop C = Closed Loop) | Duty Cycle<br>Compensat<br>ion | Fault Soft<br>Turnoff | Turnon<br>Dv/Dt<br>protection |

|-----------------|----------------------------|----------------------------------------------------------------|--------------|---------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------|-----------------------|-------------------------------|

| Brushless<br>DC | DRV8305-<br>Q1             | <b>√</b> 0                                                     |              |                                                   |                                                                              |                                                             |                                |                       | 1                             |

|                 | DRV3255-<br>Q1             | ✓O (Note1)                                                     | 0            |                                                   |                                                                              |                                                             |                                | 1                     | 1                             |

|                 | DRV3245-<br>Q1             | ✓O (Note1)                                                     | 0            |                                                   |                                                                              |                                                             |                                | 1                     | 1                             |

|                 | DRV3233-<br>Q1             | <b>√</b> 0                                                     | <b>√</b> O/C | <b>√</b> 0                                        |                                                                              | Note2                                                       |                                | 1                     | 1                             |

|                 | DRV8334/-<br>Q1            | <b>√</b> 0                                                     | <b>√</b> O/C | <b>√</b> 0                                        |                                                                              | Note2                                                       |                                | 1                     | 1                             |

|                 | DRV8161/2                  | <b>√</b> 0                                                     |              |                                                   |                                                                              |                                                             |                                | 1                     | 1                             |

|                 | DRV8363/-<br>Q1            | <b>√</b> 0                                                     |              |                                                   |                                                                              |                                                             |                                | 1                     | 1                             |

|                 | DRV8320/2<br>3             | <b>√</b> 0                                                     | <b>√</b> C   |                                                   |                                                                              |                                                             |                                |                       | 1                             |

|                 | DRV8350/3                  | <b>√</b> 0                                                     | <b>√</b> C   |                                                   |                                                                              |                                                             |                                | 1                     | 1                             |

|                 | DRV8340/3-<br>Q1           | <b>√</b> 0                                                     | <b>√</b> C   |                                                   |                                                                              |                                                             |                                |                       | 1                             |

|                 | DRV8328                    |                                                                |              |                                                   |                                                                              |                                                             |                                |                       |                               |

|                 | DRV8329/-<br>Q1            |                                                                |              |                                                   |                                                                              |                                                             |                                |                       |                               |

|                 | DRV8300/-<br>Q1            |                                                                |              |                                                   |                                                                              |                                                             |                                |                       |                               |

#### **Slew Rate Control**

Slew rate control is one of the key elements to consider when designing a motor system. Determining the desired MOSFET slew rate is a tradeoff between EMI performance and efficiency. In general, there are two methods for slew rate control: open loop slew rate control and close loop slew rate control. MOSFET slew rate control is accomplished by adjusting the gate current to control the MOSFET turn on and turn off time. For the open loop slew rate control, the designer needs to select the gate current for the desired slew rate. For the close loop slew rate control, the gate driver device automatically adjusts the gate current to achieve the desired slew rate through some hardware or software configurations.

#### **VDS Slew Rate Control**

Electrical noise produced by the motor's magnetic fields and switching currents produces EMI, which can disrupt the operation of nearby electronic devices due to radiated or conducted emissions. EMI is influenced by motor design, power and motor speed. There are other sources of EMI in a motor driver system, however in this article we focus on EMI generated during MOSFET switching in the motor design.

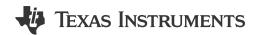

Slew rate control during the MOSFET Miller region is essential to balance EMI and thermal performance in a motor design as shown in Figure 1 below. Slowing down the VDS slew rate can help reduce EMI by suppressing high-frequency switching noise caused by the fast rise or fall of the switch node voltage. Although slowing down the VDS slew rate improves EMI, the incurred power loss from the MOSFET switching increases. This is because the device spends longer time operating in a region with high VDS voltage and high IDS current, resulting in more power loss during slower switching in the Miller range. Selecting a slew rate that balances EMI performance with thermal performance for the target application is important for a design engineer.

Figure 1. VDS Slew Adjustability

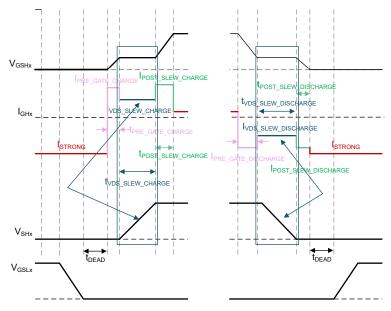

Many of Ti's motor drivers offer adjustable slew rate control to allow the user to tune the MOSFET switching speed based on EMI and thermal considerations. There are two types of slew rate control – open loop slew rate control and close loop slew rate control. For the open loop control method, the designer can configure the charge/discharge gate current over SPI to control the slew rate. Control of the gate current during the MOSFET Miller region is a key component for adjusting the VDS rise and fall times of the MOSFET. For a driver that uses the close loop method for slew rate control, the engineer can configure the target slew rate in the gate driver registers, and the driver automatically adapts the gate current as needed to hit the target slew rate by monitoring the VDS voltage slew rate. For a driver without open loop or closed loop slew rate control, the MOSFET slew rate has to be adjusted by adding external components such as gate resistors to slow down the gate current. Configurable open loop and closed loop slew rate control has the benefit of ease of use during the development phase since configurable open loop and closed loop slew rate control allows for simple adjustments over SPI to adjust the slew rate with different MOSFETs without the need of hardware change. This allows the ability to quickly tune the slew rate of the MOSFET during testing to find the best setting. Configurable slew rate control also reduces design size and design cost by removing resistor and diode components as shown in Figure 2. Configurable slew rate control saves up to three resistors (RSOURCE, RSINK, RPD) and one diode (DSINK) for each MOSFET.

Figure 2. Hardware Slew Rate Control

# **MOSFET Switching Optimization**

# **Turnoff Pre-Discharge Current**

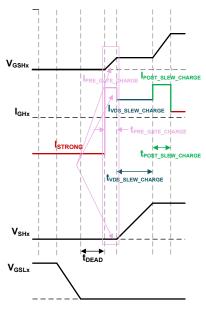

MOSFET gate turnoff pre-discharge is a feature that allows the user to program a strong pre-discharge gate current to rapidly discharge the gate voltage to the miller region. An example is shown in Figure 3, where a strong gate pre-discharge current is applied to the gate to rapidly discharge the gate voltage down till the miller region, at which time the driver switches over to a slower discharge current through the EMI critical region.

Figure 3. Pre-Discharge Current

A high pre-discharge current can be used in this region since there is no VDS slewing (VSHx) present prior to the miller region, resulting in less EMI concern. This can be done in an open loop or closed loop configuration. In open loop, the user selects the desired pre-discharge gate current and selects the desired time the gate current is applied based on how long the current takes to reach the miller region for the particular MOSFET. With closed loop, the user programs a pre-discharge time over SPI and the gate driver applies a strong pre-discharge gate current to discharge the gate to the miller region based on the programmed pre-discharge time.

The benefits of using turnoff pre-discharge current include:

- 1. Reduction in MOSFET switching losses

- 2. Higher duty cycle operation

- 3. Reduction of duty cycle jitter

MOSFET switching losses can be reduced due to reducing the duration of operation in a higher Rdson region during MOSFET turnoff. Additionally, higher duty cycle operation can be achieved and duty cycle jitter can be reduced due to reducing the overall MOSFET turnoff time, providing more precise duty cycle control by reducing the switching time.

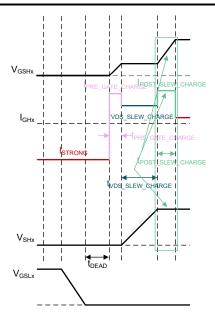

## **Turn on Pre-Charge Current**

Figure 4. Pre-Charge Current

Turn on pre-charge current is similar to turn off pre-discharge current. For turn on pre-charge current, the user is able to program a strong pre-charge gate current to rapidly charge the gate voltage until the miller region is reached. Since no VDS slewing is present prior to the miller region a high pre-charge current can be used. Currently, some of TI's drivers offer closed loop configuration for turn on pre-charge current. The user configures a target pre-charge time, and the driver uses a stronger gate drive current during MOSFET turn on to target the configured pre-charge time until the driver detects that the miller region is reached.

The benefits of using gate turn on pre-charge current are similar to the benefits of the gate turnoff pre-discharge feature:

- 1. Shorter MOSFET turn on time, reducing MOSFET switching losses

- 2. Higher duty cycle operation

- 3. Reduction of duty cycle jitter

MOSFET switching losses can be reduced due to faster MOSFET turn on time resulting in lower power losses due to less time spent operating with body diode conduction. Additionally, higher duty cycle operation can be achieved, and duty cycle jitter can be reduced due to reducing the overall MOSFET turn on time, providing more precise duty cycle control by reducing the switching time.

#### **Turn on Post-Charge Current**

Figure 5. Post-Charge Current

Gate turn on post-charge current is a feature used to fully enhance the MOSFET gate voltage after the miller region is complete. This is done by applying a strong post-charge gate current that rapidly charges the gate voltage to 12V after the VDS voltage has finished slewing. A high post-charge current can be used since there is no VDS slewing present after the miller region has finished. This feature is offered with open and closed loop configuration. In open loop configuration the user selects the desired post charge gate current, and the driver switches to the selected current once the IDRIVE control time expires during MOSFET turn on. In closed loop, the driver uses a stronger gate drive current during MOSFET turn on after the driver detects the VDS slew is complete.

Benefits of turn on post-charge current include:

1. Reducing power loss during MOSFET turn on.

By quickly enhancing the MOSFET VGS voltage to approximately 12V after the VDS slew has completed, this results in reducing the MOSFET Rdson faster and results in a reduction in power loss due to less time being spent in high RDSON operation.

### Protection/Fault/Behavior Response

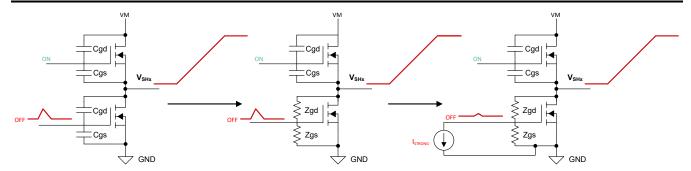

## Turnon dV/dt protection

6

A dV/dt turnon is a system issue that can occur when rapidly slewing a MOSFET. When the switching node (the connection point between the high-side and low-side MOSFETs) rapidly slews (Figure XX), voltage can couple into the gate of the non-switching MOSFET through the parasitic gate-to-drain capacitance ( $C_{GD}$ ) of that MOSFET. The coupling can cause a rise in the gate-to-source voltage of the MOSFET which is supposed to remain off. If the gate voltage crosses the MOSFET threshold voltage (Vth), the off MOSFET can briefly turn on while the opposite MOSFET is being turned on which causes cross conduction or shoot through. Shoot through can result in MOSFET overheating and possible damage. By enabling a strong pulldown on the off MOSFET during the turnon of the opposite MOSFET, the gate driver can provide a low-impedance path for parasitic charge that couples into the gate. This strong gate pulldown path helps reduce any rise in the gate-to-source voltage of the off MOSFET helping prevent parasitic turnon due to dV/dt coupling during MOSFET switching.

Figure 6. dV/dt Protection

# Benefits of turnon dV/dt protection:

Can help reduce dV/dt coupling during MOSFET turnon by strongly pulling down the opposite MOSFET gate, possibly eliminating the need for adding external Cgs capacitance depending on the design. (possibly eliminate)

## **Configurable Deadtime**

As mentioned when discussing dV/dt protection, avoiding cross-conduction or "shoot-through" conditions to prevent damaging the power MOSFETs or system supply when switching MOSFET systems is critical. Cross conduction occurs when both the high-side and low-side MOSFET are turned on at the same time. Power supply and ground introduce a low impedance path which allows for large current flow, potentially damaging the external MOSFETs or power supply as well as other components.

Shoot-through most commonly occurs when switching from one FET being on to the opposite FET being on. Sufficient time must be given between one FET being commanded off and the other FET being commanded on to maintain that the device gives enough time for the first FET to completely turn off to avoid both MOSFETs being on at the same time. This delay between turning off one MOSFET and turning on the opposite MOSFET is called dead time. Longer dead time decreases the efficiency of the motor driver because of diode conduction losses, but too short of deadtime can result in both MOSFETs turning on at the same time.

Depending on the device, Configurable dead time either uses close loop or open loop control.

In closed loop configurable deadtime, the driver can maximize efficiency by monitoring the MOSFET VGS voltage to provide an optimized amount of dead time for the switching MOSFET system. The VGS monitors make sure the driver disables the opposite MOSFET in the half-bridge before enabling the commanded MOSFET.

In addition to cross conduction protection (shoot-through), this method can provide system performance benefits by reducing the period of diode conduction. Conduction losses of the MOSFET internal body diode are typically worse than standard MOSFET conduction losses and decrease the overall system efficiency. Drivers integrate internal handshaking when switching from the low-side to high-side (or high-side to low-side) external MOSFET. The handshaking is designed to prevent the external MOSFETs from going to a period of cross conduction. The internal handshaking uses VGS monitors of the external MOSFETs determines when one MOSFET has been disabled and the other can be enabled. This handshaking lets the system insert an optimized dead time into the system without the risk of cross conduction.

In Open loop Control, the user selects desired deadtime, the driver monitors time between input commanded off and opposite input commanded on and forces the outputs low for the programmed deadtime duration. In Closed Loop Control the user selects desired deadtime, driver monitors VGS voltage to determine when FET is off, then inserts deadtime

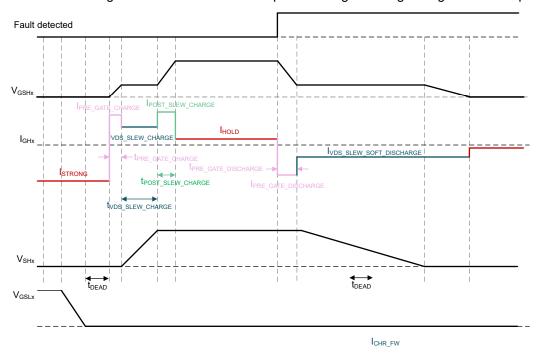

#### **Fault Soft Turnoff**

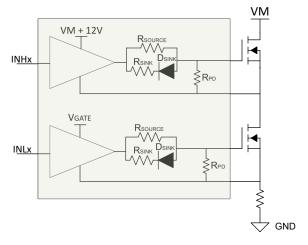

Fault Soft Turnoff protects the driver in the case of a fault which leads to a shutdown event (for example overcurrent or shoot through condition) by slowing the VDS slewing during MOSFET turnoff. Slowing the slewing lowers inductive spiking and reduces transients which increases design robustness during overcurrent events. When high current builds up in a system, a fast turnoff causes significant inductive spiking which can damage

the driver. During normal switching operation, the MOSFET can turn off relatively quickly (Figure 7). But in the case of an overcurrent fault possibly due to a failed MOSFET, the high current flowing through the parasitic inductances on the board can cause large spiking if the current path is rapidly cut off and rerouted through the MOSFET body diode. To help overcome this challenge, the driver slows the MOSFET turnoff by lowering the gate current to a soft discharge current to slow down the phase voltage slewing during the fault response.

Figure 7. Fault Response

The way this soft shutdown current is implemented varies from device to device. When the driver detects a fault, some devices lower the current a certain number of steps below the gate current level selected during normal operation. Other drivers allow the user to select the desired lowered gate drive level. There are also devices which enable a pre-discharge current during a shutdown event prior to reaching the miller region. The user can program the discharge current which discharges the gate to the miller region and then switch to the soft discharge current throughout the Vds slewing region. Devices with pre-discharge during shutdown help the driver get to the Miller region as quickly as possible before enabling the soft discharge current to fully turn off the MOSFET. This predischarge allows for reducing overall MOSFET turnoff time during fault response and shortening the time that high currents are present in the system while still slowing down during the critical VDS slew region.

## **Duty Cycle Compensation**

8

The goal of Duty Cycle Compensation is to positively manage Propagation delay and the impact on switching performance so that the output phase voltage duty cycle equals the commanded input duty cycle. Good switching performance is important to achieve peak performance from the motor in regard to speed and torque control. Duty Cycle Compensation helps compensate for the delay from input to output and mismatch during turn on and turn off behaviors. These two parameters directly impact the minimum and maximum duty cycle, frequency range, and duty cycle step resolution.

While most gate drivers specify the delay and mismatch parameters, gate drivers are only one part of the overall input to output delay. The other key part is the MOSFET switching delay. At high slew rates, the MOSFET contribution to propagation delay and mismatch is often minimal as compared to the driver delays. In contrast, at slow slew rates, as often found in EMC sensitive systems, the MOSFET slew rate can be a main contributor. Duty cycle compensation monitors the output phase on time and adjusts the output phase to match the input commanded on time, adjusting for changes in motor current direction. Benefits include more accurate duty cycle control, where the output duty cycle is adjusted to closely match the commanded input duty cycle.

www.ti.com Trademarks

## Conclusion

TI offers a variety of brushed and brushless motor gate drivers for a variety of industrial and automotive applications. A designer can choose a TI BDC or BLDC Gate driver to meet the application needs with a mix of features across the portfolio, including features to help tune the balance of EMI performance and thermal performance by controlling switching slew rate, additional pre and post Miller range performance optimization during MOSFET switching periods, shoot through protection by configurable or automatic deadtime insertion and parasitic dV/dt gate turn on prevention, and soft turn off during fault events to reduce voltage spikes especially in an over current fault event. These features help address challenges with EMI, efficiency, acoustics, MOSFET protection, and more. To learn more about TI's motor driver products, please visit TI Motor Drivers

# **Trademarks**

All trademarks are the property of their respective owners.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated