# Application Note Simplifying Distributive Antenna System or Repeater Design Without FPGA

Kang Hsia

#### ABSTRACT

Different wireless communication systems serve different purposes depending on the service environment, coverage requirement, and user capacity. This report provides a deep dive to a typical distributive antenna system (DAS) and repeater system, and their associated service environment. Moreover, this also highlights the benefits of the integrated radio frequency transceivers in a direct receiver to transmitter loopback with built-in digital pre-distortion function to different communications systems.

# **Table of Contents**

| 1 Introduction                                                             | 2 |

|----------------------------------------------------------------------------|---|

| 1.1 Acronyms Used in This Document                                         | 2 |

| 2 Distributive Antenna System                                              |   |

| 3 Repeater System                                                          |   |

| 4 Goals of DAS and Repeater Design                                         | 6 |

| 5 RF Repeater System Without FPGA/ASIC                                     |   |

| 6 Overcoming Bandpass Filter Effects From Cable Dispersions and Multi-Path |   |

| 7 Summary                                                                  | 9 |

| •                                                                          |   |

# **List of Figures**

| Figure 2-1. Typical Environment for DAS Setup                                  | . 3 |

|--------------------------------------------------------------------------------|-----|

| Figure 2-2. Principle of DAS Operation to Improve Indoor Coverage and Capacity |     |

| Figure 3-1. Typical Environment for Repeater Setup                             |     |

| Figure 5-1. AFE7769D RX DDC to TX DUC Loopback Feature                         |     |

| Figure 5-2. AFE7769D TX, RX, and FB Chain                                      |     |

| 5                                                                              |     |

#### Trademarks

All trademarks are the property of their respective owners.

# **1** Introduction

This application report provides background on 4G or 5G distributed antenna systems (DAS), repeater, or base transceiver stations (BTS) setup, and provides an example of an actual design of a simplified DAS or repeater module design without field programmable gate array (FPGA) or digital front end (DFE) logic, with consideration of the AFE7769D's built-in direct RF loopback functionality, crest factor reduction (CFR) and digital pre-distortion (DPD) processing features. The reference design is flexible and modular, and provides wide instantaneous bandwidth, a flexible RF range, and an optional JESD204C interface that relieves data transfer bottlenecks.

The overall design includes the AFE7769D family of RF-sampling transceivers, which enable modular platform designs with multiple channel counts for transmitters and receivers, as well as various instantaneous bandwidth capabilities.

Applications include:

• DAS

2

- Repeaters

- Small Cell

- Macro-BTS

- Massive MIMO (AAS)

### 1.1 Acronyms Used in This Document

DAS: distributive antenna system

BTS: base transceiver station

RF: radio frequency

DDC: digital down converter

DUC: digital up converter

FPGA: field programmable gate array (FPGA)

DFE: digital front end logic

# 2 Distributive Antenna System

An example of a typical wireless communications system environment using DAS is described in this section.

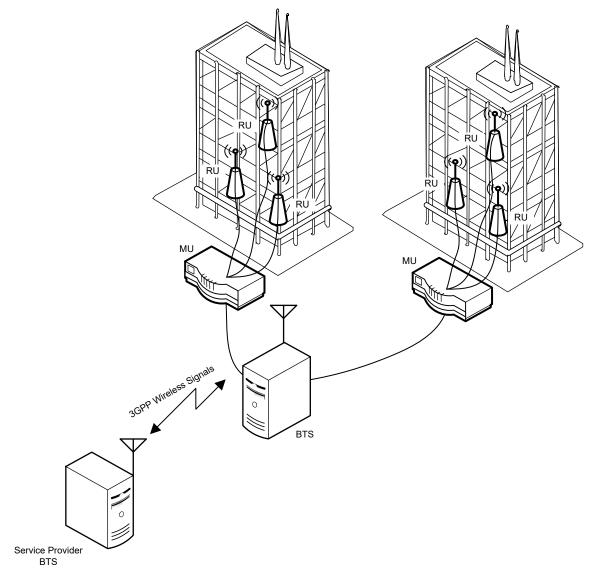

Figure 2-1. Typical Environment for DAS Setup

Figure 2-1 shows a typical service environment for DAS. Many private office buildings and public service buildings have many mobile users in a crowded and enclosed environment. The enclosed nature of the building environment does not allow external wireless signals from a base station (BTS) to reach inside the buildings. Therefore, without additional remedies to the wireless signal path, these buildings have coverage and capacity issues for the mobile users.

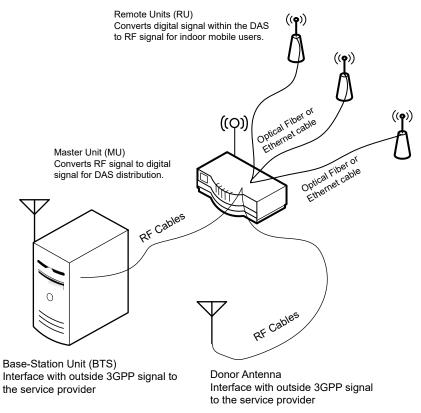

#### Figure 2-2. Principle of DAS Operation to Improve Indoor Coverage and Capacity

The building owners or manager can introduce DAS to simply redistribute the wireless signal path from outside the building to inside the building. Per Figure 2-2, a DAS typically consists of two principle elements: a master unit (MU) and one or more remote units (RU). The simplified operating principle is based on the master unit interface with an outside BTS or donor antenna that redistributes the outside signal indoors through indoor remote units. The indoor remote units can be placed throughout the building to improve coverage and capacity of the service. The key constraint is that the DAS is transparent to the mobile user and the BTS as the DAS is simply redistributing the signal.

The following summarizes the functionalities of each key component of the DAS:

- MU: this is the master unit of the DAS. The MU interfaces primarily with an outside BTS or donor antenna, and it bridges the outside signal with indoor RUs.

- RU: the building owner or manager can install various RUs throughout the building to increase coverage and capacity of the interface with the mobile users. The RUs interface with the MU to bridge the mobile users with the MU.

- BTS: this unit is responsible for the air interface between the mobile service provider and the mobile user. Since the air interface has difficulty penetrating through the buildings, DAS are installed to bridge the BTS with the mobile user and service provider.

Donor Antenna: in case the air interface signal is sufficiently strong without significant fading effect, the MU can interface directly with a donor antenna to reach a more remote BTS as opposed to installing a BTS outside the building. Installing the BTS directly outside the building to interface with the MU directly requires RF cell planning from the service provider to assess potential interference to other cells. The use of a donor antenna can possibly save the building manager the cost of BTS cell planning and installation and also reduces DAS installation time. If a BTS is indeed installed near the building, the MU can connect to the BTS with fiber cable directly without the use of a donor antenna.

New trend of the DAS design includes power distribution over Ethernet or over fiber. This approach allows the entire MU and RU to be powered over Ethernet or fiber line directly. The idea of power over cable is to allow the entire DAS system to be powered directly and independently from the main building power distribution service. The power utility bill can be separated between the DAS system and building owners.

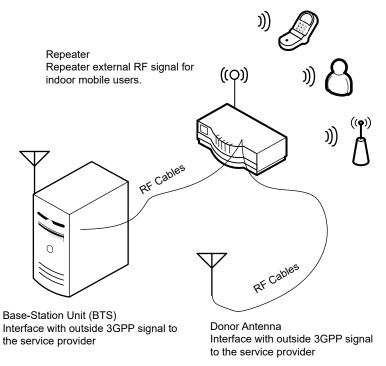

## **3 Repeater System**

Repeater system is very similar to DAS system. However, instead of fiber optic or Ethernet cable to distribute the RF signal from the MU to the RU, both the MU and RU have another set of uplink and downlink antenna for the distribution of RF signal over air, as shown in Figure 3-1.

Figure 3-1. Typical Environment for Repeater Setup

# 4 Goals of DAS and Repeater Design

Regardless of the design for the DAS or repeater system, the goals of the system are to achieve the following:

- Direct RF signal transfer and redistribution that is transparent to the user. The user does not receive any

unwanted noise on top of the existing voice or data transfer. The base station does not receive any unwanted

noise on top of existing signal.

- Enhances signal strength and signal coverage. The user does not experience any lack of coverage as they

move into any buildings.<sup>1</sup>

- Introduces zero latency to the RF input to the RF output. Through the redistribution process, the user experiences delay in voice or data transfer.

With the above design goals, the system designers can look into the AFE77xxD family of integrated transceiver <sup>2</sup> with CFR and DPD built to fulfill requirements through the following features:

- Support of multple RF operating bands from both the 4G and 5G spectrums. For example, the AFE77xxD family of devices can support 2T2R1FB operating in FDD RF bands (for instance, B1, B3, and B7), while the other 2T2R1FB operating in TDD RF bands (N41, N77, and N79).

- Up to 4x RF PLLs to support multiple operating RF bands. With flexible on-chip low IF NCO on both DDC and DUC side, the device can support up to three RF bands.

- Integrated CFR and DPD block on the RF transceiver. This offloads all digital logic resources from FPGA or digital ASIC.

- Instantaneous bandwidth of 300MHz support. The interface rate for RX DDC and TX DUC chains can support up to 368.64MSPS of interface rate, which translates to about 300MHz of maximum output and input bandwidth out of the transceiver. The CFR and DPD rate can support the linearization of the entire 300MHz of bandwidth.

- Up to 4x SerDes transmitter (STX) and 4x SerDes receiver (SRX) with 32.5Gbps of SerDes rate. With integrated JESD204C support, the RF transceiver can support high density data transfer.

- Lineariztion of the power amplifiers of up to 50dBm of PA rated output power. Designers can utilize one PCB solution to support DAS, repeater, and macro remote radio applications.

- Direct DDC to DUC loopback mode to further reduce digital latency in DAS and repeater applications.

<sup>&</sup>lt;sup>1</sup> Digital pre-distortion is a technique to push the boundary of the RF power amplifier in the transmitter chain, and therefore increases the signal coverage. The AFE7769D family of devices with integrated DPD can maximize PA output power, and hence improve the coverage.

<sup>&</sup>lt;sup>2</sup> For details to the AFE7769D family of devices, see the AFE77xxD Quad/Dual-Channel RF Transceiver With Dual Feedback Paths Integrating CFR/DPD Data Sheet (SBASAG4).

# **5 RF Repeater System Without FPGA/ASIC**

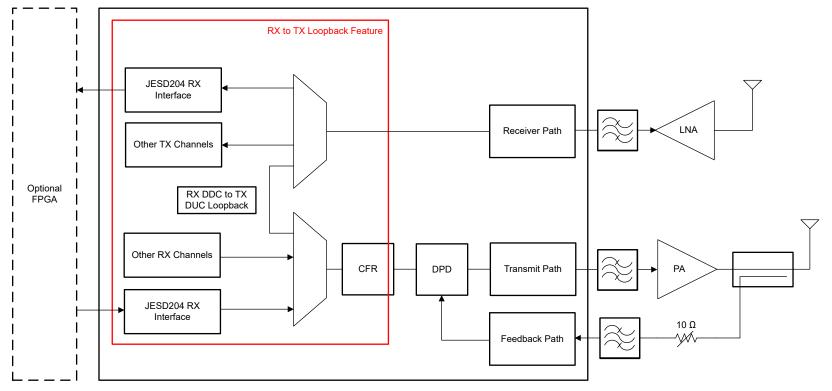

Traditionally, the typical RF input to RF output loopback through integrated RF transceiver has to go through the following path as shown in the signal chain for a typical repeater system (see Figure 5-1).

RF input to RX DDC chain, through the JESD204 TX chain, externally through some PCB routing (either through the FPGA or directly JESD204 TX to JESD204 RX traces), through the JESD204 RX chain, to the TX DUC chain and then up convert to the RF output.

Although the FPGA provides additional signal processing enhancement for the DAS or repeater system such as additional digital filtering and potentially ISI cancellation (for example, inter symbol cancellation), the FPGA is the main cost driver for the system, and potentially impact overall power consumption of the system. Moreover, the industrial standard interface between RF transceiver is the JESD204 standard with serialized interface. The interface between the FPGA and RF transceiver adds latency to the repeater system.

As shown in Figure 5-1, The AFE7769D offers internal RX DDC to TX DUC direct loopback. As the RX DDC chain's down conversion signal feeds directly into the TX DUC upconversion chain, the entire signal path has reduced latency.

Figure 5-1. AFE7769D RX DDC to TX DUC Loopback Feature

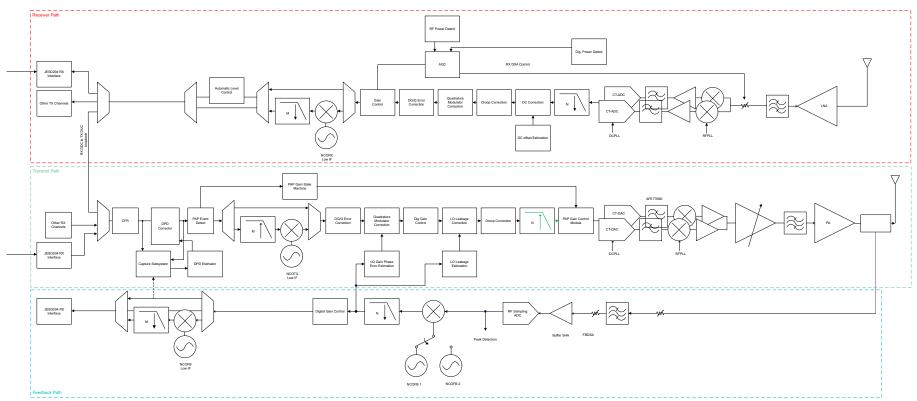

As shown in Figure 5-2, in addition to the direct RX DDC to TX DUC direct loopback, the integrated digital pre-distortion (DPD) capability of the AFE7769D can linearize power amplifiers in the transmitter system. Integrating the DPD processing logic to the RF transceiver further reduces the cost and power consumption of the system.

Figure 5-2. AFE7769D TX, RX, and FB Chain

The benefits of the internal RX DDC to TX DUC direct loop back includes the following:

- Reduction of overall repeater system power consumption: the system designer does not need to include the FPGA and the JESD204 power consumption into the system. The designer can also reduce the size of the power supply circuitry as needed.

- Reduction of overall system cost: with the removal of the FPGA and downsizing of the PCB size and power supply circuit power capacity, the designer can further reduce the overall cost.

Moreover, the system designers can have additional flexibilities in the design. They can configure the AFE7769D RX DDC to TX DUC loopback with the following capabilities:

- Flexibility to enable which signal chain has the loopback path feature: For example, the user can enable RX1 to TX1 and RX2 to TX2 with DDC to DUC loopback, while maintaining traditional JESD204 interface with the FPGA for RX3 to TX3 and RX4 to TX4.

- Flexibility to enable internal signal mux feature to allow RX channels to loop back to certain TX channels: for example, the user has ability to route RX1 to TX2 and RX2 to TX1, if the PCB layout requires such flexibility.

# 6 Overcoming Bandpass Filter Effects From Cable Dispersions and Multi-Path

With the ideal condition of signal propogation from the MU to RU, the signal characteristic has a proper pulse filter to maintain the waveform meets various regional spectral mask requirements. If the signals go through typical Ethernet or fiber channel, the channel characteristic can introduce dispersion factor that can potentially widen the effective shape of the signal. In the case of repeater system, the signal goes through multi-path effect. In essence, the fiber dispersion factor and the repeater multi-path effect create a bandpass behavior and distorts the original pulse shaping filter. Therefore, to overcome the bandpass behavior, the design does the following:

- RX DDC: the designers choose the proper DDC filter within the AFE77xxD family to removal additional distortions due to the bandpass behavior.

- RX analog front end filtering: the designers add analog RF bandpass filters to filter out the additional distortions to the waveform.

## 7 Summary

Benefits of AFE7769D family in DAS and Repeater Systems: The AFE7769D offers many benefits in the DAS and repeater design. Besides the integrated CFR and DPD capability to offload processing logic from FPGA or ASIC to the integrated RF transceiver, the AFE7769D family also includes built-in DDC to DUC loop back mode to further eliminate the additional FPGA or ASIC based on the system requirement.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated